оо

О5 05 СО О

Изобретение относится :к цифровой измерительной технике.

Цель изобретения - упрощение цифрового измерителя отклонения частоты от номинальной.

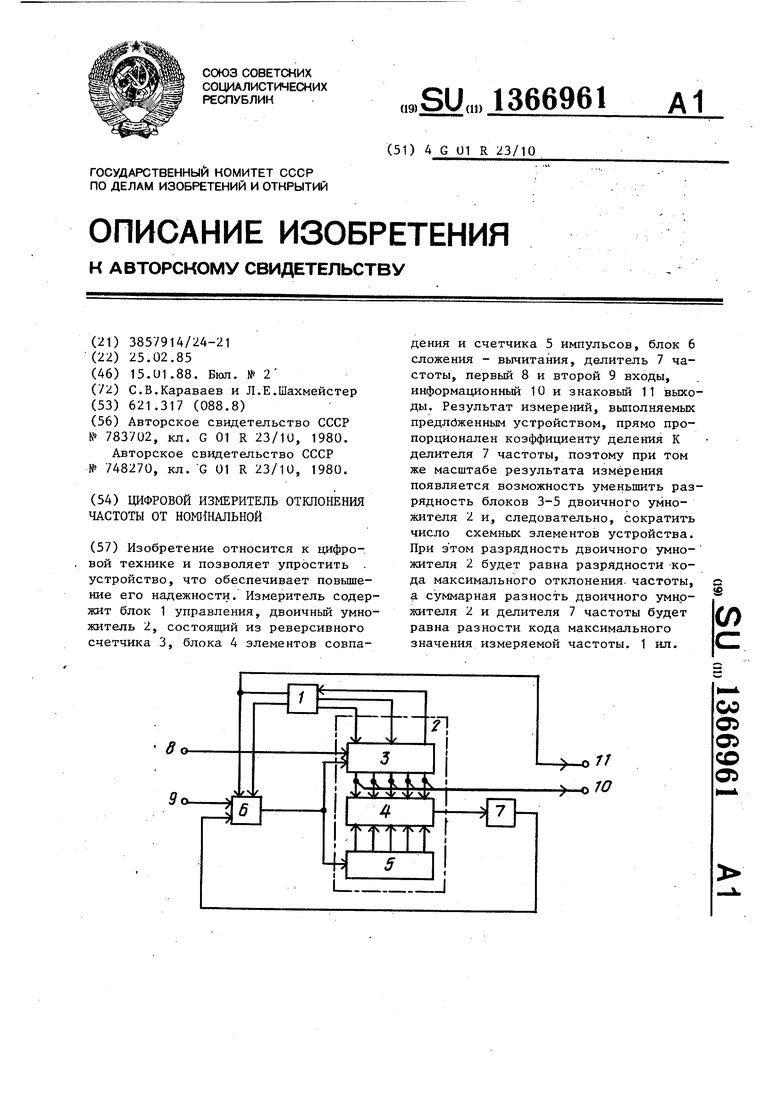

На чертеже представлена функциональная схема предлагаемого измерителя .

Цифровой измеритель содержит блок 1 управления, двоичный умножитель 2, состояа1,ий из реверсивного счетчика 3 блока 4 элементов совпадения и счетчика 5 импульсов, блок 6 сложения- вычитания, делитель 7 частоты, пер- вь1й 8 и второй 9 входы, информационный 10 и знаковьй 11 выходы.

Блок ,1 управления первым и вторым выходами соединен с первым и вторым соответственно управляющими входам . блока 6 сложения - вычитания, первьй вход которого является вторым входом измерителя, а второй вход соединен с выходом делителя 7 частоты, вход «которого соединен с выходом двоично- |Го умножителя 2, которым является выход блока А элементов совпадения, :первые входы которого соответственно соединены с выходами реверсивного счетчика 3 и являются информационным выходом 10 измерителя, а вторые входы соединены с выходами счетчика 5 импульсов, вход которого объединен с вьиитающим входом реверсивного счетчика 3 и соединен с выходом бло- ка 6 сложения - вычитания, суммирующий вход реверсивного счетчика 3 является первым входом 8 измерителя, знаковым выходом 11 измерителя является первый выход блока 1 управления вход которого соединен с выходом переполнения реверсивного счетчика 3, входу направления счета которого соединены с третьим и четвертым выходами блока 1 управления.

Измеритель, работает следующим образом.

: Предпололсим, что частота f. , поступающая на вход 8, больше частоты .fj, поступающей на вход 9. Блок 1 управления задает блоку 6 режим сло- жения, а далее управляет режимом работы блока 6 и направлением счета реверсивного счетчика 3 таким образом, что всегда поддерживается отри- цательньй характер обратной связи двоичного умножителя 2 через делитель 7 частоты с блоком 6 сложения - вычитания.

Частоты на входах реверсивного счетчика 3 f. и f равны:

f. f, ;

f- f, + fj ,

где fa - частота на выходе делителя 7,равная

f - f . 5 . L .

- . N, k

где N 2 - коэффициент пересчета

двоичного умножителя 2; п - разность двоичного умножителя;

k - коэффициент деления делителя 7 частоты; Z - код в реверсивном .счет- 1чике 3.

В установившемся режиме частоты на суммирующем f и вычитающем f входах реверсивного счетчика равны, (поэтому

k . f

f, f

(1)

.k- - - ,

л

где

Таким образом, в устайовившемся режиме содержимое реверсивного счет«чика 3 пропорционально разности частот и при выборе частоты f в ка|честве номинальной пропорционально отклонению измеряемой частоты f от

номинальной со знаком минус,

2

Если при f т

блок 1 управления находится в состоянии, задающем работу блока 6 в режиме вычитания, то направление счета реверсивного счетчика 3 противоположно указанному на чертеже, а установившегося ре- жима не будет, так как

f 4

fi

f.

- f

1 -I при любой частоте fa.

Следовательно, реверсивньй счетчик 3 переполнится и сигнал с его выхода переполнения поступит на. блок 1 управления, которьй переключит блок 6 и реверсивньй счетчик 3 в состояние, рассмртренное вьше.

При f,

работа измерителя

происходит аналогично, но установившийся режим достигается при работе блока 6 в режиме вычитания. В этом случае .

N.

Z

4f

(2)

CO знаком плюс, который соответст- g

д

вует уровню логического новом выходе 11.

нуля на знаИз формул (1) и (2) следует, что результат измерения прямо пропорционален коэф4)ициенту деления к делителя 7 частоты, и поэтому при том же масштабе результата измерения Z появляется возможность уменьшить разрядность блоков 3-5 двоичного умножителя 2 и, следовательно, сократить число элементов измерителя, т.е. упростить его. В этом случае разрядность двоичного умножителя 2 равна

g

66961

ного счетчика и являются информационным выходом измерителя, а вторые входы соответственно - с выходами счетчика импульсов, вход которого объединен с вычитаюпщм входом реверсивного счетчика и соединен с выходом блока сложения - вычитания, первый информационньй вход которого д (Является вторым входом измерителя, а первый и второй управляющие входы соединены соответственно с первым и вторым выходами блока управления, вход которого соединен с выходом переполнения реверсивного счетчика, суммирующий вход которого является входом измерителя, отличающийся тем, что, с целью упрощения, дополнительно введен делитель

15

| название | год | авторы | номер документа |

|---|---|---|---|

| УМНОЖИТЕЛЬ ЧАСТОТЫ | 1990 |

|

RU2020558C1 |

| Устройство для определения первой разности частотно-импульсного сигнала | 1982 |

|

SU1043675A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УСКОРЕНИЙ | 2001 |

|

RU2189047C1 |

| СИСТЕМА КОРРЕКЦИИ | 2005 |

|

RU2282148C1 |

| Цифровой линейный экстраполятор | 1979 |

|

SU868769A1 |

| Цифровой многоточечный измерительный мост | 1980 |

|

SU938164A1 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1980 |

|

SU920722A1 |

| Частотно-импульсное дифференцирующее устройство | 1990 |

|

SU1751755A1 |

| Цифровой линеаризатор | 1982 |

|

SU1056453A1 |

| Устройство для возведения в степень | 1984 |

|

SU1282119A1 |

Изобретение относится к цифровой технике и позволяет упростить . устройство, что обеспечивает повьше- ние его надежности. Измеритель содержит блок 1 управления, двоичньй умножитель 2, состоящий из реверсивного счетчика 3, блока 4 элементов совпадения и счетчика 5 импульсов, блок 6 сложения - вычитания, делитель 7 частоты, первый 8 и второй 9 входы, информационный 10 и знаковый 11 выходы. Результат измерений, выполняемых предлбженным устройством, прямо пропорционален коэффициенту деления К делителя 7 частоты, поэтому при том же масштабе результата измерения появляется возможность уменьшить разрядность блоков 3-5 двоичного умножителя 2 и, следовательно, сократит-ь число схемных элементов устройства. При этом разрядность двоичного умно- жителя 2 будет равна разрядности -кода максимального отклонения, частоты, а суммарная разность двоичного умножителя 2 и делителя 7 частоты будет равна разности кода максимального значения измеряемой частоты. 1 ил. (Л

25

разрядности кода максимального откло- jg частоты, вход которого соединен с нения частоты, а суммарная разрядность двоичного умножителя 2 и делителя частоты 7 равна разрядности кода максимального значения измеряемой частоты.

Формула изобрете ни я

Цифровой измеритель отклонения частоты от номинальной, содержащий бло к управления, блок сложения - вычитания и двоичный умножитель, состоящий из блока элементов совпадения, первые-входы которого соединены . соответственно с выходами реверсивО и

30

выходом блока элементов совпадения а выход - с вторым информационным входом блока сложения - вычитания, третий и четвертый выходы блока управления соединены соответственн с входами направления счета реверсивного счетчика, а.первьй выход б ка управления является знаковым-вы ход ом измерителя, причем разраядно двоичного умножителя равна разрядности кода.максимального отклонени частоты, а суммарная разрядность д ичного умножителя и делителя часто равна разрядности кода максимально значения-частоты.

частоты, вход которого соединен с

выходом блока элементов совпадения, а выход - с вторым информационным входом блока сложения - вычитания, третий и четвертый выходы блока управления соединены соответственно с входами направления счета реверсивного счетчика, а.первьй выход блока управления является знаковым-выход ом измерителя, причем разраядность двоичного умножителя равна разрядности кода.максимального отклонения частоты, а суммарная разрядность двоичного умножителя и делителя частоты равна разрядности кода максимального значения-частоты.

| Устройство для измерения отклонений частоты от номинального значения | 1978 |

|

SU783702A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой измеритель отклонения измеряемой частоты от номинальной | 1976 |

|

SU748270A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-01-15—Публикация

1986-02-25—Подача