(54) ЦИФРОВОЙ ЛИНЕЙНЫЙ ЭКСТРАПОЛЯТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой линейный экстраполятор | 1975 |

|

SU628502A1 |

| Цифровое экстраполирующее устройство | 1983 |

|

SU1091171A1 |

| Экстраполятор видеосигнала изображения | 1989 |

|

SU1718246A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU1099317A1 |

| Двухотсчетный преобразователь синусно-косинусно-модулированных сигналов переменного тока в код | 1985 |

|

SU1283969A1 |

| БОРТОВАЯ СТАНЦИЯ ОПРЕДЕЛЕНИЯ КООРДИНАТ ДВИЖУЩИХСЯ ИСТОЧНИКОВ ИЗЛУЧЕНИЯ | 1989 |

|

SU1841039A1 |

| Следящий умножитель частоты | 1979 |

|

SU832556A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1986 |

|

SU1406528A1 |

| Линейный экстраполятор периода следования импульсов | 1978 |

|

SU943773A1 |

| Преобразователь частоты в код | 1978 |

|

SU744974A1 |

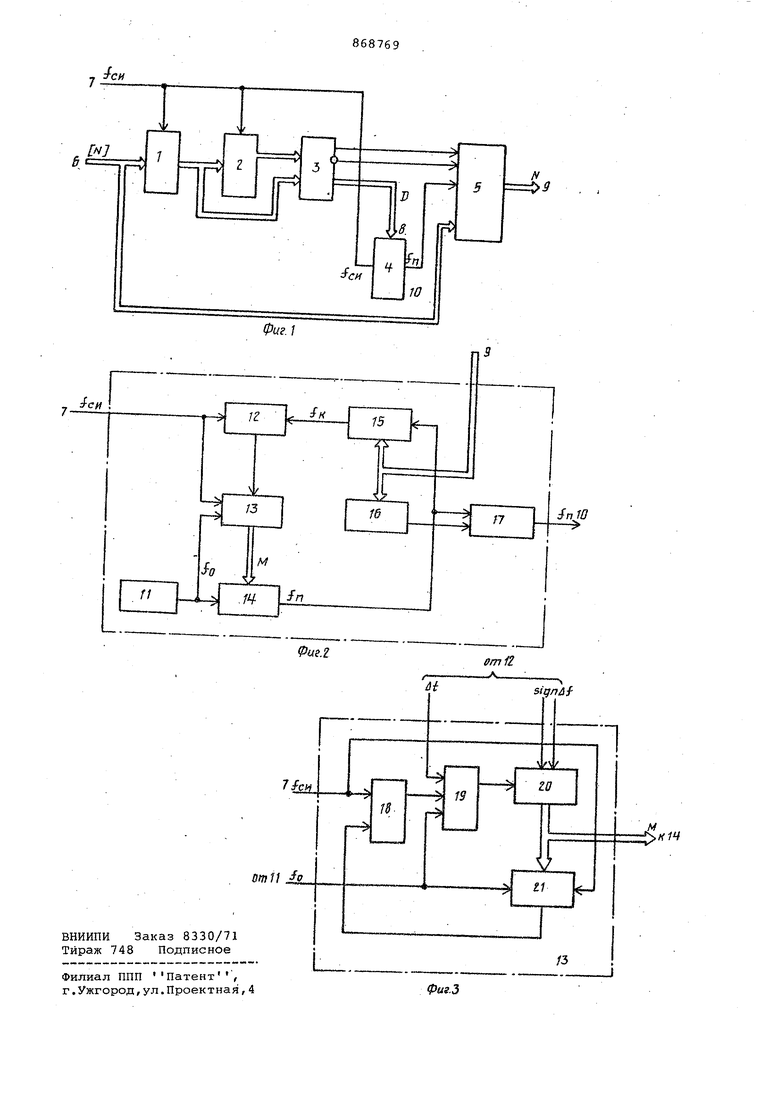

Изобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых специализированных вычислительных устройствах для вычисления значений дискретной (по времени) функции, заданной в виде ко дов в последовательные моменты времени. Известен цифровой линейный экстраполятор, содержащий первый и второй регистры, преобразователь код-частота и реверсивный счетчик ГШ Недостатком такого устройства является низкая точность, вычисления вы ходных значений кода в промежутках между моментами поступления входных значений. Наиболее близким к предлагаемому является цифровой линейный экстраполятор, содержащий первый и второй регистры, преобразователь код-частота, блок определения разности и реверсив ный счетчик 2. Недостатком известного устройства является ограниченная область применения. В частности, при поступлении входных кодов через неравноотносящие .моменты времени (когда частота синхроимпульсов, сопровождающих коды, переменна) экстраполятор не может работать из-за значительных погрешностей экстраполяции. Цель изобретения - расширение области применения за счет возможности линейной экстраполяции при переменной частоте следования синхроимпульсов входных кодов. Поставленная цель достигается тем, что в цифровой линейный экстраполятор, содержащий первый и второй регистры, блок определения разности и реверсивный счетчик, группа входов которого соединена с группой входов первого регистра и является группой кодовых входов экстраполятора, выходом которого является группа выходов реверсивного счетчика, входы сложения и вычитания которого соединены с прямым и инверсным выходами знакового разряда блока определения разности соответственно, первая и вторая группы входов блока определения разности соединены соответственно с группами разрядных выходов первого и второго регистров, группа разрядных выходов первого регистра соединена с группой входов «второго регистра, управляющие входы первого и второго регистров соединены с входом синхроимпульсов зкстраполятора, введен управляемый умножитель частоты импульсов, тактовый вход которого соединен с входом синхроимпульсов экстраполятора, группа информационных входов соединена с группой ,выходов блока определения разности, а выход соединен с импульсным входом реверсивного счетчика. Управляемый умножитель частоты импульсов содержит генератор импульсов опорной частоты, схему сравнения блок управления, первый и второй управляемые делители частоты, дешифратор и элемент И, выход которого явля ется выходом умножителя, первые вход схемы сравнения и блока управления соединены с тактовым входом умножите ля , группа входов первого управляемо го делителя частоты и группа входов дешифратора соединены с группой информационных входов умножителя, выход дешифратора соединен С №ервым -в5с дом элемента И, второй вход которого соединен с импульсным входом первого и выходом второго управляемых делите лей частоты, импульсный вход и групп входов второго управляемого делителя частоты соединены с выходом генератора импульсов опорной частоты и группой выходов блока управления соответственно, второй и третий входы блока управления соединены с выходом генератора импульсов опорной частоты и схемы сравнения соответственно,вто рой вход схемы сравнения соединен с выходом первого управляемого делителя частоты, , Блок управления содержит триггер, элемент И и два счетчика, причем Первый вход триггера соединен с управляющим входом первого счетчика и с первым входом блока, второй вход триггера соединен с выходом первого счетчика, выход триггера соединен с первым входом элемента И, выход кото рого соединен со счетным входом второго счетчика, группа выходов которо го является группой выходов блока, второй вход элемента И соединел со счетным входом первого счетчика и со вторым входом блока, третий вход эле мента И соединен с управляющим входом второго счетчика и с третьим вхо дом блока. На фиг. 1 представлен предлагаемый экстраполятор, структурная схема; на фиг. 2 - блок-схема управляемогб умножителя частоты импульсовjна фиг. 3 - блок управления, структурiна$ схема. Цифровой линейный экстраполятор, содержит первый и второй регистры 1 и, 2, блок 3 определения разности, управляемый умножитель 4 частоты импульсов и реверсивный счетчик 5,входы ,6-8 и выходы 9 и 10. Управляемый умножитель 4 частоты импульсов содержит генератор 11 импульсов опорной частоты, схему 12 равнения, блок 13 управления, управяемые делители 14 и 15 частоты, деифратор 16 и элемент И 17. Блок 13 управления содержит тригер 18, элемент И 19 и счетчики 20 21. . Блок 3 определения разности предазначен для вычисления приращения ходного кода и знака разности. Управляемый умножитель 4 частоты мпульсов предназ-начен для формироваия повышенной частоты следования мпульсов. Реверсивный счетчик 5 предназначен для формирования экстраполированного выходного кода. Цифровой линейный экстраполятор работает следующим образом. При поступлении сигнала синхронизации и входного кода значение пос- леднего записывается в первый регистр 1 и реверсивный счетчик 5. Во второй регистр 2 переписывается предыдущее значение входного кода из первого регистра 1. Одновременно сигнал синхронизации поступает на импульсный вход управляемого умножителя 4 частоты импульсов. Блок 3 определения разности вычисляет приращение входного кода, которое поступает на управляющий выход 9 умножителя 4 частоты, определяя требуемый коэфс идиент умножения. На выходе 10 умножителя формируется последовательность импульсов,, равномерно распределенных в течение интервала времени дг tj-t между соседними кодами, число которых равно приращению входного кода. Если приращение входного кода больше (меньше) нуля, то выходным сигналом знакового разряда блока 3 определения разности при поступлении очередного значения входного кода реверсивный счетчик 5 устанавливается в режим вычитания (сложения). При этом каждый импульс, поступсшзщий на вход реверсивного счетчика 3, уменьшает (увеличивает) его содержание на единицу. Таким образом, в течение интервала экстраполяции ui выходной код в экстраполяторе изменяется по линейному закону, т.е. осуществляетсй линейная экстраполяция. Управляемый делитель 4 частоты импульсов работает следующим образом. , Частота импульсов синхронизации умножается на число, .пропорциональное коду разности, таким образом, что на выходе 10 формируются импульсы повышенной частоты, равномерно расположенные в интервалах экстраполяции. Умножитель 4 частоты реализован как частотно-импульсная следящая система (с отрицательной обратной связью по частоте). Контур отрицательной обратной связи по частоте замыкается через управляемый делитель 15 частоты,коэффициент деления которого определяется кодом разности. Такцм образом, код разности упра ляет по цепи отрицательной обратной связи коэффициентом умножения умножи теля 4 частоты. С целью блокировки минимально возможных частот на выходе умножите ля 4 частоты используется логический элемент И 17, управляемый дешифрато ром 16. Дешифратор 16 определяет нулевой порог частоты (зону нечувстви тельности). При этом частота fg является стабильной высокой частотой генератора 11 импульсов. Блок 13 управления является регулятором частоты посредством кода управления коэффициента деления управляемого делителя 14 частоты. Умно житель 4 частоты импульсов, являющийся замкнутой частотно-импульсной следящей системой с управляемым коэф фициентом умножения, обладает опреде ленной инерционностью (постоянной вр мени), позволяющей сгладить скачки кода разности между интервалами экст раполяции. Он имеет хорошую помехоза щищенность (достаточный коэффициент сглаживания флюктуации) и требуемые динамические характеристики, позволяющие использовать его в качестве основного элемента цифрового линейно го экстраполятора. В предлагаемом цифровом линейном экстраполяторе отсутствует пульсация выходного кода и сбои реверсивного счетчика 5 зл счет одновременного поступления на его суммирующий и вычитающий входы импульсов (так как последнее исключено блоком 3 определения разности). Формула изобретения 1. Цифровой линейный экстраполятор, содержащий первый и второй регистры, блок определения разности и реверсивный счетчик, группа входов которого соединена с группой входов первого регистра и является группой кодовых входов экстраполя-тора, выходом которого является группа выходов -реверсивного счетчика, входы сложения и вычитания которого соединены с прямым и инверсным выходами знакового разряда блока определения разности соответственно, первая и вторая группы входов блока определения разности соединены соответственно с группами разрядных выходов первого и второго регистров, группа разрядных выходов первого регистра соединена с группой входов второго регистра,уп равляющие входы первого и второго регистров соединены с входом синхроимпульсов экстраполятора, о т л и чающи йся тем, что, с целью расширения области применения, он содержит управляемый умножитель частоты импульсов,тактовый вхОд которого соединен с входом синхроимпульсов экстраполятора, группа информационных входов соединена с группой выходов блока определения разности, а выход соединен с импульсным входом реверсивного счетчика. 2.Экстраполятор по п. 1, о т личающийся тем, что управляемый умножитель частоты импульсов, содержит генератор импульсов опорной частоты, схему сравнения, блок управления, первый и второй управляемые делители частоты, дешифратор и элемент И, выход которого является выходом умножителя, первые входы схемы сравнения и блока управления соединены с тактовым входом умножителя, группа входов первого управляемого , делителя частоты и группа входов дешифратора соединена с группой информационных входов умножителя, выход дешифратора соединен с первым входом элемента И, второй вход которого соединен с импульсным входом первого и выходом второго управляемых делителей частоты, импульсный вход и группа входов второго управляемого делителя частоты соединены с выходом генератора импульсов опорной частоты и группой выходов блока управления соответственно, второй и -третий входы блока управления соединены с выходом генератора импульсов опорной часто|ты и схемы сравнения соответственно, второй вход схемы сравнения соединен с выходом первого управляемого делителя частоты. 3.Экстраполятор по пп. 1 и 2, отличашщийся тем, что блок управления содержит триггер элемент И и два счетчика, причем первый вход триггера соединен с управляющим входом первого счетчика и с первым входом блока, второй вход триггера соединен с выходом первого счетчика, выход триггера соединен с первым входом элемента И, выход которого соединен со счетным входом второго счетчика, группа выходов которого является группой выходов блока, BTOpoJt вход элемента И соединен со счетным входом первого счетчика и со вторым входом блока, третий вход элемента И соединен с управляющим входом второго счетчика и с третьим входом блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 486321, кл. G Об J 1/02, G Об F 15/34, 1974. 2.Авторское свидетельство СССР № 628502, кл. G 06 J 1/02, G 0€ F 15/34, 1975 (прототип).

Авторы

Даты

1981-09-30—Публикация

1979-10-11—Подача