(Sk) УСТРОЙСТВО ДЛЯ ДИФФЕРЕНЦИРОВАНИЯ ЧАСТОТНО-ИМПУЛЬСНЫХ СИГНАЛОВ

1

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам дифференцирования частотно-импульсных си1- налов по невременному аргументу.

Известно частотно-импульсное дифференцирующее устройство, содержащее реверсивные счетчики, двоичные умножители, коммутаторы, триггеры-, дифференцирующий блок и частотноимпульсный множительный блок til.

Известно также частотно-импульсное дифференцирующее устройство, содержащее реверсивные счетчики, двоичные умножители, дифференцирующий блок и блок определения знака 12.

Общим недостатком этих т;тройств осуществляющих дифференцирование по невременному аргументу, является пониженная точность дифференцирования .

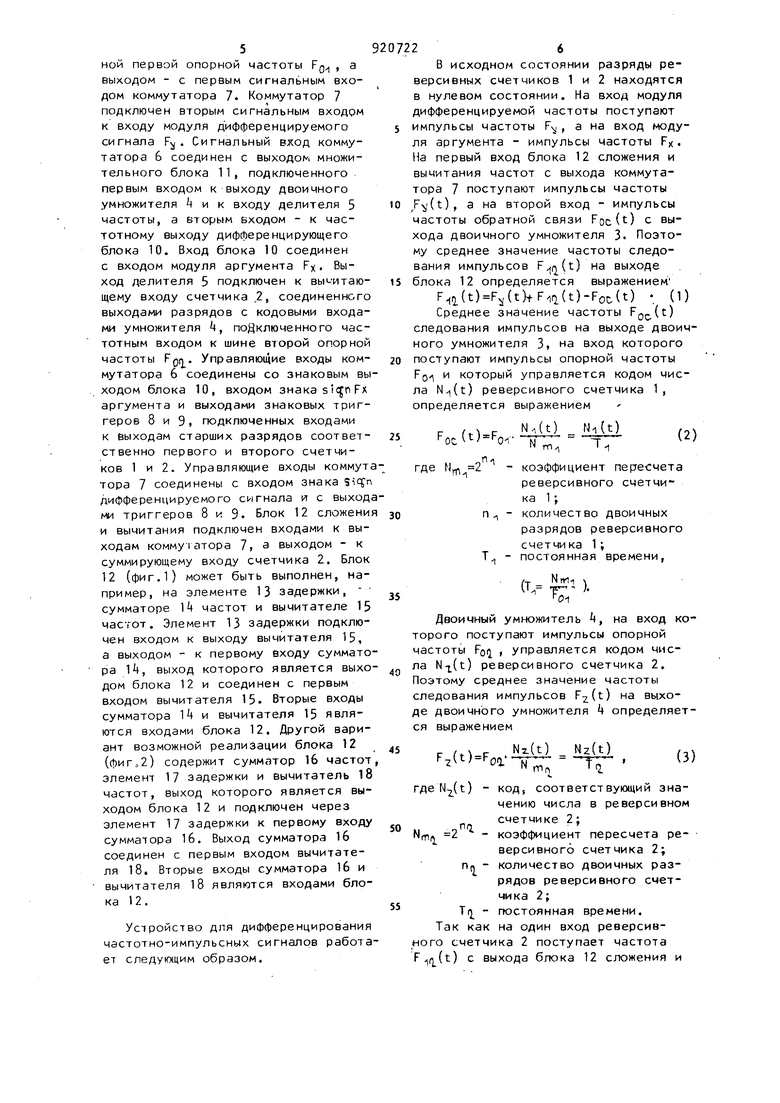

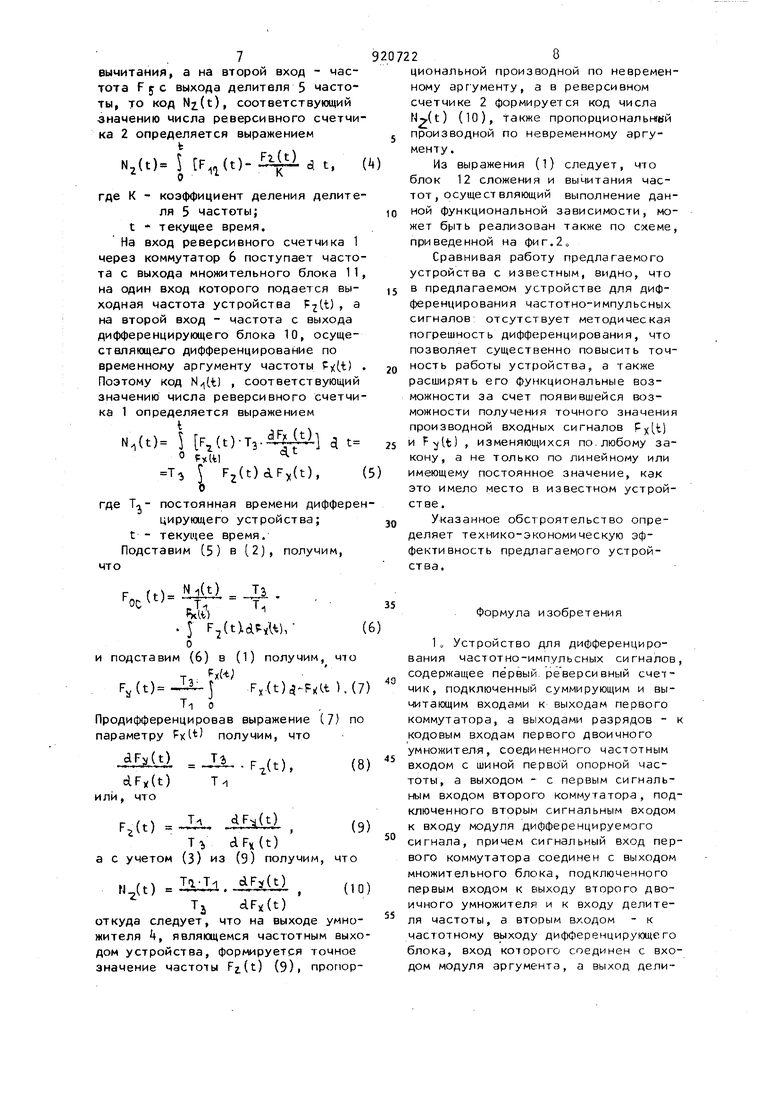

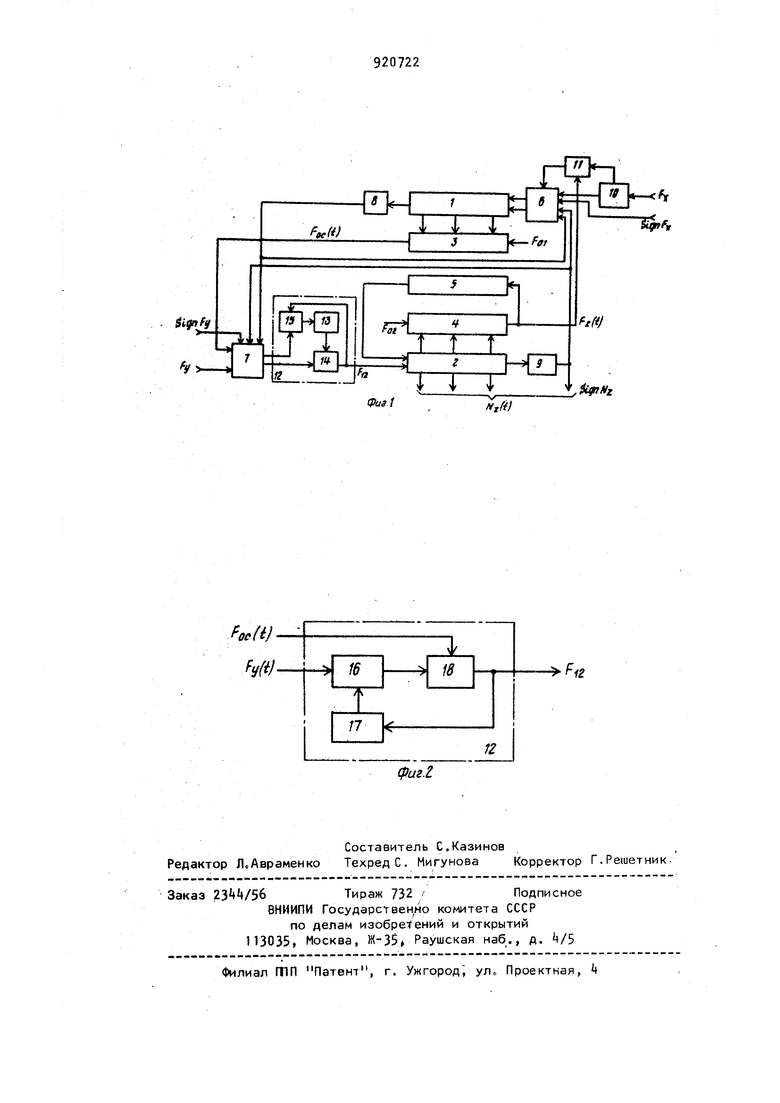

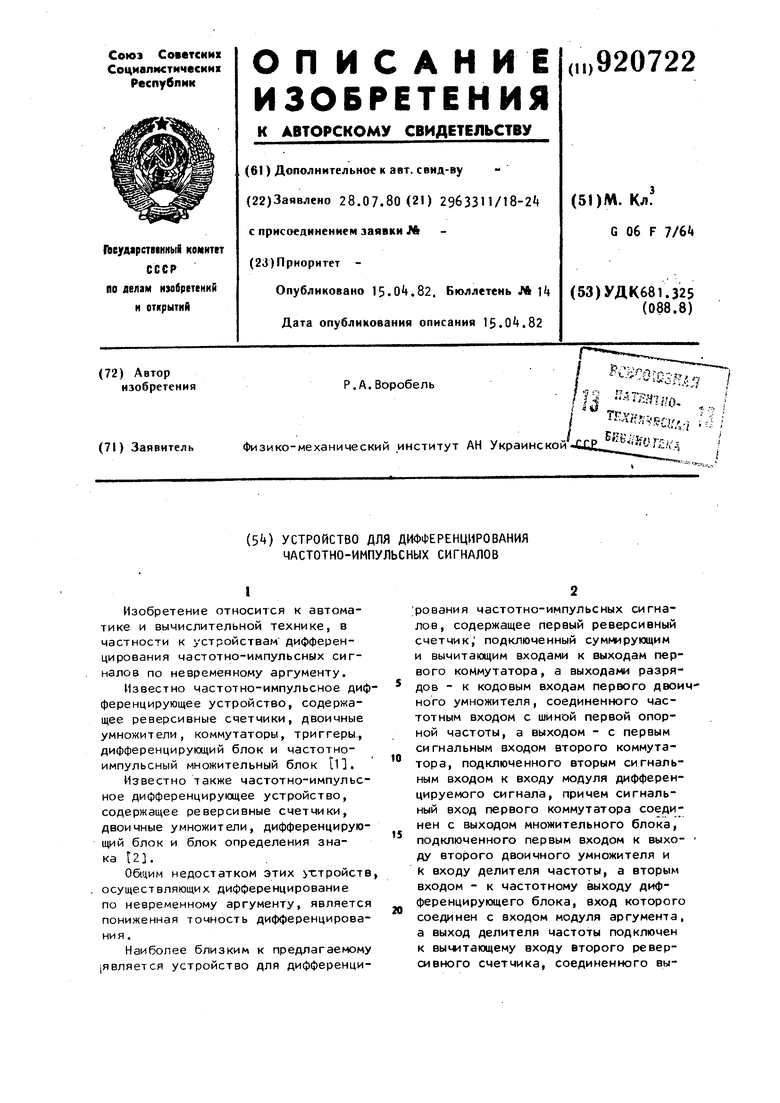

Наиболее близким к предлагаемому является устройство для дифференцирования частотно-импульсных сигналов, содержащее первый реверсивный счетчик, подключенный суммирующим и вычитающим входами к выходам первого коммутатора, а выходами разрядов - к кодовым входам первого двоичного умножителя, соединенного частотным входом с шиной первой опорной частоты, а выходом - с первым сигнальным входом второго коммутатора, подключенного вторым сигнальным входом к входу модуля дифференцируемого сигнала, причем сигнальный вход первого коммутатора соединен с выходом множительного блока, подключенного первым входом к выхо- ду второго двоичного умножителя и k входу делителя частоты, а вторым входом - к частотному выходу дифференцирующего блока, вход которого соединен с входом модуля аргумента, а выход делителя частоты подключен к вычитающему входу второго реверсивного счетчика, соединенного выходами разрядов с кодовыми входами второго двоичного умножителя, подключенного частотным входом к шине второй опорной частоты, причем управляющие входы первого коммутатора соединены со знаковым выходом дифференцирующего блока, входом знака аргумента и выходами первого и второго знаковых приггеров, подключенных входами к выходам старших разрядов соответственно первого ивторого реверсивных счетчиков, а управляющие входы второго коммутатора соединены с входом знака дифференцируемого сигнала и с выходами первого и второго знаковых триггеров, причем выходы второго коммутат ра подключены к входам блока вычита ния, соединенного выходом с суммирующим входом второго реверсивного счетчика 3. Недостаток устройства - пониженная точность дифференцирования по невременному аргументу. Целью и.зобретения является повышение точности дифференцирования по невременному аргументу. С этой целью в устройство для дифференцирования частотно-импульсных сигналов, содержащее первый ре.версивный счетчик, подключенный сум мирующим и вычитающим входами к выходам первого коммутатора, а выхода ми разрядов - к кодовым входам первого двоичного умножителя, соединен ного частотным входом с шиной перво опорной частоты, а выходом с первым сигнальным входом второго комму татора, подключенного вторым сигнал ным входом к входу модуля дифференцируемого .СИ гнала , причем сигнальный вход первого коммутатора соединен с выходом множительного блока, подключенного первым входом к выход второго двоичного умножителя и к входу делителя частоты, а вторым входом - к частотному выходу дифференцирующего блока, вход которого соединен с входом модуля аргумента, а выход делителя частоты подключен к вычитающему входу второго реверсивного счетчика, соединенного выходами разрядов с кодовыми входами второго двоичного умножителя, подключенного частотным входом к шине второй опорной частоты, примем упра ляющие входы первого коммутатора соединены со .знаковым выходом дифференцирующего блока, входом знака аргумента и выходами первого и второго знаковых триггеров, подключенных входами к выходам старших разрядов соответственно первого и второго реверсивных счетчиков, а управляющие входы второго коммутатора соединены с входом знака дифференцируемого сигнала и с выходами первого и второго знаковых триггеров, введен блок сложения и вычитания частот, подключенный входами к выходам второго коммутатора, а выходом - к суммирующему входу второго реверсивного счетчика. Блок сложения и вычитания частот может выполнен, содержащим сумматор частот, вычитатель частот и элемент задержки, подключенный входом к выходу вычитателя частот, а выходом - к первому входу сумматора частот, выход которого является выходом блока сложения и вычитания частот и соединен с первым входом вычитателя частот, а втог рые входы сумматора частот и вычитателя частот являются входами блока сложения и вычитания частот. Кроме этого блок сложения и вычитания частот может быть выполнен. содержащим сумматор частот, элемент задержки и вычитатель частот, выход которого является выходом блока сложения и вычитания частот и подключен через элемент задержки к первому входу сумматора частот, соединенного выходом с первым входом вычитателя частот, а вторые входы сумматора частот и вычитателя частот являются входами блока сложения и вычитания частот. На фиг.1 изображена блок-схема устройства; на фиг.2 - вариант выполнения блока сложения и вычитания частот. Устройство для дифференцирования частотно-импульсных сигналов (фиг.1) содержит первый и второй реверсивные счетчики 1 и 2, первый и второй двоичные умножители 3 и , делитель 5 частоты, первый и второй коммутаторы 6 и 7, первый и второй знаковые триггеры 8 и 9, дифференцирующий блок 10, множительный блок 11 и блок 12 сложения и вычитания. Счетчик 1 подключен cyммиpyюu им и вычитающим входами к выходам коммутатора 6, а выходами разрядов к кодовым входам двоичного умножителя 3, соединенного частотным входом с шиной первой опорной частоты FQ , а выходом - с первым сигнальным входом коммутатора 7. Коммутатор 7 подключен вторым сигнальным входом к входу модуля дифференцируемого сигнала F( . Сигнальный вход коммутатора 6 соединен с выходом множительного блока 11, подключенного первым входом к выходу двоичного умножителя 4 и к входу делителя 5 частоты, а вторым входом - к частотному выходу дифференцирующего блока 10. Вход блока 10 соединен с входом модуля аргумента FX. Выход делителя 5 подключен к вы-итающему входу счетчика .2, соединенного выходами разрядов с кодовыми входами умножителя 4, подключенного частотным входом к шине второй опорной частоты FQQ. Управляющиб входы коммутатора 6 соединены со знаковым выходом блока 10, входом знака sicjnFx аргумента и выходами знаковых триггеров 8 и 9, подключенных входами к выходам старших разрядов COOTBBIственно первого и второго счетчиков 1 и 2. Управляющие входы коммутатора 7 соединены с входом знака Sicfn дифференцируемого сигнала и с выходми триггеров 8 и 9. Блок 12 сложени и вычитания подключен входами к выходам коммутатора 7, а выходом - к суммирующему входу счетчика 2. Блок 12 (фиг,1) может быть выполнен, например, на элементе 13 задержки, сумматоре 1 частот и вычитателе 15 частот. Элемент 13 задержки подключен входом к выходу вычитателя 15, а выходом - к первому входу сумматора 1А, выход которого является выходом блока 12 и соединен с первым входом вычитателя 15. Вторые входы сумматора и вычитателя 15 являются входами блока 12. Другой вариант возможной реализации блока 12 (фиго2) содержит сумматор 16 частот элемент 17 задержки и вычитатель 18 частот, выход которого является выходом блока 12 и подключен через элемент 17 задержки к первому входу сумматора 16. Выход сумматора 16 соединен с первым входом вычитателя 18. Вторые входы сумматора 16 и вычитателя 18 являются входами блока 1 2 .

Устройство для дифференцирования частотно-импульсных сигналов работает следующим образом.

В исходном состоянии разряды реверсивных счетчиков 1 и 2 находятся в нулевом состоянии. На вход модуля дифференцируемой частоты поступают

5 импульсы частоты F, , а на вход модуля аргумента - импульсы частоты FX. На первый вход блока 12 сложения и вычитания частот с выхода коммутатора 7 поступают импульсы частоты

0 (t) , а на второй вход - импульсы частоты обратной связи Foc(t) с выхода двоичного умножителя 3. Поэтому среднее значение частоты следования импульсов (t) на выходе 5 блока 12 определяется выражением

F,(t)F.,,(t)f (t)-Fot(t) (1) Среднее значение частоты (t) следования импульсов на выходе двоичного умножителя 3, на вход которого 0 поступают импульсы опорной частоты FQ И который управляется кодом числа ) реверсивного счетчика 1, определяется выражением

N-.,(t) Ni(t)

(2) N гл, Т

1

где Н,„.2

коэффициент пересчета

ч реверсивного счетчика 1 ; л количество двоичных

разрядов реверсивного

счетчика 1 ;

Т. постоянная времени.

,Ntrl N

V -FT

Двоичный умножитель А, на вход которого поступают импульсы опорной частоты FOQ , управляется кодом числа ) реверсивного счетчика 2. Поэтому среднее значение частоты следования импульсов F2(t) на выходе двоичного умножителя Ц определяется выражением

. ц(

(3

m п 1 гдеГ(1) - код, соответствующий значению числа в реверсивном счетчике 2;

N

NmQ --i

коэффициент пересчета реверсивного счетчика 2; количество двоичных разПп рядов реверсивного счетчика 2;

Trj - постоянная времени. Так как на один вход реверсивного счетчика 2 поступает частота (t) с выхода блока 12 сложения и вычитания, а на второй вход - частота Fjc выхода делителя 5 частоты, то код N2.(t), соответствующий значению числа реверсивного счетчи ка 2 определяется выражением N,(t) S F,, (t)-MlI 4 t. О где К - коэффициент деления делите ля 5 частоты; t - текущее время. На вход реверсивного счетчика 1 через коммутатор 6 поступает часто та с выхода множительного блока 11 на один вход которого подается выходная частота устройства на второй вход - частота с выхода дифференцирующего блока 10, осуществляющего дифференцирование по временному аргументу частоты Pxtt) Поэтому код ) , соответствующий значению числа реверсивного счетчи ка 1 определяется выражением N,(t) F,(t)-T3. а t о РчШ 1 J F2(t)AFy(t), где Тт- постоянная времени диффере циpyюu eгo устройства; t - текущее время. Подставим (5) в (2), получим, г (t)-Mtl-Jj.. 00 Т-, Т. fxli) . J F.j(),И подставим (6) в (1) получим, что т, PxW F(t),.(t)).( Продифференцировав выражение (7) по параметру получим, что (t) ТЗ F(t), dFy(t)Т или, что г ГИ - Т (t) Г - V - / TV dFx(t) а с учетом (З) из (9) получим, что И (О 1ид.ЛМО, ) откуда следует, что на выходе умножителя k, являющемся частотным выхо дом устройства, фор руется точное значение частоты fi(t) (9), пропор28циональной производной по невременному аргументу, а в реверсивном счетчике 2 формируется код числа N2(t) (10), Также пропорциональкьй производной по невременному аргументу. Из выражения (1) следует, что блок 12 сложения и вычитания частот , осуществляющий выполнение данной функциональной зависимости, может бь1ть реализован также по схеме, приведенной на фиг.2„ Сравнивая работу предлагаемого устройства с известным, видно, что в предлагаемом устройстве для дифференцирования частотно-импульсных сигналов; отсутствует методическая погрешность дифференцирования, что позволяет существенно повысить точность работы устройства, а также расширять его функциональные возможности за счет появившейся возможности получения точного значения производной входных сигналов FxU) и ) , изменяющихся по. любому закону, а не только по линейному или имеющему постоянное значение, как это имело место в известном устройстве. Указанное обстроятельство определяет технико-экономическую эффективность предлагаемого устройства. Формула изобретения 1, Устройство для дифференцирования частотно-импульсных сигналов, содержащее первый, реверсивный счетчик, подключенный суммируюа(им и вычитающим входами к выходам первого коммутатора, а выходами разрядов - к кодовым входам первого двоичного умножител-я, соединенного частотным входом с шиной первой опорной частоты, а выходом - с первым сигнальным входом второго коммутатора, подключенного вторым сигнальным входом к входу модуля дифференцируемого сигнала, причем сигнальный вход первого коммутатора соединен с выходом множительного блока, подключенного первым входом к выходу второго двоичного умножителя и к входу делителя частоты, а вторым входом - к частотному выходу дифференцирующего блока, вход которого соединен с входом модуля аргумента, а выход делителя частоты подключен к вычитающему входу второго реверсивного счетчика, соединенного выходами разрядов с кодовыми входами второго двоичного умножителя, подключенного частотным входом к шине второй опорной частоты, причем управляющие входы первого коммутатора соединены со знаковым выходом дифференцирующего блока, входом знака аргумента и выходами первого и второго знаковых триггеров, подключенных входами к выходам старших разрядов соответственно первого и второго реверсивных счетчиков, а управляющие входы второго коммутатора соединены с входом знака дифференцируемого сигнала и с выходами первого и второго знаковых триггеров, отли чающееся тем, что, с целью повышения точности дифференцирования по невременному аргументу ,. в него введен блок сложения и вычитания частот, подключенный входами к выходам втогрого коммутатора, а выходом - к суммирующему входу второго реверсивного счетчика.

2. Устройство по п. 1, о т л и чающееся тем, что блок сложения и вычитания частот содержит сумматор частот, вычитатель частот и элемент задержки, подключенный входом к .выходу вычитателя частот,

а выходом - к первому входу сумматора частот, выход которого является выходом блока сложения и вычитания частот и соединен с первым входом вычитателя частот, а вторые входы сумматора частот и вычитателя частот являются входами блока сложения и вычитания частот.

3. Устройство по п. 1, о т л и чающееся тем, что блок сложения и вычитания частот содержит сумматор частот, элемент здДержки и вычитатель частот, выход которого является выходом блока сложения и

вычитания частот и подключен через элемент задержки к первому входу сумматора частот, соединенного выходом с первым входом вычитателя частот, а вторые входы сумматора

частот и вычитателя частот являются входами блока сложения и вычитания частот.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

№ , кл, G Об G 7/18, 1971.

2.Авторское свидетельство СССР № 639555, кл. G 06 G 7/18, 1977.

3.Никифоров М.Б., Поламарюк Г.О. Об изменении первой производной ча

тотно-импульсного сигнала. Автометрия, 1972, № 2, с. SI-S,рис.2-(орототип).

iignfy fy Физ1

Ht(i

| название | год | авторы | номер документа |

|---|---|---|---|

| ВСЕСОЮЗНАЯ | 1973 |

|

SU386403A1 |

| Частотно-импульсное дифференцирующее устройство | 1977 |

|

SU739555A1 |

| Частотно-импульсное дифференцирующее устройство | 1990 |

|

SU1751755A1 |

| Частотно-импульсное диференцирующее устройство | 1977 |

|

SU640315A1 |

| Частотно-импульсное дифференцирующее устройство | 1980 |

|

SU875400A1 |

| Устройство для дифферинцирования частотно-импульсных сигналов | 1975 |

|

SU526916A1 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1979 |

|

SU862150A1 |

| Инкроментный умножитель аналоговых сигналов | 1982 |

|

SU1057970A1 |

| Частотно-импульсный функциональный преобразователь | 1981 |

|

SU995095A1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ СКОРОСТИ ИЗМЕНЕНИЯ ТЕМПЕРАТУРЫ | 2012 |

|

RU2506548C1 |

Авторы

Даты

1982-04-15—Публикация

1980-07-28—Подача