ляции, вход управления и первый и второй выходы коммутатора соединены соответственно с первым входом управления и информационными выходами формирователя коэффициентов интерпрля ции.

3. Линеаризатор по п. 1 , о т - . л и ч а ю щ и и с я тем, что формирователь синхроимпульсов содержит последовательно соединенные формирователь коротких импульсов, элемент ИЛИ и элемент задержки вход формирователя коротких импульсов соединен с -первым, .а второй вход элемента ИЛИ. соединен с вторым входом формирователя синхроимпульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для кодирования сигналов частотных датчиков | 1985 |

|

SU1336246A1 |

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1988 |

|

SU1541663A1 |

| РАДИОИЗОТОПНЫЙ ТОЛЩИНОМЕР | 1992 |

|

RU2116620C1 |

| Функциональный преобразователь | 1981 |

|

SU960836A1 |

| Телевизионный координатор | 1983 |

|

SU1109956A1 |

| Цифровой следящий электропривод | 1985 |

|

SU1308982A1 |

| Спироанализатор | 1986 |

|

SU1391621A1 |

| УСТРОЙСТВО ДЛЯ ИНТЕРПОЛЯЦИИ | 1990 |

|

RU2042979C1 |

| Датчик углового положения и скорости вращения вала | 1985 |

|

SU1278718A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU960837A1 |

1 . ЦИФРОВОЙ ЯЙНЕАРИЗАТОР , содержащий последовательно соединенные частотный датчик и измеритель частоты, счетчик результата, информационные входы которого соединены с информационными выходами измерителя частоты, а также регистр перезапи- си, блок памяти констант, выходы управления измерителя частоты соединены соответственно с входом установки в О счетчика результата и с входом синхронизации регистра перезаписи, входы управления блока памяти констант соединены с выходами группы старших разрядов счетчика результата, отличающийся тем, что, с целью повышения точности и быстродействия, в него введены формирователь коэффициентов интерполяции, формирователь синхроимпульсов, реверсивный счетчик и сумматор кодов коррекции , первый выход и вторые выходы блока памяти констант соединены соответственно с первыми входами и группой входов управления формирователя коэффициентов интерполяции, третьи выходы блока памяти констант - с входами предустановки реверсивного счетчика, выходы которого поразрядно соединены с первыми входами сумматора кодов коррекции, вторые входы сумматора кодов коррекции поразрядно соединены с выходами счетчика результата; выходы знакового разряда и группы младших разрядов сиетчиков результата соединены соответственно с вторым входом управления и информационными входами формирователя коэффициентов интерполяции, а выход младшего из группы старших разрядов с первым входом формирователя синхроимпульсов, второй вход которого соединен с вторым выходом управления измерителя частоты, выход формирователя синхроимпульсов соединен с входом синхронизации реверсивного счетчика, шины сложения и вычитания ко(Л торого соединены с информационными выходами формирователя коэффициентов интерполяции; выходы сумматора кодов коррекции соединены - с D-входами регистра перезаписи, выходы которого соединены с выходами устройства. 2. Линеаризатор по п. 1, отел Од личающийся тем, что формирователь коэффициентов интерполяции 4 СП содержит последовательно соединенные блок формирователей коротких импульСО сов, мультиплексор и коммутатор, причем частотные входы блока формирователей коротких импульсов соединены с информационными входами формирователя коэффициентов интерполяции, входы управления формирователями коротких импульсов объединены и соединены с вторым входом управления формирователя коэффициентов интерполяции, входы управления мультиплексора соединены с группой входов управления формирователя коэффициентов интерпо

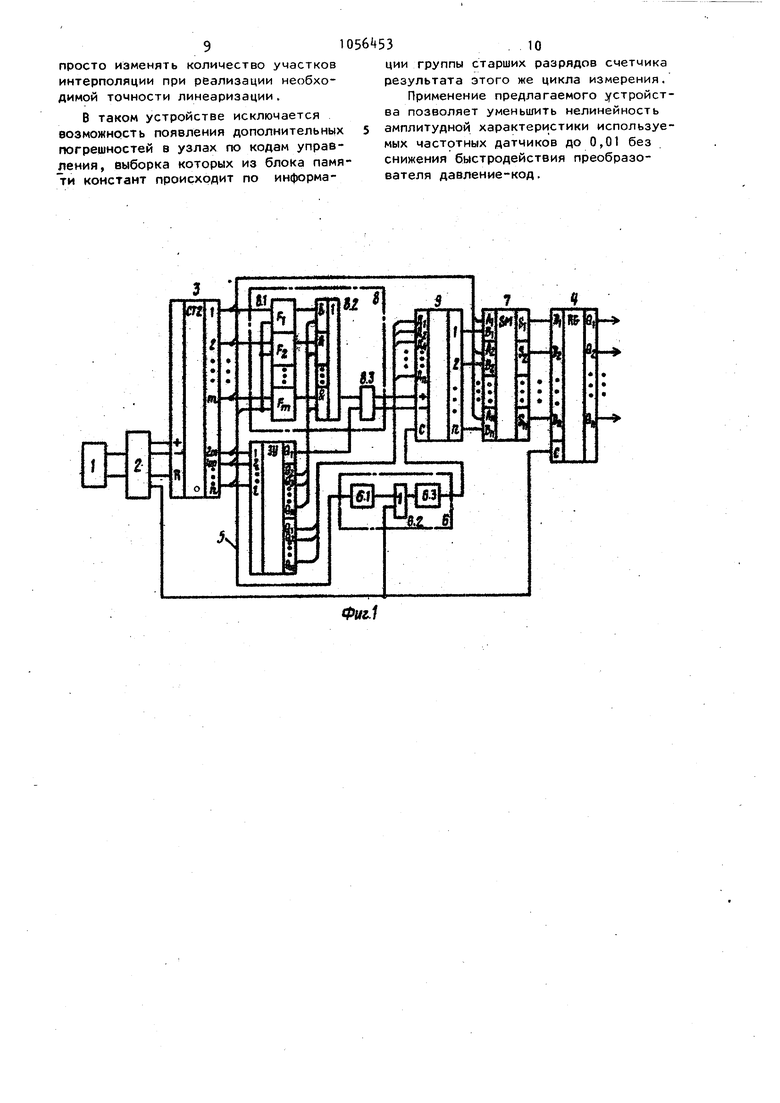

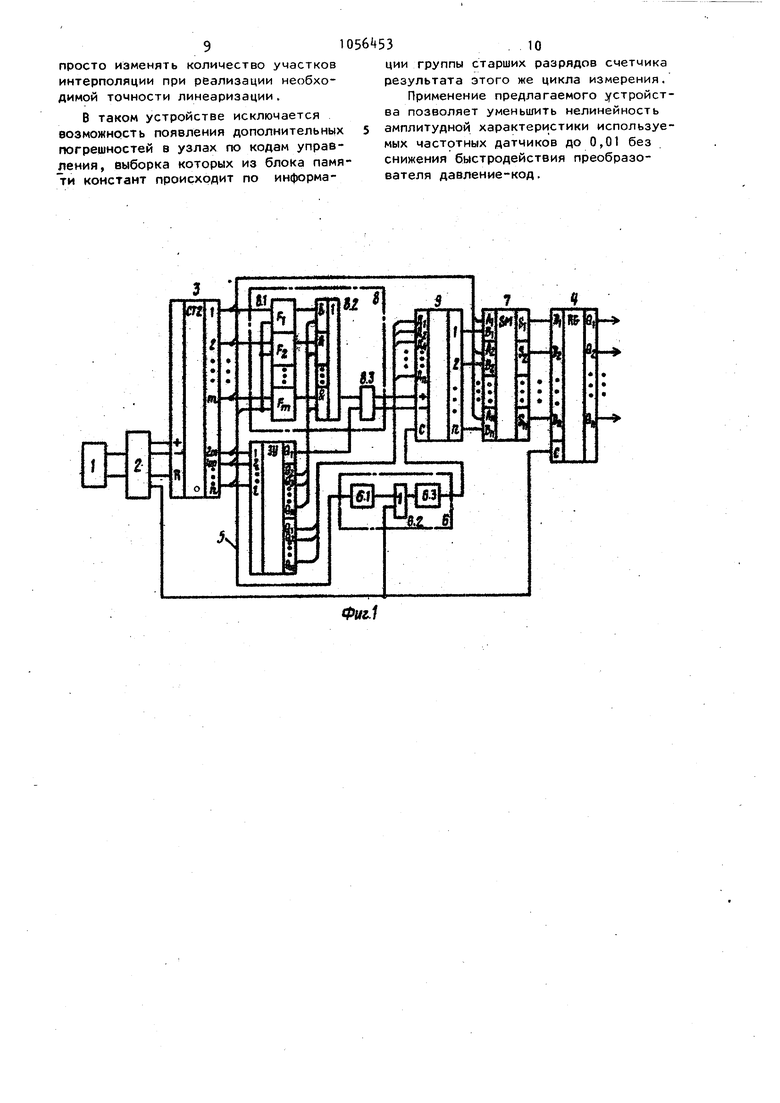

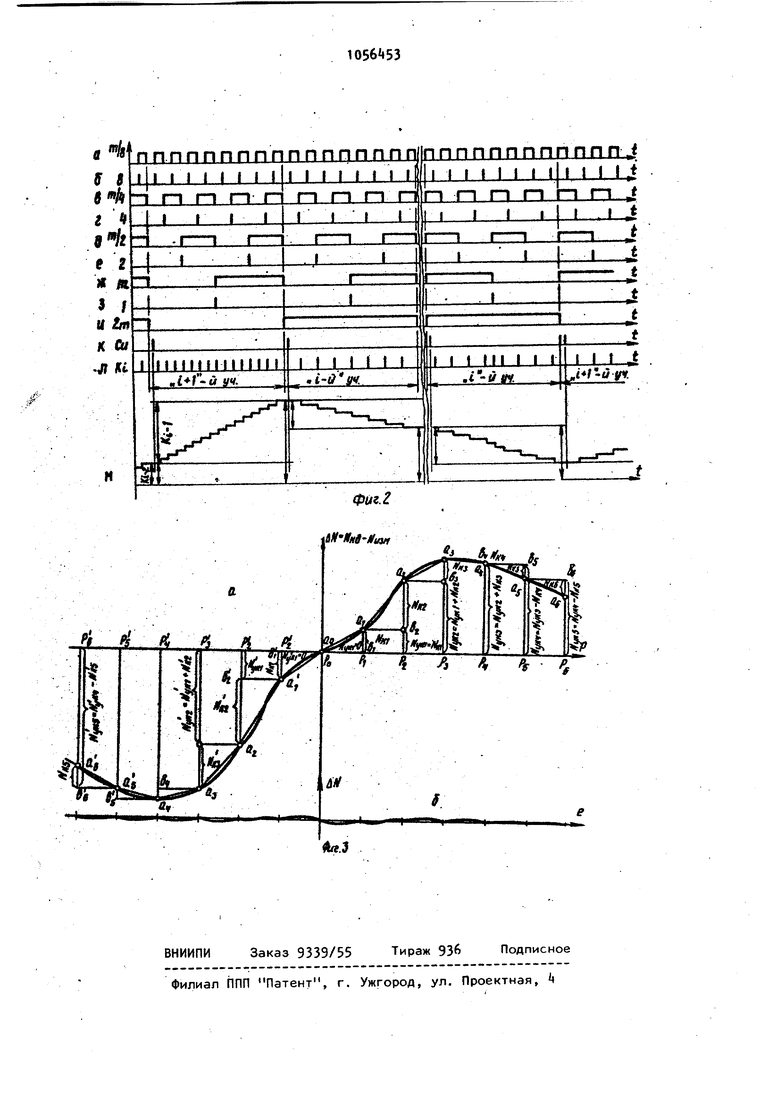

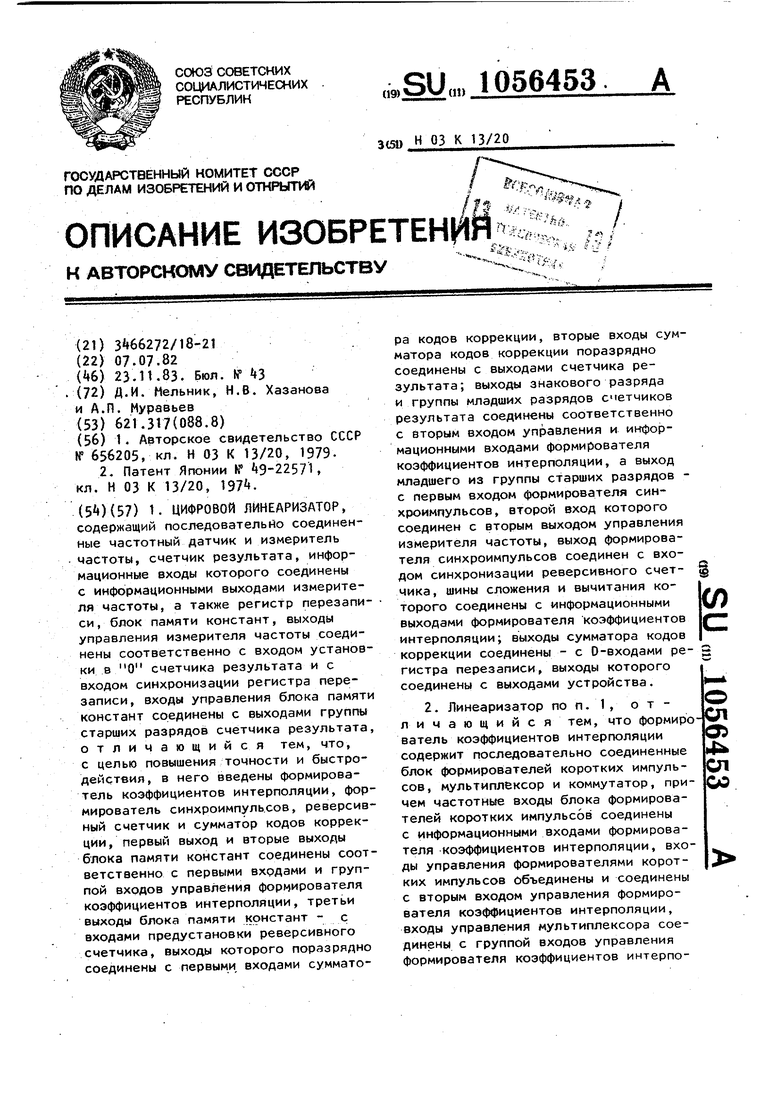

Изобретение относится к измерительной технике и предназначено для линеаризации частотных датчиков различных физических величин С кодовцм выходом. , .. л Известен цифровой линеаризатор, содержащий генератор, счетчик импульсов, цифровой компаратор, дешифратор участков интерполяции, улраеляемый делитель частоты, дополнитель ный счетчик и схему управления С13 Недостатком этого цифрового линеаризатора является низкое быстродействие. Наиболее близким к изобретению яв ляется цифровой линеаризатор сигнала содержащий последовательно соединенные частотный датчик, измеритель час тоты, управляющий делитель частоты, счетчик результата, информационные входы- которого соединены информационными выходами измерителя частоты а также регистр перезаписи, блок памяти констант, первый вход управления измерителя частоты соединен с соответствующим входом установки в нуль счетчика результата vi входом синхронизации регистра перезаписи, информационные входы которого поразрядно соединены с выходами счетчика результата, выходы старших разрядов счетчиков результата соединены с управляющими входами блока памяти констант, выходы которого соединены с входами управления делителем часто ты. В этом устройстве весь диапазон измерения разбивается на участки интерполяции. Для каждого такого участ ка заранее определяются и записываются в блок памяти значения констант, на которые необходимо изменять коэффициент деления делителя в тракте измеряемой (образцовой) частоты, чтобы выходной код счетчика результата, приходящийся на единицу измеряемого параметра, оставался примерно постоянным во всем интервале величин Таким образом, а известном устройстве запоминание узгкзвых точек интерполяции аппроксимирующей кривой осуществляется в виде определенных значений получаемого в счетчике результата кода (№ 1, N 2,...), а задание углов Наклонов интерполирующих прямых - в виде дискретных значений коэффициентов деления делителя, включенного в тракт следования импульсов измеряемой (образцовой) частоты С2 J, Однако В силу дискретности возможных значений коэффициентов деления в этом устройстве возникают неустранимые погрешности линеаризации, проявляющиеся больше всего в местах, где погрешность нелинейности наибольшая. Кроме того, недостатком известного устройства является присутствие положительной обратной связи, наличие которой при работе в однотактном режиме, вызывает дополнительные погрешности в точках излома аппроксимирующей ломаной. Целью изобретения является повышение точности и быстродействия цифровой линеаризации сложных функций. Указанная цель достигается тем, что в цифровой Линеаризатор, содержащий последовательно соединенные частотный датчик и измеритель частоты, счетчик результата, информационные входы которого соединены с информационными выходами измерителя частоты, а также блок памяти констант, регистр перезаписи, причем выходы управления измерителя частоты соединен соответственно с входом установки в О счетчика результата и с .входом синхронизации регистра перезаписи, входы управления блока памяти констант соединены с выходами группы старших разрядов счетчика результата введены формирователь коэффициентов интерполяции, формирователь синхроимпульсов, реверсивный счетчик и сумматор кодов коррекции, первый выход и вторые входы блока памяти констант соединены соответственно с первыми входами и группой входов управления формирователя коэффициентов интерполяции, третьи выходы блока памяти констант - с входами предуста новки реверсивного счетчика, выходы которого поразрядно соединены с первыми входами сумматора кодов коррекции, вторые входы сумматора кодов ко рекции поразрядно соединены с выхода ми счетчика результата; выходы знакового разряда и группы младших разрядов счетчика результата соединены соответственно с вторым входом управ ления и информационными входами фор мирователя коэффициентов интерполяции, а выход младшего из группы стар ших разрядов - с первым входом форм рователя синхроимпульсов, второй вход которого соединен с вторым выходом управления измерителя частоты выход формирователя синхроимпульсов соединен с входом синхронизации реверсивного сметчика, шины сложения и вычитания которого соединены с ин формационными выходами формировател коэффициентов интерполяции, выходы сумматора кодов коррекции соединены с О-входами регистра перезаписи, вы ходы которого соединены с выходами устройства. Кроме того, формирователь коэффи циентов интерполяции содержит последовательно соединенные блок формирователей коротких импульсов, мультиплексор и коммутатор, причем частотные входы блока формирователей коротких импульсов соединены с информационными входами формирователя коэффициентов интерполяции, входы управления формирователями коротких импульсов объединены и соединены с вторым входом управления формирователя .коэффициентов интерполяции, входы управления мультиплек сора соединены с группой входов управления формирователя коэффициентов интерполяции, вход управления и первый и второй выходы коммутатора соединены соответственно с первым входом управления и информационными выходами формирователя коэффициентов интерполяции. При этом формирователь синхроимпульсов содержит последовательно соединенные формирователь коротких импульсов, элемент ИЛИ и элемент задержки, вход-формирователя коротких импульсов соединен с первым, а второй вход элемента ИЛИ соединен с вторым входом формирователя синхроимпульсов. На фиг. 1 показана функциональная схема цифрового линеаризатора; на фиг. 2 - диаграммы напряжений, поясняющие работу устройства; на фиг. 3 диаграмма, поясняющая алгоритм формирования коэффициентов интерполяции. Устройство содержит последовательно соединенные частотный датчик 1 и измеритель 2 частоты, счетчик 3 результата, информационные входы которого соединены с.информационными выходами измерителя частоты, а также регистр 4 перезаписи, блок 5 памяти констант, первый и второй выходы управления измерителя частоты соединены соответственно с входом установки 8 О счетчика результата и с входом синхронизации регистра перезаписи, входы управления блоком памяти констант соединены с выходами группы старших разрядов счетчика результата, а также формирователь 6 синхроимпульсов, сумматор 7 кодов коррекции, формирователь 8 коэффициентов интерполяции, реверсивный счетчик 9 первый выход и вторые выходы блока памяти констант соединены соответственно с первыми входом и группой входов управления формирователя коэффициентов интерполяции, третьи выходы блока памяти констант - с входами предустановки реверсивного счетчика, выходы которого поразрядно соединены с первыми входами сумматора кодов коррекции, вторые входы сумматора кодов коррекции поразрядно соединены с выходами счетчика результата; выходы знакового разряда и группы младших разрядов счетчика результата соединены соответственно с вторым входом управления и информационными входами формирователя коэффициентов интерполяции, а выход младшего из группы старших разрядов - с первым входом формирователя синхроимпуль- сов, второй вход которого соединен с вторым выходом управления измерителя частоты, выход формирователя синхроимпульсов соединен с входом си хронизации реверсивного счетчики, ти ны сложения и вычитания которого сое динены с информационными выходами формирователя коэффициентов интерполяции, выходы сумматора кодов коррек ции, соединены с О-входами регистра перезаписи, выходы которого соединены с выходами устройства. Формирователь 6 синхроимпульсов содержит последовательно соединенные формирователь 6.1 коротких импульсов элемент ИЛИ 6.2, элемент 6.3 задержки. Формирователь 8 коэффициентов интерполяции содержит последовательно соединенные блок 8.1 формирователей коротких импульсов, мультиплексор 8.2 и коммутатор 8.3, примем частотные входы блока формирователей корот ких импульсов соединены с информационными входами формирователя коэффициентов интерполяции, входы управления формирователя коротких импульсов объединены и соединены с вто рым входом управления формирователя коэффициентов интерполяции,входы управления мультиплексора соединены с группой входов управления формирователя коэффициентов интерполяции вход управления и первый и второй выходы коммутатора соединены соответственно с первым входом управления и информационными выходами формирователя «оэффициентов интерполяции. Устройство работает следующим образом. Измеряемая (образцовая) частота, в общем случае нелинейно связанная с изменением физического параметра, с выхода измерителя 2 частоты поступает на вход счетчика 3 результата. На выходах счетчика 3 результата в конце каждого цикла измерения физического параметра формируются коды, содержащие нелинейность частотного датчика 1 и возможную нелинейность измерителя 2 частоты. Пусть в рассматриваемом случае применен дифференциальный частотный датчик 1 с измерителем 2 частот, общая нелинейность амплитудной характеристики которых приведена на. фиг. Зо, а счетчик 3 результата выгюлнен реверсивным. При поступлении мпульсов на шину сложения или вычи- : тания счетчика 3 результата, т.е. при измерении в одной или другой половинах диапазона изменения измеряеемого физического параметра, на вы-, ходе старшего п-го (знакового) разряда будет присутствовать соответственно логический О или логическая М« , ислользуеМ|)е для управления формирователями 8.t с целью формирования несовпадающих на временной оси последовательностей коротких импульсов (фиг.. 2,5,г, е, з). Для этого формирователи 8.1 коротких импульсов функционируют соответственно по переднему (фиг. 24-f-l,i участки) или заднему (фиг. ,1 участки) фронтам импульсов, снимаемых с выходов т,т/2,...... ,Ц,2,1 (фиг.З, д,в,01,...) счетчика 3 результата . После такого формирования отдельные последовательности, содержащие соответственно 1,2,4..... ,m/2,m (фиг. Зз,с,а.....) коротких импульсов, можно объединить в одну суммарную последовательность (фиг. З), содержащую от нуля до 2т-1 импульсов. Количество импульсов в суммарной последовательности для каждого участка интерполяции равно двоичному числу, формируеж)му б 5 памяти констанг для управления мультиплексором 8.2, а угли наклона формируемых прямых линий (фиг. аппроксимации могут принимать 2{п значений. По окончании предыдущего, например j-1-го цикла измерения, в регистре J перезаписи хранится код данного измерения, линейно связанный с изменением изм яемого параметра, а счетчик 3 результата устанавливается в нулевое состояние. Вследствие этого на выходах блока 5 памяти констант для первого участка интерполяции появляется логический уровень управления коммутатором 8.3, указывающий направляющие интерполяции (знак коэффициента интерполяции), код управления мультиплексором 8.2, указывающий величину коэффициента интерполяции -(угла наклона) и код узловой компенсации, учитывающий накопившуюся нелинейность. Код узловой компенсации для первого участка интерполяции импульсов, формируемым в измерителе 2 частот j переписывается в реверсивный счетчик 9. Этим заканчивается выставка начальных условий

для первого участка интерполяции очередного j-ro цикла измерения.

В течение j-ro цикла измерения импульсыизмеряемой (образцовой)Частоты поступают на шину сложения или вычитания счетчика 3 а импульсы суммарной последовательности с выхода формирователя 8 коэффициентов интерполяции - на.шину сложения или вычитания реверсивного счетчика 9. К концу первого участка интерполяции на вход реверсивного счетчика 9 поступит количество импульсов,, равное численному значению двоичного кода управления мультиплексором 8,2, формируемого блоком 5 памяти констант. Данное количество импульсов в течение первого участка интерполяции увеличивает (припоступлении их на шину сложения) или уменьшает (при поступлении импульсов на шину вычитания) код узловой компенсации, ранее переписанный в реверсивный счетчик 9 (по Ь-входам) из блока 5 памяти констант. При этом двоичные коды с выходов счетчика 3 результата и реверсивного счетчика 9 постуггают на входы параллельного сумматора 7 коррекции, на выходах.которого формируются текущие Значения двоичных кодов, связанных линейной зависимостью с изменением измеряемого параметра.

Это дает возможность воздействовать как на угол наклона амплитудной характеристики, так и на постоянную составляющую, другими словами, поворачивать амплитудную характеристику и смещать ее параллельно самой себе. При этом, разбив требуемую амплитудную характеристику на достаточное количество участков, можно для каждого узла интерполяции определить значения (фиг.-З ) кодов узловой компенсации и кодов N. коэффициентов интерполяции, при которых амплитудная характеристика предлагаемого линеаризатора будет проходить через нужные точки. Таким образом будет получено множество пар значений N и N,4 взаимно однозначное множеству участков.

По прохождении первого и последующих участков интерполяции, т.е. при изменении логических уровней на выходе (2т-го (фиг.2 и), младшего из группы разрядов счетчика 3 .результата, во-первых информация в группе (и,п/2,...... ,4т,2т) старших

разрядов принимает новые значения.

соответствующие второму и последующим участкам интерполяции, по которым на выходах блока 5 памяти констант формируются соответствующие данным

участкам (фиг. 3«) значения величины и знак коэффициентов интерполяции, а также коды Кук{ узловой компенсации, во-вторых, формирователь 6 синхроимпульсов, выдает (фиг.2 к. )

0 короткие импульсы, задержанные на время, необходимое для того, чтобы процесс формирования кодов на выходах блока 5 памяти констант завершился, по которым в реверсивный счетчик 9,

5 по О-входам записываются коды компенсации. Таким образом, коды , Ny, Ny,, УК 2 /узловой компенсации (фиг. 30) являются суммой предыдущих значений

0 кодов коэффициентов интерполяции и компенсируют нелинейность в точках aO,a1, а2,... и al,a2.. ) .узлах интерполяции.

Между узлами интерполяции, т.е. в

5 пределах участков, интерполяция производится прямыми линиями (aO-a1, a1-a2, а2-аЗ..., и , аМ-а2, а2-аЗ). В результате этого (фиг.З) характеристика нелинейности преобраQ зователя параметр - двоичный код из вида (фиг. 3ч) переходит к виду (фиг. 3 S}, т.е. уменьшается до величины разрешающей способности преобразователя.

По окончании поступления импульсов образцовой (измеряемой) частоты на вход счетчика 3 результата, т.е. после окончания j-ro цикла измерения импульсов с выхода измерителя 2 частот, информация с выходов сумматора 7 кодов коррекции переписывается в регистр Ц перезаписи.

Таким образом, введение в состав устройства формирователя коэффициентов интерполяции и использование для этой цели циклически изменяющихся младших разрядов счетчика результата позволяет существенно увеличить точность воспроизведения аппроксимирующей ломаной при незначительном усложнении блока памяти констант. Введение реверсивного счетчика с предустановкой и сумматора кодов коррекции позволяет увеличить быстродействие устройства, так как появляется возмож5 ность одновременно с измерением выполнять функции по линёаризаиии.

Введение формирователя синхроимпульсов дает возможность достаточно

91

просто изменять количество участков интерполяции при реализации необходимой точности линеаризации.

В таком устройстве исключается возможность появления дополнительных погрешностей в узлах по кодам управления, выборка которых из блока памя ти констант происходит по информаOSei+S}10

ции группы старших разрядов счетчика результата этого же цикла измерения.

Применение предлагаемого устройства позволяет уменьижть нелинейность 5 амплитудной характеристики используемых частотных датчиков до 0,01 без снижения быстродействия преобразователя давление-код. п п п п п п п п п п п п п п п

AHttni-gta п п(|п п п п п п п п п п п п ,

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой линеаризатор | 1976 |

|

SU656205A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-11-23—Публикация

1982-07-07—Подача