со з

О5

со

Изобретение относится к контрольно-измерительной технике и может быть использовано для обеспечения контроля интегральных микросхем.

Цель изобретения - повышение быстродействия контроля путем исключения повторного опроса группы нормально функционирующих зависимых входов.

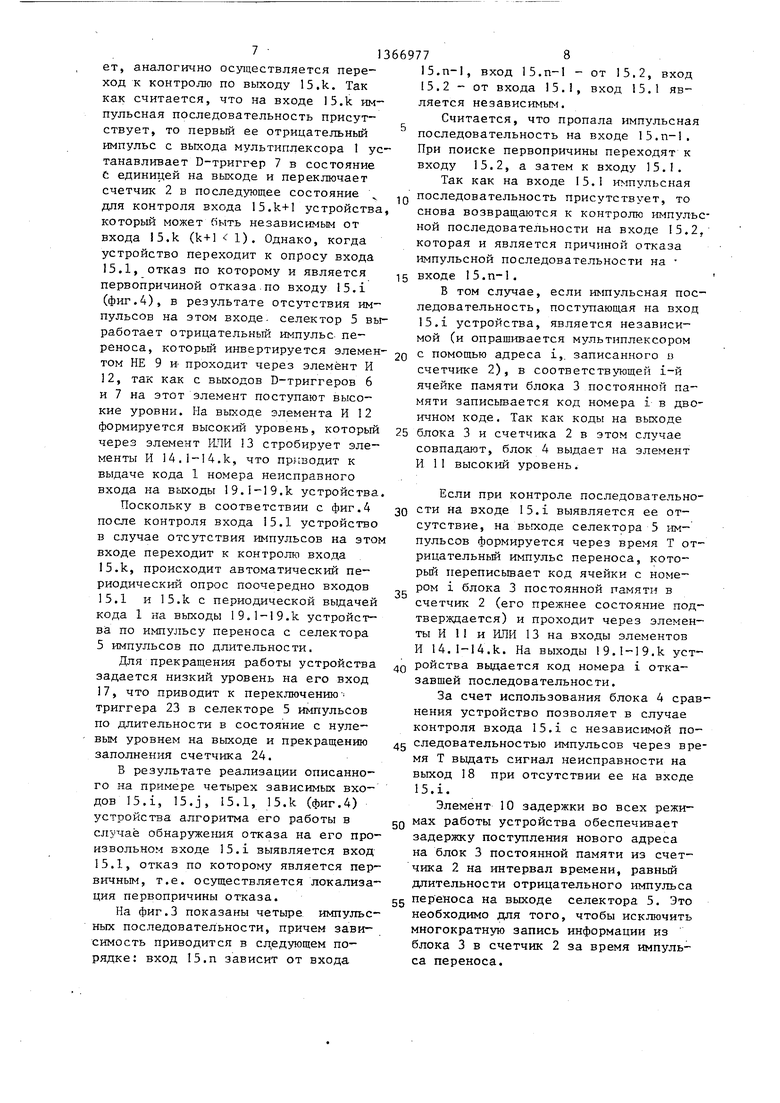

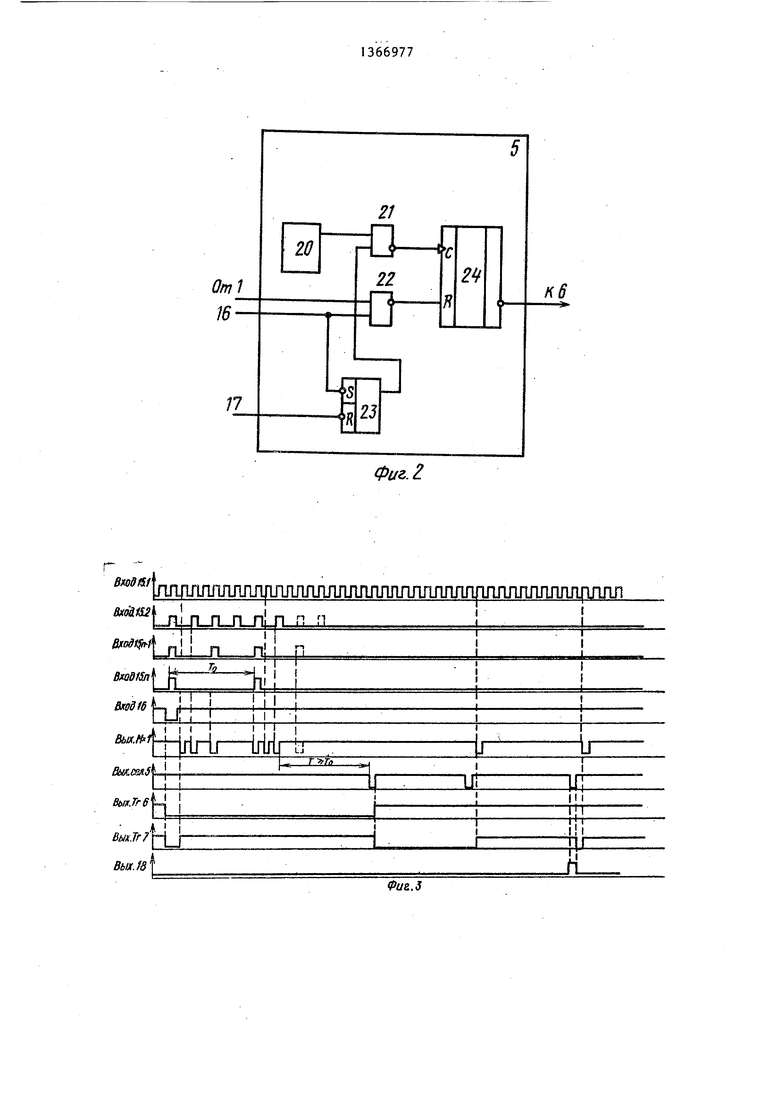

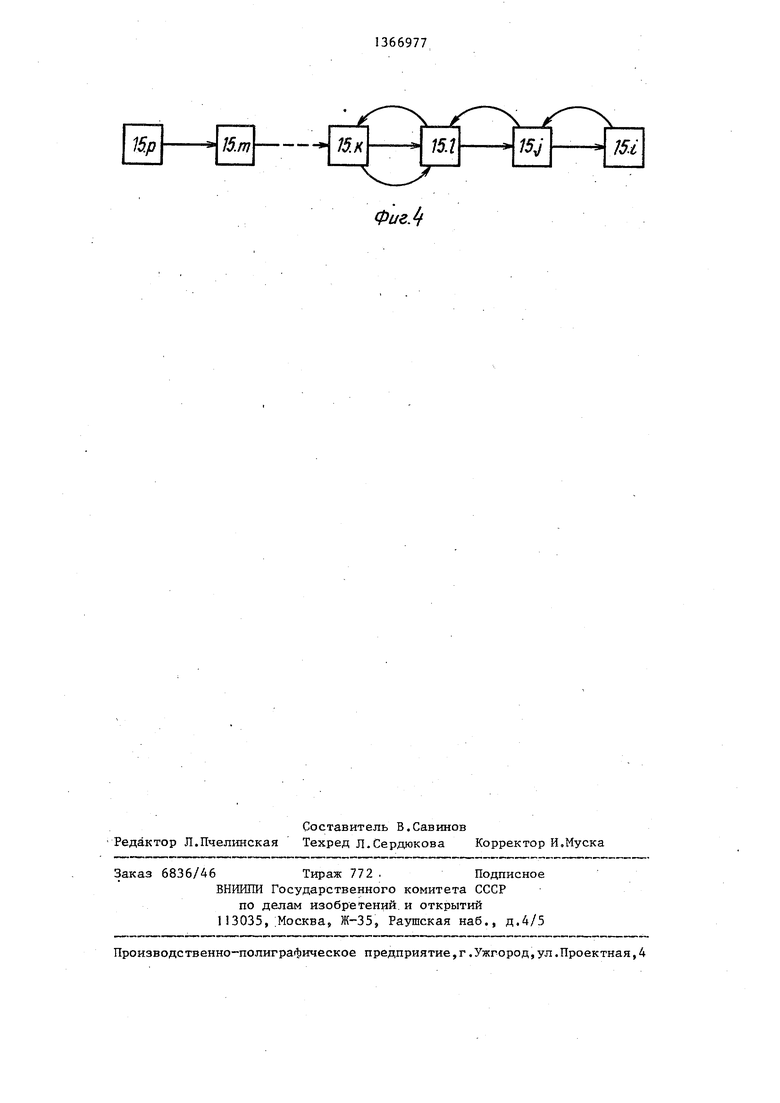

На фиг.1 приведена схема устройства; на фиг.2 - схема селектора импульсов по длительности; на фиг.З - временная диаграмма работы устройства; на фиг.4 - алгоритм поиска неисправности.

Устройство содержит мультиплексор 1, счетчик 2, блок 3 постоянной памяти, блок 4 сравнения, селектор 5 импульсов по длительности, первый 6 и второй 7 D-триггеры, первый 8 и второй 9 элементы НЕ, элемент 10 задержки, первый 11 и второй 12 элементы И, элемент РШИ 13, группу 14 элементов И, содержащую элементы И 14.1-14.k, первые входы.устройства 15.1-15.П, второй вход 16, третий вход 17, первый выход .18 и вторые выходы 19.1-19.k.

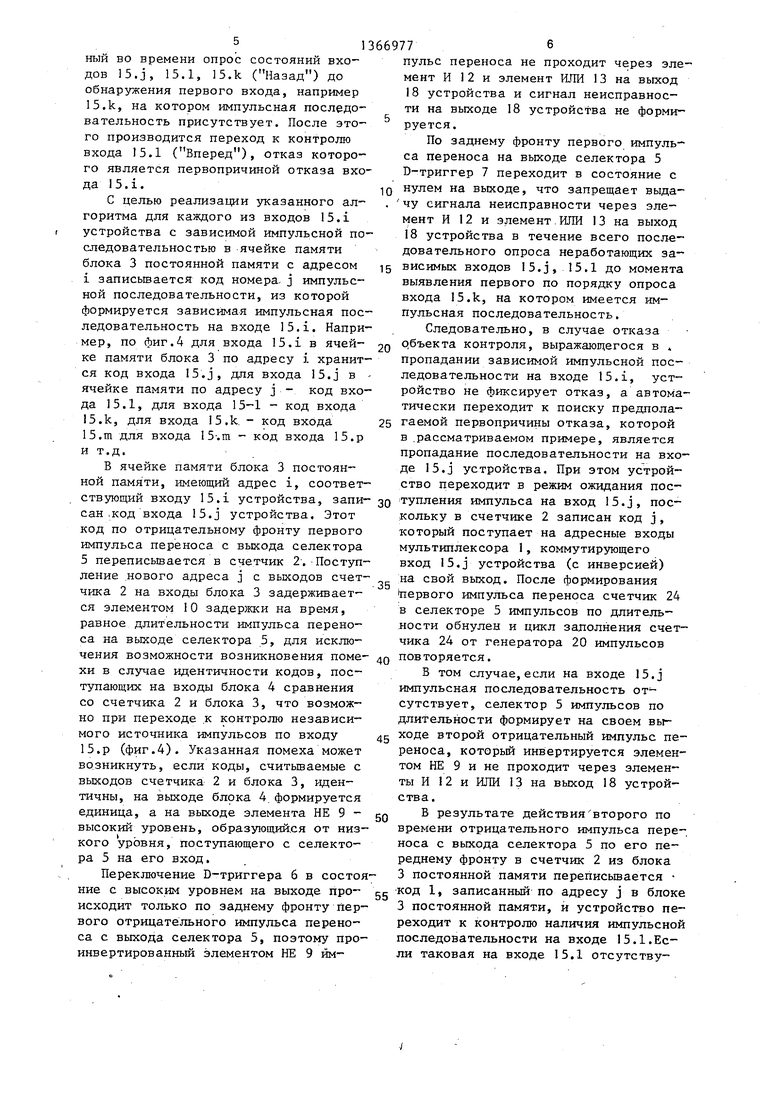

Селектор 5 импульсов по длительности с одержит генератор 20 импульсов, первый 21 и второй 22 элементы И-НЕ, RS-триггер 23 и счетчик 24.

Информационные входы мультиплексора 1 соединены с первыми входами 15.1-15.П, устройства, адресные входы - с информационными выходами счетчика 2. Выход мультиплексора 1 соединен со счетным входом счетчика 2 и первым входом селектора 5 импульсов по длительности. Второй вход селектора импульсов соединен с вторым входом 16 устройства и установочным входом первого D-триггера 6 и входом первого элемента НЕ 8. Выход первого элемента НЕ 8 соединен с установочным входом счетчика 2, которьй соединен управляющим входом с выходом селектора 5 импульсов по длительности, син- хровходом первого D-триггера 6 и входом второго элемента НЕ 9, соединенного выходом с первыми входами первого 1 1 и второго 12 элементов И, соединенных выходами с первым и вторым входами элемента ИЛИ 13 соответственно, соединенного выходом.с первым выходом 18 устройства и первыми входами группы элементов И I4.1-.14.k, каяздый из выходов которой соединен с соот- ветствзпощим вторым выходом 19.1-19.k

устройства, вторые входы групды связаны с соответствующими выходами счетчика 2, соединенными через эле-

мент 10 задержки с срответствующими входами блока 3 постоянной памяти. Выходы блока 3 постоянной памяти соединены с соответствующими информационными входами счетчика 2 и первыми

входами блока 4 сравнения, который соединен вторыми входами с выходами элемента 10 задержки, выходом - с вторым входом первого элемента И 11. Третий вход первого элемента И I1 соединен с инверсным выходом первого D- триггера 6, прямой выход которого соединен с вторым входом второго элемента И 12, а информационный вход с шиной 1 устройства. Третий вход се-

лектора 5 импульсов соединен с третьим входом устройства, D-вход второго D-триггера 7 соединен с общей шиной устройства, С-вход - с выходом селектора 5 импульсов по длительности, S-вход - с выходом мультиплексора 1, R-вход - с вторым входом устройства, прямой выход - с третьим входом второго элемента И 12.

Селектор 5 импульсов по длительности содержит генератор 20 импульсов, выход которого соединен с первым входом первого элемента И-НЕ 21. Выход первого элемента И-НЕ соединен со счетным входом счетчика 24, установочньш вход которого соединен с выходом второго элемента И-НЕ 22. Выход селектора 5 импульсов по длительности является выходом переноса счетчика 24. Первый вход второго элемента И-НЕ 22 соединен с первым входом селектора импульсов-по длительности.

Второй вход селектора импульсов соединен со вторым входом второго элемента И-НЕ 22 и первым установочным входом RS-триггера 23. Выход RS-триг гера соединен с вторым входом первого элемента И-НЕ 21, второй установочный вход RS-триггера 23 - с третьим входом 17 селектора импульсов по длительности.

Устройство работает следующим об- , разом.

Пусть, например, импульсные последовательности на входах 15.1, 15.2,- 15.П-1, 15.П устройства являются зависимыми.

Перед Контролем наличия последовательностей импульсов на входах 15.1-15.п устройства на его вход 16

31366977 ;,4

подается отрицательный импульс на- с R-входа счетчика 24. После этого чальной установки (фиг.3), который устройство переходит в режим ожида

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля интегральных схем | 1986 |

|

SU1377785A1 |

| Цифровой интерполяционный фильтр | 1990 |

|

SU1728962A1 |

| Устройство для ввода информации от двухпозиционных датчиков | 1987 |

|

SU1444739A1 |

| Устройство для контроля многоканальных импульсных последовательностей | 1987 |

|

SU1478216A1 |

| СПОСОБ МОНИТОРИНГА КАНАЛОВ СВЯЗИ В ВОЛОКОННО-ОПТИЧЕСКОЙ СИСТЕМЕ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2022 |

|

RU2785587C1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1254506A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Устройство для поиска зон информации на магнитном носителе | 1989 |

|

SU1644217A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

| Динамическое запоминающее устройство | 1987 |

|

SU1465914A1 |

устанавливает через элемент НЕ 8 счетчик 2 в нулевое состояние, селектор 5 импульсов по длительности - в состояние с высоким уровнем на выходе, D-триггеры 6 и 7 - в состояние с низким уровнем на выходе.

Высокий уровень на выходе селектора 5 импульсов по длительности (фиг.2) образуется за счет того, что импульс начальной установки с входа 16 устройства проходит на вход элемента И-НЕ 22, на выходе которого формируется высокий уровень, устанавливающий счетчик 24 в нулевое состояние, при этом на его выходе переноса устанавливается высокий уровень. Одновременно

тановки поступает на S-вход RS-триг- гера 23, который высоким уровнем со своего выхода разрешает прохождение импульсов генератора 20 импульсов на С-вход счетчика 24. После окончания прохождения импульса начальной устания поступления импульсов на его вход 15.2. В случае наличия импульсной последовательности на входе 15.2 первый ее импульс добавляет в счетчик 2 единицу и устанавливает счетчик 24 в нуль, в результате чего устройство

JQ переходит к контролю импульсной последовательности на входе 15.3. В случае годности объекта контроля, т.е. когда на всех входах 15.1-15.П имеются импульсные последовательности,

15 устройство обеспечивает последовательный во времени опрос состояний на входах 15.3-15.п и далее циклически 15.1-15.п и т.д. Коэффициент пересчета счетчика 2 выбирается равным п.

импульс начальной ус- 20 Частота импульсов генератора 20 и разрядность счетчика 24 выбираются таким образом, чтобы время Т заполнения счетчика 24 и формирования импульса переноса на его выходе перено- 25 са бьшо больше или равно-максимально возможному интервалу Т между импульсами во всех импульсных последовательновки на вход 16 счетчик 24 начинает подсчет импульсов, поступающих на его С-вход от генератора 20 импульсов, а

ностях, поступающих на все входы 15.1- 15.п. При годности объекта контроля

устройство переходит в режим ожидания 30 отрицательные импульсы с выхода мульприхода импульса на его вход 15.1 (фиг.З). Если этот импульс приходит через время, меньшее,чем время переполнения счетчика 24, необходимое для формирования отрицательного импульса переноса на его выходе, то он проходит, инвертируясь, на выход мультиплексора 1 (фиг.З). Отрицательный импульс с выхода мультиплексора 1, соответствующий первому положительному импульсу на входе 15.1 устройства, инвертируется элементом И-НЕ 22, поступает на установочный вход счетчика 24, сбрасьтая его высоким

35

типлексора 1 удерживают триггер 7 в положении с высоким уровнем на выходе.

Пусть импульсная последовательность на входе 15.1 является зависимой от импульсных последовательностей на входах 15.j,15.1, 15.k (где 1 1 j произвольные числа) в соответствии с фиг.4, на которой услов- 4Q но показана эта зависимость, и в момент опроса входа 15.1 устройства через время Т, отсчитьшаемое от заднего фронта импульса на входе 15.1-1 устройства, импульс на входе 15.1 отуровнем в нуль, и подготавливает та- 45 сутствует. При этом на выходе переноса счетчика 24 и выходе селектора 5 формируется отрицательный импульс переноса, передний фронт которого поступает на V-вход счетчика 2 и разреким образом селектор 5 импульсов к контролю наличия импульсов на входе 15.2 устройства. Этот же импульс устанавливает по S-входу D-триггер 7

в единичное состояние. Передний фронт gQ. щает перепись в счетчик 2 двоичного отрицательного импульса с выхода муль- кода, считываемого в момент опроса

типлексора 1 подготавливает счетчик по С-входу (фиг.1)-к переключению. По заднему (положительному) фронту

этого импульса осуществляется добав- gg информационные входы счетчика 2).

ление в счетчик 2 единицы и разреща- ется повторное заполнение счетчика 24 (фиг.2) импульсами от генератора 20, так как снимается высокий уровень

Алгоритм поиска первопричины от каза в данном случае соответствует фиг.4, т.е. для выявления причины отказа производится последователь-

ния поступления импульсов на его вход 15.2. В случае наличия импульсной последовательности на входе 15.2 первый ее импульс добавляет в счетчик 2 единицу и устанавливает счетчик 24 в нуль, в результате чего устройство

переходит к контролю импульсной последовательности на входе 15.3. В случае годности объекта контроля, т.е. когда на всех входах 15.1-15.П имеются импульсные последовательности,

устройство обеспечивает последовательный во времени опрос состояний на входах 15.3-15.п и далее циклически 15.1-15.п и т.д. Коэффициент пересченостях, поступающих на все входы 15.1- 15.п. При годности объекта контроля

5

типлексора 1 удерживают триггер 7 в положении с высоким уровнем на выходе.

Пусть импульсная последовательность на входе 15.1 является зависимой от импульсных последовательностей на входах 15.j,15.1, 15.k (где 1 1 j произвольные числа) в соответствии с фиг.4, на которой услов- Q но показана эта зависимость, и в момент опроса входа 15.1 устройства через время Т, отсчитьшаемое от заднего фронта импульса на входе 15.1-1 устройства, импульс на входе 15.1 отвхода 15.1 устройства из блока постоянной памяти (по адресу 1, задаваемому со счетчика 2 и поступающему на

информационные входы счетчика 2).

Алгоритм поиска первопричины отказа в данном случае соответствует фиг.4, т.е. для выявления причины отказа производится последователь-

ный во времени опрос состояний входов 15.J, 15.1, 15.k (Назад) до обнаружения первого входа, например 15.k, на котором импульсная последовательность присутствует. После этого производится переход к контролю входа 15.1 (Вперед), отказ которого является первопричиной отказа входа 15.1.

С целью реализации указанного алгоритма для каждого из входов 15.1 устройства с зависимой импульсной последовательностью в ячейке памяти блока 3 постоянной памяти с адресом 1 записьюается код номера- j импульсной последовательности, из которой формируется зависимая импульсная последовательность на входе 15,1. Например, по фиг,4 для входа 15.1 в ячейке памяти блока 3 по адресу 1 хранится код входа 15.J, для входа 15.J в ячейке памяти по адресу j - код входа 15.1, для входа 15-1 - код входа I5.k, для входа I5.k - код входа 15.m для входа 15-.га - код входа 15.р и т.д.

В ячейке памяти блока 3 постоянной памяти, имеющий адрес 1, соответствующий входу 15.1 устройства, запи сан ,код входа 15.j устройства. Этот код по отрицательному фронту первого импульса переноса с выхода селектора 5 переписьшается в счетчик 2.-Поступление нового адреса j с выходов счет Ч1жа 2 на входы блока 3 задерживается элементом 10 задержки на время, равное длительности импульса переноса на выходе селектора 5, для исключения возможности возникновения помехи в случае идентичности кодов, поступающих на входы блока 4 сравнения со счетчика 2 и блока 3, что возможно при переходе к контролю независимого источника импульсов по входу 15.Р (фиг.4). Указанная помеха может возникнуть, если коды, считьшаемые с выходов счетчика 2 и блока 3, идентичны, на выходе блока 4. формируется единица, а на выходе элемента НЕ 9

высокий уровень, образующийся от низкого уровня, поступающего с селектора 5 на его вход.

Переключение D-триггера 6 в состояние с высоким уровнем на выходе про- gg исходит только по заднему фронту первого отрицательного импудьса переноса с выхода селектора 5, поэтому про- инвертированный элементом НЕ 9 им0

5

о тупления импульса

g

пульс переноса не проходит через элемент И 12 и элемент ИЛИ 13 на выход 18 устройства и сигнал неисправности на выходе 18 устройства не формируется.

По заднему фронту первого импульса переноса на выходе селектора 5 D-триггер 7 переходит в состояние с нулем на выходе, что запрещает выдачу сигнала неисправности через элемент И 12 и элемент. РШИ 13 на выход 18 устройства в течение всего последовательного опроса неработающих зависимых входов 15.J, 15.1 до момента выявления первого по порядку опроса входа I5.k, на котором имеется импульсная последовательность.

Следовательно, в случае отказа рбъекта контроля, выражающегося в пропадании зависимой импульсной последовательности на входе 15.1, устройство не фиксирует отказ, а автоматически переходит к поиску предпола- 5 гаемой первопричины отказа, которой в .рассматриваемом примере, является пропадание последовательности на входе 15.J устройства. При этом устройство переходит в режим ожидания поена вход 15.J, поскольку в счетчике 2 записан код j, который поступает на адресные входы мультиплексора 1, коммутирующего вход I5.J устройства (с инверсией) на свой выход. После формирования (первого импульса переноса счетчик 24 в селекторе 5 импульсов по длительности обнулен и цикл заполнения счетчика 24 от генератора 20 импульсов повторяется.

В том случае, если на входе 15.J импульсная последовательность отсутствует, селектор 5 импульсов по длительности формирует на своем вы- g ходе второй отрицательный импульс переноса, который инвертируется элементом НЕ 9 и не проходит через элементы И 1 2 и ИЛИ 13 на выход 18 устройства.

В результате действия второго по времени отрицательного импульса переноса с выхода селектора 5 по его переднему фронту в счетчик 2 из блока 3 постоянной памяти переписьшается код 1, записанный по адресу j в блоке 3 постоянной памяти, и устройство переходит к контролю наличия импульсной последовательности на входе 15.1.Если таковая на входе 15,1 отсутству5

0

0

ет, аналогично осуществляется переход к контролю по выходу 15.k. Так как считается, что на входе 15.k импульсная последовательность присутствует, то первый ее отрицательный импульс с выхода мультиплексора 1 устанавливает D-тригг-ер 7 в состояние С единицей на выходе и переключает счетчик 2 Б последующее состояние для контроля входа 15.k+l устройства который может быть независимым от входа 15.k (k+1 - 1). Однако, когда устройство переходит к опросу входа 15,1, отказ по которому и является первопричиной отказа.по входу 15.1 (фиг.4), в результате отсутствия импульсов на этом входе- селектор 5 выработает отрицательный импульс- пе-

реноса, который инвертируется элемен- JQ с помощью адреса i,. записанного в

том НЕ 9 и проходит через элемент И 12, так как с выходов D-триггеров 6 и 7 на этот элемент поступают высокие уровни. На выходе элемента И 12

счетчике 2), в соответствующей i-й ячейке памяти блока 3 постоянной п мяти записьгоается код номера i в д ичном коде. Так как коды на выходе

формируется высокий уровень, который 25 блока 3 и счетчика 2 в этом случае

через элемент ИЛИ 3 стробирует элементы И 14.1-14.k, что приводит к выдаче кода 1 номера неисправного входа на выходы 19.1-19.k устройства.

Поскольку в соответствии с фиг.4 после контроля входа 15.1 устройство в случае отсутствия импульсов на этом входе переходит к контролю входа 15.k, происходит автоматический периодический опрос поочередно входов 15.1 и 15.k с периодической выдачей кода 1 на выходы 19.1-19.k устройства по импульсу переноса с селектора 5 импульсов по длительности.

Для прекращения работы устройства задается низкий уровень на его вход 17, что приводит к переключению- триггера 23 в селекторе 5 импульсов по длительности в состояние с нуле- - вым уровнем на выходе и прекращению заполнения счетчика 24.

В результате реализации описанного на примере четырех зависимых входов 15.1, 15.J, 15.1, 15.k (фиг.4) устройства алгоритма его работы в случае обнаружегшя отказа на его произвольном входе 15.1 выявляется вход 15.1, отказ по которому является первичным, т.е. осуществляется локализация первопричины отказа.

На фиг.З показаны четыре импульсных последовательности, причем зависимость приводится в следующем порядке: вход 15.П зависит от входа

35

40

совпадают, блок 4 выдает на элемент И 11 высокий уровень.

Если при контроле последовательн

30 сти на входе 15.1 выявляется ее отсутствие, на выходе селектора 5 импульсов формируется через время Т о рицательньш импульс переноса, кото- рьш переписьшает код ячейки с номером i блока 3 постоянной памяти в счетчик 2 (его прежнее состояние по тверждается) и проходит через элеме ты И 11 и ИЛИ 13 на входы элементов И 14.-l4.k. На выходы 19.1-19.k ус ройства выдается код номера i отказавшей последовательности.

За счет использования блока 4 ср нения устройство позволяет в случае контроля входа 15.1 с независимой п

45 следовательностью импульсов через в мя Т вьщать сигнал неисправности на выход 18 при отсутствии ее на вход 15.1.

Элемент 10 задержки во всех режи

50 мах работы устройства обеспечивает задержку поступления нового адреса на блок 3 постоянной памяти из счет чика 2 на интервал времени, равный длительности отрицательного импульс

gg переиоса на выходе селектора 5. Эт необходимо для того, чтобы исключит многократную запись информации из блока 3 в счетчик 2 за время импуль са переноса.

Считается, что пропала импульсная последовательность на входе 15.П-1. При поиске первопричины переходят к входу 15.2, а затем к входу 15.1.

Так как на входе I5.I импульсная последовательность присутствует, то снова возвращаются к контролю импульсной последовательности на входе 15.2, которая и является причиной отказа импульсной последовательности на входе 15.П-1.

В том случае, если импульсная последовательность, поступающая на вход 15.1 устройства, является независимой (и опрашивается мультиплексором

с помощью адреса i,. записанного в

счетчике 2), в соответствующей i-й ячейке памяти блока 3 постоянной памяти записьгоается код номера i в двоичном коде. Так как коды на выходе

5

0

совпадают, блок 4 выдает на элемент И 11 высокий уровень.

Если при контроле последовательно0 сти на входе 15.1 выявляется ее отсутствие, на выходе селектора 5 импульсов формируется через время Т от- рицательньш импульс переноса, кото- рьш переписьшает код ячейки с номером i блока 3 постоянной памяти в счетчик 2 (его прежнее состояние подтверждается) и проходит через элементы И 11 и ИЛИ 13 на входы элементов И 14.-l4.k. На выходы 19.1-19.k устройства выдается код номера i отказавшей последовательности.

За счет использования блока 4 сравнения устройство позволяет в случае контроля входа 15.1 с независимой по-

5 следовательностью импульсов через время Т вьщать сигнал неисправности на выход 18 при отсутствии ее на входе 15.1.

Элемент 10 задержки во всех режи-

0 мах работы устройства обеспечивает задержку поступления нового адреса на блок 3 постоянной памяти из счетчика 2 на интервал времени, равный длительности отрицательного импульса

g переиоса на выходе селектора 5. Это необходимо для того, чтобы исключить многократную запись информации из блока 3 в счетчик 2 за время импульса переноса.

Ф о рмула изобретения

ю щ е е с я тем, что селектор импульсов по длительности содержит генератор импульсов, соединенный выходом с первым входом первого элемента 30 И-НЁ, соединенного выходом со счетным входом счетчика, соединенного выходом переноса с выходом селектора,

установочным входом - с выходом ВТО-

рого элемента И-НЕ, соединенного пер- 35 вым входом с первым входом селектора, второй вход которого соединен с вторым входом второго элемента И-НЕ и первым установочным входом RS-тригге- ра, соединенного выходом с вторым 40 входом первого элемента И-НЕ, вторым установочным входом RS-триггера - с третьим входом селектора.

5

держки с соответствующими входами блока постоянной памяти, соединенного выходами с соответствующими информационными входами счетчика и пер- .выми входами блока сравнения, соединенного вторыми входами с выходами элемента задержки, выходом - с вторым входом первого элемента И, соединенного третьим входом с инверсным выходом первого D-триггера, прямой выход которого соединен с вторым входом второго элемента И, а информационный вход первого D-триггера соединен с щиной 1 устройства, третий вход селектора импульсов по длительности соединен с третьим входом устройства, D-вход второго D-триггера соединен с общей шиной устройства.

ю щ е е с я тем, что селектор импульсов по длительности содержит генератор импульсов, соединенный выходом с первым входом первого элемента И-НЁ, соединенного выходом со счетным входом счетчика, соединенного выходом переноса с выходом селектора,

установочным входом - с выходом ВТО-

рого элемента И-НЕ, соединенного пер- вым входом с первым входом селектора, второй вход которого соединен с вторым входом второго элемента И-НЕ и первым установочным входом RS-тригге- ра, соединенного выходом с вторым входом первого элемента И-НЕ, вторым установочным входом RS-триггера - с третьим входом селектора.

г

BbixJr Вых. 15

Фиг. I

riruuifinmi

Фиг.

| Устройство для контроля импульсов | 1978 |

|

SU781723A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля импульсов | 1982 |

|

SU1062623A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-01-15—Публикация

1986-05-11—Подача