Изобретение относится к вычислительной технике и может быть использовано для отладки аппаратно-программных средств микроЭВМ и микропроцессорных устройств в реальном масштабе времени.

Цель изобретения - повышение производительности при отладке аппаратно-программных средств микропроцессорных систем.

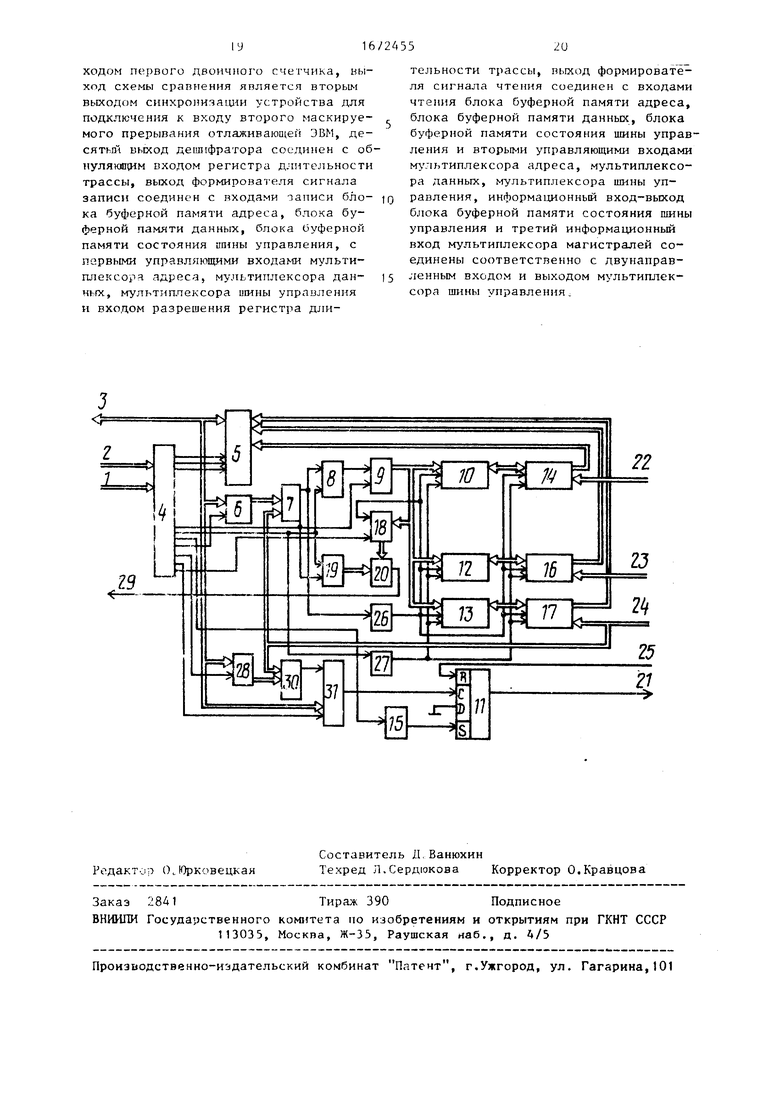

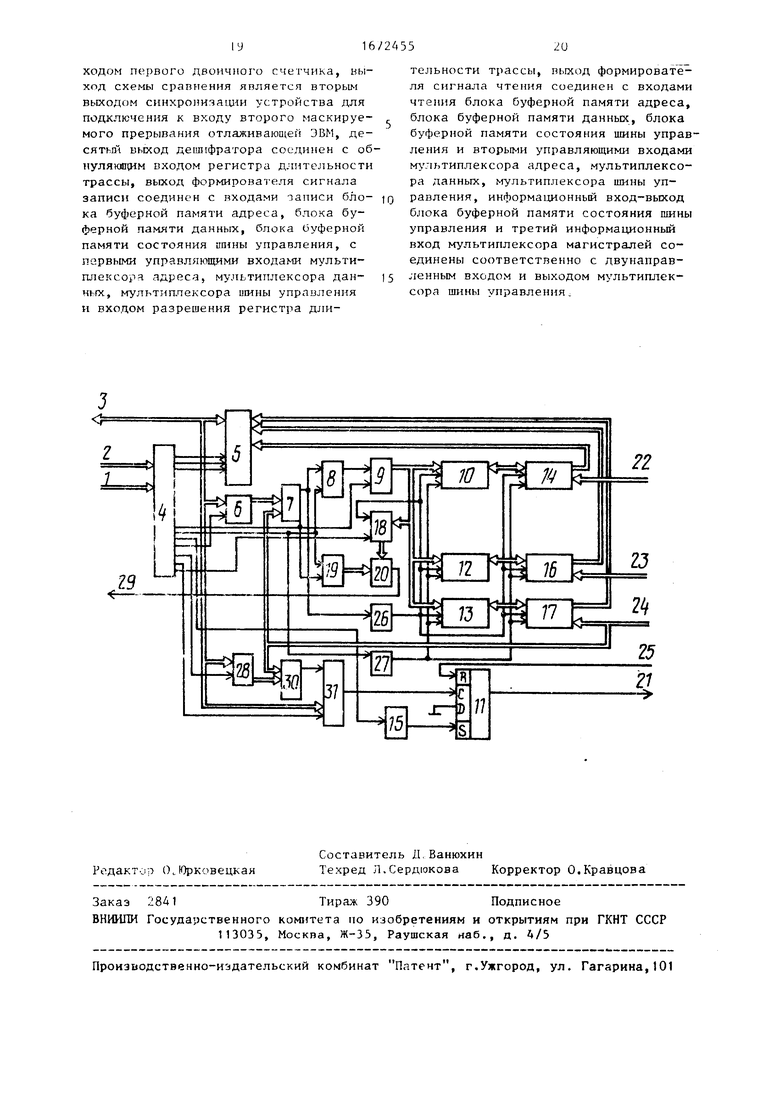

На чертеже представлена структурная схема устройства для. отладки микропроцессорных систем,

Устройство содержит адресный вход 1, первый информационный вход 2, информационный выход 3, дешифратор 4, мультиплексор 5 магистралей, первый

регистр 6, первый селектор /, элемент ИЛИ 8, первый двоичный счетчик 9, блок 10 буферной памяти адреса, триггер 11, блок 12 буферной памяти данных, блок 13 буферной памяти состояния шины управления, мультиплексор 14 адреса, формирователь 15 короткого импульса, мультиплексор 16 данных, мультиплексор 17 шины управления, регистр 18 длительности трассы, второй двоичный счетчик 19, схему 20 сравнения, первый выход 21 синхронизации, второй, третий и четвертый информационный входы 22-24 соответственно, вход 25 начальной установки, формирователь 26 сигнала записи, формирователь 27 сигнала чтения,

О

4

го ел ел

второй регистр 28, второй выход 29 синхронизации, второй селектор 30 и вычитающий счетчик 31 импульсов о При включении питания одиночный импульс с входа 25 начальной установки поступает на нулевой вход (R-вход) триггера 11 и устанавливает его в нулевое состояние Триггер 11 формирует нулевой сигнал, поступающий через первый выход 21 синхронизации устройства в отлаживаемую микропроцессорную систему в виде сигнала WAIT (ожидать) и в отлаживающую ЭВМ в виде сигнала первого маскируемого запроса прерывания

На первый информационный вход дешифратора 4 через адресный вход 1 устройства поступают разряды адресной шины отлаживающей ЭВМ. Через первый информационный вход 2 устройства на второй вход дешифратора 4 поступают сигналы шины управления отлаживающей ЭВМ с

При поступлении на дешифратор 4 совокупности сигналов разрядов адреса, сигналов управления Запись и Чтение в зависимости от кода, поступившего на вход дешифратора 4, возбуждается один из выходов дешифратора 4,

Поступающий код на входе дешифратора 4 может быть десяти типов.В соответствии с работой устройства для отладки микропроцессорных систем обозначим каждый из кодов символами: а, Ь, с, ct, е, f, g, h, i, jt При поступлении на входы дешифратора 4 кодов а, Ь, с возбуждаются соответственно первый, второй и третий выходы дешифратора 4, которые соединены соответственно с первым, вторым и третьим управляющими входами мультиплексора 5 магистралей о При наличии кодов а, Ь, с на входах дешифратора 4 мультиплексор 5 магистралей обеспечивает коммутацию информации соответственно с информационных выходов мультиплексора 14 адреса, мультиплексора 16 данных и мультиплексора 17 шины управления на информационный выход 3 устройства. Код d возбуждает четвертый зыход дешифратора 4, который соединен с обнуляющими входами первого 9 и второго 19 двоичных счетчиков, Посредством кода d осуществляется произвольной-; сброс одновременно содержимого первого 9 и второго 19 двоичных счетчиков. Код е возбуждает

5

0

5

0

5

0

5

0

5

пятый выход дешифратора 4, который соединен с входом формирователя 27 сигнала чтения, со счетным входом второго двоичного счетчика 19 и с первым входом элемента ИЛИ 8, сигнал с выхода которого поступает на счетный вход первого двоичного счетчика 9о Посредством последовательной подачи кода е осуществляется восстановление сформированной после прогона трассы участка отлаживаемой программы за счет последовательного наращивания содержимого первого 9 и второго 19 двоичных счетчиков, а также запуска формирователя 7.1 сигнала чтенияс Код f возбуждает шестой выход дешифратора 4, который соединен с входом формирователя 15 короткого импульса„ Код f, запуская формирователь 15 короткого импульса, переводит триггер 11 по установочному входу (S-вход) в единичное состояние, снимая тем самым сигнал WAIT с первого выхода 21 синхронизации устройства для отлаживаемой микропроцессорной системы и осуществляя запуск отлаживаемой микропроцессорной системы после останова Коды g, h, i возбуждают соответственно седьмой, восьмой и девятый выходы дешифратора 4, которые подключены к входам разрешения соответственно регистра 6, регистра 28 и вычитающего счетчика 31 импульсов При наличии кодов g, h, i на входах дешифратора 4 последний сигналами на седьмом, восьмом и девятом своих выходах разрешает запись информации с информационного выхода 3 устройства соответственно в регистр 6, регистр 28 и на установочный вход вычитающего счетчика 31 импульсов„ Код j возбуждает десятый выход дешифратора 4, который подключен к обнуляющему входу регистра 18 длительности трассьи Посредством кода j осуществляется произвольный сброс содержимого регистра 18 длительности трассьи

Регистры 6 и 28 предназначены для задания режима работы соответственно первого / и второго 30 селекторов

Под воздействием комбинации сигналов, хранящейся в регистре 28, второй селектор 30 пропускает только один определенный разряд шины управления отлаживаемой микропроцессорной системы, например Чтение памяти или сигнал первого цикла команды, с

1

четвертого информационного яхола 24 устройства на счетный вход вычитающего счетчика 31 импульсов Кодом информации информационного вькода 3 устройства по установок- юму пхолу вычитаюпилй счетчик 31 импульсов настраивается на подтечет определенно о числа импульсов при поступлении сигнала с одиннадцатого выхода дешифратора 4 на вход разрешения вычитающего счетчика 31 импульсов, задавая тем самым длину трассы контролируемого участка отлаживаемой программы, На счетный вход вычитающего счетчика 31 импульсов поступают импульсы раз-- рядл управления, пропускаемые вторым селектором 30 с четвертого информационного входл 24 устроит ч ва -, Пр поступлении на счетный йхог. вычитг.ю.щего счетчика 31 импульсов количества импульсов, равного колу на его информационном входе, вычитающий счетчик 31 импульсе., возбуждает сиг-нал, поступающий на г..ахровизирующий вход (С-вход) триггера 11. На информационный вход (Т)-1;ход) три/ гера 1 1 подается логический нуч;., При поступлении сигнала нг смнхронп:,прую:щ1Й вход (С-вход) триггера 11 последний устанавливается Р нулевое ic лголние и вырабатывает сиг-нал WATT (ожидать для отлаживаемой программ -: микропроцессорной системы на ;. рвом выходе 21 синхронизации устройства,, Одновременно нулевой сигнал с л; кода триггера 11 подается в виде первого маскируемого сигнала прерывания INT1 для отлаживающей ЗВМ через первый выход 21 синхронизации уст ройстваа

Под воздействием комбинации двоичных сигналов, хранящейся в регистре 6, первый селектор 7 пропускает только один определенный разряд шин;,; управления отла.-шваемой микропроцессорной системы, например Ml -- CHI нал начала каждого машинного цикла или тактовый импульс начала ха;;-дого машинного такта (в зависимости от требуемой глубины достоверней. ти Функционирования аппаратно-программных средств), с четвертого информационного входа 24 устройства на вход формя- |рователя 26 сигнала яяписи . :и ьто- рс/й вход элемента ИЛИ 8, сигнал с выхода которого поступает на счетный вход первого двоичного счетчика 9.

ни

О1. .jujpHOb

L. рНОЙ

,;..;.. Игр н-:лм -а- ОЛРОС

С

5

0

5

0

55

д.воп-.ггый г-:г--; л-. т,а;: импульс., йог-. п.---Т1-; смет}1ЫЙ, чход, yci rtiKi.. . т двоичный ксл, - торь.и госту- p. fT на адреол|г-1е вхл,: --: .; f) буфг- -1- ;;r,ii 1.ммяти адреса, : Лгг-1яти даннь;:; f .V1 -1

1Т-1Г ЯТИ СОСТОЯНИЯ, /ill:: НИИ ДВОИЧНЫЙ : . Че .

после;и.}-;пте.:т: ч;-: ячеек блоков иус ямчюй пзмя- л адреса 10, буферной пак.чти дангных 12 и буферное ;.аг яти СОСТОЯ1ГИЛ шилн я т-,, :нления 13, между информацлонными ,:.. i.v-; n которы-- и (..(.кттветстг ующпм. ..1; )), --лен1 s.i. ..-:о. мул;-.-гриле;. i .j;vpi. со, мущ.типлексор,: 16 л. ним:-.- м мул. уун- плгК|.орл. 1 ,; и:м.ч| лц). ;iji;. 1-;-.п П 1олсхо- Д1ГГ одновременны) оп:-;сь (-Г -пппей Мул)л нплексспи- я,п; Гч:- 1, лунных 6 и тины управления i/ оОоскечпяают передачу пнф,,-jMannn с ;;rj-or. го 2, третьего 23 I; чег/гн:ртого 24 пп 4:г)рма- Ц1тонньп входов устоойс гвг пп ннформл- ционныс зхо;дь сооТ1 етст;:енпо блоков буфернс й памяти :прее.ч |П, г.у .Ьсрно памяти данны:-. К: л буЛерно памяти состо гня ;ш;н;. лт-авленп;) 13 при лнчп сигнала с выхо: .а (Ьор л .г. оъателя 2о сигнала aanncii на первых угн -лоши:- ;:.:нг-; i.ходах мультнпле;-:соров я. ...1Х 16 И ШмТ Ы yilpar jiCHil.-I 1/,

При наличии сигнала с тт.сго.да ровате.пя 2/ сигнала чтения нл вторых уп р а в i я ютих в х о ли х м у л j т 11 п. е i.- с о р о в адреса 14, данных 16 л шин:,- упп- вле- нля 17 последние обеспечивают передачу и времен юс хранение информаи.н:. поступающей через их двунаправленные

входы с информационных

блоков

i

буферной памяти адреса 10, буферно-й памяти данных 12 и буферной памяти состояния шины управления 13 па информационные -ВУОДЫ мульгпч1лексоро-п а ;росл 14S данных ) : unni;-: упр.-гилс: 17 соответственно

Блоки буферной памяти алзос.; 10, буферной памяти д.алньк 12 п ovthepnoji п.- :-1;лгл состояния шины управления 3 о Теспечивают сохранение массив. информации о состоянии адресной птпп1-:, шлны данных, шины управления отлаживаемой микропроцессорной системы на всей трассе отлажпваомо то учплпха программ :- и выдачу этого масспга нп- формап,ии при восставов.пеннн I ru -iciec- кой трассы после прохождения ее заданной длиныо

Формирователи сигнала записи 26 и сигнала чтения 21 вырабатывают импульсы заданной формы и длительности, необходимые для записи и считывания информации в блоки и из блоков буферной памяти адреса 10, буферной памяти данных 12 и буферной памяти состояния шины управления 13 через мультиплексоры адреса 14, данных 16 и шины управления 1/ соответственное

Регистр 18 длительности трассы запоминает текущую двоичную комбинацию на выходе первого двоичного счетчика 9 при каждом воздействии импульса с выхода формирователя 26 сигнала записи на вход разрешения регистра 18 длительности трзссыо В момент выработки импульсов вычитающим счетчиком 31 имиутьсов регистр 18 длительности трассы записывает максимальную двоичную комбинацию на втоде первого двоичного счетчика 9, запоминая тем самым верхнюю границу заполнения ячеек блоков буферной памяти адреса 10, буферной памяти данных 12 и буферной памяти состояния шины управления 13 при формировании трассы прогона участка отлаживаемой программы

Под воздействием импульсов с пятого выхода дешифрлтора 4 на счетный вход второго двоичного счетчика 19 последний вырабатывает текущий адрес на своем выходе, поступающий на второй вход схемы 20 сравнения. При достижении на выходе второго двоичного счетчика 19 величины двоичного числа, равного двоичному числу, поступающему на первьй вход схемы 20 сравнения из регистра 18 длительности трассы, схема 20 сравнения вырабатывает сигнал второго маскируемого прерывания 1NT2 для отлаживающей ЭВМ на втором выходе 29 синхронизации устройства о

Для отладки аппаратно-программных средств микропроцессорной системы к устройству подсоединяются отлаживающая ЭВМ и отлаживаемая микропроцессорная система следующим образомt

Адресная шина отлаживающей ЭВМ подсоединяется к адресному входу 1 устройства, шина управления - к первому информационному входу 2 устройства, шина данных - к информационному выходу 3 устройства, линия сигнала на первый маскируемый запрос прерывания INT1 - к первому выхоцу 21 синхронизации устройства, линия сиг

П

5

0

5

0

5

0

5

нала на второй маскируемый запрос прерывания INT2 - к второму выходу 29 синхронизации устройства

Адресная шина отлаживаемой микропроцессорной системы подсоединяется к второму информационному входу 22 устройства, шина данных подсоединяется к третьему информационному входу 23 устройства, шина управления - к четвертому информационному входу 24 устройства, линия сигнала ожидания WAIT - к первому выходу 21 синхронизации устройства

Принцип работы устройства заключается в следующем. При отлаживании л микропроцессорной системы,работающей в реальном масштабе времени на рабочей скорости, не исключена возможность того, что в результате ошибок в программе, несовместимости аппаратно-программных средств, аппаратных сбоев микропроцессорная система начнет беспорядочное блуждание по памяти, рассматривая числовые массивы как цепочки команд, а команды как данные или адреса Поэтому возникает задача фактически проследить трассу нз каждом отлаживаемом участке программы и, анализируя состояние адресной шины, шины данных, шины управления, например, при каждом обращении к памяти или на каждом машинном цикле, или на каждом машинном такте (в зависимости от глубины достоверного контроля), выявить адекватность реального функционирования программ отлаживаемой микропроцессорной системы ожидаемому в целом и точно обнаружить момент и характер сбоя в ходе программыо

Любую программу, записанную в машинных кодах в память отлаживаемой микропроцессорной системы, можно представить в виде конечного числа линейных участков, связанных между собой командами перехода, и в отсутствие внешних прерываний функционирование отлаживаемой микропроцессорной системы на каждом линейном участке строго детерминировано в том смысле, что при правильно заданном прохождении в отлаживаемой микропроцессорной системе на управляющих линиях формируется строго определенная временная диаграмма сигналов управления, которую можно просчитать еще до начала прогона самой программы,, Поэтому длительность трассы каждого

контролируемого участка отлаживаемой программы можно задать и ограничить количеством импульсов на той или ино линии управления отлаживаемой микропроцессорной системы

Задавая длительность ожидаемой трассы каждого участка отлаживаемой программы, установочный вход вычитающего счетчика 31 импульсов определяет количество, а регистр 28 и второй селектор 30 - вид импульсов, поступающих из шины управления отлаживаемой микропроцессорной системы через четвертый информационный вход 24 уст ройства на счетный вход вычитающего счетчика 31 импульсов для их подсчет

Регистр 6 и первый селектор 7 определяют глубину достоверного протоколирования фактической трассы при прогоне каждого участка отлаживаемой трассы (например, при каждом машинном цикле или на каждом машинном такте), устанавливая вид импульсов, поступающих с шины управления отлаживаемой микропроцессорной системы через четвертый информационный вход 24 устройства на вход формирователя 26 сигнала записи и через второй вход элемента ИЛИ 8 на счетный вход первого двоичного счетчика 9С Первый двоичный счетчик 9, формируя на своем выходе адресный код, обеспечивает последовательное заполнение ячеек одновременно блоков буферной памяти адреса 10, буферной памяти данных 12 и буферной памяти состояния шины управления 13 информацией, поступающей соответственно через мультиплексоры адреса 14, данных 16 и шины управления 17с второго 22, третьего 23 и четвертого 24 информационных входов устройства о состоянии адресной шины шины данных и шины управления отлаживаемой микропроцессорной системы„

При поступлении на счетный вход вычитающего счетчика 31 импульсов количества, равного коду, записанному на информационный вход вычитающего счетчика 31 импульсов, происходит переброс триггера 11 в нулевое состояние0 К этому моменту в регистр 18 длительности трассы заносится по величине адресный код занятых под фактическую трассу прогона ячеек бло- ков 10, 12 и 13 буферной памяти„ Сигнал с выхода триггера 11 поступает через первый выход 21 синхронизации устройства в виде сигнала WAIT

0

0

5

5

$

0

5

0

5

0

(ожидать) в отлаживаемую микропроцессорную систему для ее останова Одновременно сигнал с выхода триггера 11 в виде маскируемого .запроса прерывания INT1 поступает через первый выход 21 синхронизации устройства в отлаживающую ЭВМ, запуская программу обработки маскируемого запроса прерывания INT1, в соответствии с которой ЭВМ переносит информацию о фактической трассе участка прогона отлаживаемой программы из каждой занятой под трассу ячейки блоков 10, 12 и 13 буферной памяти для анализа и отображения в отлаживающей ЭВМ„ Момент окончания фактической трассы при считывании информации из ячеек блоков 10, 12 и 13 буферной памяти определяет схема 20 сравнения, на первый вход которой поступает двоичный код с регистра 18 длительности трассы, г на второй вход - текущий двоичный код адреса, формируемого вторым двоичным счетчиком 19 о

При достижении конца сформированной трассы схема 20 сравнения вырабатывает сигнал INT2, поступающий через второй выход 29 синхронизации устройства в отлаживающую ЭВМ и запускающий в ней программу обработки маскируемого запроса прерывания ГЫТ2, в соответствии с которой анализируется, подготавливается и заносится на установочный вход вычитающего счетчика 31 импульсов, в регистр 28 и регистр 6 информация о следующем участке прогона отлаживаемой программы, а также автоматически запускается отлаживаемая микропроцессорная система.

Устройство работает следующим об- разомо

Отлаживаемая микропроцессорная система в соответствии с организацией своего интерфейса подсоединяется своей адресной шиной, шиной данных, шиной управления к второму 22, третьему 23 и четвертому 24 ш.форма- ционным входам устройства соответственно о Первый выход 21 синхронизации устройства является линией сигнала ожидания WAIT для отлаживаемой микропроцессорной системы

Отлаживающая ЭВМ в соответствии с организацией своего интерфейса подсоединяется адресной шиной к адресному входу 1 устройства шиной управления - к первому информационному

входу 2 устройства, шиной данных - к информационному выходу 3 устройства, линией сигнала первого маскируемого прерывания INT1 - к первому выходу 21 синхронизации устройства, линией сигнала второго маскируемого прерывания INT2 - к второму выходу 29 синхронизации устройства„

Работа устройства для отладки микропроцессорных систем начинается с того, что при включении питания с входа 25 начальной установки устройства поступает одиночный импульс на нулевой вход (R-вход) триггера 11 и устанавливает его в нулевое состояние С выхода триггера 11 нулевой сигнал поступает через первый выход 21 синхронизации устройства на линию сигнала WAIT отлаживаемой микро- процессорной системы

При последующем включении питания в отлаживаемой микропроцессорной системе последняя остановится в начале первого машинного цикла обработки нулевой ячейки отлаживаемой программы, так как на первом выходе 21 синхронизации устройства присутствует сигнал WA1Т к моменту начальной установки,

В с ю четстиии с предварительным анализом отлаживаемой программы микропроцессорной системы в программу 1ла;шван--Ег й ЭВМ заносится информация о динамике процесса прогона первого участка и каждого последующего с тлажираемой программы..

Отлаживающая ЭВМ в начале своей программы подготавливает устройство для отладки микропроцессорных систем к прогону первого участка программ от ;аживаемой микропроцессорной системы. Для этого отлаживающая ЭВМ выставляет по адресному входу 1 устройства И ПерВОМУ Информационному входу 2 устройства на вход дешифратора 4 последова-ельно коды d и j, которые возбуждают сигналы на четвертом и десятом выходах дешифратора 4 и, соответственно, очищают содер- жимое первого 9 и второго 19 двоичных счетчиков и регистра 18 длительности трассыо

Затем отлаживающая ЭВМ выставляет по адресному входу 1 устройства и первому информационному входу 2 устройства на входы дешифратора 4 код g который возбуждает седьмой выход дешифратора 4, разрешая занести с ин

д 5 0

5 0

0 д 0

,

5

формационного выхода 3 устройства в регистр 6 первого селектора код информации, определяющий режим работы первого селектора 7 и, соответственно, глубину достоверного контроля функционирования аппаратно-программных средств отлаживаемой микропроцессорной системы при прогоне первого участка (например, за счет формирования ячеек трассы на каждом машинном цикле или в каждом машинном такте) „

Затем отлаживающая ЭВМ выставляет по адресному входу 1 устройства и первому информационному входу 2 устройства на входе дешифрлтоиа 4 код h, который возбуждает на восьмом выходе дешифратора 4 сигнал, разрешающий занести с информационного выхода 3 устройства в регистр 28 код информации, определяющий выбор сигнальной линии шины управления отлаживаемой микропроцессорной системы с четвертого информационного входа 24 устройства через второй селектор 30 и пропуск импульсов с выбранной сигнальной линии на счетный вход вьпитчющего счетчика 31 импульсов,

Затем отлаживающая ЭВМ выставляет по адресному входу 1 устройства и первому информационному входу 2 устройства на моде дешифратора 4 код i, который возбуждает девятый выход дешифратора 4, сигнал с выхода которого, воздействуя на вход разрешения вычитающего счетчика 31 импульсов, разрешает запись двоичного кода на установочный вход вычитающего счетчика 31 импульсов с информационного выхода 3 устройства с, Двоичный код равен ожидаемому количеству импульсов, которые формируются на выбранной вторым селектором 30 линии сигнала управления шины управления отлаживаемой микропроцессорной системы (четвертый информационный вход 24 устройства) к моменту окончания прогона первого участка отлаживаемой программы о

Завершая подготовку к прогону первого участка отлаживаемой программы, отлаживающая ЭВМ выставляет по адресному входу 1 устройства и первому информационному входу 2 устройства на входе дешифратора 4 код f, который возбуждает шестой выход дешифратора 4, воздействующий на формирователь 15 короткого импульса, послед13

ний вырабатывает импульс, перебрасывающий триггер 11 но единичному входу (S-вход) в единичное состояние, снимая тем самым сигнал WAIT с первого выхода 21 синхронизации устройства. Кроме того, отлаживающая ЭВМ снимает маску с маскируемого запроса на прерывание IN11.

Отлаживаемая микропроцессорная система приступает к прогону первого участка отлаживаемой программы на рабочей скорости

Импульсы с выбранной первым селектором / линии управления (например, тактовые импульсы или импульсы начала цикла) шины управления отлаживае- мой микропроцессорной системы (четвертый информационный вход 24 устройства) поступают через второй вход элемента ИЛИ 8 на счетный вход первого двоичного счетчика 9 и одновременно на вход формирователя 26 сигнала записи. При этом первый двоичный счетчик 9 с поступлением первого и каждого последующего импульсов на свой t счетный вход формирует на выходе нарастающий двоичный код, который воздействует одновременно на адресные входы блоков буферной памяти адреса 10, буферной памяти данных 12 .и буферной памяти состояния шины управления 13 и на информационный вход регистра 18 длительности трассы.

Сигнал с выхода формирователя 26 сигнала записи воздействует на первые управляющие входы мультиплексоров адреса 14, данных 16 и шины управления 1 /, на входы записи блоков буферной памяти адреса, буферной памяти данных и буферной памяти состояия шины управления и на вход разре- ения регистра 18 длительности трасы, обеспечивая одновременное занесение информации о состоянии адресной шины, шины данных и шины управения отлаживаемой микропроцессорной системы с второго 22, третьего 23 и четвертого 24 информационных входов устройства в последовательные ячейки соответственно блоков 10, 12 и 13 буферной памяти и запоминание в регистре 18 длительности трассы текущего адреса заполняемых ячеек блоков 10, 12 и 13 буферной памяти,

При. достижении на счетном входе вычитающего счетчика 31 импульсов определенного количества импульсов, заданного кодом, занесенным на устано

10

672455 14

вочный вход вычитающего счетчика 31 импульсов, последний вырабатывает сигнал, который поступает на синхронизирующий вход (С-вход) триггера 11 и перебрасывает последний в нулевое состояние, На первом выходе 21 синхронизации устройства появляется сигнал WAIT, останавливающий работу отлаживаемой микропроцессорной системы К этому моменту в регистр 18 длительности трассы будет занесен адрес последней занятой ячейки трассы после прогона первого участка программы,,

. 5 Одновременно сигнал с выхода триггера 11 поступает в виде первого маскируемого сигнала прерывания INT1 в отлаживающую ЭВМ черед первый выход 21 синхронизации устройства0 Сигнал

20 INT1 означает, что отлаживаемая микропроцессорная система отработала первый заданный участок отлаживаемой программы на рабочей скорости и, воспринимая и обрабатывая это преры25 вание INT1, отлаживающая ЭВМ выводит из устройства информацию о сформированной трассе о

Выполняя программу обработки прерывания INT1, отлаживающая ЭВМ

3Q выставляет вначале по адресному входу 1 устройства и первому информационному входу 2 устройства на входах дешифратора 4 код d, который возбуждает сигнал на четвертом выходе дешифратора 4, очищая первый 9 и второй 19 двоичные счетчики0 Затем отлаживающая ЭВМ выставляет по адресному входу 1 устройства и первому информационному входу 2 устройства на пер40

45

вый и второй входы дешифратора 4 код е, возбуждающий на пятом выходе дешифратора 4 сигнал, который поступает на вход формирователя 21 сигнала чтения, на счетный вход второго двоичного счетчика 19 и через второй вход элемента ИЛИ 8 на счетный вход первого двоичного счетчика 9, На выходе первого двойного счетчика 9 формируется двоичный код, соответст- 50 вующий адресу первой занятой под

трассу ячейки блоков буферной памяти адреса 10, буферной памяти данных 12 и буферной памяти состояния шины управления 13, формирователь 27 сигнала чтения вырабатывает сигнал, одновременно воздействующий на входы чтения блоков 10, 12 и 13 буферной памяти и на вторые управляющие входы мультиплексоров адреса 14, данных 16

55

15

и шины управления 1/, Содержимое пер вьк ячеек блоков 10, 12 и 13 буферной памяти поступает одновременно на информационные выходы соответственно мультиплексоров адреса 1г, данные 16 и :ии :ы управления 17.. Второй двоичный счетчик 1 J фиксирует адрес первых распечатанных ячеек памяти блоков 10, 12 и 13 буферной памяти Затем отлаживающая ЭВМ выставляет по тдресному входу i устройства и первому информационному входу 2 устройства на первый и второй входы дешифратора 4 последовательно ко-

№ мульг1 п.;чг ч сор J магистралей последовательно коммутирует информацию с информационных гыходов мультиплексоров адреса 14, данных 16 и ыины упраьчепкн нл первый иш юрмоцион- ный :птхо... 3 устройства для запоминания п последующего лнализа я отла- жнва -;о;: №;:, отлаживающая ЭВМ но pro,-1 - Л выставляет по адресном входу 1 устройств-, и первому информационно входу 2 устройства на

перпь и ; последона редав.ъ блоко 11 в отпяж гг ;l 1,1 тч to Л

Т .И Л: Г i , P - i

ичный ко, ; (.чеччико °

Хр.Я Г J4t ГОСЯ

vc.poTi хо ты пепшФрятора ч ечьно к.щы e, .i, b, c, ne, it: .ги. ВТОРЫХ .т,

1. и Р уф. памяти i . -для запоминания и --:-сь; ivii 4io U :-cc -yix-jnn oc- ; гея г; 1 i .-. iir.yi, ппка цво- : у:,;ход1. второго -воичьсг ке достиг i T значения j регистре 18 длительности тргк:сы адреса последл й занято: пор трас .-у ячейки в блок .х 10, 12 и 3 г ферной памяти. В этот момент СУ с; л 20 сраян ния вьиает сигнал о гс рого . аскпруемого прерывания Тл Т2, мост.лгющий на второй выход 29 .инхроннзапии у трсйстра в отла- , . ш гл:. м с-,10чаюыи; ;;, UT-J иы- iO.L- . -. .-h.ti - .. i :-:чег,:ой трассе пер-., го ; : гс ка от,г - -:ча; см--;-- прогг-ам MI. -авсгшен.

RriCiipi ;-: и обраоэ гг-п- л -„игнал

К I ОРОГО ,,:.уеМиГО npt:pfc F- и 1.Я

., тла;кнлак:1п.;1я ЭВМ а--ализ1:jr - ет s илнг.ичру З . трассу прогона тт-гр- иого участк : (ггл./и- йе;:он п:.,ограм.-..- в : ч..-(. т .. мого фу(--, in Oti ..i.r-чп г ; П; :;;.тно- nporuaNrM- ных сред..тъ -.тлаэтю,;:-мой мнггопг. - .,ее.орнс.-Л . .v-.1.; отлая и-аем н .MUKpO:i ,. чес- о1-; о я .-.нстсмс- :-а ч;-.рьом ,. Астк.: лрпгр;;ммы функщ огиоог-. г:та

5

10

15

-,„ 25

/245516

адекватно, то, выполняя обработку второго маскируемого прерывания INT2, отлаживающая ЭВМ подготавливает устройство для отладки микропроцессорных систем для прогона отлаживаемой микропроцессорной системы на втором участке отлаживаемой программы,. Для этого отлаживающая ЭВМ гыставляет по адресному входу 1 устройства и первому информационному входу 2 устройства на первый п второй входы дешифратора 4 последовательно коды d, j, g, h, i, которые последовательно возбуждают четвертый, де.ся- тый, седьмой, восьмой и девятый выходы деигифратоуа 4 и, соответственно, очищай,-; содержимое первого 9 и второго 19 двоичных счетчиков и регистра 18 длительности трассы, разрешают занести коды информации с информационного выхода 3 устройства в регистр 6, регистр 28 и ка услаковоч- ньгй вход вычитающего счетчика П импульсов г

Завершая подготовку к прогону второго участка отлаживаемой программы, отл.чхл-гьают.чя ЭВМ выставляет по адресному входу устройства и первому информапионному входу 2 устройст- яа на первый и т.аорой пходы дешифра- : я 4 код f. к i орый позбу7кдает j r-:,TC-n ныход дешифратор i, воздийст- вугачии на вход зля 15 короткого импульса,последний перебрасывает

30

40

.is.

50

триггер М по еланичному входу ( ду) в единичное состояние , снимая тем самым сигнал WAIT с первого выхода 21 синхронизации устройства и разрешая отлаживаемой микропроцессорной системе приступить к прогону второго участка отлаживаемой программы на рабочей скоростио

Процесс прогона второго и каждого последующего участков отлаживаемой программы повторлйтся циклически, вплоть до окончания отлаживаемой программы,:

Ф о р мула и з о б р е т . н и п

Устройство ;ии отладки микропро- г-есгррн .гх систем, содержащее дешиф- ратцР мультиплексор магистралей, чср лыь двоичный счетчик, блок буфер- r.yi i jiAMHTii адрес-а, блок буферной пл- даьмых, мул ьтиш-t ксор адреса, мультиплексор iiaHHiix, элемент Е1ЛЧ, триггер, ;v;pMH гатель короткого импульса, причем адресный вход устройства для подключения к шине адреса отлаживающей ЭВМ соединен с первым информационным входом дешифратора, второй информационный вход которого соединен с первым информационным входом устройства для подключения к шине управления отлаживающей ЭВМ, информационный вход-выход устройства для подключения к шине данных отлаживающей ЭВМ соединен с информационным входом-выходом мультиплексора магистралей, первый, второй и третий выходы дешифратора соединены соответственно с первым, вторым и третьим управляющими входами мультиплексора магистралей, четвертый выход дешифратора соединен с обнуляющим входом первого двоичного счетчика, счетный вход которого соединен с выходом элемента ИЛИ, пятый выход дешифратора соединен с первым входом элемента ИЛИ, информационный выход первого двоичного счетчика соединен с адресными входами блока буферной памяти адреса и блока буферной памяти данных, шестой выход дешифратора соединен через формирователь короткого импульса с единичным входом триггера, нулевой вход триггера cq- единен с входом начальной установки устройства, информационный вход триггера соединен с шиной нулевого потенциала устройства, информационный вход-выход бдрка буферной памяти адреса соединен с двунаправленным входом мультиплексора адреса, информационный вход-выход блока буферной памяти данных соединен с двунаправленным входом мультиплексора данных, информационный вход мультиплексора адреса соединен с вторым информационным входом устройства для подключения к шине адреса отлаживаемой микропроцессорной системы, информационный вход мультиплексора данных соединен с третьим информационным входом устройства, для подключения к шине данных отлаживаемой микропроцессорной системы, информационные выходы мультиплексора адреса и мультиплексора данных соединены соответственно с первым и вторым информационными входами мультиплексора магистралей, отличающееся тем, что, с целью повышения производительности при отладке аппаратно- программных средств микропроцессор0

5

0

5

0

5

0

5

0

5

ных систем, в устройство введены первый селектор, первый регистр, второй двоичный счетчик, схема сравнения, регистр длительности трассы, второй селектор, второй регистр, вычитающий счетчик импульсов, блок буферной памяти состояния шины управления, мультиплексор шины управления, формирователь сигнала записи, формирователь сигнала чтения, причем информационные входы первого регистра, второго регистра и информационный вход вычитающего счетчика импульсов соединены с информационным входом- выходом устройства для подключения к шине данных отлаживающей ЭВМ, седьмой, восьмой и девятый выходы дешифратора соединены соответственно с входами разрешения первого регистра, второго регистра и вычитающего счетчика импульсов, выход первого регистра соединен с входом управления первого селектора, выход второго регистра соединен с входом управления второго селектора, информационные входы первого селектора, второго селектора и мультиплексора шины управления соединены с четвертым информационным входом устройства для подключения к шине управления отлаживаемой микропроцессорной системы, выход первого селектора соединен с вторым ходом элемента И и входом формирователя сигнала записи, выход второго селектора соединен со счетным входом вычитающего счетчика импульсов, выход обнуления которого соединен с тактовым входом триггера, выход которого является первым выходом синхронизации устройства для подключения к входу первого маскируемого запроса прерывания отлаживающей ЭВМ для подключения к входу ожидания отлаживаемой микропроцессорной системы, счетный вход второго двоичного счетчика и вход формирователя сигнала чтения соединены с пятым выходом дешифратора, обнуляющий вход второго двоичного счетчика соединен с четвертым выходом дешифратора, информационный выход второго двоичного счетчика соединен с первым входом схемы сравнения, выход регистра длительности трассы соединен с вторым входом схемы сравнения, информационный вход регистра длитель- ности трассы и адресный вход блока буферной памяти состояния шины управления соединены с информационным вы

ходом первого двоичного гчегчика, выход схемы сравнения является вторым выходом синхронизации устройства для подключения к входу второго маскируемого прерывания отлаживающей ЭВМ, десятый выход дешифратора соединен с обнуляющим входом регистра длительности трассы, выход формирователя сигнала записи соединен с входами -записи бло- ка буферной памяти адреса, блока буферной памяти данных, блока буферной памяти состояния шины управления, с первыми управляющими входами мультиплексора адреса, мультиплексора дан- чых, мультиплексора тины управления и входом разрешения регистра дли

тельности трассы, выход формирователя сигнала чтения соединен с входами чтения блока буферной памяти адреса, блока буферной памяти данных, блока буферной памяти состояния шины управления и вторыми управляющими входами мультиплексора адреса, мультиплексора данных, мультиплексора шины управления, информационный вход-выход блока буферной памяти состояния шины управления и третий информационный вход мультиплексора магистралей соединены соответственно с двунаправленным входом и выходом мультиплексора шины управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1988 |

|

SU1624460A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| Устройство для отладки микропроцессорной системы | 1987 |

|

SU1453408A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство отладки микропрограммных блоков | 1988 |

|

SU1541617A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для отладки программ | 1985 |

|

SU1297064A1 |

| Устройство для запоминания трассы функционирования многопроцессорных систем | 1990 |

|

SU1737454A1 |

Изобретение относится к вычислительной технике и может быть использовано для отладки аппаратно-программных средств микроЭВМ и микропроцессорных систем. Цель изобретения - повышение производительности при отладке аппаратно-программных средств микропроцессорных систем. Устройство для отладки микропроцессорных систем содержит мультиплексоры адреса и данных, первый счетчик, триггер, формирователь короткого импульса, мультиплексор магистралей, элемент ИЛИ, дешифратор, блоки буферной памяти адреса и данных. В устройство введены вычитающий счетчик импульсов, схема сравнения, первый и второй регистры, первый и второй селекторы, мультиплексор шины управления, регистр длительности трассы, блок буферной памяти состояния шины управления, формирователь сигнала записи, формирователь сигнала чтения второго счетчика. 1 ил.

| Патент Великобритании № 14414444, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-08-23—Публикация

1989-09-05—Подача