ОЭ О5

оо

со Од

Изобретение относится к цифровой электроизмерительной технике и может быть применено при построении измерителей активной мощности и энергии йе прерывных и радиоимпульсньк периодических колебаний, а также постоянных сигналов.

Цель изобретения - повышение точности и быстродействия.

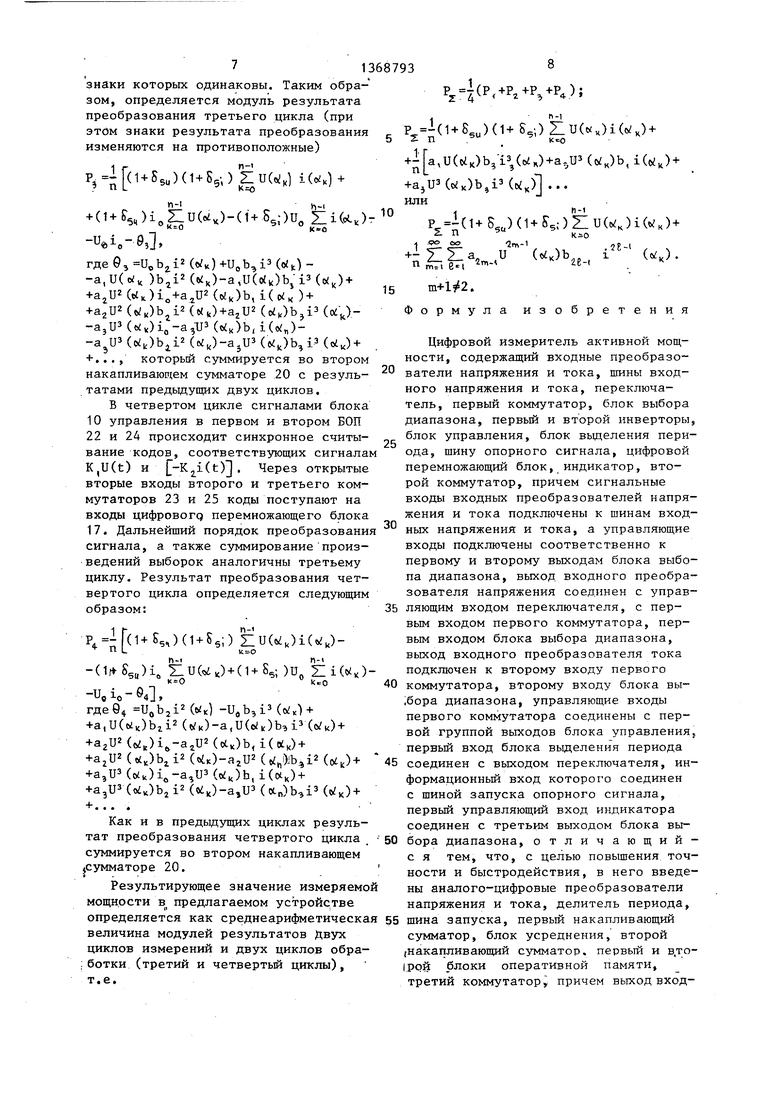

На чертеже приведена структурная схема цифрового измерителя активной мощности.

Цифровой измеритель активной мощности состоит из входного преобразователя 1 напряжения, входного преобразователя 2 тока, шины 3 входного напряжения, шины 4 входного тока, переключателя 5, первого коммутатора 6j блока 7 выбора диапазона, nepjBoro 8 и второго 9 инверторов, блока 10 управления, аналого-цифрового преобразователя (АЦП) 11 напряжения, АЦП 12 тока, делителя 13 периода, блока 14 выделения периода, шины 15 запус- ка шины 16 опорного сигнала, цифрового перемножающего блока 17, первот го накапливающего сумматора 18, блок 19 усреднения, второго накапливающего сумматора 20, индикатора 21,. первого блока 22 оперативной памяти (БОП), второго коммутатора 23, второго блока 24 оперативной памяти, и третьего коммутатора 25, причем сигнальные входы преобразователей 1 и 2 напряжения и тока подключены к шинам 3 и 4 входных сигналов, а управляющие входы - соответственно к первому и второму выходам блока 7 выбора диапазона, выход входного преобразователя 1 напряжения соединен с. управляющим входом переключателя 5, первым входом первого коммутатора 6 и первым входом блока 7 выбора диапазона, выход входного преобразователя 2 тока подключен к второму входу первого коммутатора 6 и второму входу блока 7 выбора диапазона, выход входного преобразователя 1 напряжения через первый инвертор 8 соединен с третьим входом первого коммутатора 6j выход входного преобразователя 2 .тока через второй инвертор 9 подключен к четвертому входу первого коммутатора 6, управляющие входы которого соединены с первой группой выходов блока 10 управления, первый выход первого коммутатора 6 соединен с входом АЦП 11 напряжения и первым

0

0

0

5

входом блока 10 управления, а второй выход - с входом АЦП 12 тока и вторым входом блока 10 управления, первый выход которого соединен с первыми управляющими входами АЦЦ 11 и 12 напряжения и тока, вторые управляющие входы которых соединены с выходом делителя 13 периода и третьим входом блока 10 управления, а их управляющие выходы соединены соответственно с четвертым и пятым входами блока 10 управления, шестой вход которого соединен с входом делителя 13 периода и 5 выходом блока 14 вьщеления периода, первый вход которого соединен с выходом переключателя 5, а второй - с шиной 15 запуска, информационный вход переключателя 5 -соединен с щиной 16 опорного сигнала, вторая группа выходов блока 10 управления соединена с управляющими входами цифрового перемножающего блока 17, вьЬсоды которого соединены с сигнальными входами первого накапливающего сумматора 18, управляющие входы которого соединены с третьей группой выходов блока 10 управления, второй выход которого соединен с управляющим входом блока 19 усреднения, сигнальные входы которого соединены с выходами первого накапливающего сумматора 18, а выходы- с сигнальными входами второго накапливающего сумматора 20, управляющие входы которого соединены с четвертой группой выходов блока 10 управления, а выходы - с сигнальными входами индикатора 21, первьШ управляющий вход которого подключен к третьему выходу блока 7 выбора диапазона, а второй управляющий вход - к третьему выходу блока 10 управления, сигнальные входы первого БОП 22 соединены с выходами АЦП 11 напряжения и с первыми входами второго коммутатора 23, управляющие входы БОП 22 соединены с пятой гр уппой выходов блока 10 управления, управляющий вход соединен с четвертым выходом блока 10 управления и с управляющим входом второго БОП 24, а выходы - с вторыми входами второго коммутатора 23, управляющий вход которого соединен с пятьм выходом блока 10 управления и управляющим входом третьего коммутатора 25, а выходы подключены к первым входам цифрового перемножающего блока 17, вторые входы которого соединены с выходами третьего коммутатора 25,

5

0

5

0

5

первые входы которого соединены с выходами АЦП 12 тока и входами второго БОП 24, а вторые входы - с выходами второго БОП 24, управляющие входы которого соединены с шестой группой выходов блока 10 управления, - . Цифровой измеритель активной мощности работает следующим образом.

второй входы блока 10 управления, В зависимости от знака этих сигналов и номера цикла измерения блок 10 управления изменяет режим работы первого накапливающего сумматора 18 (режим суммирования или вычитания),

Управляющим импульсом делителя 13 периода через вторые управляющие

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель электрической энергии | 1990 |

|

SU1746322A1 |

| Цифровой измеритель электрической энергии | 1990 |

|

SU1749842A1 |

| Устройство для измерения температуры | 1987 |

|

SU1472771A1 |

| Устройство для симметрирования токов трехфазных четырехпроводных сетей | 1990 |

|

SU1758773A1 |

| Устройство для измерения температуры | 1986 |

|

SU1362951A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ МНОГОФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА В КОД ДЛЯ УСТРОЙСТВ ЭЛЕКТРОМЕХАНОТРОНИКИ | 1994 |

|

RU2094945C1 |

| Устройство для измерения активной и реактивной мощности | 1990 |

|

SU1780035A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Адаптивный корректор | 1987 |

|

SU1417197A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1750060A1 |

Изобретение относится к цифровой измерительной технике и может быть использовано при построении измерителей активной мощности и энергии непрерывных и радиоимпульсных периодических колебаний, а также постоянных сигналов. Целью изобретения является повьшение точности и быстродействия. Устройство содержит преобразователь 1напряжения, входной преобразователь 2тока, шины 3 выходного напряжения, шины 4 входного тока, переключатель 5, коммутаторы 6, 23 и 25, блок 7 выборки данных, инверторы 8 и 9, блок. 10 управления, аналого-цифровые, преобразователи 11 и 12 напряжения и тока соответственно, делитель 13 периода, блок 14 вьщеления периода, шины 15.запуска, шины 16 опорного сигнала, цифровой перемножающий блок 17, сум- маторы 18 и 20, индикатор 21, блоки 22 и 24 оперативной памяти. Поставленная цель достигается предложенным схемным построением и новыми функциональными связями устройства. 1 ил. €

Через переключатель 5 на вход бло ка 14 вьщеления периода поступает либо выходной сигнал входного преобразователя 1 напряжения (t) при синусоидальной форме последнего, либо сигнал с шины 16 - Up, , частота которого равна основной частоте входного сигнала, когда напряжение U(t) периодично, но не синусоидально, В последнем случае измеряется активная мощность суммы гармоник. При измерении мощности постоянного тока время измерения определяется периодом напряжения сетевой помехи. При этом на вход блока 14 выделения периода подается либо переменное напряжение питания прибора через шину 16 опорного сигнала вместо UQJ , либо вьщеленное на выходе преобразователя 1 переменное напряжение помехи, которое поступает на вход блока 14 выделения периода через первый вход переключателя 5, С приходом запускакщего импульса на шину 15 запуска на выходе блока 14 вьщеления периода формируются последовательно во времени импульсы дли- тельностью рТ (Т - период колебаний входного сигнала), Первый из указанных импульсов, поступая на вход делителя 13 периода, делится последним на п равных частей. При этом определяются моменты запуска обоих АЦП, т,е, отбора информации. Вторым импульсом блока 14 выделения периода через первую группу выходов блока 10 управления замыкаются на время рТ первый и третий ключи первого коммутатора 6, При этом в первом цикле измерений на вход аналого-цифрового преобразователя 11 напряжения с выхода входного преобразователя 1 напряжения подается в определенном масштабе напряжение K,U(t), а на вход аналого-цифрового преобразователя 12 тока - сигнал с -выхода входного преобразователя 2 тока, пропорциональный току (t),

Одновременно указанные сигналы подаются соответственно на первый и

10 входы запускаются АЦП 11 и 12 напря15

жения тока. По приходу сигналов готовности обоих АЦП на четвертый и пятый входы блока 10 управления последним формируются через вторую и пятую группу выходов, а также четвертый и пятый выходы управляющие импульсы, которыми измеренные мгновенные значения напряжения и тока через открытые первые входы второго и третьего коммутаторов 23 и 25 перезаписываются во входные регистры цифрового перемножающего блока 17, а также записьшаются с определенными адресами в ячейки памяти первого и второго БОП 22 и 24, После этого сигналом блока 10 управления через его первый выход производится сброс обоих АЦП, Эквиваленты мгновенных значений периодических сигналов U (oij,) и 30 i (), преобразованные посредством АЦП 11 И 12 с учетом их погрешностей, можно записать в виде полиномов, которые представляют ряды Маклорена, и ()Uo+()U(oiK)+ajU2 U) -+

20

25

35

40

45

50

В5

+а,) + ...(в(); i (, + (1 + 9i )i()+bji4c K) + +bji3 (oix) + . , .+bni (Ык) , где (1+Ssu)a, ;аг;а ; . . ,,a и (1+ Sg; ) b , ,b j,,,, ,b n - коэффициенты ряда Маклорена; U и ig -первые члены ряда Маклорена, которые определяют аддитивные составляющие погрешности АЦП напряжения и тока соответственно;

5, - коэффициенты, характеризующие мультипликативные составляющие погрешности АЦП напряжения и тока соответственно,

Результат перемножения записывается в выходном регистре цифрового перемножающего блока 17, Управляющим сигналом блока 10 управления через третью группу выходов происходит перезапись этого результата во входной регистр первого накапливающего сумматора 18, Через интервал времени.

suHS

10

равный , запускаются аналого- цифровые прЁобразователи 11 и 12 напряжения и тока и подцикл измерений., записи в оперативную память и преобразований вновь повторяется. После повторения п-го цикла ключи коммутаторов 6, 23 и 25 размыкаются, и первый цикл измерений заканчивается. При этом в выходном регистре первого накапливающего сумматора 18 записывается результат, в котором просуммированы все произведения выборок с одинаковыми знаками и вычтены все произведения выборок с -противоположными знаками. Последнее возможно при сдвиге фаз ме)вду сигналами напряжения и тока. С помощью блока 19 усреднения осуществляется деление результата измерения на количество выборок п. Зна-2о

При этом на вход АЦП 11 напряжения подается напряжение -K,U(t) , а н вход АЦП 12 тока - сигнал, пропорц

g нальный току (t)J ..Дальнейший порядок измерения во втором цикле аналогичен первому. При этом через открытые первые входы второго и тре его коммутаторов 23 и 25 коды АЦП и 12 напряжения и тока перезаписыв ются во входные регистры цифрового перемножающего блока 17, а также з писываются в ячейки памяти с опред ленными адресами первого и второго

15 БОИ 22 и 24. Порядок суммирования вычитания произведений выборок так аналогичен порядку первого цикла и мерений. Результат измерения второ цикла определяется следующим образ

FIC; J па rVLJJJLjn ЧС - 1 П и L1. ЛО. , -

чение п целесообразно выбирать равным ( Sj; ) 21 и(.) i (о)41 /„„„ , 1 о о ч ..,. Г1

2 (где ,2,3,...), поскольку в этом случае деление с помощью блока 9 усреднения сводится к сдвигу запятой на число двоичных разрядов i, Та- 25 КИМ образом, выходной сигнал перво.го накапливающего сумматора в виде двоичного кода со сдвинутой запятой с приходом управляющего сигнала через четвертую группу выходов блока 10 управления перезаписывается во второй накапливающий сумматор 20. При этом результат измерения первого цикла записывается

П-1

-(i + Ssc,)io Z:tJ(K)-(i + 5;)Uo ZliC + е,.

0

k-o

+Uoio

30

где О, Ык) -Uob,i3(oi,)- -a,U(oi.)b,i2 (,и(ы,)Ь, i (ы.) + +a,U2 (ciJio-a.jU2 (ciJb,i() + (Ык)Ь2.12 (ti.) ( (cij

-a3U3(oi)io+a3U4oI.K)b,i(tiK) (б6,)Ьг i (6i,) (о(,,)ь,1з ()

+ . . . . .

Результат измерения второго цик суммируется во втором накапливающе сумматоре.

|5K+0 + S5,)U(ci,)-«-aiU4 i.) +

+a,,U3 (cij + ,.. ( ) х1(ы.к)+Ь21ЧЫх)+Ьз1Чо к) + . . .

.,.b,i(oi,) i:r(1+55,)(1+S5;)U(6iK)

-J til К O

xi(cix) + (1 + s, )U(oi)i, -Hd + Sg; )i(odK)Uo + -i-D, „ + Q i (1 + &5,) (1 + gi) E и (o,)

(ij+(i+S5,)i, z:u(ot,,)+(i;.,)u,s:

f. OK - O

H i(oi)+Upig+e,,(2)

где, .i4oiK)+Uob,i4VK) + +a, UCciJb i (Ык)+а,и(ы,()Ьэ1з (oi.J + Ча ШЧсгЛ +а иЧо Ь.КЫк) + ( (oi) (ы,)Ь i ( «к)- +aзUЗ ( otj i (о1к)Ь, i(oi) + («K) () («{к)Ьэ1з (ciK) + + , ,.

Bo втором цикле измерений, который начинается сразу после первого, на время рТ, замыкаются второй и четвертый ключи первого коммутатора 6,

При этом на вход АЦП 11 напряжения подается напряжение -K,U(t) , а на вход АЦП 12 тока - сигнал, пропорциональный току (t)J ..Дальнейший порядок измерения во втором цикле аналогичен первому. При этом через открытые первые входы второго и третьего коммутаторов 23 и 25 коды АЦП 11 и 12 напряжения и тока перезаписываются во входные регистры цифрового перемножающего блока 17, а также записываются в ячейки памяти с определенными адресами первого и второго

БОИ 22 и 24. Порядок суммирования и вычитания произведений выборок также аналогичен порядку первого цикла измерений. Результат измерения второго цикла определяется следующим образом:

5

П-1

-(i + Ssc,)io Z:tJ(K)-(i + 5;)Uo ZliC.)- + е,.

0

k-o

+Uoio

0

5

0

где О, Ык) -Uob,i3(oi,)- -a,U(oi.)b,i2 (,и(ы,)Ь, i (ы.) + +a,U2 (ciJio-a.jU2 (ciJb,i() + (Ык)Ь2.12 (ti.) ( (cij-a3U3(oi)io+a3U4oI.K)b,i(tiK) (б6,)Ьг i (6i,) (о(,,)ь,1з () +

+ . . . . .

Результат измерения второго цикла суммируется во втором накапливающем сумматоре.

На этом процесс, включающий два цикла измерений входных сигналов, прекращается. Два последующих цикла (третий и четвертый) включают обработку результатов измерений входньпс сигналов первых двух циклов,.запи-- санных в первом и втором БОП22и24.

При этом в третьем цикле с помощью определенных сигналов блока 10

5-управления в первом БОП 22 происходит синхронное считывание кодов, соответствующих сигналу -K,U(t), а о втором БОП 24 - сигналу (t). Через открытые вторые входы второго

0 и третьего коммутаторов 23 и 25 сигналы в виде двоичных кодов поступают на входы цифрового перемножающего блока 17. Дальнейший порядок преобразования аналогичен предьщущим цикg лам за исключением того, что в первом накапливающем сумматоре происходит суммирование произведений выборок, знаки которых противоположны, и вычитание произведений выборок.

71368

знаки которых одинаковы. Таким образом, определяется модуль результата преобразования третьего цикла (при этом знаки результата преобразования изменяются на противоположные)

П-1

P,

n-i

h-i

+ ()((1+55;)(о(.,)-U«,io-0,l,

где 0, (Ык) +Uob,i3 (Ы) - -а,и(с )Ь.,)-а,и(о()((Х,) + +a,,U4tt)i,+a,,U4oiJb, ) +

+агиЧв/к)Ь.Р(б)+аги2(с,)Ь51Чс я - (ы,)1о-а,БЗ (Ы,)Ь, i(« J-ajU4oi,)b.j.i4ei,,)-ajU4e4)b,i3UJ + +..., который суммируется во втором накапливающем сумматоре 20 с резуль- татами предьщущих двух циклов,

В четвертом цикле сигналами блока 10 управления в первом и втором БОГТ 22 и 24 происходит синхронное считывание кодов, соответствующих сигнала K,U(t) и ). Через открытые вторые входы второго и третьего коммутаторов 23 и 25 коды поступают на входы цифровогд перемножающего блока 17. Дальнейший порядок преобразовани сигнала, а также суммирование произведений выборок аналогичны третьему циклу. Результат преобразования четвертого цикла определяется следующим образом:

()(1+55;) z:uuji(.i,)п

-()i, Z.UU) + ()U, )

-и, 10-64,

гдеб Uobji2 (ы,) -Ueb,) + +a,U(eiK)bii2 (в;к)-а,и(в Jb, (СУ:К) + (о,)1 -аги2 (cijb, i(ot,) + +а,иЧ«(к)Ч12 (о О-агШ («i. (oi,)+ +a, (of ,U3 (oi Jb, 1(о1к) + +азиз (oijbj 12 (oi J-a,U3 (ocn)b,i3 (0/) + + . . . .

Как и в предьщзшщх циклах результат преобразования четвертого цикла суммируется во втором накапливающем сумматоре 20.

Результирующее значение измеряемо мощности в предлагаемом устройстве

определяется как среднеарифметическая55 шина запуска, первый накапливающий

величина модулей результатов Двухсумматор, блок усреднения, второй

циклов измерений и двух циклов обра-(Накапливающий с т матор. первый и в,тоботки (третий и четвертьй циклы), |рой блоки оперативной памяти,

т.е.третий коммутатору причем выход входР |(Р, +Р);

Z 4

((1+S5;)i:U(«,)i() +

2 п

K4D

,и(Ык)Ь, Ц(,)+а.и5 (, i(}- +азиз(огк)Ь,1Чо) ...

или

1

П-1

.))1(к)+

2- п Ц..О

.)Ь.„ . (J.

пЬеГ,- . Формул

26-1

изобретения

0

Цифровой измеритель активной мощности, содержащий входные преобразо5

0

ватели напряжения и тока, шины входного напряжения и тока, переключатель, первый коммутатор, блок выбора диапазона, первый и второй инверторы, блок управления, блок вьщеления периода, шину опорного сигнала, цифровой перемножающий блок, индикатор, второй коммутатор, причем сигнальные входы входных преобразователей напряжения и тока подключены к шинам входных напряжения и тока, а управляющие входы подключены соответственно к первому и второму выходам блока выбо- па диапазона, выход входного преобразователя напряжения соединен с управ5 ляющим входом переключателя, с первым входом первого коммутатора, пер- вьм входом блока выбора диапазона, выход входного преобразователя тока подключен к второму входу первого

0 коммутатора, второму входу блока вы- ,бора диапазона, управляющие входы первого коммутатора соединены с первой группой выходов блока управления, первьм вход блока вьщеления периода

5 соединен с выходом переключателя, информационный вход которого соединен с шиной запуска опорного сигнала, первый управляющий вход индикатора соединен с третьим выходом блока вы0 бора диапазона, отличающий- с я тем, что, с целью повьш1ения точности и быстродействия, в него введены аналого-цифровые преобразователи напряжения и тока, делитель периода.

ного преобразователя напряжения через первый инвертор соединен с третьим входом первого коммутатора, выход входного преобразователя тока через второй инвертор соединен с четвертым входом первого коммутатора, первый выход первого коммутатора соединен с входом аналого-цифрового преобразователя напряжения и первым входом блока управления, а второй выход - с входом аналого-цифрового преобразователя тока и вторым входом блока управления, первый выход которого соединен с первыми управляющими входами аналого- цифровых преобразователей напряжения и тока, вторые управляющие входы которых соединены с выходом делителя периода и с третьим входом блока управления, а их управляющие выходы соединены соответственно с четвертым и пятым входами блока управления, шестой вход которого соединен с входом делителя периода и выходом блока выделения периода, второй вход которого 25 коммутатора, а выходы подключены к

соединен с шиной запуска, вторая группа выходов блока управления соединена с управляющими входами цифрою вого перемножающего блока, выходы которого соединены с сигнальными входами первого накапливающего сумматора, управляющие входы которого соединены с третьей группой выходов блока управления, второй выход которого соединен с управляющим входом блока усреднения, сигнальные входы которого

соединены с выходами первого накапливающего сумматора, а выходы - с сигнальными входами второго накапливающего сумматора, управляющие входы которого соединены с четвертой группой выходов блока управления, а выходы соединены с сигнальными входами индикатора, второй управляющий вход которого подключен к третьему выходу блока управления, сигнальные входы первого блока оперативной памяти соединены с выходами аналого-цифрового преобразователя напряжения и с первыми входами второго коммутатора, управляющие входы - с пятой группой выходов блока управления, управляющий вход - с четвертым выходом блока управления и с управляющим входом второго блока оперативной памяти, а выходы - с вторыми входами второго коммутатора, управляющий вход которого соединен с пятым выходом блока управления и управляющим входом третьего

первым входам цифрового перемножающего блока, вторые входы .которого соединены с выходами третьего коммутатора, первые входы которого соединены с выходами аналого-цифрового преобразователя тока и с входами второго блока оперативной памяти, а вторые входы - с выходами второго блока оперативной памяти, управляющие входы которого соединены с шестой группой выходов блока управления.

| Одноканальное устройство сравнения амплитуд и фаз двух переменных напряжений | 1978 |

|

SU790250A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой измеритель мощности | 1982 |

|

SU1092422A2 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-01-23—Публикация

1985-12-11—Подача