45 «

Изобретение относится к вычислительной и цифровой измерительной технике и может быть использовано для преобразования цифровых величин в аналоговые.

Известен цифроаналоговый преобразователь, содержащий задатчик кодов, блок питания, генератор, преобразователь кодов, сумматор, блок деления, блок сравнения, блок коррекции, входную шину, первую и вторую выходные шины.

Недостатком данного преобразователя является сложность схемы и необходимость использования внешнего высокоточного аналого-цифрового преобразователя, работающего в комплексе с данным цифроана- логовым преобразователем.

Известен также цифроаналоговый преобразователь, содержащий основной, -вспомогательный и дополнительный циф- роаналоговые преобразователи, первый, второй и третий регистры, вычислительный блок, аналоговое суммирующее устройство, блок сравнения, блок управления, вход и выход устройства.

Недостатком данного цифроаналогово- го преобразователя является незначительное повышение линейности устройства.

Наиболее близким по технической сущности к изобретению является ТГифроаналй- говый преобразователь, содержащий информационный вход устройства, первый цифровой коммутатор, арифметико-логическое устройство, первый регистр, второй цифровой коммутатор, первый и второй управляющие входы устройства, блок управления, регистр последовательного приближения, блок постоянной памяти, блок оперативной памяти, второй регистр, третий цифровой коммутатор, регистр сдвига, основной цифроаналоговый преобразователь, блок сравнения, вспомогательный цифроаналоговый преобразователь и выход устройства, причем информационный вход устройства соединен с первым информационным входом первого цифрового коммутатора, второй информационный вход которого соединен с первым выходом арифметико-логического устройства, управляющий вход соединен с четвертым выходом блока управления, выход соединен с информационным входом регистра, первый управляющий вход которого соединен с первым выходом блока управления, а выход соединен с первым информационным входом арифметико-логического устройства и информационным входом блока оперативной памяти, первый и второй управляющие входы устройства соединены сботв тствен- но с первым и вторым входами блока управления, пятый выход которого подключен к

управляющему входу арифметико-логического устройства, второй информационный вход которого соединен с выходом цифрового коммутатора, управляющий вход которого соединен с шестым выходом блока управления, первый и второй информационный входы подключены соответственно к выходам блока постоянной памяти и блока оперативной памяти, седьмой выход блока

0 управления соединен с первым управляющим входом регистра последовательного приближения, восьмой и девятый выходы блока управления соединены соответственно с первым и вторым управляющими

5 входами блока оперативной памяти, десятый выход блока управления соединен с адресными входами блока постоянной и оперативной памяти, одиннадцатый выход блока управления соединен с вторыми уп0 равляющйми входами регистра последовательного приближения и регистра сдвига, первый управляющий вход которого соединен с третьим выходом блока управления, двенадцатый и тринадцатый выходы кото5 рого соединены соответственно с первым и вторым управляющими входами третьего цифрового коммутатора, первый и второй информационные входы которого подключены соответственно к шинам единичного и

0 нулевого потенциала, третий информационный вход подключен к выходу блока сравнения, четвертый информационный вход подключен к второму выходу арифметико- логического устройства, выход третьего циф5 рового коммутатора соединен с вторым управляющим входом регистра и информационным входом регистра последовательного приближения, выход которого соединен с информационным входом второго регистра,

0 управляющий вход которого соединен с вторым выходом блока управления, выход второго регистра соединен с входом основного цифроаналогового преобразователя, выход которого соединен с выходом устройства и

5 вторым входом блока сравнения, первый вход которого подключен к выходу вспомогательного цифроаналогового йреобразова- теля, вход которого соединен с выходом регистра сдвига.

0 Недостатком данного цифроаналогового преобразователя является низкая точность при функционировании в широком температурном диапазоне. Объясняется это влиянием погрешностей точных весов

5 корректируемых разрядов при определении кодов реальных еесоз корректируемых разрядов. Уменьшить же количество некорректируемых разрядов (чтобы их температурным дрейфом можно было пренебречь) в известном устройстве нельзя вследствие

адекватного увеличения количества корректируемых разрядов, соответствующего уменьшения веса младшего корректируемого разряда и возможого нарушения соответствия между выходными сигналами основного и вспомогательного цифроана- логовых преобразователей при самоповерке.

Цель изобретения - повышение точности устройства в широком температурном диапазоне.

Поставленная цель достигается тем, что в цифроаналоговый преобразователь, содержащий вспомогательный преобразователь кода в ток, вычислительный блок, информационные входы которого являются входной шиной преобразуемого кода, группа управляющих входов подключена к соответствующим выходам группы выходов блока управления, а управляющие входы - с первого по шестой включительно соединены с выходом с первого по шестой блока управления, первый и второй входы которого являются соответственно первой и второй входными шинами управления, а седьмой выход соединен с входом синхронизации первого регистра последовательного приближения, информационный вход которого подключен к выходу цифрового коммутатора, а выходы соединены с соответствующими информационными входами регистра, вход управления которого соединен с восьмым выходом блока управления, а выходы соединены с соответствующими входами основного преобразователя кода в ток, выход которого соединен с первым входом блока сравнения токов и является первой выходной шиной, девятый и десятый выходы блока управления цифрового коммутатора, а одиннадцатый и двенадцатый выходы подключены соответственно к входу записи и входу синхронизации регистра сдвига, дополнительно введены преобразователь тока в напряжение, блок деления токов, элемент И, блок постоянной памяти, счетчик и второй регистр последовательного приближения, информационные выходы которого соединены с соответствующими входами вспомогательного преобразователя кода в ток, информационный вход объединен с информационным входом первого регистра последовательного приближения, а вход синхронизации и управляющий выход соединены соответственно с тринадцатым выходом и третьим входом блока управления, четырнадцатый и пятнадцатый выходы которого соединены соответственно с первым и вторым входами управления блока деления токов, информационный вход которого соединен с выходом вспомогательного преобразователя кода в ток, а выход объединен с выходом основного преобразователя кода в ток и соединен с входом преобразователя тока в напряжение, 5 выход которого является второй выходной шиной, второй вход блока сравнения токов соединен с шиной нулевого потенциала, а выход соединен с первым входом элемента И и четвертым входом блока управления,

0 шестнадцатый выход которого соединен с вторым входом элемента И, выход которого подключен к первому информационному входу цифрового коммутатора, второй информационный вход которого соединен с

5 выходом регистра сдвига, информационные входы которого подключены к соответствующим выходам блока постоянной памяти, входы которого подключены к соответствующим выходам счетчика, входы сброса и

0 синхронизации которого соединены соответственно с семнадцатым и восемнадцатым выходами блока управления, девятнадцатый, двадцатый и двадцать первый, выходы которого соединены соответст5 венно с седьмым управляющим входом вычислительного блока, с третьим управляющим и третьим информационным входами цифрового коммутатора, пятый вход соединен с управляющим выходом первого реги0 стра последовательного приближения, а шестой вход соединен с выходом вычислительного блока.

Вычислительный блок: выполнен в виде арифметико-логического устройства, перво5 го и второго цифровых коммутаторов, регистра, блока постоянной памяти и блока оперативной памяти, выходы которого соединены с соответствующими первыми информационными входами первого

0 цифрового коммутатора, первый и второй управляющие входы являются соответственно первым и вторым управляющими входами блока, а адресные входы объединены с соответствующими адресными входами

5 блока постоянной памяти и являются соответствующими входами группы управляющих входов блока, выходы блока постоянной памяти подключены к соответствующим вторым информационным вхо0 дам первого цифрового коммутатора, управляющий вход которого является четвертым управляющим входом блока, а выходы соединены с первыми информационными входами арифметико-логического

5 устройства, управляющий вход и выход которого являются соответственно пятым управляющим входом и выходом блока, вторые информационные входы подключены к соответствующим выходам регистра и объединены с информационными входами

блока оперативной памяти, а группа выходов соединена с соответствующими первыми информационными входами второго цифрового коммутатора, вторые информационные входы иуправляющий вход которого являются соответственно информационными входами и шестым управляющим входом блока, а выходы соединены с соответствующими информационными входами регистра, первый и второй управляющие входы которого являются соответственно третьим и седьмым управляющими входами блока.

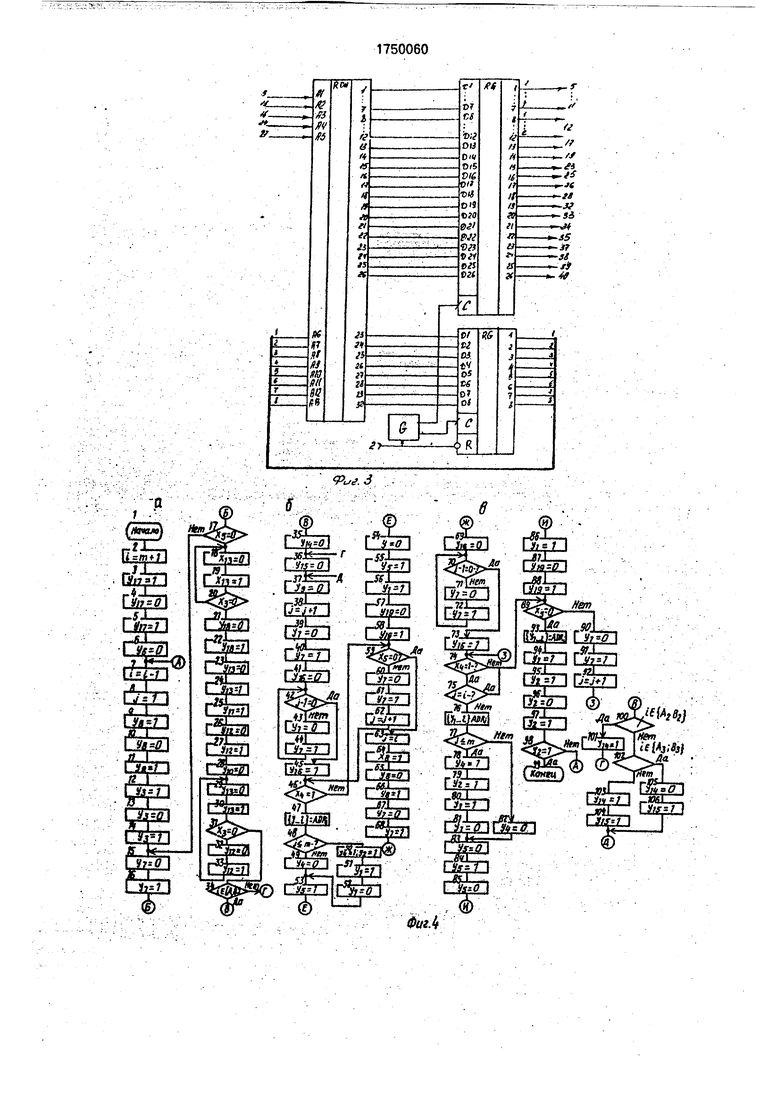

Блок управления выполнен в виде постоянного запоминающего устройства, первого и второго регистров и генератора импульсов, вход которого объединен с входом обнуления первого регистра и является .первым входом блока, а первый и второй выходы соединены с входами синхронизации первого и второго регистров, соответст- венно, информационные входы второго регистра соединены с соответствующими первыми выходами постоянного запоминающего устройства, вторые выходы которого соединены с соответствующими информационными входами первого регистра, выходы которого подключены к соответствующим входам группы адресных входов постоянного запоминающего устройства, адресные входы с первого по пятый которого являются соответственно вторым, шестым, пятым, третьим и четвертым входами блока, выходы с первого по седьмой второго регистра являются соответственно первым, вторым, третьим, девятнадцатым, четвертым, пятым и шестым выходами блока, выходы с восьмого по двенадцатый являются группой выходов блока, тринадцатый и четырнадцатый выходы второго регистра являются соответственно седьмым и восьмым выходами блока, выходы с пятнадцатого по восемнадцатый являются соответственно с тринадцатого по шестнадцатый выходами блока, выходы с девятнадцатого по двадцать шестой второго регистра являются соответственно девятым, десятым, двадцатым, двадцать первым, одиннадцатым, двенадцатым, семнадцатым и восемнадцатым выходами блока.

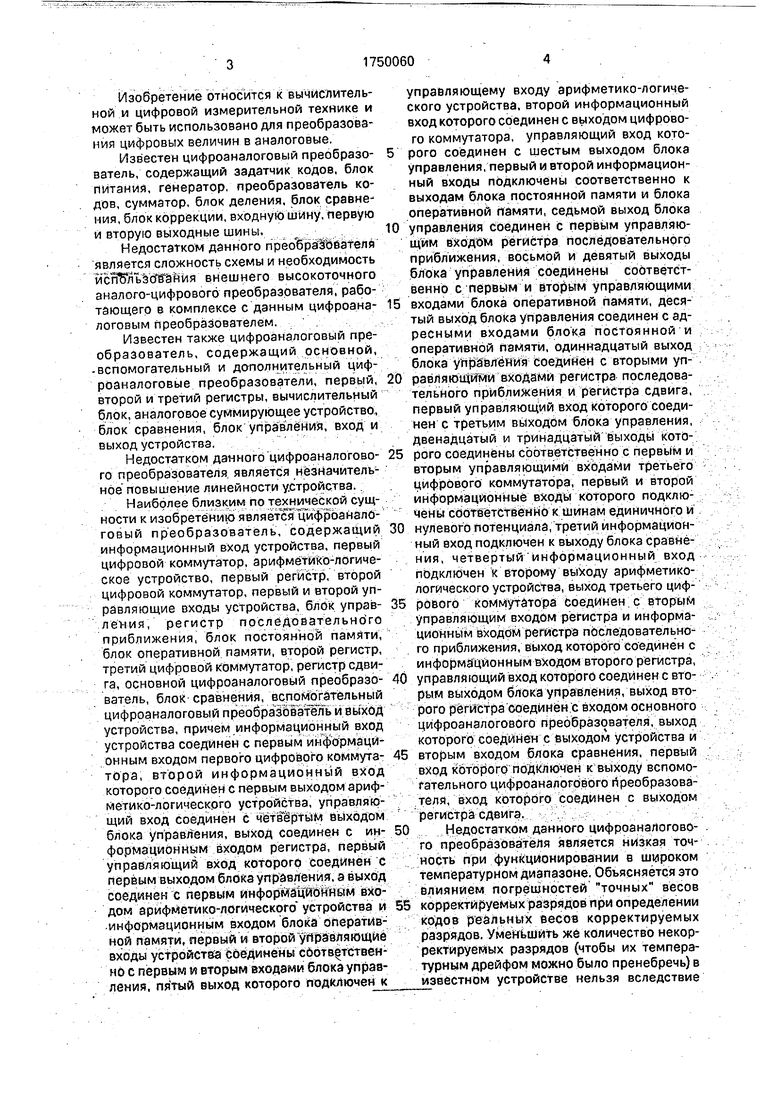

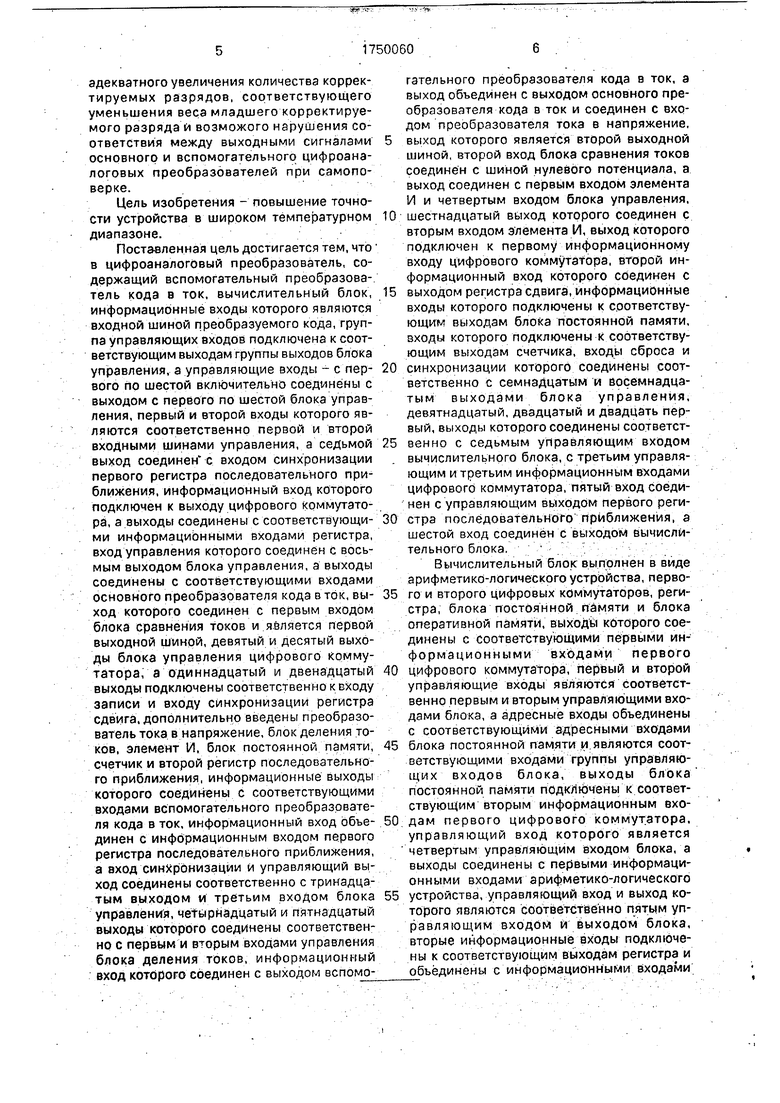

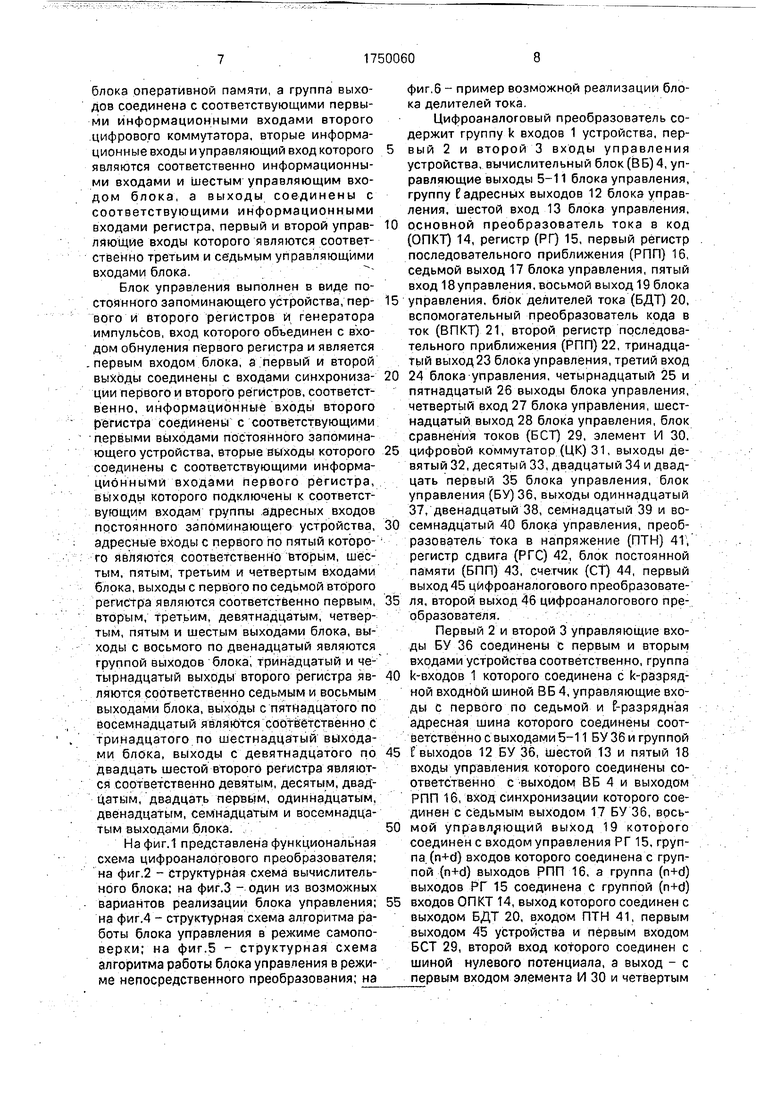

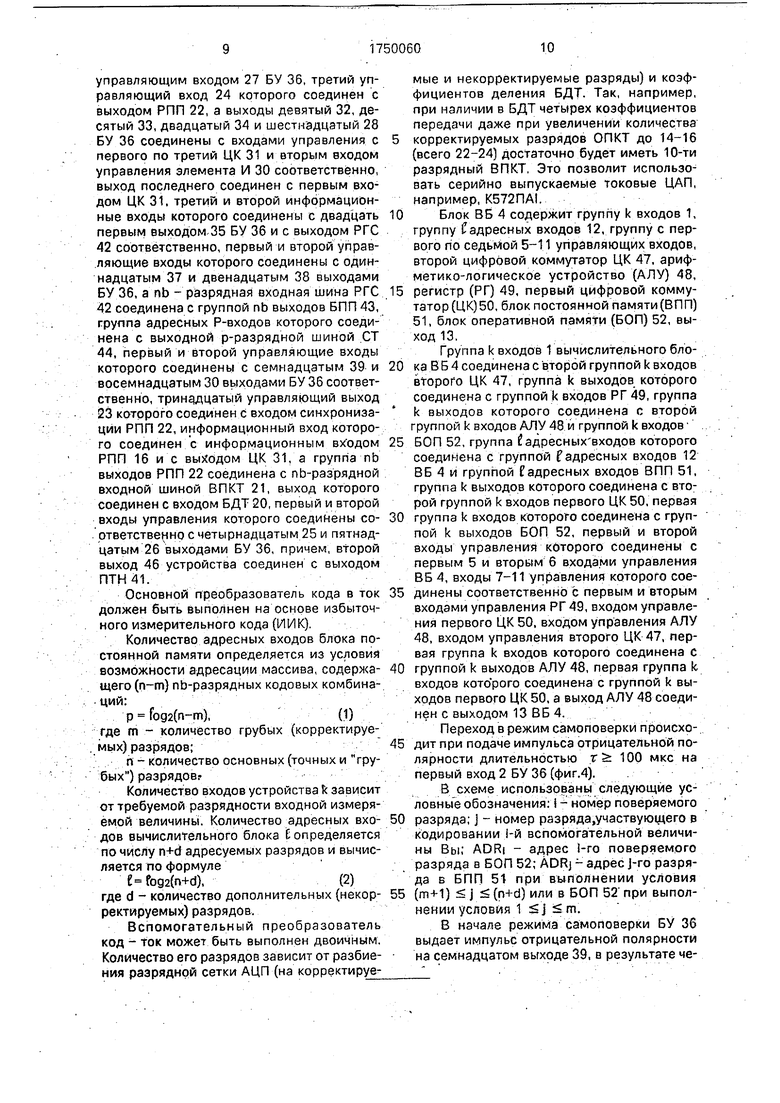

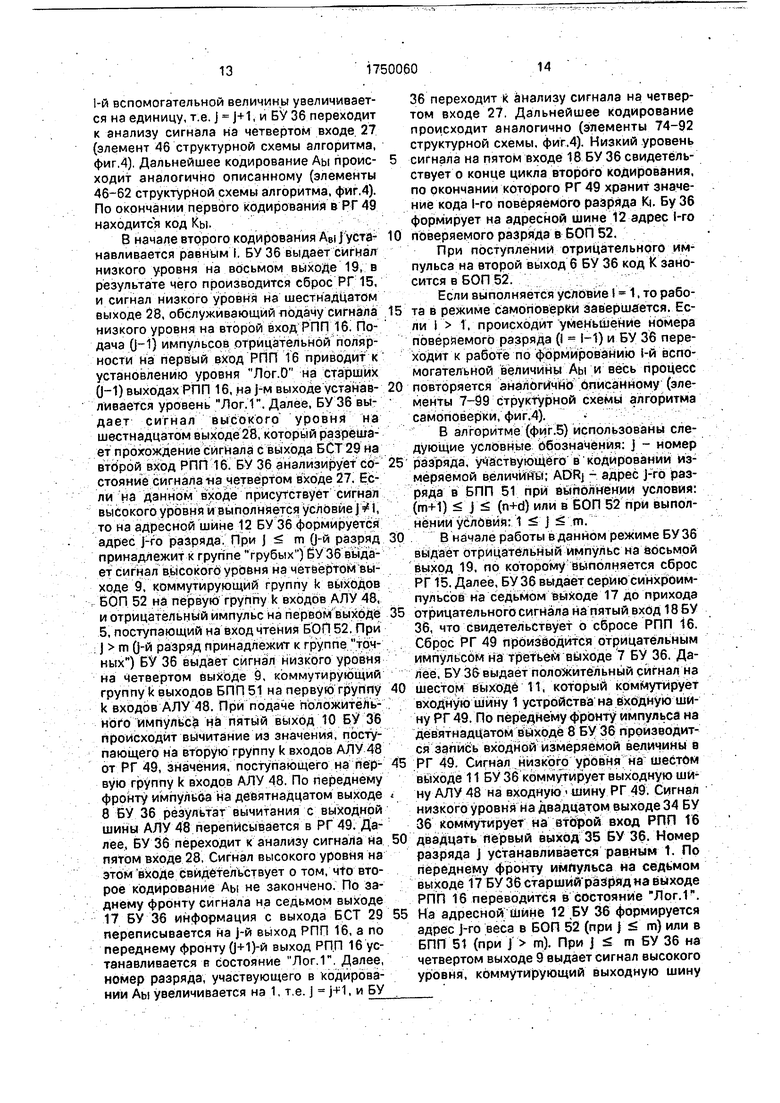

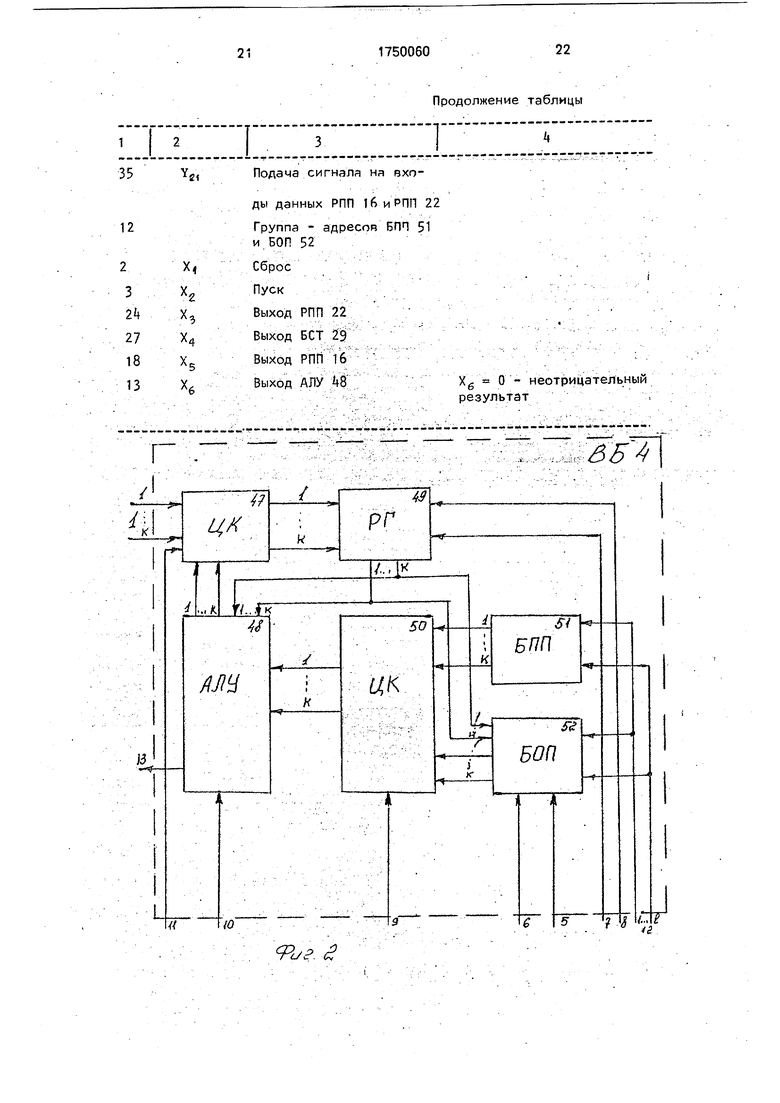

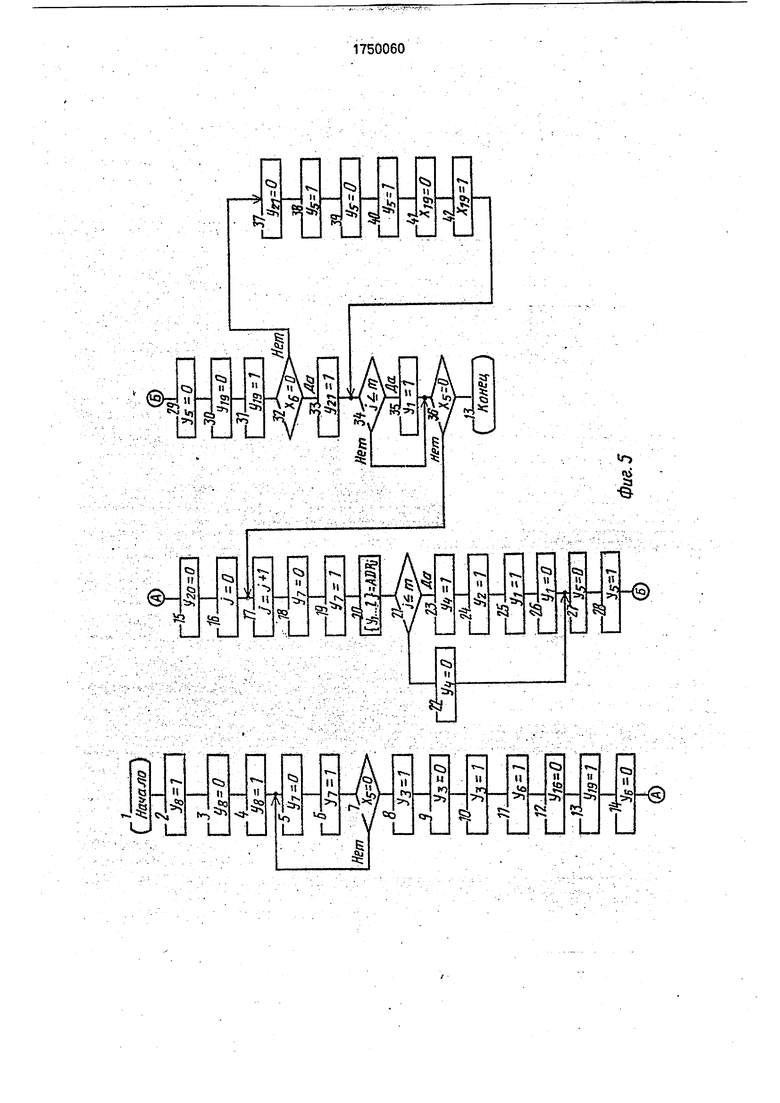

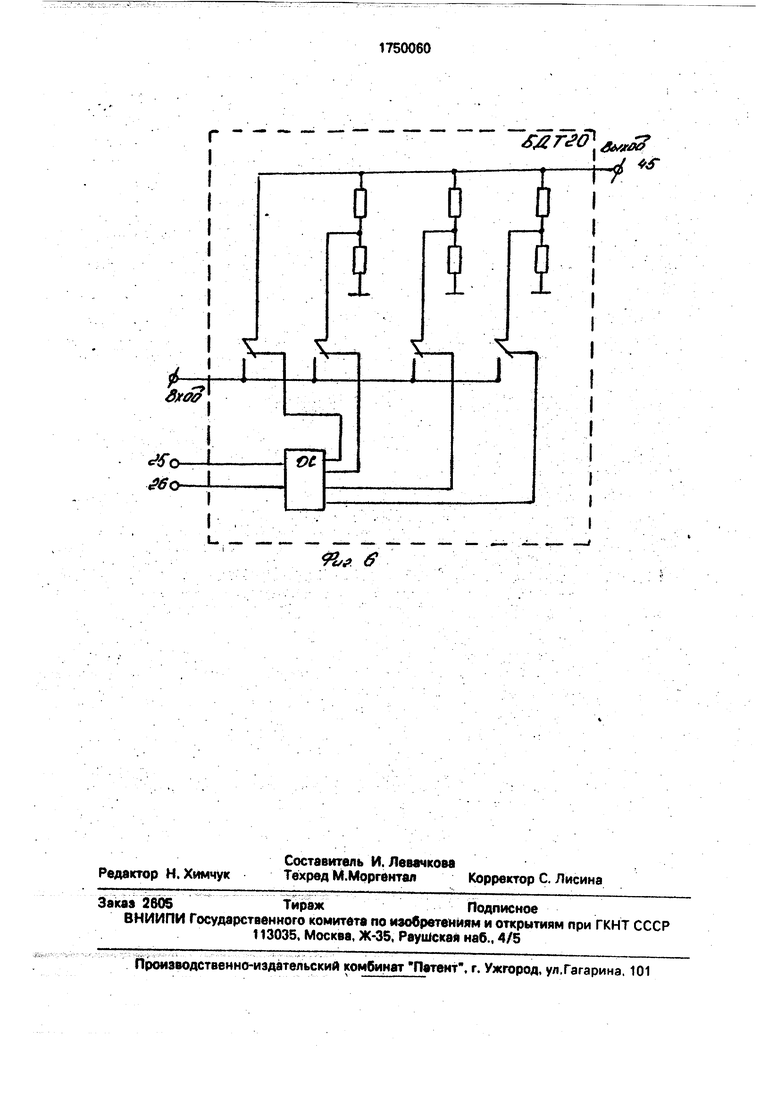

На фиг.1 представлена функциональная схема цифроаналогового преобразователя; на фиг.2 - Структурная схема вычислительного блока; на фиг.З - один из возможных вариантов реализации блока управления; на фиг.4 - структурная схема алгоритма работы блока управления в режиме самоповерки; на фиг.5 - структурная схема алгоритма работы блока управления в режиме непосредственного преобразования; на

фиг 6 - пример возможной реализации блока делителей тока

Цифроаналоговый преобразователь содержит группу k входов 1 устройства, первый 2 и второй 3 входы управления устройства, вычислительный блок (ВБ) 4, управляющие выходы 5-11 блока управления, группу Ј адресных выходов 12 блока управления, шестой вход 13 блока управления,

0 основной преобразователь тока в код (ОПКТ) 14, регистр (РГ) 15, первый регистр последовательного приближения (РПП) 16, седьмой выход 17 блока управления, пятый вход 18управления, восьмой выход 19 блока

5 управления, блок делителей тока (БДТ) 20, вспомогательный преобразователь кода в ток (ВПКТ) 21, второй регистр последовательного приближения (РПП) 22, тринадцатый выход 23 блока управления, третий вход

0 24 блока управления, четырнадцатый 25 и пятнадцатый 26 выходы блока управления, четвертый вход 27 блока управления, шестнадцатый выход 28 блока управления, блок сравнения токов (БСТ) 29, элемент И 30,

5 цифровой коммутатор (ЦК) 31, выходы девятый 32, десятый 33, двадцатый 34 и двадцать первый 35 блока управления, блок управления(БУ)36, выходы одиннадцатый 37, двенадцатый 38, семнадцатый 39 и во0 семнадцатый 40 блока управления, преобразователь тока в напряжение (ПТН) 41, регистр сдвига (РГС) 42, блок постоянной памяти (БПП) 43, счегчик (СТ) 44, первый выход 45 цифроаналогового преобразовате5 ля, второй выход 46 цифроаналогового преобразователя.

Первый 2 и второй 3 управляющие входы БУ 36 соединены с первым и вторым входами устройства соответственно, группа

0 k-входов 1 которого соединена с k-рэзряд- ной входной шиной ВБ 4, управляющие входы с первого по седьмой и С-разрядная адресная шина которого соединены соответственно с выходами 5-11 БУ 36 и группой

5 f выходов 12 БУ 36, шестой 13 и пятый 18 входы управления которого соединены соответственно с выходом ВБ 4 и выходом РПП 16, вход синхронизации которого соединен с седьмым выходом 17 БУ 36, вось0 мой управляющий выход 19 которого соединен с входом управления РГ 15, группа (n-f-d) входов которого соединена с группой (n+d) выходов РПП 16, а группа (n+d) выходов РГ 15 соединена С группой (n+d)

5 входов ОПКТ 14, выход которого соединен с выходом БДТ 20, входом ПТН 41, первым выходом 45 устройства и первым входом БСТ 29, второй вход которого соединен с шиной нулевого потенциала, а выход - с первым входом элемента И 30 и четвертым

управляющим входом 27 БУ 36, третий управляющий вход 24 которого соединен с выходом РПП 22, а выходы девятый 32, десятый 33, двадцатый 34 и шестнадцатый 28 БУ 36 соединены с входами управления с первого по третий ЦК 31 и вторым входом управления элемента И 30 соответственно, выход последнего соединен с первым входом ЦК 31, третий и второй информационные входы которого соединены с двадцать первым выходом 35 БУ 36 и с выходом РГС 42 соответственно, первый и второй управляющие входы которого соединены с одиннадцатым 37 и двенадцатым 38 выходами БУ 36, a nb - разрядная входная шина РГС 42 соединена с группой nb выходов БПП 43, группа адресных Р-входов которого соединена с выходной р-разрядной шиной СТ 44, первый и второй управляющие входы которого соединены с семнадцатым 39 и восемнадцатым 30 выходами БУ 36 соответственно, тринадцатый управляющий выход 23 которого соединен с входом синхронизации РПП 22, информационный вход которого соединен с информационным входом РПП 16 и с выходом ЦК 31, а группа nb выходов РПП 22 соединена с nb-разрядной входной шиной ВПКТ 21, выход которого соединен с входом БДТ 20, первый и второй входы управления которого соединены соответственно с четырнадцатым 25 и пятнадцатым 26 выходами БУ 36, причем, второй выход 46 устройства соединен с выходом ПТН41.

Основной преобразователь кода в ток должен быть выполнен на основе избыточного измерительного кода (ИИК).

Количество адресных входов блока постоянной памяти определяется из условия возможности адресации массива, содержащего (n-m) nb-разрядных кодовых комбинаций:

р fog2(n-m),(1)

где m - количество грубых (корректируемых) разрядов;

п - количество основных (точных и грубых) разрядов

Количество входов устройства k зависит от требуемой разрядности входной измеряемой величины. Количество адресных входов вычислительного блока Е определяется по числу n+d адресуемых разрядов и вычисляется по формуле

(n+d),(2)

где d - количество дополнительных (некорректируемых) разрядов.

Вспомогательный преобразователь код - ток может быть выполнен двоичным. Количество его разрядов зависит от разбиения разрядной сетки АЦП (на корректируемые и некорректируемые разряды) и коэффициентов деления БДТ. Так, например, при наличии в БДТ четырех коэффициентов передачи даже при увеличении количества 5 корректируемых разрядов ОПКТ до 14-16 (всего 22-24) достаточно будет иметь 10-ти разрядный ВПКТ, Это позволит использовать серийно выпускаемые токовые ЦАП, например, К572ПА1.

0 Блок ВБ 4 содержит группу k входов 1, группу адресных входов 12, группу с первого по седьмой 5-11 управляющих входов, второй цифровой коммутатор ЦК 47, арифметико-логическое устройство (АЛУ) 48,

5 регистр (РГ) 49, первый цифровой коммутатор (ЦК) 50, блок постоянной памяти (ВПП) 51, блок оперативной памяти (БОП) 52, выход 13.

Группа k входов 1 вычислительного бло0 ка В Б 4 соединена с второй группой k входов второго ЦК 47, группа k выходов которого соединена с группой k входов РГ 49, группа k выходов которого соединена с второй группой k входов АЛУ 48 и группой k входов

5 БОП 52, группа Јадресных входов которого соединена с группой Ј адресных входов 12 ВБ 4 и группой адресных входов ВПП 51, группа k выходов которого соединена с второй группой k входов первого ЦК 50, первая

0 группа k входов которого соединена с группой k выходов БОП 52, первый и второй входы управления которого соединены с первым 5 и вторым 6 входами управления ВБ 4, входы 7-11 управления которого сое5 динены соответственно с первым и вторым входами управления РГ49, входом управления первого ЦК 50, входом управления АЛУ 48, входом управления второго ЦК 47, первая группа k входов которого соединена с

0 группой k выходов АЛУ 48, первая группа k входов которого соединена с группой k выходов первого ЦК 50, а выход АЛУ 48 соединен с выходом 13 В Б 4.

Переход в режим самоповерки происхо5 дит при подаче импульса отрицательной полярности длительностью т 100 мкс на первый вход 2 БУ 36 (фиг,4).

В схеме использованы следующие условные обозначения: i - номер поверяемого

0 разряда; j - номер разряда,участвующего в кодировании 1-й вспомогательной величины Вы; ADRi - адрес 1-го поверяемого разряда в БОП 52; ADRj - адрес j-ro разряда в БПП 51 при выполнении условия

5 (т-И) j (n+d) или в БОП 52 при выполнении условия 1 j т.

В начале режима самоповерки БУ 36 выдает импульс отрицательной полярности на семнадцатом выходе 39, в результате чего производится сброс СТ 44. и сигнал низкого уровня на шестом выходе 41, коммутирующий на первую группу входов ЦК 47, группу выходов АЛУ 48. Номер поверяемого разряда i устанавливается равным m (m - номер младшего разряда из группы поверяемых). Далее, БУ 36 выдает импульсы отрицательной полярности на восьмом выходе 19 и третьем выходе 7. в результате чего производится сброс РГ 15 и РГ 49 соответственно.

Сброс РПП 16 и РПП 22 осуществляется следующим образом.

БУ 36 выдает серию синхроимпульсов на седьмом выходе 17 до прихода отрицательного сигнала на пятый вход 19 БУ 36 и серию синхроимпульсов на тринадцатом выходе 23 до прихода отрицательного сиг- - нала на третий вход 24 БУ 36. По переднему фронту сигнала, выдаваемого БУ 36 на восемнадцатом выходе 40 и поступающему на второй вход СТ 44, на группе р выходов СТ 44 устанавливается адрес ячейки БПП 43, в которой находится код i-й вспомогательной величины Кы и на пв - разрядную входную шину РГС 42 поступает код Кы. Передний фронт сигнала на тринадцатом выходе 23 БУ 36 переводит первый выход РПП 22 в состояние Лог.Г. СигнгГл бйсвЙоТо у ровня на одиннадцатом выходе 37 БУ 36 переводит в режим загрузки Данных от группы параллельных пь входов. Далее, БУ 36 выдает отрицательный импульс на двенадцатом выходе 38, по переднему фронту которого выполняется сдвиг информации на пь входах РГС 42 и информация с пь входа РГС 42 переписывается на последовательный выход РГС 42, и отрицательный сигнал на десятом выходе 33, по которому последовательный выход РГС 42 коммутируется на второй вход РПП 22. По заднему фронту сигнала на тринадцатом выходе 23 БУ 36 информация с второго входа РПП 22 переписывается на первый выход РПП 22, а на второй выход nb-разрядной шины РПП 22 переписывается уровень Лог.1.. По переднему фронту импульса на двенадцатом выходе 38 БУ 36 информация с nb-ro входа РГС 42 переписывается на последовательный выход РГС 42. По заднему фронту импульса на тринадцатом выходе 23 БУ 36 информация с второго входа РПП 22 переписывается на второй выход РПП 22, а на третий выход РПП 22 переписывается уровень Лог,1, Аналогичным образом вся информация с группы параллельных пь входов РГС 42 переписывается в РПП 22. Об окончании опи- (ГывШГмого прЪ це С сёг свидетельствует сигнал низкого уровня на третьем входе 24 БУ 36. Таким образом, на nb-разрядную

входную шину ВПКТ 21 поступает код Кы. Далее. БУ 36 выдает кодовую комбинацию на четырнадцатом 25 и пятнадцатом 26 выходах, задающую коэффициент деления для

БДТ 20. Величина коэффициента деления определяется значением номера поверяемого разряда I. В результате на входе БСТ 29 устанавливается аналоговая величина, соответствующая коду i-й вспомогательной

0 величины.

Далее, БУ 26 выдает сигнал низкого уровня на девятом выходе 32, коммутирующий выход элемента И 30 на второй вход РПП 16, Номер разряда, участвующего в ко5 дировании 1-й вспомогательной величины, j устанавливается равным (1+1). Передний фронт импульса на седьмом выходе 17 БУ 36 переводит первый выход РПП 16 в состояние Лог.1. Сигнал низкого уровня на шес0 тнадцатом выходе 28 БУ 36 обуславливает подачу уровния Лог.О на второй вход РПП 16. Подача ) импульсов отрицательной полярности на первый вход РПП 16 приводит к установлению уровня Лог.О на стар5 ших 0-1) выходах РПП 16, на j-м выходе РПП 16 устанавливается уровень Лог.1, Далее, БУ 36 выдает сигнал высокого уровня на шестнадцатом выходе 28, разрешающий прохождение сигнала с выхода БСТ 29 а

0 второй вход РПП 16. По заднему фронту импульса на седьмом выходе 17 БУ 36 информация с выхода БСТ 29 переписывается на j-й выход РПП 16, а по переднему фронту (|+1)-й выход РПП 16 устанавлива5 ется в состояние Лог.1. Сигнал с выхода БСТ 29 поступает также на четвертый вход 27 БУ 36. При присутствии сигнала высокого уровня на этом входе на адресной разрядной шине 12 БУ 36 формируется

0 адрес J-ro разряда. При j m Q-разряд принадлежит к группе неточных) БУ 36 выдает сигнал высокого уровня на четвертом выходе 9, коммутирующий группу k выходов БОП 52 на первую группу k входов АЛУ 48,

5 и импульс отрицательной полярности на первом выходе 5, поступающий на вход чтения БОП 52. При j m Q-й разряд принадлежит к группе точных) БУ 36 выдает сигнал низкого уровня на четвертом выходе 9, ком0 митирующий группу k выходов БПП 51 на первую группу k входов АЛУ 48. По приходу отрицательного импульса на пятом выходе 10 БУ 36 происходит суммирование данных, поступающих на первую и вторую

5 (с выходной шины РГ 49) входные k-разряд- ные шины АЛУ 48. По переднему фронту импульса на девятнадцатом выходе 8 БУ 36 результат суммирования с выходной шины АЛУ 48 переписывается в РГ 49. Далее, номер разряда, участвующего в кодировании

1-й вспомогательной величины увеличивается на единицу, т.е. j J+1, и БУ 36 переходит к анализу сигнала на четвертом входе 27 (элемент 46 структурной схемы алгоритма, фиг.4) Дальнейшее кодирование Аы проис- ходит аналогично описанному (элементы 46-62 структурной схемы алгоритма, фиг.4). По окончании первого кодирований в РГ 49 находится код Кы.

В начале второго кодирования A8i j уста- навливается равным I. БУ 36 выдает сигнал низкого уровня на восьмом выходе 19, в результате чего производится сброс РГ 15, и сигнал низкого уровня на шестнадцатом выходе 28, обслуживающий лодачу сигнала низкого уровня на второй вход РПП 16. Подача Q-1) импульсов отрицательной полярности на первый вход РПП 16 приводит к установлению уровня Лог.О на старших (J-1) выходах РПП 16, на j-м выходе устанав- ливается уровень Лог. 1й. Далее, БУ 36 выдает сигнал высокого уровня на шестнадцатом выходе 28, который разрешает прохождение сигнала с выхода БСТ 29 на второй вход РПП 16. БУ 36 анализирует со- стояние сигнала на четвертом входе 27. Если на данном входе присутствует сигнал вы со кого уровня и выполняется условие j э81, то на адресной шине 12 БУ 36 формируется адрес j-ro разряда. При j m Q-й разряд принадлежит к группе грубых) 6У 36 выдает сигнал высокого уровня на четвертом выходе 9, коммутирующий группу k выходов БОП 52 на первую группу k входов АЛУ 48, и отрицательный импульс на первом выходе 5, поступающий на вход чтения БОП 52. При j m разряд принадлежит к группе точных) БУ 36 выдает сигнал низкого уровня на четвертом выходе 9, коммутирующий группу k выходов БПП 51 на первую группу k входов АЛУ 48. При подаче положительного импульса на пятый выход 10 БУ 36 происходит вычитание из значения, поступающего на вторую группу k входов АЛУ 48 от РГ 49, значения, поступающего на пер- вую группу k входов АЛУ 48. По переднему фронту импульса на девятнадцатом выходе 8 БУ 36 результат вычитания с выходной шины АЛУ 48 переписывается в РГ 49. Далее, БУ 36 переходит к анализу сигнала на пятом входе 28. Сигнал высокого уровня на этом входе свидетельствует о том, что второе кодирование Аы не закончено. По заднему фронту сигнала на седьмом выходе 17 БУ 36 информация с выхода БСТ 29 переписывается на j-й выход РПП 16, а по переднему фронту 0+1)-й выход РПП 16 устанавливается в состояние Лог Г Далее, номер разряда, участвующего в кодировании Аы увеличивается на 1, т е. j j+1, и БУ

36 переходит к анализу сигнала на четвертом входе 27. Дальнейшее кодирование происходит аналогично (элементы 74-92 структурной схемы, фиг.4). Низкий уровень сигнала на пятом входе 18 БУ 36 свидетельствует о конце цикла второго кодирования, по окончании которого РГ 49 хранит значение кода 1-го поверяемого разряда Ki. Бу 36 формирует на адресной шине 12 адрес 1-го поверяемого разряда в БОП 52.

При поступлении отрицательного импульса на второй выход 6 БУ 36 код К заносится в БОП 52.

Если выполняется условие I 1, то работа в режиме самоповерки завершается. Если I 1, происходит уменьшение номера поверяемого разряда (I 1-1) и БУ 36 переходит к работе по формированию 1-й вспомогательной величины Аы и весь процесс повторяется аналогично Описанному (элементы 7-99 структурной схемы алгоритма самоповерки, фиг.4).

В алгоритме (фиг.5) использованы следующие условные обозначения: j - номер разряда, участвующего в кодировании измеряемой величины; ADRj - адрес j-ro разряда в БПП 51 при выполнении условия: (гл+1) j (n+d) или в БОП 52 при выполнении условия: 1 т.

В начале работы в данном режиме БУЗб выдает отрицательный импульс на восьмой выход 19, по которому выполняется сброс РГ 15. Далее, БУ 36 выдает серию синхроимпульсов на седьмом выходе 17 до прихода отрицательного сигнала на пятый вход 18 БУ 36, что свидетельствует о сбросе РПП 16. Сброс РГ 49 производится отрицательным импульсом на третьем выходе 7 БУ 36. Далее, БУ 3& выдает положительный сигнал на шестом выходе 11, который коммутирует входную шину 1 устройства на входную шину РГ 49. По переднему фронту импульса на девятнадцатом выходе 8 БУ 36 производится запись входной измеряемой величины в РГ 49. Сигнал низкого уровня на шестом выходе 11 БУ 36 коммутирует выходную шину АЛУ 48 на входную« шину РГ 49. Сигнал низкого уровня на двадцатом выходе 34 БУ 36 коммутирует на второй вход РПП 16 двадцать первый выход 35 БУ 36. Номер разряда j устанавливается равным 1. По переднему фронту импульса на седьмом выходе 17 БУ 36 старший разряд на выходе РПП 16 переводится в состояние Лог.1. На адресной шине 12 БУ 36 формируется адрес j-ro веса в БОП 52 (при j S m) или в БПП 51 (при j m). При j m БУ 36 на четвертом выходе 9 выдает сигнал высокого уровня, коммутирующий выходную шину

БОП 52 ни первую входную шину АЛУ 48, и отрицательный импульс на первом выходе 5. по которому информация считывается из ячейки с адресом ADRj на выходную шину БОП 52, При J m БУ 36 на четвертом выходе 9 выдает сигнал низкого уровня, коммутирующий выходную шину БПП 51 на первую входную шину АЛУ 48. Далее, выполняется сравнение кода К, записанного в РГ 49 с кодом Kj. Сравнение выполняется в ВБ 4 путем вычитания из кода К кода веса j-ro разряда и анализа знака 2j; |1,,

ZJ-(3)

tO, K Kj.

Для этого БУ 36 подает положительный импульс на вход управления 10 АЛУ 48, по которому происходит вычитание из содер- .жимого РГ49 веса j-ro разряда. По переднему фронту импульса на девятнадцатом выходе 8 БУ 36 полученная таким образом разность записывается в РГ 49. Далее, БУ 36 анализирует состояние шестого входа 13. При положительном сигнале на этом входе, что соответствует выполнению ус- лоеия К К| производится восстановление разности до исходной величины К (К К + +Kj), для чего подается отрицательный импульс на управляющий вход АЛ У 48. Резуль- тат суммирования формируется в РГ 40 по переднему фронту импульса на девятнадцатом выходе 8 БУ 36. На шторой вход РПП 16 в этом случае БУ 36 подает уровень Лог.О,

При отрицательном сигнале на шестом входе 13 6У 36, мтв соответствует выполнению условия К Kj. 6У 36 подает на второй вход РПП 16 уровень Лог.1. По заднему фронту импульса на первом входе РПП 16 информация с его второго входа перепись - вается на j-й выход, Далее, БУ 36 переходит к анализу сигнала на пятом входе 18. При наличии положительного сигнала на этом входе производится увеличение номера разряда j на 1 и БУ 36 переходит к следую- щему такту преобразования (элемент 17 структурной схемы на фиг.5). Описанная процедура выполняется для всех (m-d) разрядов. Сигнал низкого уровня на пятом входе 18 БУ 36 свидетельствует о конце цикла цифроаналогового преобразования. В результате, на выходе РПП 16 сформирован код входной величины К, а на выходах 46 и 45 устройства присутствуют соответствующие ему аналоговые сигналы АО и AI.

Примеры реализации блоков предлагаемого устройства.

Блок управления может быть синтезирован различными методами. Например, он

может быть выполнен на основе автомата с памятью или по принципу программного управления,

Для формирования управляющих сигналов применена последовательностями схема с использованием ПЗУ.

Необходимые для управления работой ЦАП управляющие и условные сигналы приведены в таблице.

Таким образом, в предлагаемом устройстве формирование вспомогательного аналогового сигнала происходит с учетом реальных весов основного и вспомогательного преобразователей код - ток, что позволяет повысить точность цифроаналогоеого преобразования в широком температурном и временном диапазонах и применить в качестве вспомогательного преобразователя код - ток серийно выпускаемый ЦАП малой разрядности

Формула изобретения 1. Цифроаналогоеый преобразователь, содержащий вспомогательный преобразователь кода в ток, вычислительный блок, информационные входы которого являются входной шиной преобразуемого кода, группа управляющих входов подключена к соответствующим выходам группы выходов блока управления, а управляющие входы с первого по шестой включительно соединены соответственно с выходами с первого по шестой блока управления, первый и второй входы которого являются соответственно первой и второй входными шинами управления, а седьмой выход соединен с входом синхронизации первого регистра последовательного приближения, информационный вход которого подключен к выходу цифрового коммутатора, выходы соединены с соответевтующими информационными входами регистра, вход управления которого соединен с восьмым выходом блока управления, а выходы соединены с соответствующими входами основного преобразователя кода в ток, выход которого соединен с первым входом блока сравнения токов и является первой выходной шиной, девятый и десятый выходы блока управления соединены соответственно с первым и вторым входами управления цифрового коммутатора, а одиннадцатый и двенадцатый выходы подключены соответственно к входу записи и входу синхронизации регистра сдвига, отличающийся тем, что, с целью повышения точности преобразования, в него введены преобразователь тока в напряжение, блок деления токов, элемент И. блок постоянной памяти, счетчик и второй регистр последовательного приближения, информационные выходы которого соединены с соответствующими входами вспомогательного преобразователя кода в ток, информационный вход объединен с информационным входом первого регистра последовательного приближения, а вход синхронизации и управляющий выход соединены соответственно с тринадцатым выходом и третьим входом блока управления, четырнадцатый и пятнадцатый выходы которого соединены соответственно с первым и вторым входами управления блока деления токов, информационный вход которого соединен с выходом вспомогательного преобразователя кода в ток, а выход объединен с выходом основного преобразователя кода в ток и соединен с входом преобразователя тока в напряжение, выход которого является второй выходной шиной/ второй вход блока сравнения токов соединен с шиной нулевого потенциала, а выход соединен с первым входом элемента И и четвертым входом блока управления, шестнадцатый выход которого соединен с вторым входом элемента И, выход которого подключен к первому информационному входу цифрового коммутатора, второй информационный вход которого соединен с выходом регистра сдвига, информационные входы которого подключены к соответствующим выходам блока постоянной памяти, входы которого подключены к соответствующим выходам счетчика, вход сброса и синхронизации которого соединены соответственно с семнадцатым и восемнадцатым выходами блока управления, девятнадцатый, двадцатый и двадцать первый выходы которого соединены соответственно с седьмым управляющим входом вычислительного блока, с третьим управляющим и третьим информационным входами цифрового коммутатора, пятый вход соединен с управляющим выходом первого регистра последовательного приближения, а шестой вход соединен с входом вычислительного блока.

2, Преобразователь поп 1, о т л и ч а ю- щ и и с я тем, что вычислительный блок выполнен в виде арифметико-логического устройства, первого и второго цифровых коммутаторов, регистра, блока постоянной памяти и блока оперативной памяти, выходы которого соединены с соответствующими первыми информационными входами первого цифрового коммутатора, первый и второй управляющие входы являются соответственно первым и вторым управляющими входами блока, а адресные входы объединены с соответствующими адресными входами блока постоянной памяти и являются соответствующими входами группы управляющих входов блока, выходы блока постоянной памяти подключены к соответствующим вторым информационным вхо- дам первого цифрового коммутатора, управляющий вход которого является четвертым управляющим входбм блока, а выходы соединены с первыми информационными входами арифметико-логического

0 устройства, управляющий вход и выход которого являются соответственно пятым управляющим входом и выходом блока, вторые информационные входы подключены к соответствующим выходам регистра и

5 объединены с информационными входами блока оперативной памяти, а группа выходов соединена с соответствующими первыми информационными входами второго цифрового коммутатора, вторые инфор0 мационные входы и управляющий вход которого являются соответственно информационными входами и шестым управляющим входом блока, а выходы соединены с соответствующими информационными

5 входами регистра, первый и второй управляющие входы которого являются соответственно третьим и седьмым управляющими входами блока.

3. Преобразователь по п. 1, о т л и ч а ю0 щийся тем, что блок управления выполнен в виде постоянного запоминающего устройства, первого и второго регистров и генератора импульсов, вход которого объединен с входом обнуления первого регистра и явля5 ется первым входом блока, а первый и второй выходы соединены с входами синхронизации первого и второго регистров соответственно, информационные входы второго регистра соединены с соответству0 ющими первыми выходами постоянного запоминающего устройства, вторые входы которого соединены с соответствующими информационными входами первого регистра, выходы которого подключены к соот5 ветствующим входам группы адресных входов постоянного запоминающего устройства, адресные входы с первого по пятый которого являются соответственно вторым, шестым, пятым, третьим и четвер0 тым входами блока, выходы с первого по седьмой второго регистра являются соответственно первым, вторым, третьим, девятнадцатым, четвертым, пятым и шестым выходами блока, выходы с восьмого по две5 надцатый являются группой выходов блока, тринадцатый и четырнадцатый выходы второго регистра являются соответственно седьмым и восьмым выходами блока, выходы с пятнадцатого по восемнадцатый являются соответственно с тринадцатого по

шестнадцатый выходами блока, выходы с девятнадцатого по двадцать шестой второго регистра являются соответственно девятым, десятым, двадцатым, двадцать первым, одиннадцатым, двенадцатым, семнадцатым и восемнадцатым выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифроаналогового преобразования | 1984 |

|

SU1248072A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1257848A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1216827A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1221754A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1257847A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1790030A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1702525A1 |

| Устройство отсечения многоугольника для графического дисплея | 1990 |

|

SU1777151A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1279064A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для преобразования цифровой информации в аналоговую. Цель изобретения- повышение точности преобразования. Цифроаналоговый преобразователь содержит вычислительный блок 4, основной преобразователь 14 тока в код, регистр 15, первый регистр 16 последовательного приближения, блок 20 делителей тока, вспомогательный преобразователь 21 кода в ток, второй регистр 22 последовательного приближения, блок 29 сравнения токов, элемент И 30, цифровой коммутатор 31, блок 36 управления, преобразователь 41 тока в напряжение, регистр 42 сдвига, блок 43 постоянной памяти и счетчик 44. Положительный эффект достигается за счет введения блоков 20, 22, 30, 41, 43, 44 и изменения алгоритма функционирования преобразователя в режиме самоповерки. 2 з.п.ф-лы, 6 ил., 1 табл, (Л С

хю «

% ъ

YH

Y

«

t

Y18

to

Управление ЦК 31

Управление параллельно-последовательнымрежимом работы

Вход синхроимпульса РГС 42

Вход синхроимпульса РПП 2

Управление коэффициентом деления БДТ 20

Разрешение/запрет прохождения сигнала с выхода S6T 29 на вход данных РПП 16

Сброс СТ kk

-Вход синхроимпульса СТ №

Управление записью в РГ

Управление ЦК 31

элемента И 30

Y-IO 0 - подключение выхода РГС 2 на входы данных РПП 16, РПП 22

VM - 1 - загрузка данных от параллельных nft входов

«

О - запрет

00 подключение двадцать первого 35 выхода БУ 36 на входы данных РПП 16 и РПП 22

Фиг Ј

Продолжение таблицы

(#54

fi

,

W I«-P4S§ §5:

fc u a a t; fe 3

Т 1 i i n J n i TV r TT - i - ----J

I

at о

К во ав«оо ов oo- 1 23 ч

Ч1-. t -

у и yt; аааа;;} -. ч

WiMUtiaiV«M4.:

Ј

S-,

f

. ЛГо

91 6

t

5

| Устройство цифроаналогового преобразования | 1984 |

|

SU1257847A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для цифроаналогового преобразования | 1984 |

|

SU1248072A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-07-23—Публикация

1990-03-26—Подача