Изобретение относится к автоматике, в частности к автоматизированной аппаратуре связи, и может быть использовано в системах передачи данных для сложных комг 1утаций большого числа каналов связи, передающих информацию в цифровом коде,

Цель изобретения - повышение быстродействия модуля многоканального ком татора при соединении двух абонентов.

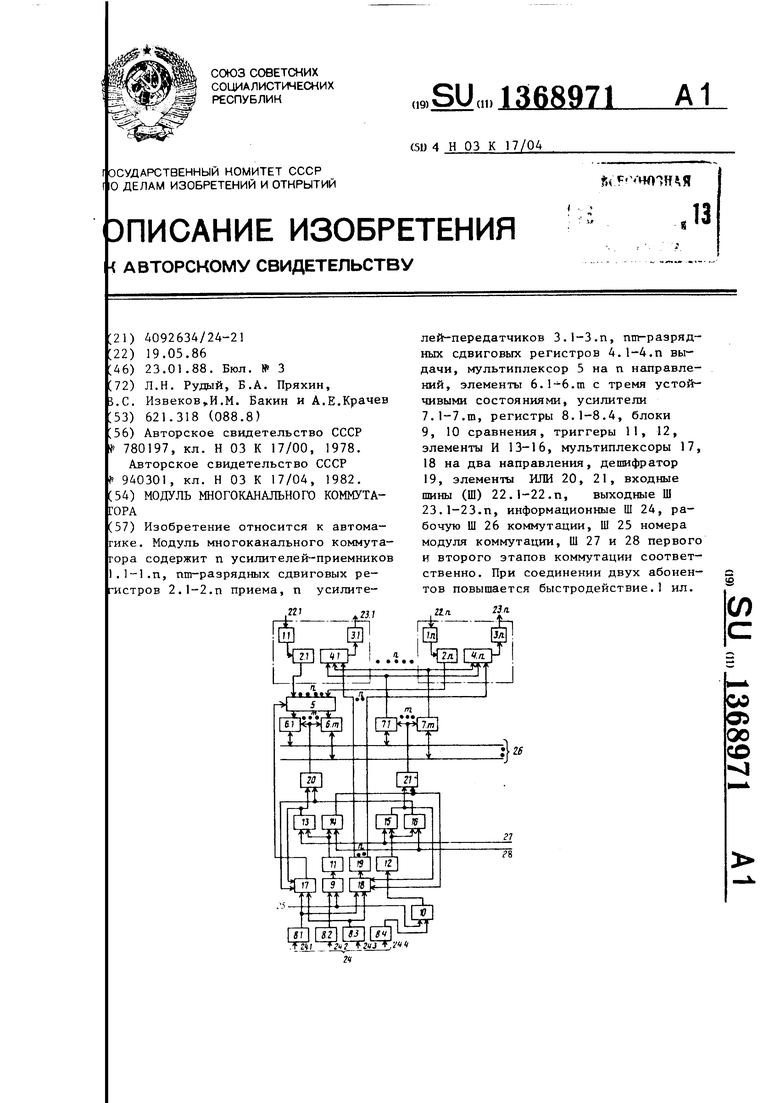

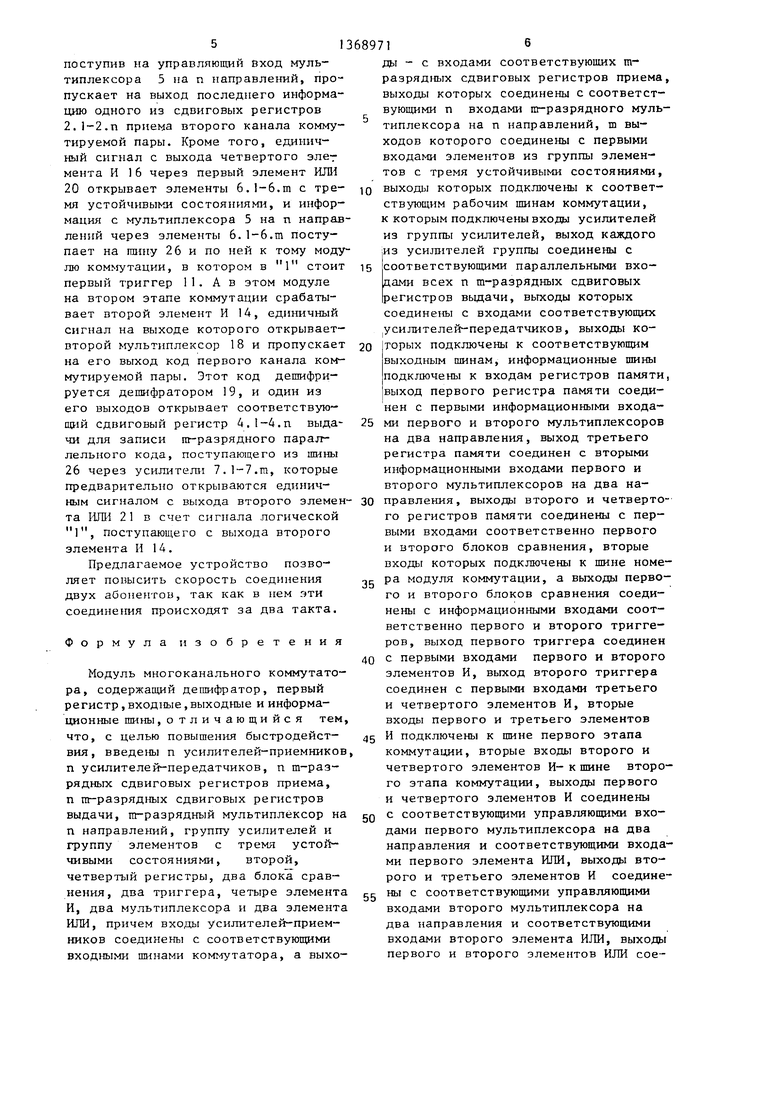

На чертеже представлена структурная схема модуля многоканального коммутатора.

Модуль многоканального коммутатора содержит п усилителей-приемников 1.1-1.и, пт-разрядных cдвигoвIJlx регистров 2.1-2.П приема, п усилителей передатчиков 3.1-З.п, ппг-разряд- HLIX сдвиговых регистров 4.1-4.п выдачи, мультиплексор 5 на п направлений, группу элементов 6.1-б.т с тремя устойчивыми состояниями, группу усилителей 7.1-7,т, четыре регистра 811-8.4, два блока 9 и 10 сравнения два триггера 11 и 12, четыре элемента И 13-16, два ъгультиплексора 17 и 18 на два направления, дешифратор 19, два элемента ИЛИ 20 и 21, вход- Hi:,ie шины 22. 1-22.п, выходные шины 23.1-23.п, информационные шины 24, шину 25 номера модуля коммутации, рабочие иины 26 коммутации, шину 27 первого этапа коммутации и шину 28 второго этапа коммутации.

Вход111 усилителей-приемников 1.1-1.П соединены с соответствующими входныьш шинами 22.1-22.п, а выходы - с входами соответствующих га-разрядных сдвиговых регистров 2.1-2.П приема, выходы которых соединены с соответствующими входами т-разрядного мультиплексора 5 на п направлений, m выходов которого соединены с первыми входами соответствующих элементов 6.1-6.т с тремя устойчивыми состояниями, выходы которых соединены с входами соответствующих усилителей 7.1-7.m и рабочими шинами 26 коммутации.Выход каждого из усилителей 7,1-7.т соединен с соответствующими входами всех регистров 2.1-2.П приема, выходы которых соединены с входами соответствующих усилителей-передатчиков 3.1--З.П, выходы которых соединены с соответствующими выходными шинами 23.1-23.п. Информационные шины 24

соединены с входами регистров 8.1-8.4. Выход первого регистра 8.1 соединен с первыми информацирн- ными входами первого 17 и второго 18 мультиплексоров. Выход третьего регистра 8.3 соединен с вторыми информационными входами первого 17 и второго 18 мультиплексоров. Выходы

второго 8.2 и четвертого 8,4 регистров соедине1Л1 с первыми входами соответственно первого 9 и второго 10 блоков сравнения, вторые входы которых подключены к шине 25 номера модуля .коммутации.

Выходы блоков 9 и 10 сравнения соединены с входами соответственно первого 11 и второго 12 триггеров. Выход триггера 11 соединен с первыми входами первого 13 и второго 14 элементов И. Выход второго триггера соединен с первыми входами третьего 15 и четвертого 16 элементов И, Вторые входы первого 13 и третьего 15

элементов И соединены с шиной 27

первого этапа коммутации. Вторые входы второго 14 и четвертого 16 элементов И соединены с шиной 28 второго этапа коммутации. Выходы первого 13

и четвертого 16 элементов И соединены с соответствующими управляющими входами первого мультиплексора 17 и соответственно с первым и вторым входами первого элемента ИЛИ 20, выход которого соединен с вторыми входами элементов 6.1-6.т. Выходы второго 14 и третьего 15 элементов И соединены с соответствующими управляющими входами второго мультиплексорэ 18 и соответственно с первым и вторым входами второго элемента ИЛИ 21, выход которого соединен с управляющими входами усилителей 7,1-7,т. Выходы первого 17 и второго 18 мультиплексоров соединены соответственно с входом мультиплексора 5 на п направлений и входом дешифратора 19, выходы которого соединены с входами разрешения параллельной записи соответствующих сдвиговых регистров 4.1-4.п.

Модуль многоканального коммутатора работает следующим образом. Информация по входным шинам

22,1-22.п, поступающая на усилители- приемники 1.1-1.П, накапливается на т-разрядных сдвиговых регистрах 2,1-2.п приема, работающих с частотой канала связи. Информация, посту

в

3.

с йзиговых

pa Зотающих

За 5ача

дяг

ра

ве :ти

2Ц

8.

рс

рл :тики

па эы:

Мф

к

8,

КУ

рь: ни зая рс го ме э

ПС ЦП

1

ЦП i

тс эого,

ГЦ СТр

ке рс ч ге э

ПС

ПС ступает

нг ется

М€ КДУ

BSиными;

тр яггер

М ЯТ

ег

вс го

щ: авления

т.

Эт от

в оды

ЛЕ ЛИЙ, Н

ш- енно

2.

в

3J

ШИ

паЬщая по выходным шинам 23.1-23.п анал через усилители-передатчики 1-3.п, выдвигается из га-разрядных регистров 4.1-4.П выдачи, с частотой канала связи коммутатора, в который вхо- модули многоканального коммутат эаключается в том, чтобы прообмен накопленной информацией двумя каналами, номера котоуказаны в управляющем слове кс| мутации (УСК).

УСК по информационным шинам ,1-24.4 записывается на регистры 1-8.4 памяти. В первом 8.1 и вто- 4 8.2 регистрах помещаются характ первого каиала коммутируемо его номер (регистр 8.1) и но- модуля коммутации (регистр 8.2) оторому он подключен. В третьем 3 и четвертом 8.4 регистрах поме- ща|отся соответственно характеристи- второго канала коммутируемой па- Первый блок 9 сравнения, сравномер модуля коммутации с вто регистра 8.2 и персональный ио модуля коммутации, поступающий шине 25 номера модуля коммутасвоим сигналом устанавливает в первый триггер 11. В каком-то другом модуле коммутации, номер ко- , помещенный в четвертый ре- 8.4, совпадает на втором бло- 10 сравнения с персональным номе модуля коммутации, второй триг- 12 устанавливается в 1. Затем шине 27 первого этапа коммутации сигнал, по которому иачи- процесс обмена информацией двумя выбранными (скоммутиро-

) каналами. В том модуле кс 1мутации, где стоит в 1 первый

11, срабатывает первый эле- И 13, и единичный сигнал на о выходе пропускает на выход пер- мультиплексора 17 на два накод первого регистра 8.1, номер первого канала пары код поступает на управляющие мультиплексора 5 на п направ- , что заставляет его пропустит выход накопленную информацию

с того сдвигового регистра 1-2.п приема, код которого указан первом регистре 8.1. Кроме того, ef иничный сигнал с выхода первого емента И 13 через первый элемент 20 поступает на управляющие вхо

0

5

0

5

97

0

5

0

5

0

5

1

дь1 элементов 6. 1-6.m с тремя состояниями и открывает их.

Таким образом, информация первого канала коммутируемой пары из мультиплексора 5 на п направлений через m элементов 6.1-6.m поступает на m рабочих шин коммутации (РШК) 26, по которым распространяется на все модули коммутации, входящие в коммутатор. Но только в том модуле коммутации, где второй триггер 12 установлен в 1, срабатывает третий элемент И 15, единичный сигнал на выходе которого через второй элемент ИЛИ 21 поступает на управляющие входы усилителей 7.1-7.т и открывает их. Таким образом, информация первого канала коммутируемой пары из РШК 26 через m усилителей 7.1-7.т поступает на все п сдвиговых регистров 4.1-4.п выдачи в виде т-разрядного двоичного кода. Но записывается этот код только в один из сдвиговых регистров 4.1-4.п выдачи, номер которого в виде сигнала с дешифратора 19 поступает на вход разрешения записи в сдвиговый регистр выдачи параллельным кодом. Дешифратор 19 дешифрирует код номера второго канала коммутируемой пары, указанного в регистре 8.3 и пропущенного вторым мультиплексором 18 под действием единичного сигнала с выхода третьего элемен - та И 15.

На этом первый этап коммутации заканчивается. Он позволяет информацию, накопленную в одном из сдвиговых регистров 2.1-2.п приема первого канала коммутируемой пары, переписать в один сдвиговый регистр 4.1-4.П выдачи второго канала коммутируемой пары. Второй этап коммутации заключается в обратном действии: информацию, накопленную в одном из сдвиговых регистров 2.1-2.П приема второго канала коммутируемой пары, переписывают в один из сдвиговых регистров 4.1-4.П выдачи первого канала коммутируемой пары. Для этого сигнал на шине 27 снимается и выдается сигнал на шину 28 в виде логической 1. В том модуле коммутации, где установлен ;з 1 второй триггер 12, срабатывает четвертый элемент И 16, и единичный сигнал на его выходе пропускает на выход первого мультиплексора 17 код второго канала коммутируемой пары, который.

поступив на управляющий вход мультиплексора 5 на п направлений, пропускает на выход последнего информацию одного из сдвиговых регистров 2.1-2.П приема второго канала коммутируемой пары. Кроме того, единичный сигнал с выхода четвертого элет мента И 16 через первый элемент ИЛИ 20 открывает элементы 6.1-6.т с тремя устойчивыми состояниями, и информация с мультиплексора 5 на п направлений через элементы 6.1-6.т поступает на 1ШП1У 26 и по ней к тому модулю комьгутации, в котором в 1 стоит первый триггер 11. А в этом модуле на втором этапе коммутации срабатывает второй элемент И 14, единичный сигнал на выходе которого открывает- второй мультиплексор 18 и пропускает на его выход код первого канала коммутируемой пары. Этот код дешифрируется дешифратором 19, и один из его выходов открывает соответствующий сдвиговый регистр 4.t-4.n выдачи для записи т-раэрядного параллельного кода, поступающего из шины 26 через усилители 7.1-7.т, которые предварительно открываются единичным сигналом с выхода второго элемента ИЛИ 21 в счет сигнала логической 1, поступающего с выхода второго элемента И 14.

Предлагаемое устройство позволяет повысить скорость соединения двух абонентов, так как в нем эти соединения происходят за два такта.

Формула изобретения

Модуль многоканального коммутатора, содержащий дешифратор, первый регистр,входные,выходные и информационные шнны, отличающийся тем, что, с целью повышения быстродействия, введены п усилителей-приемников, п усилителей-передатчиков, п т-раз- рядных сдвиговых регистров приема, п га-разрядных сдвиговых регистров выдачи, го-разрядный мультиплексор на п направлений, группу усилителей и группу элементов с тремя устойчивыми состояниями, второй, четвертый регистры, два блока сравнения, два триггера, четыре элемента И, два мультиплексора и два элемента ИЛИ, причем входы усилителей-приемников соединены с соответствующими входными шинами комг-гутатора, а выхо10

15

20

25

30

35

40

45

50

13689716

ДЫ - с входами соответствующих га- разрядных сдвиговых регистров приема, выходы которых соединены с соответствующими п входами т-разрядного мультиплексора на п направлений, ш выходов которого соединены с первыми входами элементов из группы элементов с тремя устойчивыми состояниями, выходы которых подключены к соответствующим рабочим щинам коммутации, к которым подключены входы усилителей из группы усилителей, выход каждого из усилителей группы соединены с соответствующими параллельными входами всех п га-разрядных сдвиговых регистров вьщачи, выходы которых соединены с входами соответствующих |УСилителей-передатчиков, выходы которых подключены к соответствующим выходным шинам, информационные шины подключены к входам регистров памяти, выход первого регистра памяти соединен с первыми информационными входами первого и второго мультиплексоров на два направления, выход третьего регистра памяти соединен с вторыми информационными входами первого и второго мультиплексоров на два направления, выходы второго и четвертого регистров памяти соединены с первыми входами соответственно первого и второго блоков сравнения, вторые входы которых подключены к щине номера модуля коммутации, а выходы первого и второго блоков сравнения соединены с информационными входами соответственно первого и второго триггеров, выход первого триггера соединен с первыми входами первого и второго элементов И, выход второго триггера соединен с первыми входами третьего и четвертого элементов И, вторые входы первого и третьего элементов И подключены к шине первого этапа коммутации, вторые входы второго и четвертого элементов И- к шине второго этапа коммутации, выходы первого и четвертого элементов И соединены с соответствующими управляющими входами первого мультиплексора на два направления и соответствующими входами первого элемента ИЛИ, выходы второго и третьего элементов И соединены с соответствующими управляющими входами второго мультиплексора на два направления и соответствующими входами второго элемента ИЛИ, выходы первого и второго элементов ИЛИ сое55

ДИ ве

то

ВЬ

со

шны с управляющими входами соот- ственно элементов из группы элемен 3 с тремя устойчивыми состояниями . силителей из группы усилителей, оды первого и второго мультиплёк- )QB на два направления соединены

соответственно с управхшющим входом мультиплексора на п направлений и входом дешифратора, п выходов которого соединены с входами разрешения параллельной записи соответствуюпщх поразрядных сдвиговых регистров вьдачи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

| Устройство для контроля аналоговых объектов | 1986 |

|

SU1397941A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОКАЛЬНЫХ ПОРЯДКОВЫХ СТАТИСТИК | 1990 |

|

RU2024934C1 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1386987A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ТЕЛЕГРАФНЫХ РАДИОСИГНАЛОВ | 1990 |

|

RU2009615C1 |

| Устройство приоритетного доступа к магистрали | 1990 |

|

SU1839249A1 |

| Устройство для поиска максимального числа | 1985 |

|

SU1314334A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналами связи | 1983 |

|

SU1160421A1 |

| Устройство для вычисления свертки | 1989 |

|

SU1688259A1 |

| МОДУЛЬ КОММУНИКАЦИОННОЙ СЕТИ, ПРЕДНАЗНАЧЕННЫЙ ДЛЯ ПЕРЕДАЧИ СООБЩЕНИЙ, ОБМЕНА СООБЩЕНИЯМИ И ОРГАНИЗАЦИИ ВЕЩАТЕЛЬНЫХ РЕЖИМОВ ОБМЕНА СООБЩЕНИЯМИ | 2000 |

|

RU2178584C1 |

Авторы

Даты

1988-01-23—Публикация

1986-05-19—Подача