со со

sj

со

113

Изобретение относится к вычислительной технике и может быть использовано для контроля аналоговых объектов ,

Цель изобретения - повышение достоверности работы устройства за счет формирования устойчивых сигнатур для флуктуирующих аналоговых сигналов.

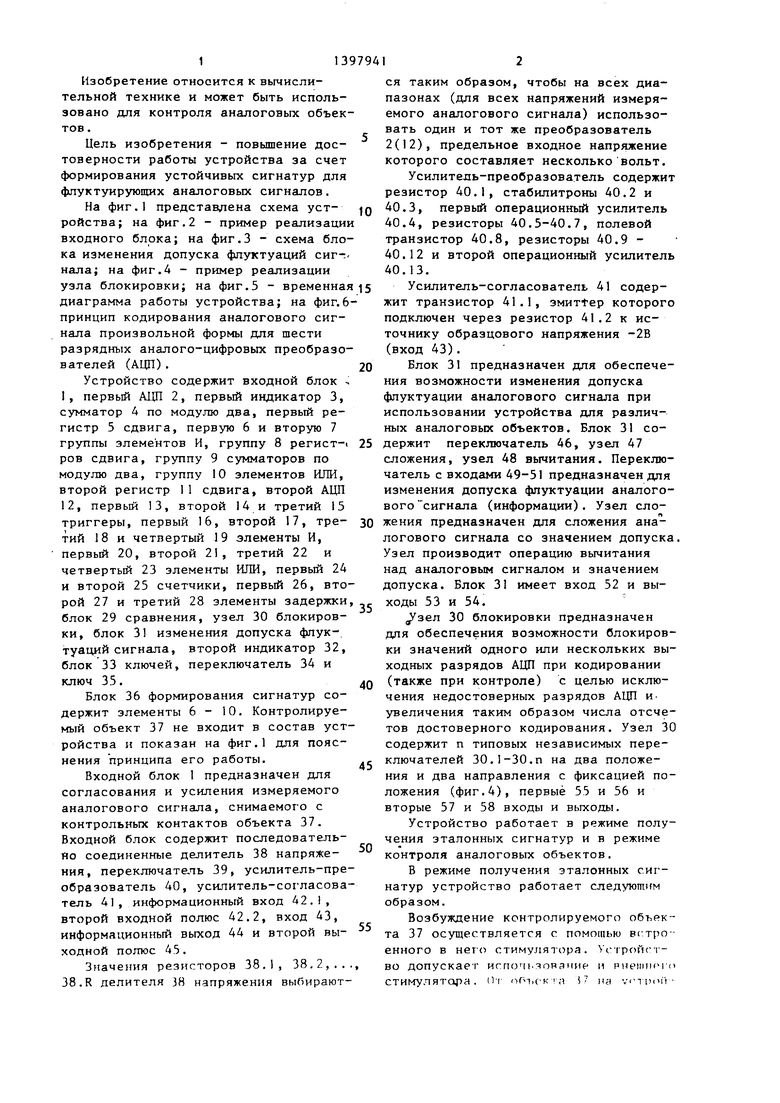

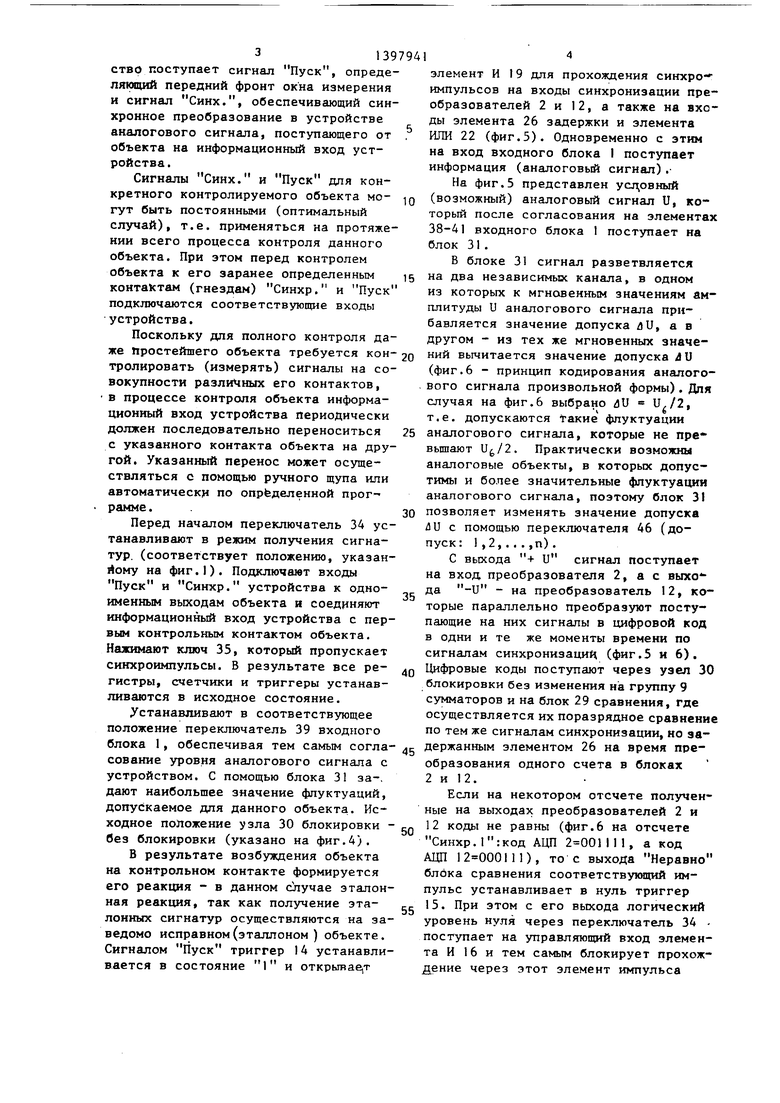

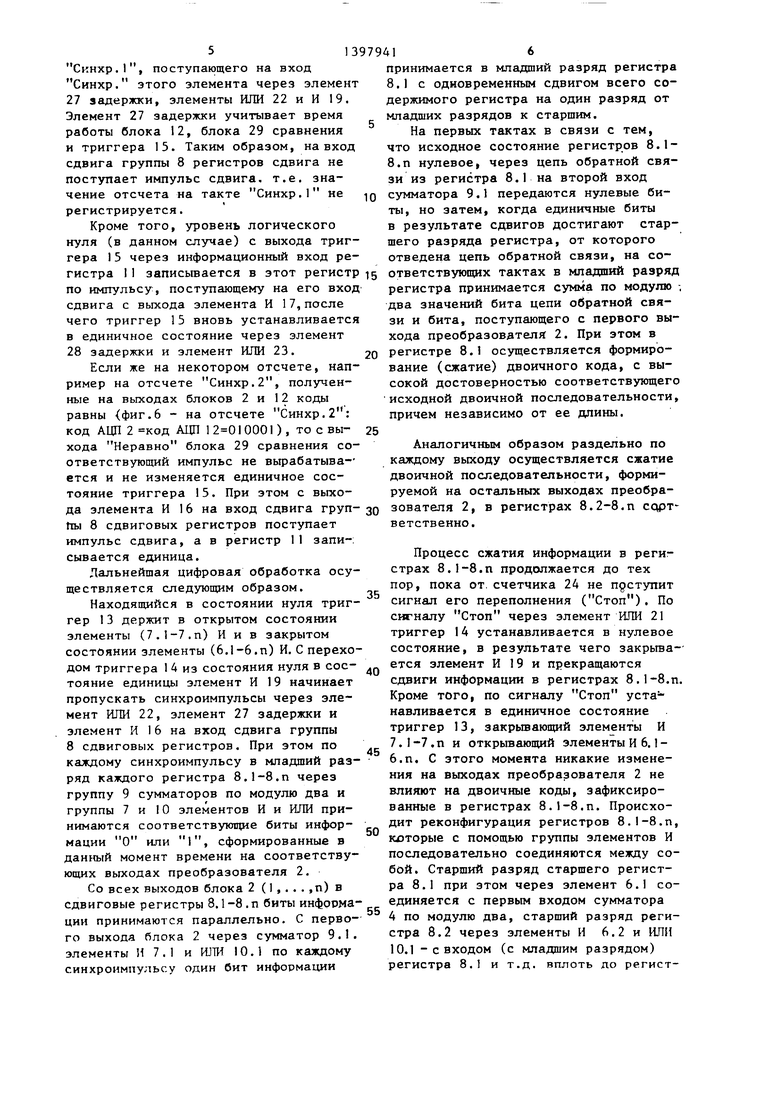

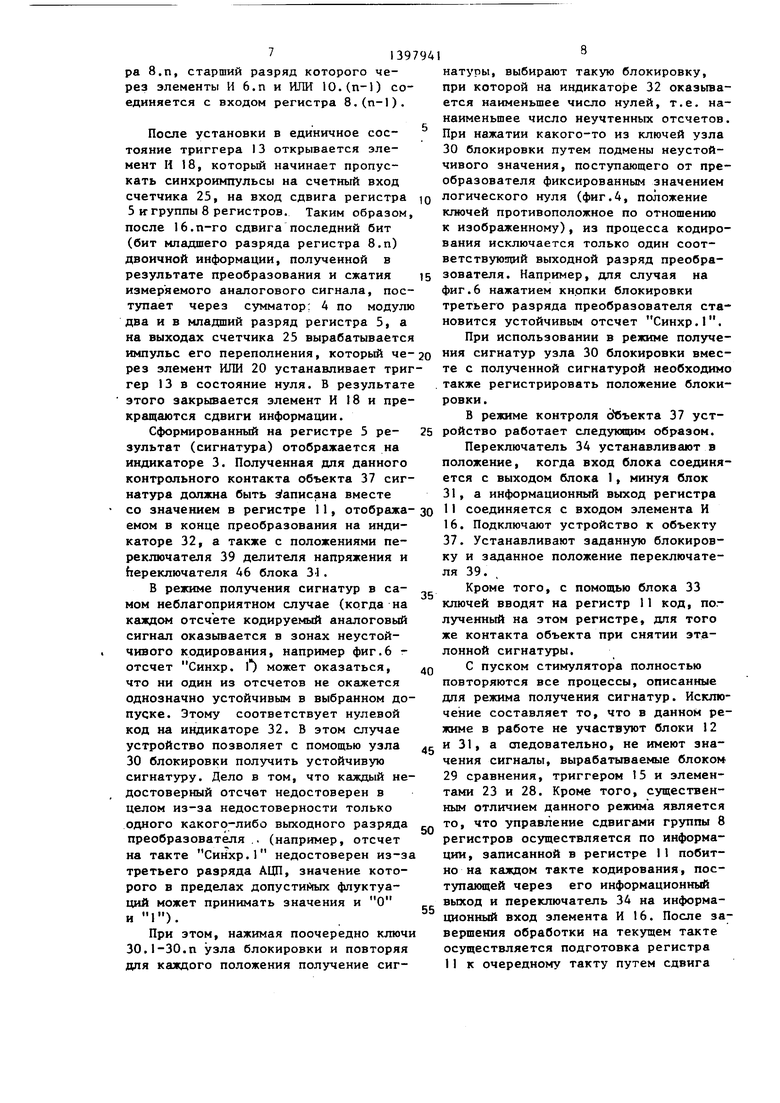

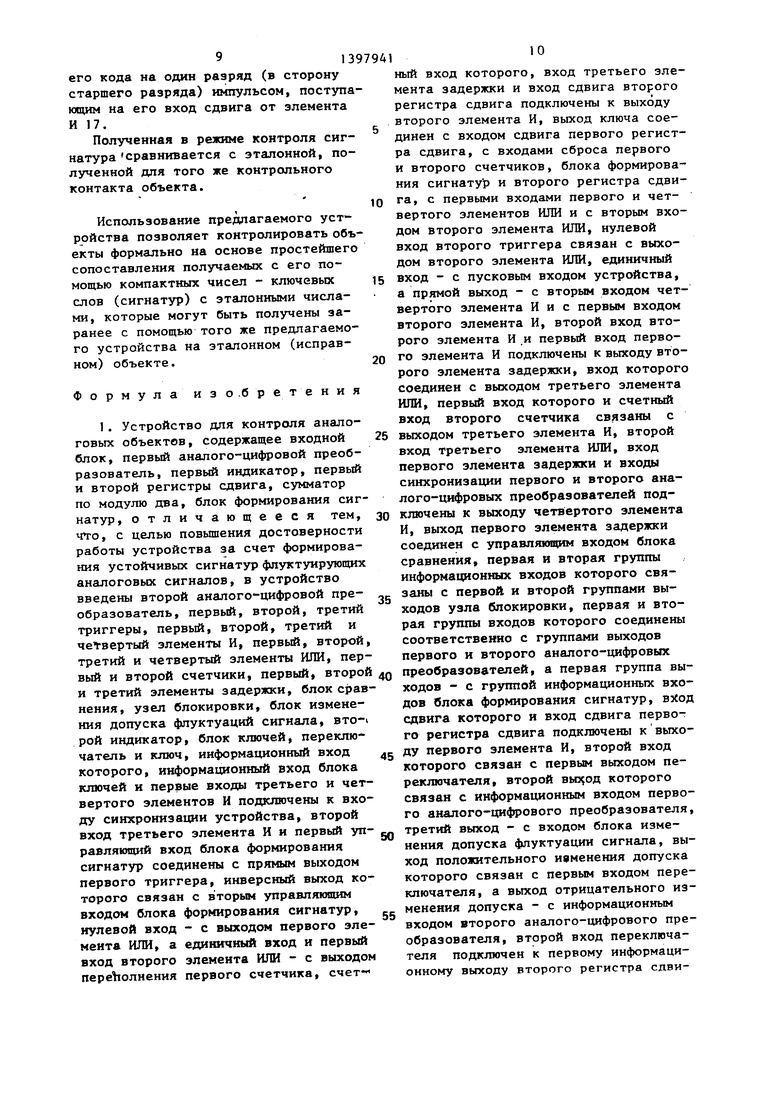

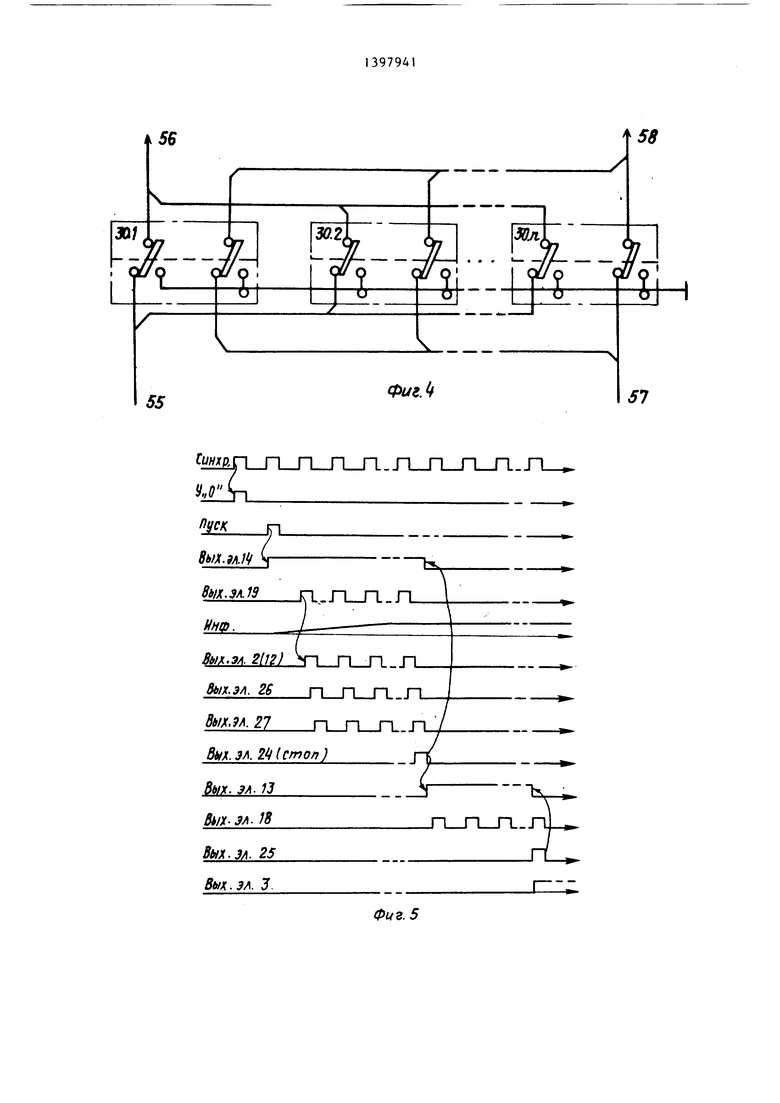

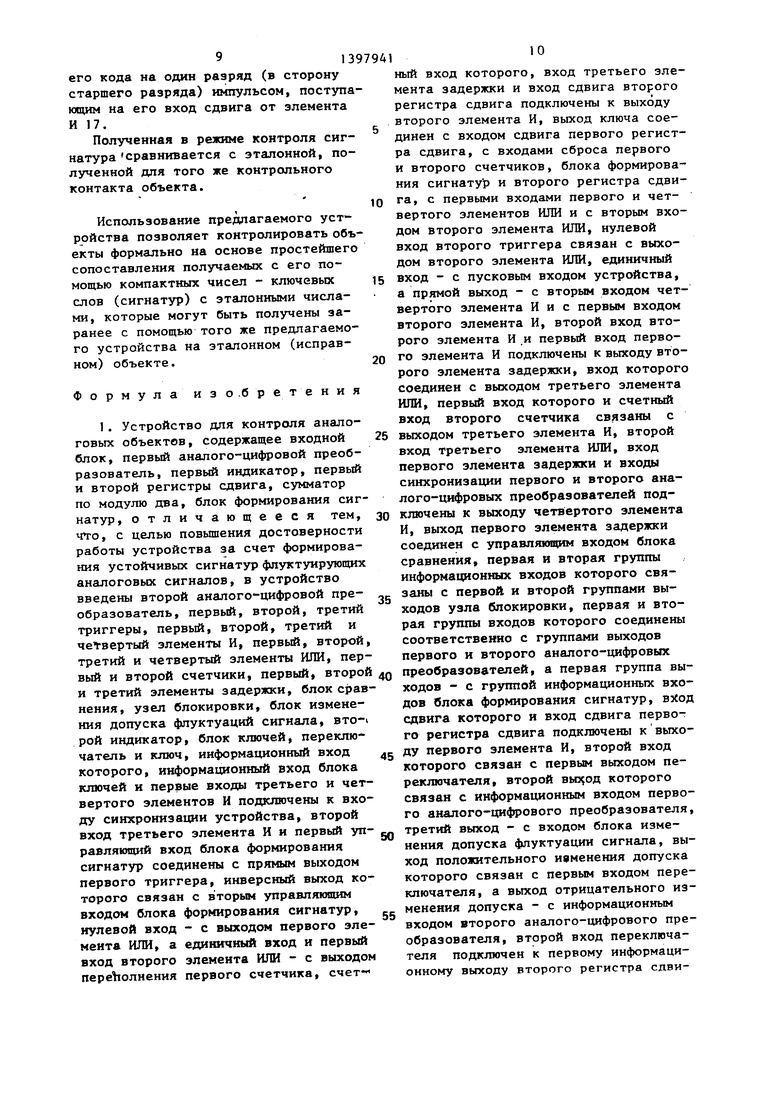

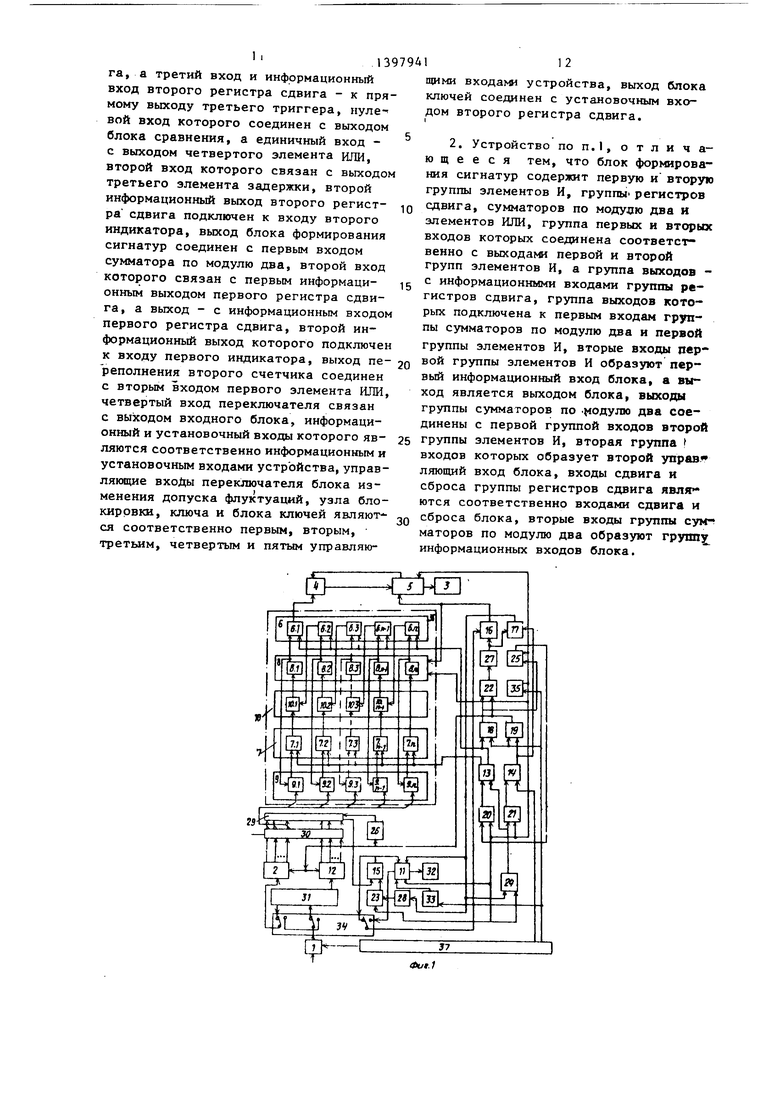

На фиг.1 представлена схема уст- ройства; на фиг.2 - пример реализации входного блока; на фиг.З - схема блока изменения допуска флуктуации сигг. нала; на фиг.4 - пример реализации узла блокировки; на фиг.З - временная диаграмма работы устройства; на фиг.6 принцип кодирования аналогового сигнала произвольной формы для шести разрядных аналого-цифровых преобразователей (АЦП).

Устройство содержит входной блок - I, первый АДП 2, первый индикатор 3, сумматор 4 по модулю два, первый регистр 5 сдвига, первую 6 и вторую 7 группы элементов И, группу 8 регист-i ров сдвига, группу 9 сумматоров по модулю два, группу 10 элементов ИЛИ, второй регистр 11 сдвига, второй АЦП 12, первый 13, второй 14 и третий 15 триггеры, первый 16, второй 17, тре- тий 18 и четвертый 19 элементы И, первый 20, второй 21, третий 22 и четвертый 23 элементы ИЛИ, первый 24 и второй 25 счетчики, первый 26, второй 27 и третий 28 элементы задержки блок 29 сравнения, узел 30 блокировки, блок 31 изменения допуска фпук-. туаций сигнала, второй индикатор 32, блок 33 ключей, переключатель 34 и ключ 35.

Блок 36 формирования сигнатур содержит элементы 6 - 10. Контролируемый объект 37 не входит в состав устройства и показан на фиг.1 для пояснения принципа его работы.

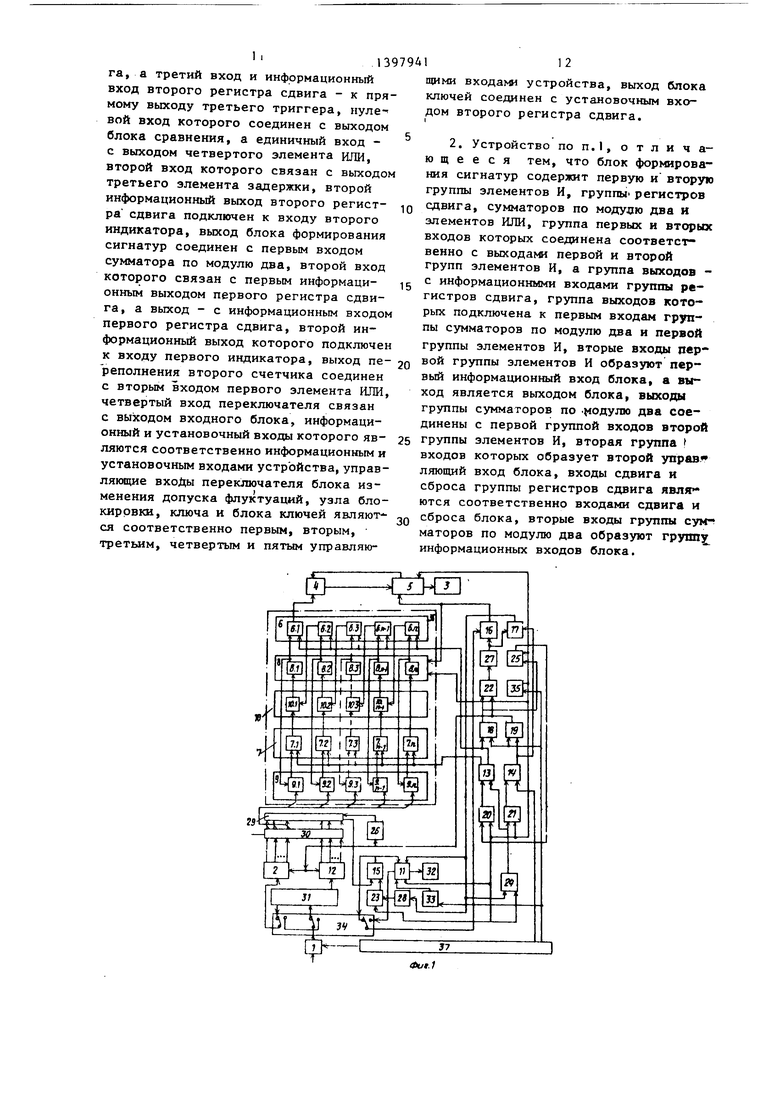

Входной блок 1 предназначен для согласования и усиления измеряемого аналогового сигнала, снимаемого с контрольных контактов объекта 37. Входной блок содержит последователь Но соединенные делитель 38 напряже НИН, переключатель 39, усилитель-преобразователь 40, усилитель-согласова- тель 41, информационный вход 42,1, второй входной полюс 42.2, вход 43, информационный выход 44 и второй вы ходной полюс 45.

Значения резисторов 38.1, 38.2,.. 38.R делителя ЗН )апряжения выбирают.-

-

I2

ся таким образом, чтобы на всех диапазонах (для всех напряжений измеряемого аналогового сигнала) использовать один и тот же преобразователь 2(12), предельное входное напряжение которого составляет несколько вольт.

Усилитель-преобразователь содержит резистор 40.1, стабилитроны 40.2 и

40.3,первый операционный усилитель

40.4,резисторы 40.5-40.7, полевой транзистор 40.8, резисторы 40.9 - 40.12 и второй операционный усилитель 40.13.

Усилитель-согласователь 41 содержит транзистор 41.1, 3MHTtep которого подключен через резистор 41.2 к источнику образцового напряжения -2В (вход 43).

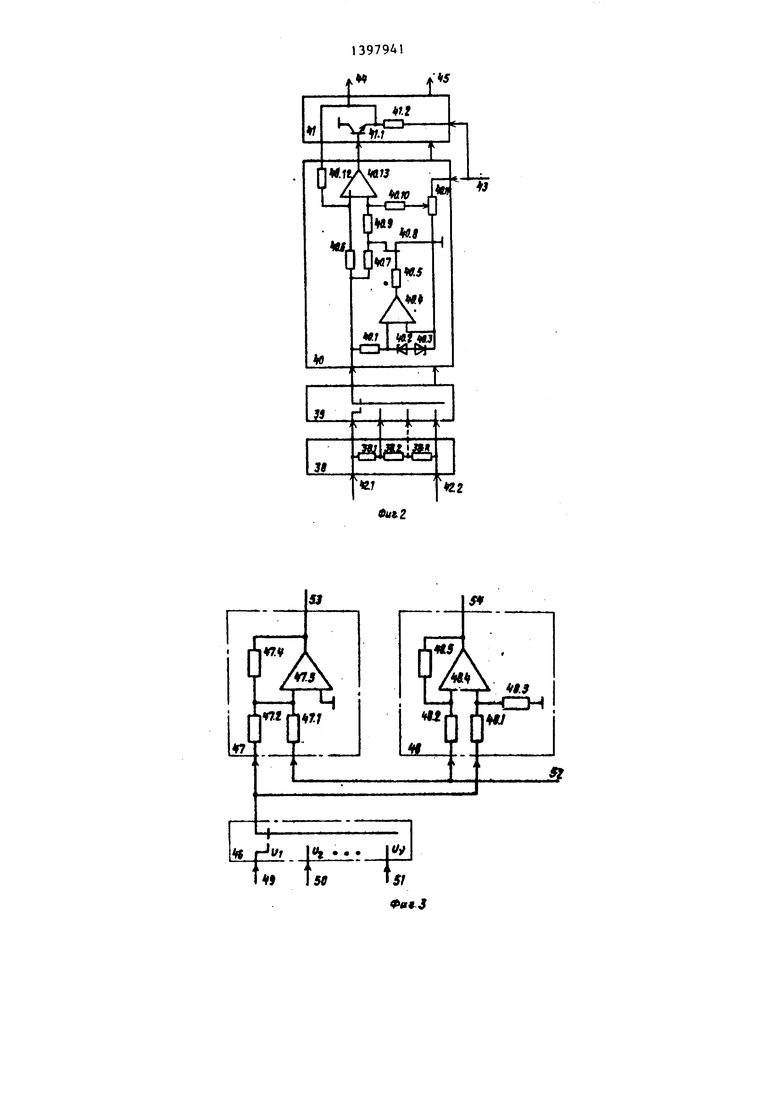

Блок 31 предназначен для обеспечения возможности изменения допуска флуктуации аналогового сигнала при использовании устройства для различных аналоговых объектов. Блок 31 содержит переключатель 46, узел 47 сложения, узел 48 вычитания. Переключатель с входами 49-51 предназначен для изменения допуска флуктуации аналогового сигнала (информации). Узел сложения предназначен для сложения аналогового сигнала со значением допуска Узел производит операцию вычитания над аналоговым сигналом и значением допуска. Блок 31 имеет вход 52 и выходы 53 и 54.

зел 30 блокировки предназначен дпя обеспечения возможности блокировки значений одного или нескольких выходных разрядов АЦП при кодировании (также при контроле) с целью исключения недостоверных разрядов АЦП И увеличения таким образом числа отсчетов достоверного кодирования. Узел 30 содержит п типовых независимых переключателей 30.1-ЗО.п на два положения и два направления с фиксацией положения (фиг.4), первые 55 и 56 и вторые 57 и 58 входы и выходы.

Устройство работает в режиме получения эталонных сигнатур и в режиме контроля аналоговых объектов.

В режиме получения эталонных сигнатур устройство работает следующим образом.

Возбуждение контролируемого обърк- та 37 осуществляется с помощью встроенного в нетч1 стимулятора. Устройс-т- во допускает игпоч1.яоваине и рнеппнм о стимулятсфа. От .с К .ч (7 на VIMDIM I3139

ство поступает сигнал Пуск, опреде- л пощий передний фронт окна измерения и сигнал Синх., обеспечивающий синхронное преобразование в устройстве аналогового сигнала, поступающего от объекта на информационный вход устройства.

Сигналы Синх. и Пуск для конкретного контролируемого объекта мо- гут быть постоянными (оптимальный случай), т.е. применяться на протяжении всего процесса контроля данного объекта. При этом перед контролем объекта к его заранее определенным контактам (гнездам) Синхр. и Пуск подключаются соответствующие входы устройства.

Поскольку для полного контроля даже Простейшего объекта требуется кон- тролировать (измерять) сигналы на совокупности различных его контактов, в процессе контроля объекта информационный вход устройства периодически должен последовательно переноситься с указанного контакта объекта на другой. Указанный перенос может осуществляться о помощью ручного щупа или автоматически по определенной программе.

Перед началом переключатель 34 устанавливают в режим получения сигнатур, (соответствует положению, указан- йому на фиг.I). Подключают входы Пуск и Синхр. устройства к одноименным выходам объекта и соединяют информационный вход устройства с первым контрольным контактом объекта. Нажимают ключ 35, который пропускает синхроимпульсы. В результате все ре- гистры, счетчики и триггеры устанавливаются в исходное состояние.

Устанавливают в соответствующее положение переключатель 39 входного блока 1, обеспечивая тем самьм согла сование уровня аналогового сигнала с устройством. С помощью блока 31 за-, дают наибольшее значение флуктуации, допускаемое для данного объекта. Исходное положение узла 30 блокировки без блокировки (указано на фиг.4).

В результате возбуждения объекта на контрольном контакте формируется его реакция - в данном случае эталонная реакция, так как получение эта- лонных сигнатур осуществляются на заведомо исправном(эталлоном ) объекте. Сигналом Пуск триггер 14 устанавливается в состояние 1 и открывае,т

g

5 0

Q

g Q

5

элемент И 19 для прохождения синхро импульсов на входы синхронизации преобразователей 2 и 12, а также на входы элемента 26 задержки и элемента ИЛИ 22 (фиг.5). Одновременно с этим на вход входного блока I поступает информация (аналоговый сигнал) .

На фиг.5 представлен усЛ|Овный (возможный) аналоговый сигнал U, который после согласования на элементах 38-41 входного блока 1 поступает на блок 31.

В блоке 31 сигнал разветвляется на два независимых канала, в одном из которых к мгновенным значениям амплитуды и аналогового сигнала прибавляется значение допуска ли, а в другом - из тех же мгновенных значений вычитается значение допуска ЛИ (фиг.6 - принцип кодирования аналогового сигнала произвольной формы). Дпя случая на фиг.6 выбрано 4U /2, т.е. допускаются гакке флуктуации аналогового сигнала, которые не пре- вьшают . Практически возможны аналоговые объекты, в которых допустимы и более значительные флуктуации аналогового сигнала, поэтому блок 31 позволяет изменять значение допуска ли с помощью переключателя 46 (допуск: 1,2,...,п).

С выхода + и сигнал поступает на вход преобразователя 2, а с выхо да -U - на преобразователь 12, которые параллельно преобразуют поступающие на них сигналы в цифровой код в одни и те же моменты времени по сигналам синхронизации (фиг.5 и 6). Цифровые коды поступают через узел 30 блокировки без изменения на группу 9 сумматоров и на блок 29 сравнения, где осуществляется их поразрядное сравнение по тем же сигналам синхронизации, но задержанным элементом 26 на время преобразования одного счета в блоках 2 и 12.

Если на некотором отсчете полученные на выходах преобразователей 2 и 12 коды не равны (фиг.6 на отсчете Синхр. Г :код АЦП 2 001111, а код АЦП 12 000111), то с выхода Неравно блока сравнения соответствующий импульс устанавливает в нуль триггер 15. При этом с его выхода логический уровень нуля через переключатель 34 поступает на управляющий вход элемента И 1 6 и тем самым блокирует прохождение через этот элемент импульса

Синхр.Г , поступающего на вход Синхр. этого элемента через элемент

27задержки, элементы ИЛИ 22 и И 19. Элемент 27 задержки учитывает время работы блока 12, блока 29 сравнения

н триггера 15. Таким образом, на вход сдвига группы 8 регистров сдвига не поступает импульс сдвига, т.е. значение отсчета на такте Синхр.Г не регистрируется.

Кроме того, уровень логического нуля (в данном случае) с выхода триггера 15 через информационный вход регистра I1 записьшается в этот регистр по импульсу, поступающему на его вхоД сдвига с выхода элемента И 17, после чего триггер 15 вновь устанавливается в единичное состояние через элемент

28задержки и элемент ИЛИ 23.

Если же на некотором отсчете, например на отсчете Синхр.2, полученные на выходах блоков 2 и 12 коды равны фиг.6 - на отсчете Синхр. код АЦП 2 код АЦП 1 0001), то с выхода Неравно блока 29 сравнения соответствующий импульс не вьфабатыва- ется и не изменяется единичное состояние триггера 15. При этом с выхода элемента И 16 на вход сдвига группы 8 сдвиговых регистров поступает импульс сдвига, а в регистр 11 запи-; сывается единица.

Дальнейшая цифровая обработка осуществляется следующим образом.

Находящийся в состоянии нуля триггер 13 держит в открытом состоянии элементы (7.1-7.п) И и в закрытом состоянии элементы (6.1-6.п) И. С переходом триггера 1 4 из состояния нуля в состояние единицы элемент И 19 начинает пропускать синхроимпульсы через элемент ИЛИ 22, элемент 27 задержки и элемент И 16 на вход сдвига группы 8 сдвиговых регистров. При этом по каждому синхроимпульсу в младший разряд каждого регистра 8.1-8.П через группу 9 сумматоров по модулю два и группы 7 и IО элементов И и ИЛИ принимаются соответствующие биты информации О или 1, сформированные в данный момент времени на соответствующих выходах преобразователя 2.

Со всех выходов блока 2 (1п) в

сдвиговые регистры 8.1-8.П биты информации принимаются параллельно. С первого выхода блока 2 через сумматор 9.1. элементы И 7.1 и ИЛИ 10.1 по каждому синхроимпульсу один бит информации

0

5

0

5

0

5

0

В

0

5

принимается в младший разряд регистра 8.1 с одновременным сдвигом всего содержимого регистра на один разряд от младших разрядов к старшим.

На первых тактах в связи с тем, что исходное состояние регистров 8.1- 8.П нулевое, через цепь обратной связи из регистра 8.1 на второй вход сумматора 9.1 передаются нулевые биты, но затем, когда единичные биты в результате сдвигов достигают старшего разряда регистра, от которого отведена цепь обратной связи, на соответствующих тактах в младший разряд регистра принимается сумма по модулю -. два значений бита цепи обратной связи и бита, поступающего с первого выхода преобразователя 2. При этом в регистре 8.1 осуществляется формирование (сжатие) двоичного кода, с высокой достоверностью соответствующего исходной двоичной последовательности, причем независимо от ее длины.

Аналогичным образом раздельно по каждому выходу осуществляется сжатие двоичной последовательности, формируемой на остальных выходах преобразователя 2, в регистрах 8.2-8.П ссуэт ветственно.

Процесс сжатия информации в регистрах 8.1-8.П продолжается до тех пор, пока от. счетчика 24 не П9ступит сигнал его переполнения (Стоп). По сигналу Стоп через элемент ИЛИ 21 триггер 14 устанавливается в нулевое состояние, в результате чего закрьгаа- ется элемент И 19 и прекращаются сдвиги информации в регистрах 8.1-8.п. Кроме того, по сигналу Стоп уста - навливается в единичное состояние триггер 13, закрьшающий элементы И 7.1-7.П и открьшающий элементы И 6.1- 6.п. С этого момента никакие изменения на выходах преобразователя 2 не влияют на двоичные коды, зафиксированные в регистрах 8.1-8.п. Происходит реконфигурация регистров 8.1-8.П, которые с помощью группы элементов И последовательно соединяются между собой. Старший разряд старшего регистра 8.1 при этом через элемент 6.1 соединяется с первым входом сумматора 4 по модулю два, старший разряд регистра 8.2 через элементы И 6.2 и ИЛИ 10.1 - с входом (с младшим разрядом) регистра 8.1 и т.д. вплоть до регист71397941

pa 8.П, старший разряд которого через элементы И б.п и ИЛИ lO.(n-l) соединяется с входом регистра 8.(п-1).

После установки в единичное состояние триггера I3 открывается элемент И 18, который начинает пропускать синхроимпульсы на счетный вход счетчика 25, на вход сдвига регистра 5 к группы 8 регистров. Таким образом, после 16.П-ГО сдвига последний бит (бит младшего разряда регистра 8.п) двоичной информации, полученной в результате преобразования и сжатия измеряемого аналогового сигнала, поступает через сумматор: А по модулю два и в младший разряд регистра 5, а на выходах счетчика 25 вырабатывается импульс его переполнения, который через элемент ИЛИ 20 устанавливает триг гер 13 в состояние нуля. В результате этого закрывается элемент И 18 и прекращаются сдвиги информации.

Сформированный на регистре 5 результат (сигиатура) отображается на индикаторе 3. Полученная для данного контрольного контакта объекта 37 сигнатура должна быть Написана вместе со значением в регистре 11, отображаемом в конце преобразования на индикаторе 32, а также с положениями переключателя 39 делителя напряжения и Ьереключателя 46 блока 31.

В режиме получения сигнатур в самом неблагоприятном случае (когда на каждом отсчете кодируемый аналоговый сигнал оказывается в зонах неустойчивого кодирования, например фиг.6 - отсчет Синхр. l) может оказаться, что ни один из отсчетов не окажется однозначно устойчивым в выбранном допуске. Этому соответствует нулевой код на индикаторе 32. В этом случае устройство позволяет с помощью узла 30 блокировки получить устойчивую сигнатуру. Дело в том, что каждый недостоверный отсчет недостоверен в целом из-за недостоверности только одного какого-либо выходного разряда преобразователя ,, (например, отсчет на такте Синхр.1 недостоверен из-за третьего разряда АЦП, значение которого в пределах допустийых флуктуации может принимать значения и О и 1).

При этом, нажимая поочередно ключи 30.1-ЗО.п узла блокировки и повторяя для каждого положения получение сиг

5

5

0

5

0

5

0

5

натуры, выбирают такую блокировку, при которой на индикаторе 32 оказьгаа- ется наименьшее число нулей, т.е. на- наименьшее число неучтенных отсчетов. При нажатии какого-то из ключей узла 30 блокировки путем подмены неустойчивого значения, поступающего от преобразователя фиксированным значением логического нуля (фиг.4, положение ключей противоположное по отношению к изображенному), нз процесса кодирования исключается только один соответствующий выходной разряд преобразователя. Например, для случая на фиг.6 нажатием кнопки блокировки третьего разряда преобразователя становится устойчивым отсчет Синхр.1.

При использовании в режиме получения сигнатур узла 30 блокировки вместе с полученной сигнатурой необходимо также регистрировать положение блокировки.

В режиме контроля Ь бъекта 37 устройство работает следующим образом.

Переключатель 34 устанавливают в положение, когда вход блока соединяется с выходом блока 1, минуя блок 31, а информационный выход регистра 11 соединяется с входом элемента И 16. Подключают устройство к объекту 37. Устанавливают заданную блокировку и заданное положение переключателя 39.

Кроме того, с помощью блока 33 ключей вводят на регистр 11 код, по.- лученный на этом регистре, для того же контакта объекта при снятии эталонной сигнатуры.

С пуском стимулятора полностью повторяются все процессы, описанные дпя режима получения сигнатур. Исключение составляет то, что в данном режиме в работе не участвуют блоки 12 и 31, а следовательно, не имеют значения сигналы, вырабатьгааемые блокон 29 сравнения, триггером 15 и элементами 23 и 28. Кроме того, существенным отличием данного режима является то, что управление сдвигами группы 8 регистров осуществляется по информации, записанной в регистре 11 побит- но на каждом такте кодирования, поступающей через его информационный выход и переключатель 34 на информационный вход элемента И 16. После завершения обработки на текущем такте осуществляется подготовка регистра 11 к очередному такту путем сдвига

его кода на один разряд (в сторону старшего разряда) импульсом, поступа- кяцим на его вход сдвига от элемента И 17.

Полученная в режиме контроля сигнатура сравнивается с эталонной, по лученной для того же контрольного контакта объекта.

Использование предлагаемого устройства позволяет контролировать объекты формально на основе простейшего сопоставления получаемых с его помощью компактных чисел - ключевых слов (сигнатур) с эталонными числами, которые могут быть получены заранее с помощью того же предлагаемого устройства на эталонном (исправном) объекте.

Формула изо.бретения

1. Устройство для контроля аналоговых объектов, содержащее входной блок, первый аналого-цифровой преобразователь, первый индикатор, первый и второй регистры сдвига, сумматор по модулю два, блок формирования сигнатур, отличающееся тем, что, с целью повышения достоверности работы устройства за счет формирования устойчивых сигнатур флуктуирующих аналоговых сигналов, в устройство введены второй аналого-цифровой преобразователь, первый, второй, третий триггеры, первый, второй, третий и четвертый элементы И, первый, второй третий и четвертый элементы ИЛИ, пер0

5

ный вход которого, вход третьего элемента задержки и вход сдвига второго регистра сдвига подключены к выходу второго элемента И, выход ключа соединен с входом сдвига первого регистра сдвига, с входами сброса первого и второго счетчиков, блока формирования сигнатур и второго регистра сдвига, с первыми входами первого и четвертого элементов ИЛИ и с вторым входом второго элемента ИЛИ, нулевой вход второго триггера связан с выходом второго элемента ИЛИ, единичный вход - с пусковым входом устройства, а прямой выход - с вторым входом четвертого элемента И и с первым входом второго элемента И, второй вход второго элемента И и первый вход первого элемента И подключены к выходу второго элемента задержки, вход которого соединен с выходом третьего элемента ШШ, первый вход которого и счетный вход второго счетчика связаны с 5 выходом третьего элемента И, второй вход третьего элемента ШШ, вход первого элемента задержки и входы синхронизации первого и второго аналого-цифровых преобразователей подключены к выходу четвертого элемента И, выход первого элемента задержки соединен с управляимцим входом блока сравнения, первая и вторая группы информационных входов которого связаны с первой и второй группами выходов узла блокировки, первая и вторая группы входов которого соединены соответственно с группами выходов первого и второго аналого-цифровых

0

0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

| Устройство для контроля аналоговых объектов | 1988 |

|

SU1522239A1 |

| Устройство для допускового контроля параметров объектов | 1982 |

|

SU1056134A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Сигнатурный анализатор | 1987 |

|

SU1444776A1 |

| Устройство для контроля экспоненциальных процессов | 1990 |

|

SU1732331A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1302435A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Устройство для определения амплитудно-частотных характеристик объектов | 1989 |

|

SU1689876A1 |

Изобретение относится к вычислительной технике и может быть исполь- ювано для контроля аналоговых объектов. Целью изобретения является повышение достоверности работы устройства за счет формирования устойчивых сигнатур флуктуирующих аналого 41х сигналов . Устройство содержит входной блок, два аналого-цифровых преобразователя, два индикатора, сумматор по модулю два, два регистра сдвига, блок формирования сигнатур, три триггера, четьфе элемента И, четыре элемента ИЛИ, два счетчика, три элемента задержки, блоки сравнения ключей и изменения допуска флуктуации сигнала, узел блокировки, переключатель и ключ. Раскрыто построение блока формирования сигнатур. Устройство позволяет контролировать объекты с произвольно флуктуирующими выходными сигналами в заданных пределах допустимых флуктуации. 1 з.п.ф-лы, 6 ил. i (Л

вый и второй счетчики, первый, второй допреобразователей, а первая группа выи третий элементы задержки, блок срав-ходов - с группой информационных вхонения, узел блокировки, блок измене-дов блока формирования сигнатур, вход

ния допуска флуктуации сигнала, BTO-Iсдвига которого и вход сдвига перворой индикатор, блок ключей, переклю-го регистра сдвига подключены к выхочатель и ключ, ииформациоиный вход которого, информационный вход блока ключей и первые входы третьего и четвертого элементов И подключены к входу синхронизации устройства, второй вход третьего элемента И и первый управляющий вход блока формирования сигнатур соединены с прямым выходом первого триггера, инверсный выход которого связан с вторым управляющим входом блока формирования сигиатур, нулевой вход - с выходом первого элемента ИЛИ, а единичный вход и первый вход второго элемента ИЛИ - с выходом переполнения первого счетчика, счет-

ДУ первого элемента И, второй вход которого связан с первым выходом переключателя, второй которого связан с информационным входом первого аналого-цифрового преобразователя, третий выход - с входом блока изменения допуска флуктуации сигнала, выход положительного изменения допуска которого связан с первым входом переключателя, а выход отрицательного из

менения допуска - с информационным входом второго аналого-цифрового преобразователя, второй вход переключателя подключен к первому информационному выходу второго регистра сдви I

га, a третий вход и информационный вход второго регистра сдвига - к прямому вькоду третьего триггера, нулевой вход которого соединен с выходом блока сравнения, а единичный вход - с выходом четвертого элемента ИЛИ, второй вход которого связан с выходом третьего элемента задержки, второй информационньА выход второго регистра сдвига подключен к входу второго индикатора, выход блока формирования сигнатур соединен с первым входом сумматора по модулю два, второй вход которого связан с первым информационным выходом первого регистра сдвига, а выход - с информационным входом первого регистра сдвига, второй информационный выход которого подключен

139

к входу первого индикатора, выход пе- 2о вой группы элементов И образуют первый информационный вход блока, а выход является выходом блока, выходы группы сумматоров по .нодулю два соединены с первой группой входов второй группы элементов И, вторая группа f входов которых образует второй управ ляющий вход блока, входы сдвига и сброса группы регистров сдвига ются соответственно входами сдвига и сброса блока, вторые входы группы сум маторов по модулю два образуют rpynnj информационных входов блока.

реполнения второго счетчика соединен с вторым входом первого элемента ИЛИ, четвертый вход переключателя связан с выходом входного блока, информационный и установочный входы которого являются соответственно информационным и установочным входами устройства, управляющие входы переключателя блока изменения допуска флуктуации, узла блокировки, ключа и блока ключей являют- ся соответственно первым, вторым, третьим, четвертым и пятым управляю1397941

12

щими входами устройства, выход блока ключей соединен с установочным входом второго регистра сдвига.

2, Устройство по П.1, о тли ч а- ю щ е е с я тем, что блок формирования сигнатур содержит первую и вторую группы элементов И, группы регистров сдвига, сумматоров по модудю два и элементов ИЛИ, группа первых и вторых входов которых соединена соответст венно с выходами первой и второй групп элементов И, а группа выходов - с информационными входами группы регистров сдвига, группа выходов которых подключена к первым входам группы сумматоров по модулю два и первой группы элементов И, вторые входы пер

вый информационный вход блока, а выход является выходом блока, выходы группы сумматоров по .нодулю два соединены с первой группой входов второй группы элементов И, вторая группа f входов которых образует второй управ ляющий вход блока, входы сдвига и сброса группы регистров сдвига ются соответственно входами сдвига и сброса блока, вторые входы группы сум маторов по модулю два образуют rpynnj информационных входов блока.

.t

Huf 0t M

19 5вtSf

«2

56

зог

55

Вых. ЗА 3.

58

Фиг. 5

CuHxp.1 ,2 Фиг. 6

CuHxpi 3

| Устройство для контроля цифровыхОб'ЕКТОВ | 1979 |

|

SU851410A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля дискретныхОб'ЕКТОВ | 1978 |

|

SU798852A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-05-23—Публикация

1986-11-17—Подача