со

о

sj

;D

СХ)

LFJ

Изобретение относится к электросвязи и может быть использовано в коммутационной технике для построения узлов коммутации временных каналов .

Целью изобретения является упрощение устройства путем упрощения временных коммутаторов.

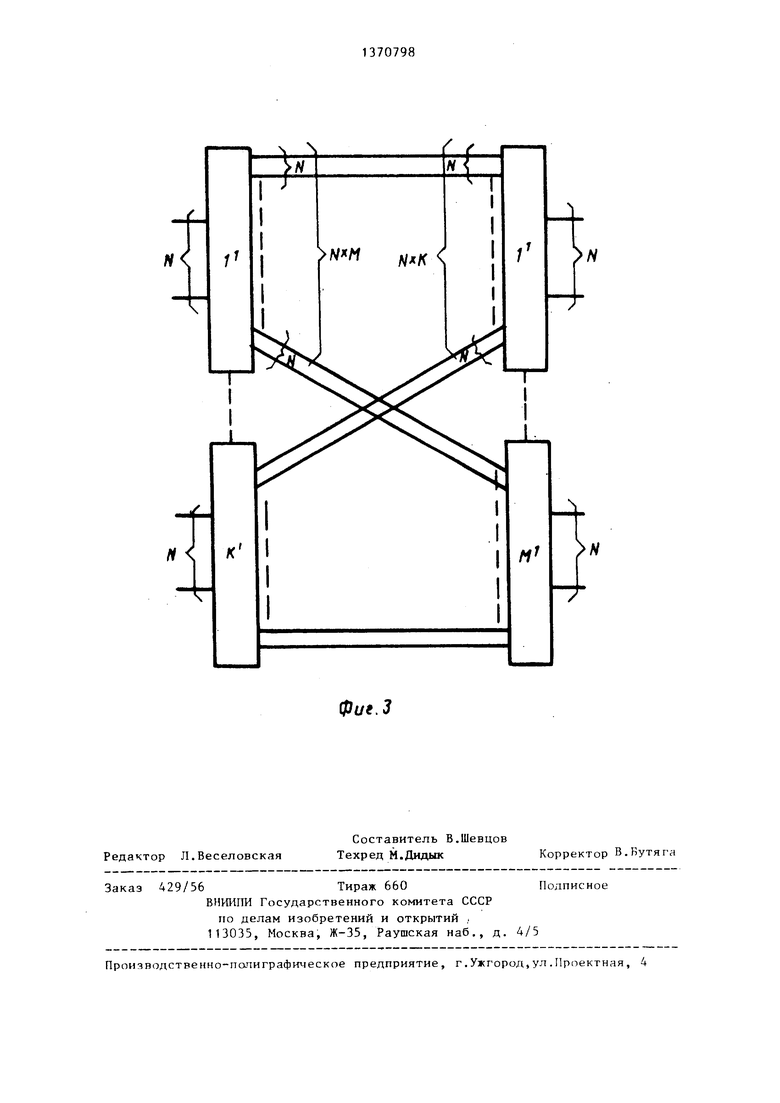

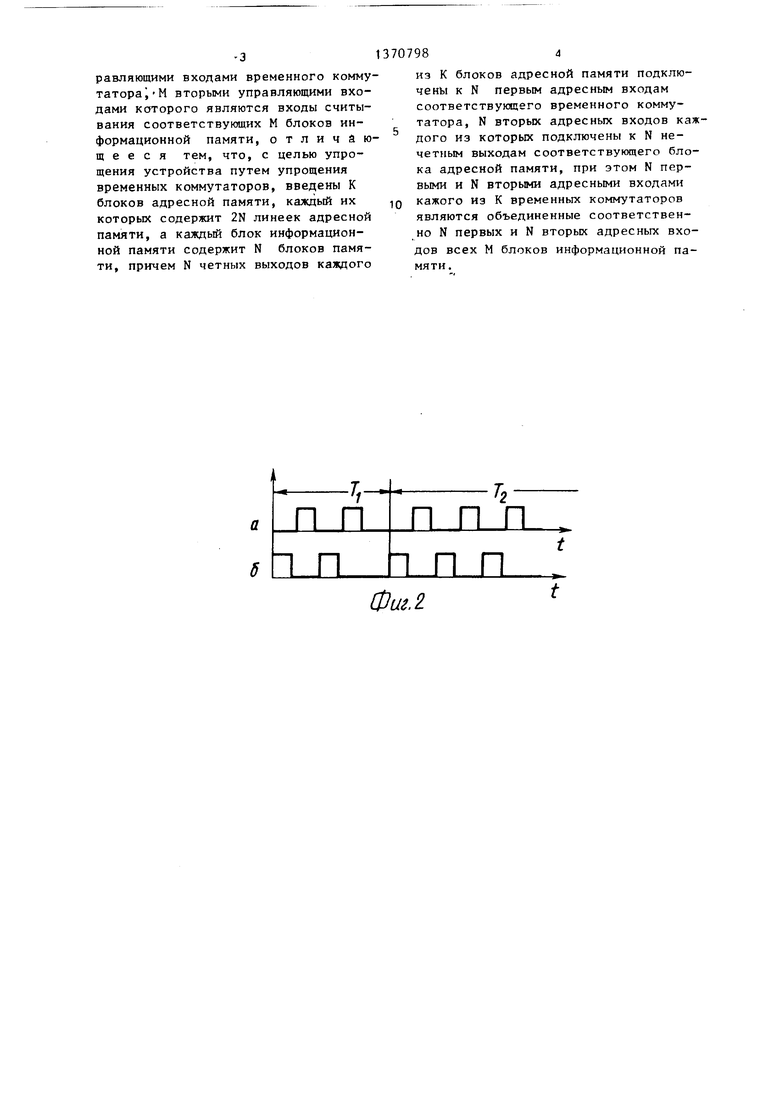

На фиг.1 приведена структурная электрическая схема устройства пространственно-временной коммутации} на фиг,2 - временные диаграммы, поясняющие работу устройства; на фиг.З - изображение пространственно- го эквивалента устройства. I Устройство пространственно-временной коммутации содержит К блоков 1 управления временной коммутацией, где К - число входных коммутируемых уплотненных линий, М блоков 2 управления пространственной коммутацией, где М - число выходных уплотненных линий. К временных коммутаторов 3, каждый из которых содержит М блоков 4 информационной памяти,каждый из которых содержит N блоков памяти, а также К блоков 5 адресной памяти, каждый из которых содержит 2N линее адресной памяти. Устройство простран ственно-временной коммутации работае следующим образом.

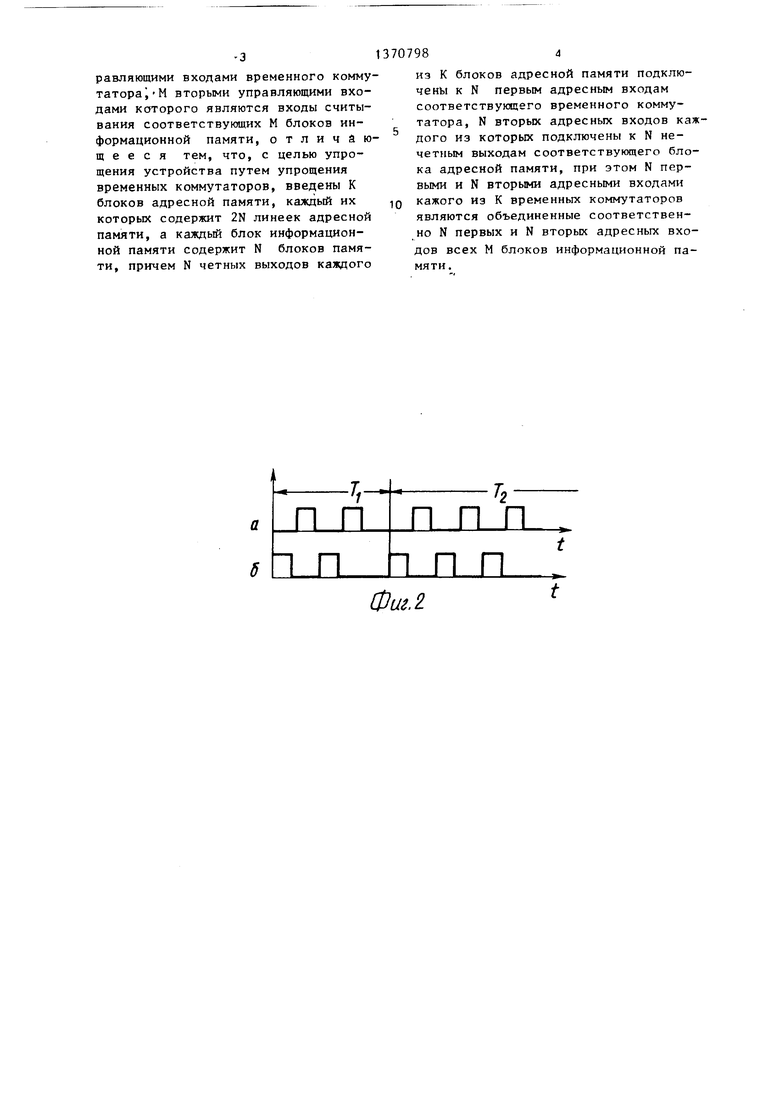

В каждый цикл Т передачи (фиг.2), совпадающий с циклом коммутации,по уплотненным линиям последовательно поступают информационные сигналы N каналов. В цикле Т вьщеляют 2N тактов: в четные такты (фиг.2а) информационные сигналы считывают из временных коммутаторов 3 в выходные уплотненные линии, в нечетные такты (фиг. 2б) информационные сигналы записывают из входных уплотненных линий в блоки 4 временных коммутаторов 3.

Считывание информационных сигналов временных каналов в выходную уплотненную линию производится циклически, всегда одинаково: в первом такте считывается сигнал из первой ячейки блока 4, во втором такте - из второй и в N-M - из N-й ячейки блока 4. При этом блок 4, содержащий эту ячейку, включается с помощью блока 2 (по проводу Считывание).

Запись информационных сигналов из входной уплотненной линии производится ациклически: информационный сигнал очередного канала записывается в ту ячейку блока 4, номер кото

o

0

5

0

5

0

5

0

5

рой равен номеру коммутируемого канала в выходной уплотненной линии (для согласования циклического счи- тьшания). При этом блок 4, содержащий эту ячейку, включается с помощью блока 1 (по проводу Запись).

Число линеек блока 5 соответствует 2N тактам цикла Т: из четных линеек поступает код адреса в четные такты (фиг.2а), из нечетных - в нечетные такты (фиг.2б).

Блоки 1 и 2 аналогично содержат адресные линейки и дешифратор адреса, по N адресных линеек в каждом блоке. Из блоков 1 поступают сигналы выбора блока А в нечетные такты, из блоков 2 - в четные. Формула изобретения

Устройство пространственно-временной коммутации, содержащее К блоков управления временной коммутацией (где К - число входных коммутируемых уплотненных линий, в каждой из которых уплотнено N каналов), М - блоков управления пространственной коммутацией (где М - число выходных уплотненных линий) и К временных коммутаторов, каждый из которых содержит М блоков информационной памяти, причем информационные входы всех К временных коммутаторов подключены к соответствующим К входньм коммутируемым уплотненным линиям, одноименные М информационных выходов всех К временных коммутаторов объединены и подключены к соответствующим М выходным уплотненным линиям, М первых управляющих входов каждого из К временных коммутаторов подключены к соответствующим М выходам каждого из К соответствующего блока управления временной коммутацией, а К выходов каждого из М блоков управления пространственной коммутацией подключены к каждому из М вхоторых управляющих входов соответствующих К временных коммутаторов, при этом в каждом из К временных коммутаторов информационные входы всех М блоков информационной памяти объединены и являются информационным входом временного коммутатора, М информационными выходами которого являются информационные выходы соот- . ветствующих М блоков информационной памяти, входы записи которых являются соответствующими М первыми уп 3

равляющими входами временного комму татора М вторыми управляющими входами которого являются входы считывания соответствующих М блоков информационной памяти, отличаю щ е е с я тем, что, с целью упрощения устройства путем упрощения временных коммутаторов, введены К блоков адресной памяти, каждый их которых содержит 2N линеек адресной памяти, а каждый блок информационной памяти содержит N блоков памяти, причем N четных выходов каждого

3707984

из к блоков адресной памяти подключены к N первым адресным входам соответствующего временного коммутатора, N вторых адресных входов каждого из которых подключены к N нечетным выходам соответствующего блока адресной памяти, при этом N первыми и N вторыми адресными входами кажого из К временных коммутаторов являются объединенные соответственно N первых и N вторых адресных входов всех М блоков информационной памяти.

10

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для пространственно-временной коммутации | 1976 |

|

SU664314A1 |

| Неблокирующее устройство пространственно-временной коммутации | 1981 |

|

SU1131045A1 |

| Устройство пространственно-временной коммутации | 1975 |

|

SU543206A1 |

| Устройство для асинхронной коммутации цифровых сигналов | 1987 |

|

SU1506584A1 |

| Многокаскадная пространственно-временная коммутационная система | 1972 |

|

SU450349A1 |

| Устройство коммутации с эластичной памятью | 1988 |

|

SU1647921A1 |

| Модуль коммутации | 1972 |

|

SU447836A1 |

| Устройство пространственно-временной коммутации | 1990 |

|

SU1753624A1 |

| Устройство для контроля коммутационной системы | 1986 |

|

SU1401639A1 |

| Устройство пространсктвенно-временной коммутации | 1978 |

|

SU684772A1 |

Изобертение относится к области электросвязи и м.б. использовано в ком 1утационной технике. Цель изобретения - упрощение устр-ва путем упрощения временных коммутаторов. Устр-во содержит К блоков 1 управления временной коммутации, где К - число входных коммути уемых уплотненных линий, М блоков 2 управления пространственной коммутацией, где М- число выходных уплотненных линий. К временных коммутаторов 3, каждый из которых содержит М блоков 4 информационной памяти,каждый из которых содержит N блоков памяти. Путем упрощения временных коммутаторов 3 введены К блоков адресной памяти 5, каждый из которых содержит 2N линеек адресной памяти. Причем N четньпс выходов каждого из К блоков адресной памяти подключены к N первым адресным входам соответствующего временного коммутатора, N вторых адресных входов каждого из которых подключены к N нечетным выходам соответствующего блока адресной памяти 5. Число линеек блока 5 соответствует 2N тактам цикла Т: из четных линеек Поступает код адреса в четные такты, из нечетных - в нечетные такты. 1 ил. (Л

Фиг. 2.

к

фие.З

м

| Устройство для пространственно-временной коммутации | 1976 |

|

SU664314A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-01-30—Публикация

1986-03-03—Подача