1

Изобретение относится к области связи, в частности к про странственно-временным коммутационным системам, базирующимся на линиях с временным уплотнением.

Известны устройства коммутации пространственного типа с синхронным принципом коммутации, которые работают только с устройством управления системы и требуют бготродействущих элементов для их реализации.

В предложенном модуле коммутации впервые осуществлена асинхронная пространственная коммутация, которая достигнута путем введения в модуль коммутации блоков памяти, схемы распределения приоритетов и дополнительных адресных шин. Это позволяет снизить требования к быстродействию элементов, упростить пространственную коммутацию и изъять управление модулем коммутации.

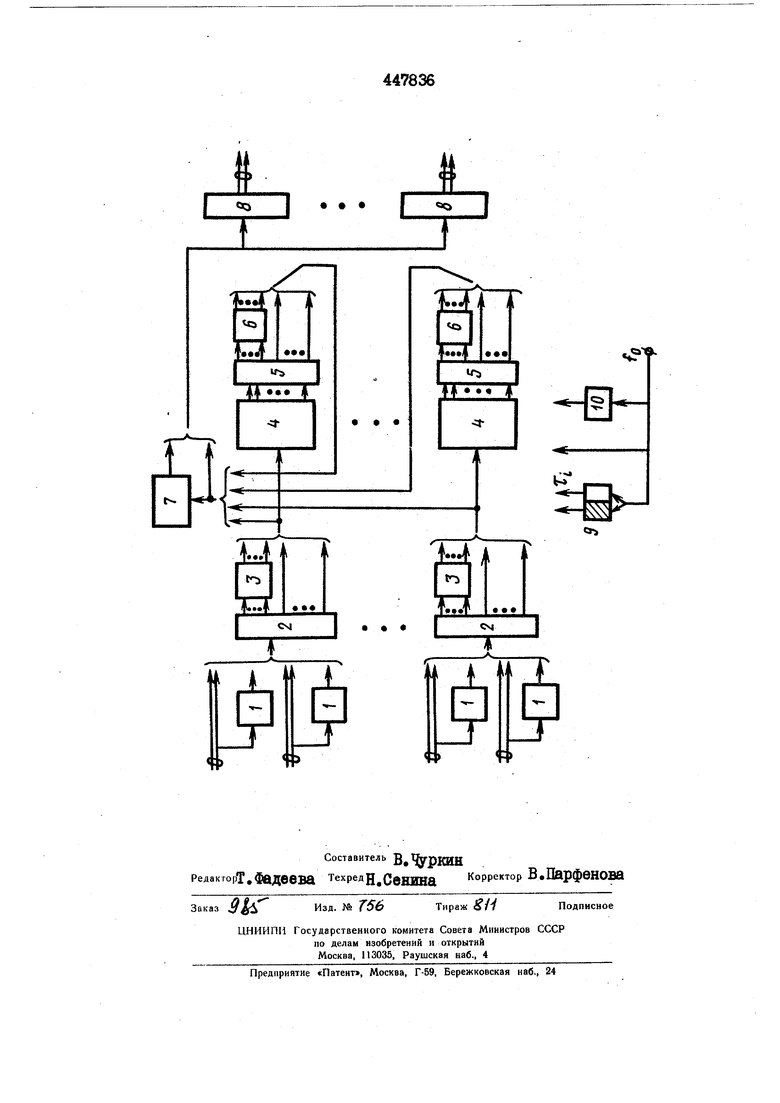

На чертеже изображен предложенный модуль коммутации.

Он состоит из входных дешифраторов 1 для опознавания информации входных адресно-информационных магистралей, входных регистров 2 для промежуточного хранения коммутируемой информации, дешифраторов 3 для определения номера выходного регистра, в который необходимо выдать информацию, блоков памяти 4 для хранения ин- i формации в процессе асинхронной коммутации, регистров 5 для промежуточного хранения информации, считанной из блоков памяти и подготовленной для коммутации, дешифраторов б для определения номера выходного регистра, в который требуется выдать информацию, схемы распределения приоритетов 7 для определения очередности обслуживания регистров с коммутируемо информацией, выходных регистров 8 |лля промежуточного хранения информации, триггера -9 и схемы НЕ Ю для выработки тактовых импульсов, синхронизирующих работу модуля коммутации. Модуль коммутации рабссает следующим образом. По m входным адресно-информационным магистралям параллельным кодом поступает информация в сопровождении адресов (номеров) временных позиций выходных уплотненных линий, в которые требуется ее выдать. Если информация принадлежит одной из уплотненных линий, обслуживаемых с помощью модуля кшмутации, то дешифраторы 1 опознают ее и производят запись на регистры 2, Каждый входной регистр 2 поочередно обслуживает две адресноинформационные магистрали и выдает их информацию в выходные регистры 8 или записывает в блоки памяти 4, если выходные регистры заняты. Номер выходного регистра, в который необходимо выдать информацию из входных регистров, определяется дешифраторами 3. Информация, записанная в блоки памяти 4, считывается и записывается на регистры 5« При этом адреса, сопровождающие информацию поступают на дешифраторы б. Считывание информации из блоков памяти 4 и запись ее на регистры 5 происходит последовательно по мере выдачи информации на выходные регистры 8. При этом дешифраторы б определяют номер выходного регистра для записи информации. Сигналы с выходов дешифраторов 3 и б и блоков памяти 4, определяющие уровень их заполнения, поступаю на схему распределения приоритетов 7, которая вырабатывает сигналы, определяющие очередность обслуживания регистров 2 л 5 (преимущественно обслуживаютОН наиболее залояненные блоки памяти). Регистры 8 обслуживают выходные адреоно информационные магистрали модуля коммутации. Триггер У и схема НЕ 10 с помощью частоты 1о вырабатывают тактовые импульсы «С синхронизирующие работу всех устройств модуля коммутации, ИЗОБРЕТЕНИЯ Модуль коммутации, содержащий регистры информации, дешифраторы адреса, триггер тактов и схему НЕ, отличающийся тем, что, с целью снижения требований к быстродействию элементов и упрощения коммутации, в него введены блоки памяти, схема распределения приоритетов и адресные шины, при этом входные магистрали подключены ко входам первых деШ1фраторов адреса и регистров информации, выходы которых соединены со входами вторых дешифраторов адреса и блоков памяти, выходы блоков памяти подключены ко входам схемы распределения приоритетов и вторых регистров информации, а их выходы подклшены ко входам третьих дешифраторов, выходы которых совместно с выходами вторых дешифраторов подключены ко входам схемы распределения приоритетов, а выходы последней совместно с выходами первых и вторых регистров информации соединены со входами третьих регистров информации, к выходам которых подключены выходные магистрали, шина синхронизирующей частоты подключена ко входу схемы НЕ, триггеру тактов и ко входам вторых и третьих дешифраторов, выходы схемы НЕ и триггера тактов соединены со входами блоков памяти и регистров информации.

r

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ КАНАЛАМИ | 1973 |

|

SU386395A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство синхронного уплотнения | 1974 |

|

SU496696A1 |

| Устройство связи для вычислительной системы | 1981 |

|

SU1275453A1 |

| Устройство для управления многоканальной измерительной системой | 1983 |

|

SU1149255A1 |

| Устройство для управления сверхоперативной буферной памятью мультипроцессорной ЭВМ | 1981 |

|

SU980097A1 |

| Устройство для обмена информацией | 1980 |

|

SU955014A1 |

| Система для обмена информацией | 1980 |

|

SU980087A1 |

| Устройство для обмена данными | 1981 |

|

SU1012235A1 |

s

i.. J

u

i I i

(

Л

Авторы

Даты

1974-10-25—Публикация

1972-07-05—Подача