а гв 17

Л /5

А.

(Л

16

оо

4::ь Ю

1IH, -.

r5fSJ7 /5ЛУ//

Изобретение относится к вычислительной технике и может быть использовано в устройствах обмена информацией по общей магистрали между процессорами в многопроцессорной вычислительной системе.

Цель изобретения - расширение области применения устройства за счет изменения приоритетов при обслуживании запросов.

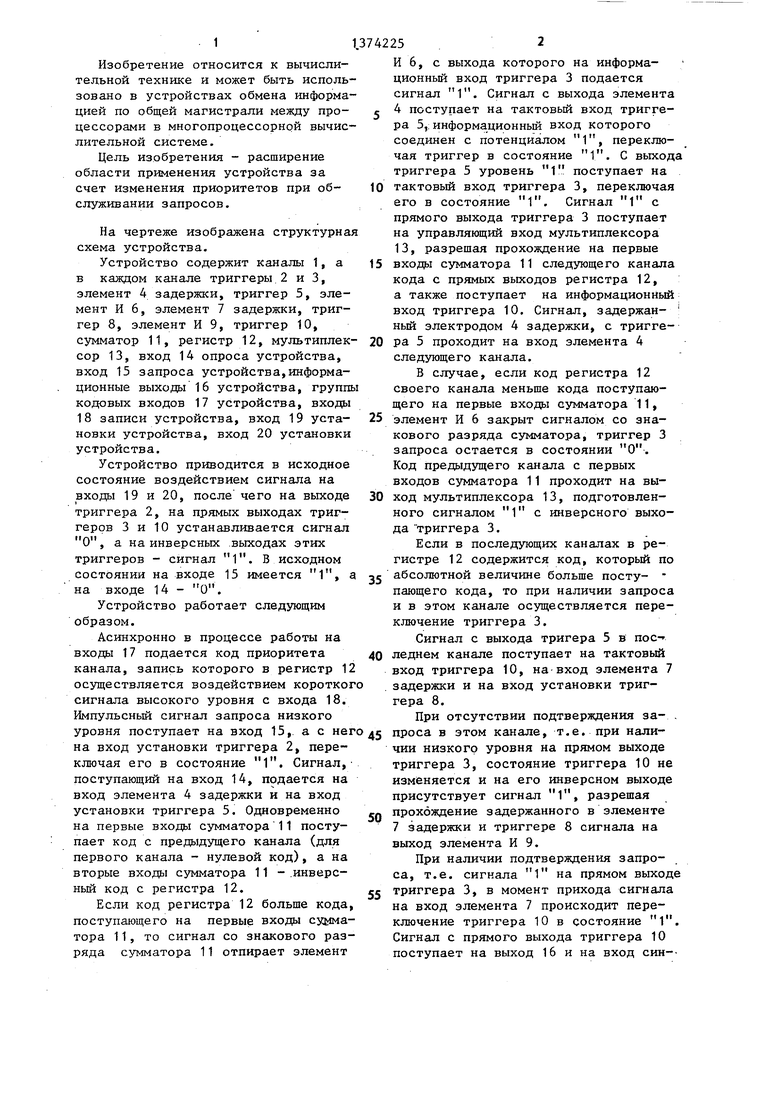

На чертеже изображена структурная схема устройства.

Устройство содержит каналы 1, а в каждом канале триггеры 2 и 3, элемент 4 задержки, триггер 5, элемент И 6, элемент 7 задержки, триггер 8, элемент И 9, триггер 10, сумматор 11, регистр 12, мультиплексор 13, вход 14 опроса устройства, вход 15 запроса устройства,информационные выходы 16 устройства, группы кодовых входов 17 устройства, входы 18 записи устройства, вход 19 установки устройства, вход 20 установки устройства.

Устройство приводится в исходное состояние воздействием сигнала на входы 19 и 20, после чего на выходе триггера 2, на прямых выходах триггеров 3 и 10 устанавливается сигнал О, а на инверсных выходах этих триггеров - сигнал 1, В исходном состоянии на входе 15 имеется 1, а на входе 14 - О.

Устройство работает следующим образом.

Асинхронно в процессе работы на входы 17 подается код приоритета канала, запись которого в регистр 12 осуществляется воздействием коротког сигнала высокого уровня с входа 18, Импульсный сигнал запроса низкого уровня поступает на вход 15,. а с нег на вход установки триггера 2, переключая его в состояние 1. Сигнал,- поступающий на вход 14, подается на вход элемента 4 задержки и на вход установки триггера 5, Одновременно на первые входы сумматора 11 поступает код с предыдущего канала (для первого канала - нулевой код), а на вторые входы сумматора 11 - .инверсный код с регистра 12,

Если код регистра 12 больше кода, поступающего на первые входы cytfMa- тора 11, то сигнал со знакового разряда сумматора 11 отпирает элемент

5

0

5

0

5

д

И 6, с выхода которого на информа- ционньй вход триггера 3 подается сигнал 1, Сигнал с выхода элемента с 4 поступает на тактовый вход триггера 5,: информационньш вход которого соединен с потенциалом 1, переключая триггер в состояние 1, С выхода триггера 5 уровень 1 поступает на 0 тактовый вход триггера 3, переключая его в состояние 1. Сигнал 1 с прямого выхода триггера 3 поступает на управляющий вход мультиплексора 13, разрешая прохождение на первые входы сумматора 11 следующего канала кода с прямых выходов регистра 12, а также поступает на информационный вход триггера 10. Сигнал, задержан- ный электродом 4 задержки, с триггера 5 проходит на вход элемента 4 следующего канала.

В случае, если код регистра 12 своего канала меньше кода поступающего на первые входы сумматора 11, элемент И 6 закрыт сигналом со знакового разряда сумматора, триггер 3 запроса остается в состоянии О. Код предыдущего канала с первых входов сумматора 11 проходит на выход мультиплексора 13, подготовленного сигналом 1 с инверсного выхода триггера 3.

Если в последующих каналах в регистре 12 содержится код, который по абсолютной величине больше посту- пающего кода, то при наличии запроса и в этом канале осуществляется переключение триггера 3.

Сигнал с выхода тригера 5 в пос- 0 леднем канале поступает на тактовый вход триггера 10, на вход элемента 7 задержки и на вход установки триггера 8,

При отсутствии подтверждения за- , проса в этом канале, т,е, при наличии низкого уровня на прямом выходе триггера 3, состояние триггера 10 не

изменяется и на его инверсном выходе присутствует сигнал 1, разрешая прохождение задержанного в элементе 7 задержки и триггере 8 сигнала на выход элемента И 9,

При наличии подтверждения запроса, т,е, сигнала 1 на прямом выходе триггера 3, в момент прихода сигнала на вход элемента 7 происходит переключение триггера 10 в состояние 1, Сигнал с прямого выхода триггера 10 поступает на выход 16 и на вход син-хронизации триггера 3, информационный вход которого подключен к потенциалу О, переключая триггер 2 в исходное состояние. Сигнал О с инверсного выхода триггера 10 в этом случае блокирует прохождение сигнала на выход элемента И 9.

Таким образом, сигнал с входа 14 при его прохождении от канала к ка- налу подтверждает запрос только в те каналах, приоритет которых выше благодаря тому, что код в регистре 12 превышает по величине код предыдущих каналов. Сигнал с выхода элемент И 9 представляет разрешение каналу с максимальным кодом среди каналов, имеющих запрос.

После переключения триггера 2 в исходное состояние канал готов к записи следующего сигнала запроса. Установка триггеров 3 и 10 в исходное состояние производится (ачей сигнала низкого уровня на вход 20 от устройства, получившего сигнал раз- решения, через интервал времени, определенный принятьм для данной системы интерфейсом.

Формула изобретения

Многоканальное устройст.во приоритета, содержащее каналы, каждый из которых содержит три триггера, первый элемент задержки, первый элемент И, причем в каждом канале вход установки в О первого триггера соеди г

О

нен с первым входом установки в О устройства, вход сброса второго триггера соединен с вторым входом уста- новки в О устройства, вход опроса соединен с входом сброса третьего триггера первого канала и через первый элемент задержки первого канала с тактовым входом третьего триггера первого канала, выход второго триггера каждого канала является соответствующим информационным выходом устройства, каждый запросный вход /стройства соединен с входом установки в 1 первого триггера одноименного канала, информационный вход первого триггера каждого канала соединен с входом логического нуля устройства, информационные входы второго и третьего триггеров каналов соединены с входом логической единицы устройства, прямой выход второго триггера каждого канала соединен с тактовым входом

о 5

0 5

0

5

„

5

0

5

первого триггера своего канала, о т- личающееся тем, что, с целью расширения области применения устройства за счет изменения приоритетов при обслуживании запросов, в каждый канал введены регистр, сумматор, мультиплексор, второй элемент задержки, второй элемент И, четвертый и пятый триггеры, причем первый вход сумматора в каждом канале соединен с первым информационным входом мультиплексора своего канала, 1второй вход сумматора соединен с инверсньт выходом регистра своего канала, прямой выход которого соединен с вторым информационным входом мультиплексора своего канала; первый вход сумматора первого канала соединен с входом логического нуля устройства, тактовый вход регистра каждого канала соединен с соответствующим входом записи устройства3 выход мультиплексора каждо- го канала соединен с первым входом сум- матора cлeд.oщeгo канала, выход знакового разряда сумматора соединен с первым входом первого элемента И своего канала, выход которого соединен с информационным входом четвертого триггера своего канала, инверсный выход которого соединен с первым управляющим входом мультиплексора своего канала прямой выход четвер- того триггера соединен с информационным входом второго триггера и с вторьм управляющим входом мультиплек сора своего каналад инверсный выход второго триггера соединен с первым входом второго элемента И, вход второго элемента задержки соединен с входом сброса пятого триггера, с тактовым входом второго триггера и с выходом второго элемента И предыдущего канала5 выход второго элемента задержки соединен с тактовым входом пятого тииггера9 выход которого соединен с вторым входом второго элемента И своего канала, вход второго элемента задержки в последнем канале соединен с выходом третьего триггера данного канала, вход сброса четвертого триггера соединен с вторым входом установки устройства; выход первого триггера соединен с вторым входом первого элемента И, информационный вход пятого триггера соединен с входом логической единицы устройства, выход третьего триггера соединен с тактовым входом четвертого триггера

.513742256

своего канала и с входом первого ства соединена с группой информаци- элемента задержки следующего канала, онных входов регистра одноименного каждая группа кодовых входов устрой- канала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для подключения абонентов к двум общим магистралям | 1984 |

|

SU1203532A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 2015 |

|

RU2589317C1 |

| Устройство для обслуживания запросов | 1988 |

|

SU1571588A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ПОДКЛЮЧЕНИЯ АБОНЕНТОВ К ОБЩЕЙ МАГИСТРАЛИ | 1991 |

|

RU2023293C1 |

| Устройство для формирования очереди запросов | 1985 |

|

SU1280630A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Устройство для передачи информации | 1989 |

|

SU1700571A1 |

| ИМИТАТОР ШУМОПОДОБНЫХ СИГНАЛОВ | 1990 |

|

RU2022448C1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1988 |

|

SU1594551A1 |

| Устройство для сопряжения каналов ЭВМ с периферийными устройствами | 1990 |

|

SU1732348A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах обмена информацией по общей магистрали между процессорами в многопроцессорной вычислительной системе. Цель изобретения - расширение области применения за счет изменения приоритетов при обслуживании запросов. Устройство содержит каналы, каждый из которых включает пять триггеров 2, 3, 5, 8, 10, два элемента задержки 4, 7, два элемента И 6, 9, сумматор 11, регистр 12, мультиплексор 13. В устройстве приоритет каналов при обслуживании запросов изменяется в зависимости от значения кода в заданных регистрах каналов в текущий момент времени. 1 ил.S

Авторы

Даты

1988-02-15—Публикация

1986-06-05—Подача