Изобретение относится к устройствам, применяемым в вычислительной технике, и средствам передачи данных, в частности к устройствам, обеспечивающим сопряжение связных вычислительных устройств, кодексов, средств автоматизированного проектирования с передающей средой (каналом, системой каналов), например в локальной вычислительной сети (ЛВС).

Целью изобретения является повышение быстродействия устройства.

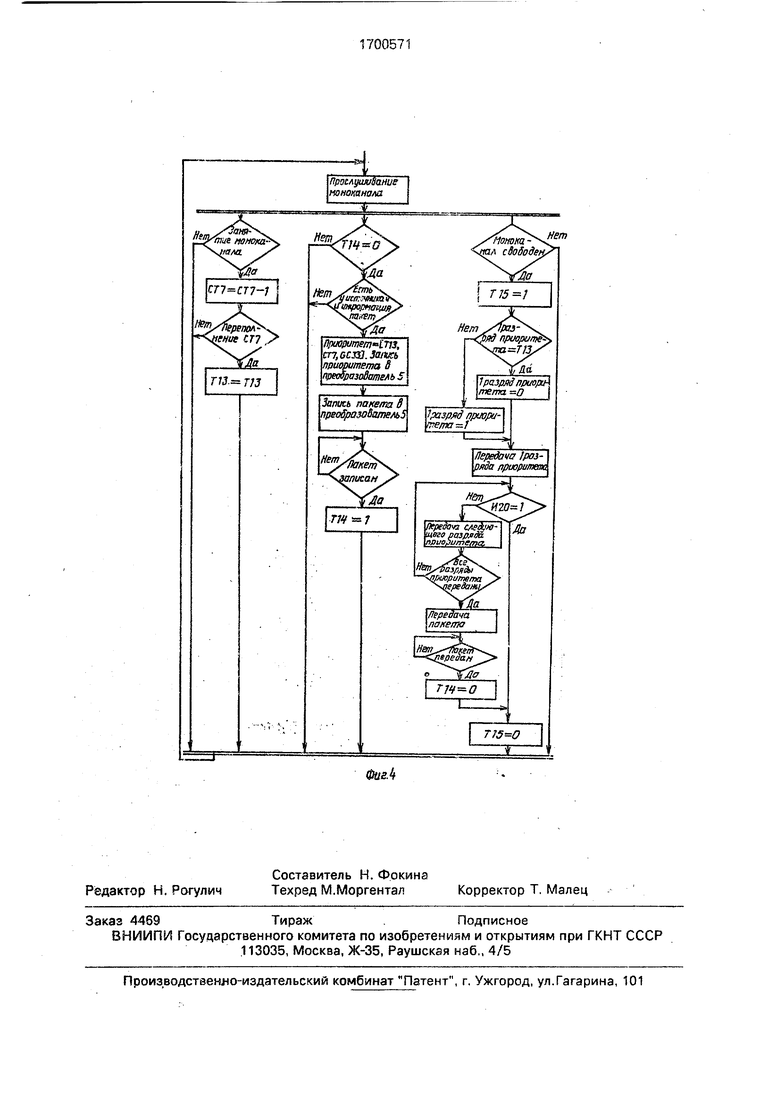

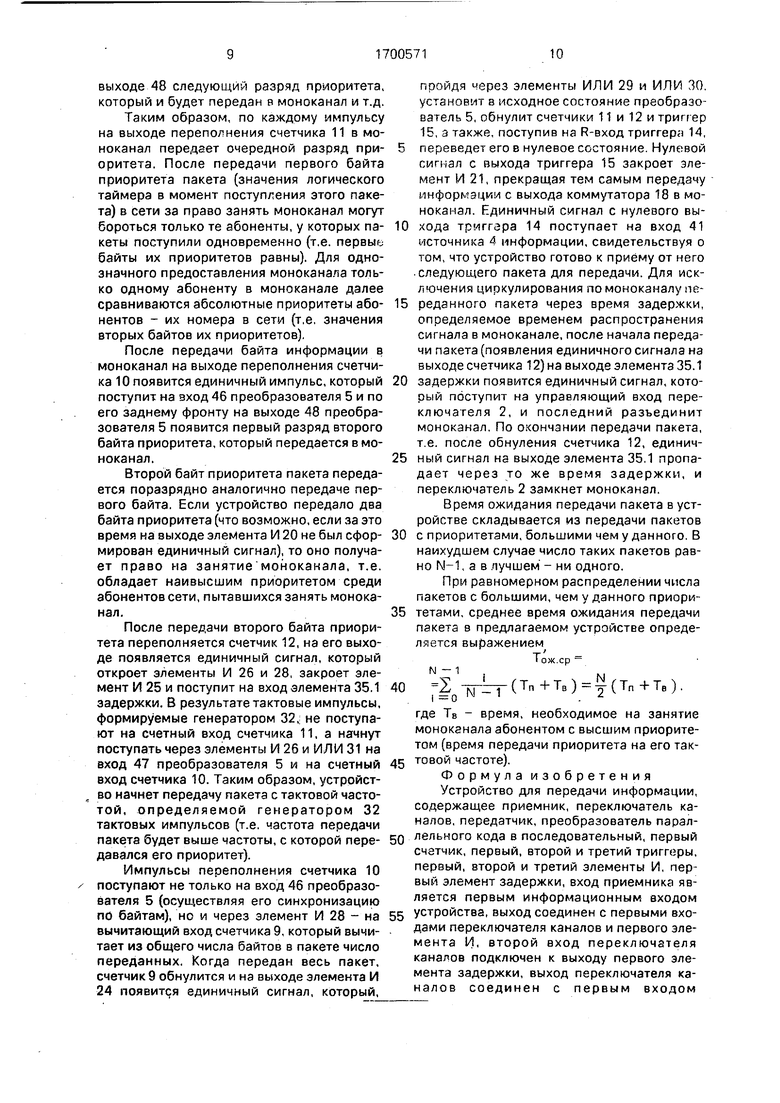

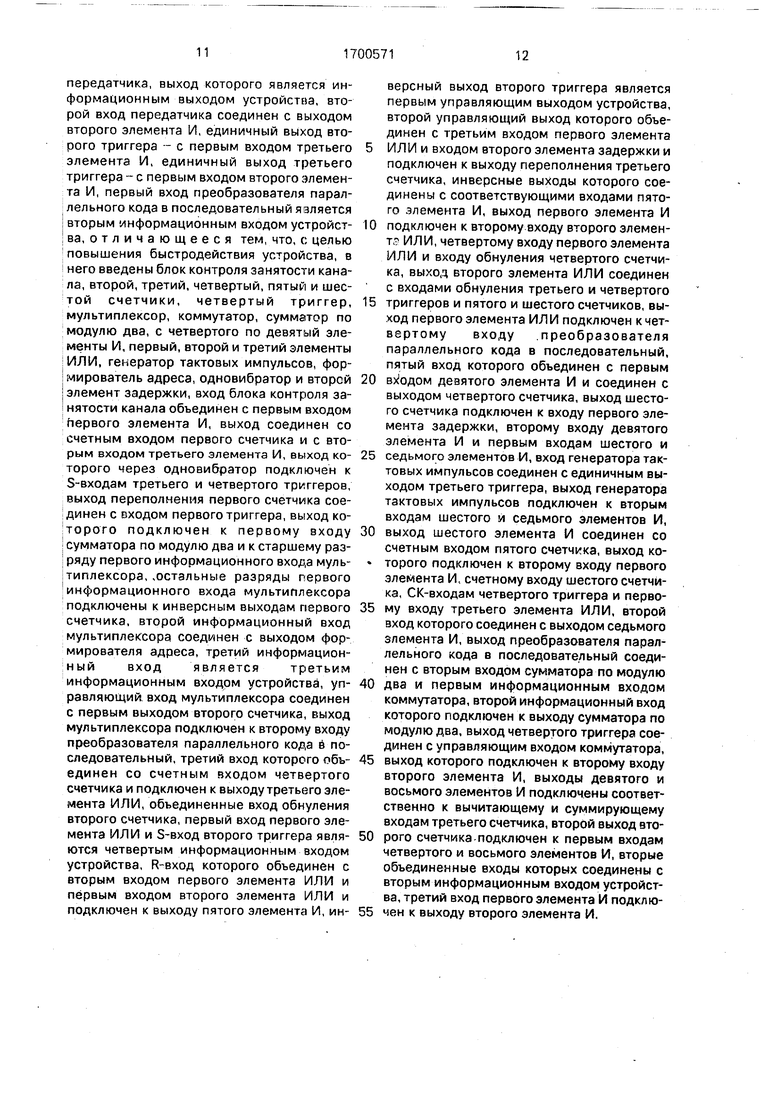

На фмг.1 приведена функциональная схема устройства; на фиг.2 - преобразователь параллельного кода в последовательный, на фиг.З - блок контроля занятости канала; на фиг.4 - фрагмент алгоритма функционирования устоойства.

Устройство для передачи информации содержит приемник , переключатель 2 каналов, передатчик 3, источник 4 информации, преобразователь 5 параллельного кода в последовательный, блок б контроля занятости канала, первый 7 - шестой 12 счетчики, первый 13 - четвертый 16 триггеры, мультиплексор 17, коммутатор 18, сумматор 19 по модулю два, первый 20 - девятый 28 элементы И, первый 29 - третий 31 элемек ты ИЛИ, генератор 32 тактовых импульсов, формирователь 33 адресз, одновибратор34, первый 35 1 и второй 35.2 элементы задержки, вход 36 приемника л выход 37 передатчика, первый 38 - третий 40 выходы и пеооьш 41 и второй 42 входы источника ин- формац первый - пять й 47 входы и выход 48 преобразователя параллельного

4 О О

сл XI

кода в последовательный, вход 49 и выход

50блока 6 контроля занятости моноканала.

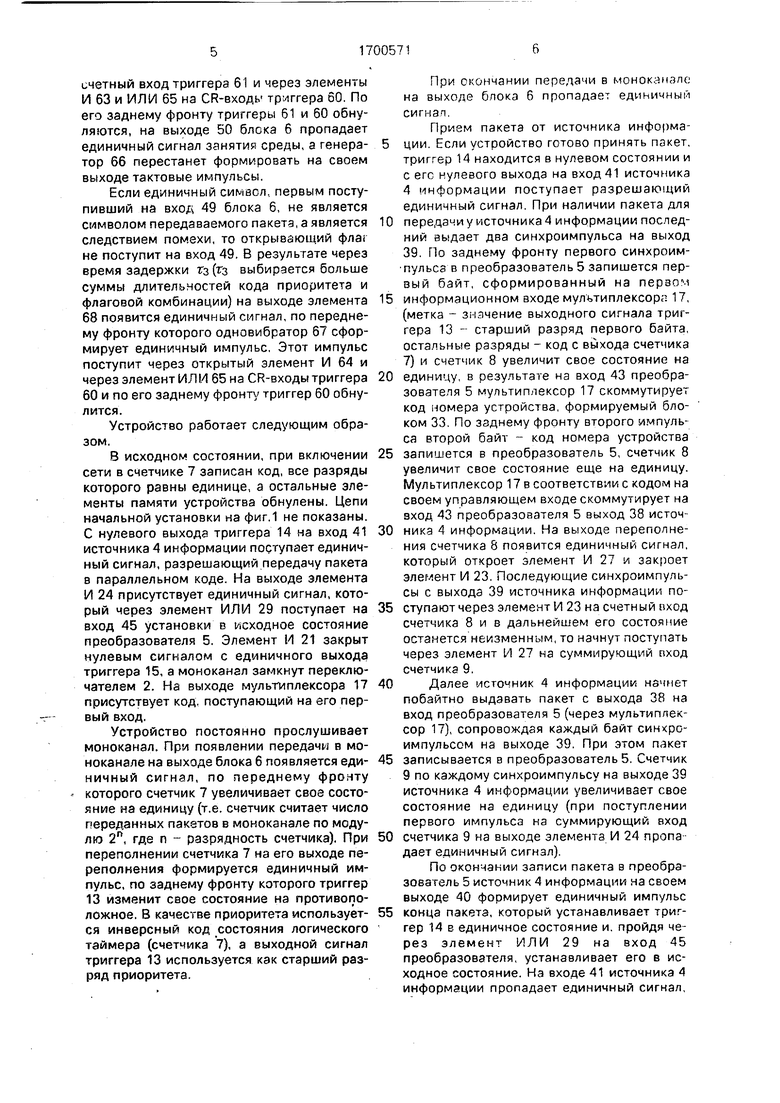

Преобразователь 5 параллельного кода в последовательный (фиг.2) содержит блок

51памяти, регистр 52 сдвига, счетчик 53, элемент И 54, первый 55 и второй 56 элементы ИЛИ одновибратор 57.1 и 57.2 и элемент 58 задержки.

Преобразователь 5 работает следующим образом. При появлении первого байта на входе 43 и сопровождающего его синхроимпульса на входе 44 байт записывается гю нулевому адресу в блок 51, По заднему фронту синхроимпульса, поступившего на вход 44 преобразователя 5, счетчмк 53 увеличит свое состояние на единицу, и следующий байт с входа 43 запишется в блок 5 :, в ячейку с первым адресом по синхроимпупь- су, поступившему на вход 44, а счегчик 53 увеличит свое состояние ча единицу (сформирует очередной адрес) и т.д. Таким образом, осуществляется запись пакета в параллельном коде.

При поступлении единичного сигнала на вход 45 одновибратор 57.1 по его переднему фронту сформирует единичный импульс, по которому счетчик 53 обнулится и с выхода блока 51 на информационный вход регистра 52 поступает первый байт пакета, хранящийся в блоке 51 по нулевому адресу. Через время задержки, определяемое временем срабатывания описанной иепочки элементов, импульс, сформированный од- новибратором 57.1, пройдет через элемент 58 задержки и элемент ИЛИ 56 на вход синхронизации записи регистра 52 и по его заднему фронту в регистр 52 запишется первый байт. Так осуадествляется установка преобразователя 5 в исходное состояние.

Для выдачи пакета в последовательном коде на вход 47 преобразователя подаются тактовые импульсы. Этиимпульсч проходят через открытый элемент И 54 на вход синхронизации сдвига регистра 52. В оезультэ- те, по заднему фронту каждого такого импульса на выходе 48 преобразователя 5 появляется очередной бит. По заднему фронту седьмого импульса, поступившего на вход 47 преобразователя 5, на входе 46 появляется единичный сигнал, который поступает на вход одновибратора 572 через элемент ИЛИ 56 на вход синхронизации записи регистра 52 и закрывает элемент И 54. Одновибратор 57.2 по переднему фронту, поступившего на его вход импульса формирует единичный импульс, который.через элемент ИЛИ 55 поступает на счетный вход счетчика 53. По заднему фронту этого импульса счетчик 53 увеличивает свое состояние на единицу, формируя тем самым

адрес ячейки блока 51, в котором хранится очередной байт пакета. В соответствии с этим адресом на информационный вход регистра 52 с выхода блока 51 считывается

очередной байт пакета.

Следующий (восьмой) импульс, поступивший на вход 47 преобразователя 5, не пройдет через элемент И 54 на вход синхронизации сдвига регистра 52, но по его за0 днему фронту формируется задний фронт единичного сигнала на входа 47, по которому в регистр 52 запишется очередной байт пакета и его первый бит поступит на выход 48 преобразователя 5, Далее работа пре5 образователя 5 при выдаче пакета повторяется.

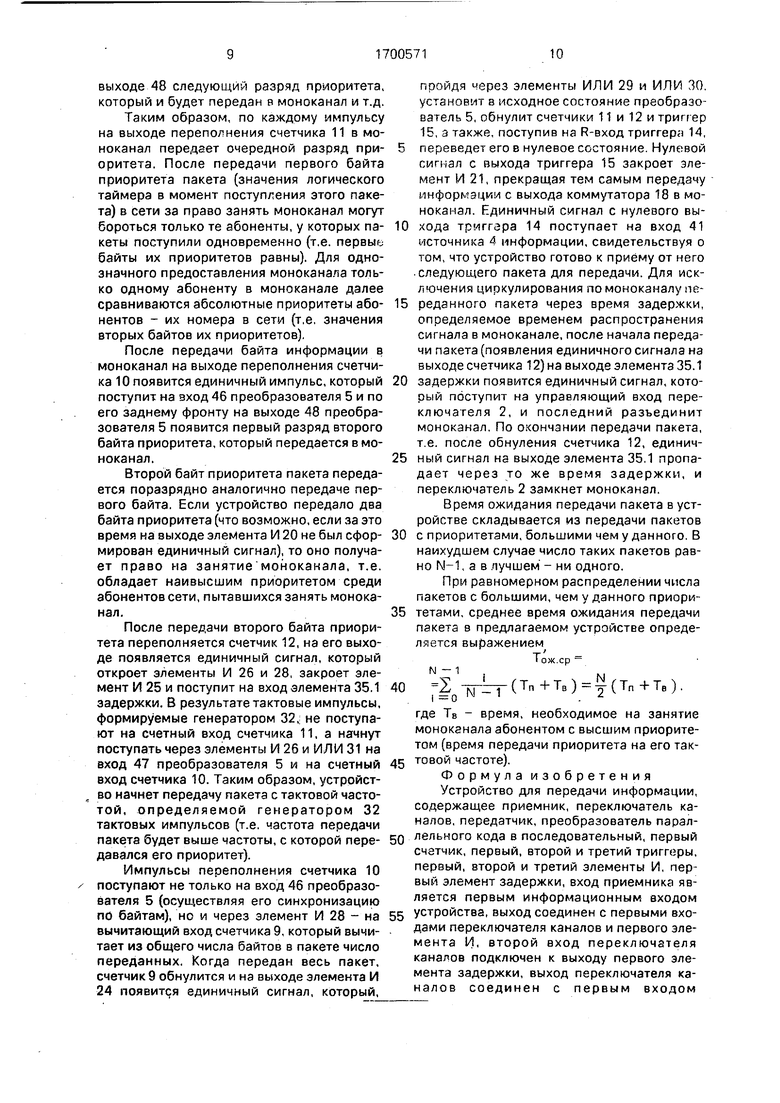

Блок 6 занятости канала (фиг.З) содержит регистр 59 сдвига, первый 60 и второй 61 триггеры, дешифратор 62, первый 63 и

0 второй 64 элементы И, элемент ИЛИ 65, генератор 66 тактовых импульсов, одновибратор 67 и элемент 68 задержки.

Блок б работает следующим образом. Первый единичный символ, поступивший с

5 выхода приемника 1 на вход 49 блока б, поступит на информационный вход регистра 59 сдвига и на S-вход триггера 60. По его переднему фронту триггер 60 перейдет в единичное состояние, единичный сигнал с

0 его выхода поступит на вход генератора 66 импульсов, на вход элемента 68 задержки и на выход 50 блока 6, сигнализируя о занятии среды передачи. Генератор 66 формирует на своем выходе тактовые импульсы, кото5 рые поступают на вход синхронизации регистра 59 сдвига, и последний записывает в последовательном коде информацию, поступающую на вход 49 блока 6 с выхода приемника 1,

0 Передача каждого пакета начинается с приоритета, а затем передается комбинация открывающего флага и т.д. Заканчивается пакет закрывающим флагом. 0 После поступления на вход 49 блока 6

5 открывающего флага, т.е. в регистре 59 сдвига хранится кодовая комбинация флага (разрядность регистра 59 определяется разрядностью флаговой комбинации), дешифратор 62 сформирует на своем выходе единичный сигнал. При поступлении на вход

0 49 блока 6 следующего символа на выходе дешифоатора 62 сформируется задний фронт единичного сигнала, по которому риггер 61 перейдет в-единичное состояние. Единичный сигнал с выхода триггера 61 от5 кроет элемент И 63 и закроет элемент И 64. При поступлении на вход 9 блока б закрывающего флага, следующего в конце пакета, на выходе дешифратора 62 сформирован единичный импульс, который поступит на

счетный вход триггера 61 и через элементы И 63 и ИЛИ 65 на CR-входь1 триггера 60. По его заднему фронту триггеры 61 и 60 обнуляются, на выходе 50 блока 6 пропадает единичный сигнал занятия среды, а генератор 66 перестанет формировать на своем выходе тактовые импульсы.

Если единичный символ, первым поступивший на вход 49 блока 6, не является символом передаваемого пакета, а является следствием помехи, то открывающий флаг не поступит на вход 49. В результате через время задержки Гз(гз выбирается больше суммы длительностей кода приоритета и флаговой комбинации) на выходе элемента 68 появится единичный сигнал, по переднему фронту которого одновибратор 67 сформирует единичный импульс. Этот импульс поступит через открытый элемент И 64 и через элемент ИЛ И 65 на CR-входы триггера 60 и по его заднему фронту триггер 60 обну- лится.

Устройство работает следующим образом.

8 исходном состоянии, при включении сети в счетчике 7 записан код, все разряды которого равны единице, а остальные элементы памяти устройства обнулены. Цепи начальной установки на фиг.1 не показаны. С нулевого выхода триггера 14 на вход 41 источника 4 информации поступает единичный сигнал, разрешающий передачу пакета в параллельном коде. На выходе элемента И 24 присутствует единичный сигнал, который через элемент ИЛИ 29 поступает на вход 45 установки в исходное состояние преобразователя 5. Элемент И 21 закрыт нулевым сигналом с единичного выхода триггера 15, а моноканал замкнут переключателем 2. На выходе мультиплексора 17 присутствует код. поступающий на его первый вход.

Устройство постоянно прослушивает моноканал. При появлении передачи в моноканале на выходе блока 6 появляется единичный сигнал, по переднему фронту которого счетчик 7 увеличивает свое состояние на единицу (т.е. счетчик считает число переданных пакетов в моноканале по модулю 2П, где п - разрядность счетчика). При переполнении счетчика 7 на его выходе переполнения формируется единичный импульс, по заднему фронту которого триггер 13 изменит свое состояние на противоположное. В качестве приоритета используется инверсный код состояния логического таймера (счетчика 7), а выходной сигнал триггера 13 используется как старший разряд приоритета.

При скончании передачи в моноканале на выходе блока 6 пропадает единичный сигнап.

Прием пакета от источника информа- 5 ции. Если устройство готово принять пакет, триггер 14 находится в нулевом состоянии и с егс нулевого выхода на вход 41 источника 4 информации поступает разрешающий единичный сигнал. При наличии пакета для 10 передачи у источника 4 информации последний аыдает два синхроимпульса на выход 39. По заднему фронту первого синхроимпульса в преобразователь 5 запишется первый байт, сформированный на первом 5 информационном входе мультиплексора 17, (метка - значение выходного сигнала триггера 13 - старший разряд первого байта, остальные разряды - код с выхода счетчика 7) и счетчик 8 увеличит свое состояние на

0 единицу, в результате на вход 43 преобразователя 5 мультиплексор 17 скоммутирует код номера устройства, формируемый блоком 33. По заднему фронту второго импульса второй байт - код номера устройства

5 запишется в преобразователь 5, счетчик 8 увеличит свое состояние еще на единицу. Мультиплексор 17 в соответствии с кодом на своем управляющем входе скоммутирует на вход 43 преобразователя 5 выход 38 источ0 ника 4 информации. На выходе переполнения счетчика 8 появится единичный сигнал, который откроет элемент И 27 и закроет элемент И 23. Последующие синхроимпульсы с выхода 39 источника информации по5 ступают через элемент И 23 на счетный пход счетчика 8 и в дальнейшем его состояние останется неизменным, то начнут поступать через элемент И 27 на суммирующий пход счетчика 9.

0Далее источник 4 информации начнет

побайтно выдавать пакет с выхода 38 на вход преобразователя 5 (через мультиплексор 17), сопровождая каждый байт синхроимпульсом на выходе 39. При этом пакет

5 записывается в преобразователь 5. Счетчик 9 по каждому синхроимпульсу на выходе 39 источника 4 информации увеличивает свое состояние на единицу (при поступлении первого импульса на суммирующий вход

0 счетчика 9 на выходе элемента И 24 пропадает единичный сигнал).

По окончании записи пакета в преобразователь 5 источник 4 информации на своем выходе 40 формирует единичный импульс

5 конца пакета, который устанавливает триггер 14 в единичное состояние и. пройдя через элемент ИЛИ 29 на вход 45 преобразователя, устанавливает его в исходное состояние. На входе 41 источника 4 информации пропадает единичный сигнал,

а единичный сигнал с единичного выхода триггера 14 откроет элемент И 22. Код в счетчике 9 соответствует числу байтов в пакете.

Если размерность пакета, выдаваемого источником 4 информации, превышает максимально допустимую, произойдет переполнение счетчика 9, и на его выходе переполнения появится единичный сигнал. Этот сигнал поступит на вход 42 источника 4 информации, указывая . превышение размерности пакета, и через элемент ИЛИ 29 на вход 45 преобразователя 5 и установит его в исходное состояние. Через время задержки, определяемое длительностью срабатывания описанных цепей, сигнал, сформированный на выходе переполнения счетчика 9, через элемент 35.2 задержки поступит на вход сброса счетчика 9 и обнулит его.

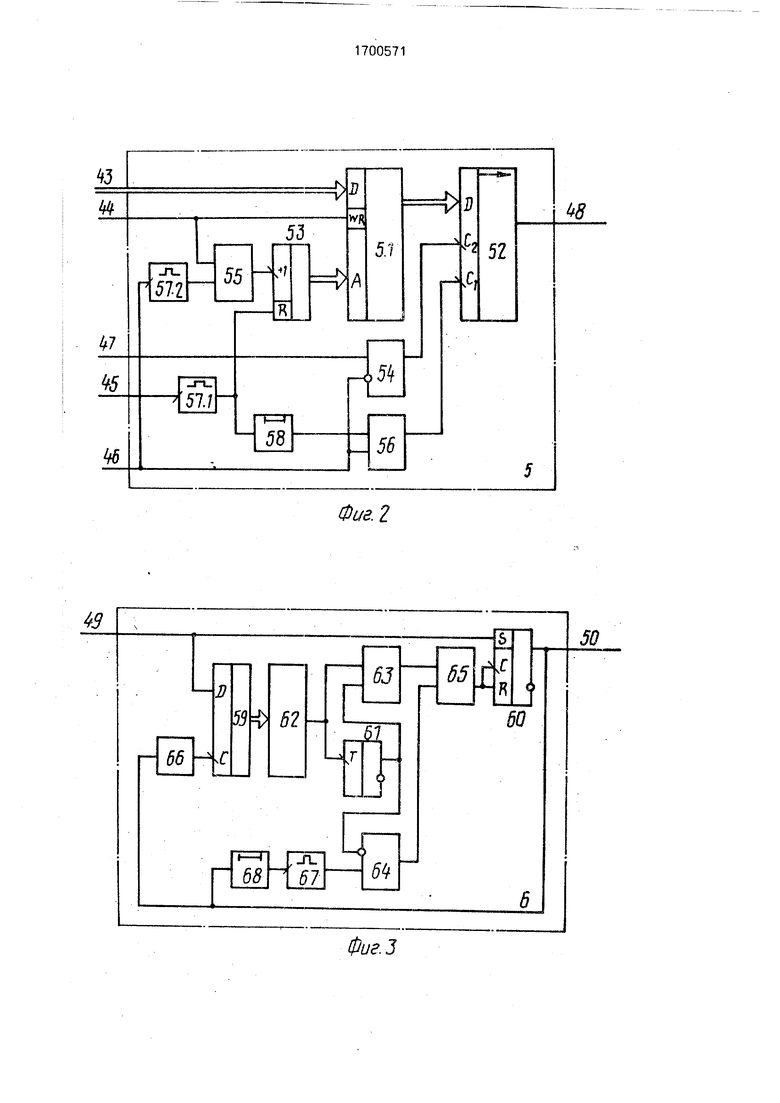

Занятие моноканала и передача пакета. Если в устройстве есть готовый пакет для Передачи (т.е. триггер 14 находится в единичном состоянии и элемент И 22 открыт), при освобождении моноканала (на выходе 50 блока 6 появится единица) на выходе элемента И 22 сформирован единичный сигнал, по переднему фронту которого одно- вибратор 34 сформирует единичный импульс. Единичный импульс с выхода од- новибратора 34 поступит на S-входы триггеров 15 и 16 и они перейдут в единичное состояние. Единичный сигнал с единичного выхода триггера 16 поступит на управляющий вход коммутатора 18 и он скоммутирует на свой выход сигнал с выхода сумматора 19 по модулю два. На входы сумматора 19 по модулю два поступает текущее значение выходного сигнала триггера 13 и первый бит заголовка пакета с выхода 48 преобразователя 5 (то же значение выходного сигнала триггера 13, но в момент записи пакета в преобразователь 5). Если значения сигналов, поступающих на входы сумматора 19 по модулю два, не равны, то на его выходе сформирован единичный сигнал, который использован в качестве первого разряда пакета. Это значит, что пакет записан в прошлом цикле счета счетчика 7 (логического таймера), а единичный первый разояд его приоритета дает ему преимущество над пакетами других абонентов сети, запись которых производилась в текущем иик/ie логического таймера. Таким образом, глобальное упорядочивание пакета в сети (общая очередь) не нарушено.

Единичный сигнал с единичного выхода триггера 5 откроет члемент И 21, первый разряд приоритета поступит на передатчик 3 и будет передан в MOHOIзнал Одновременно единичный сигнал с единичного выхода триггера 15 поступит на вход генератора 32 тактовых импульсов и последний начнет формирование на своем выходе последовательности тактовых импульсов, которые поступают через открытый элемент И 25 на счетный вход счетчика 11. Последний считает их количество. Пои переполнении счетчика 11 на его выходе сформируется

0 единичный импульс. Этот импульс поступит на третий вход элемента И 20, разрешая его работу, на двз других входа которого поступают сигнал с выхода приемника 1 (сигнал из канала) и сигнал с выхода элемента И 21

5 (значение разряда приоритета, передаваемого в в канал). Если значение сигнала в моноканале больше значения передаваемого разряда приоритета (т.е. один из абонентов, пытающихся занять моноканал, имеет

0 больший приоритет), на выходе элемента И 20 сформируется единичный сигнал, который поступит на вход сброса счетчика 10, через элемент ИЛИ 29 на вход 45 установки исходного состояния преобразователя 5 и

5 через элемент ИЛИ 30 на R-входы счетчиков 11 и 12 и триггеров 15 и 16. В результате счетчики 10-12, триггеры 15 и 16 обнуляются, а преобразователь 5 установится в исходное состояние. Таким образом,

0 устройство прекратит попытку занять моноканал и будет ожидать следующего его освобождения.

Если на выходе элемента И 20 не сформировался единичный сигнал, по заднему

5 фронту импульса с выхода счетчика 11 счетчики 10 и 12 увеличат свое состояние «а единицу, триггер 16 обнулится, а на выходе 48 преобразователя 5 появится следующий разряд приоритета. Нулевой сигнал, сфор0 мированный на выходе триггера 16, поступит на управляющий вход коммутатор& 18, и он скоммутирует на свой выход второй разряд приоритета с выхода 48 преобразо- 5, т.е. в моноканал передается следу5 ющий разряд приоритета.

По следующему импульсу, сформированному на выходе переполнения счетчика 11, произойдет сравнение передаваемого разряда с сигналом в моноканале. При отри0 цательном результате сравнения (сформирован единичный сигнал на выходе эпемента И 20) устройство прекратит попытку занять моноканал и ожидает следующего его освобождения. При положительном ре5 зультате сравнения по заднему фронту им- пульса, сформированному на выходе переполнения счетчика 11, счетчики 10 и 12 увеличат свое состояние на единицу, триггер 16 подтвердит свое нулевое состояние, а преобразователь 5 сформирует на своем

выходе 48 следующий разряд приоритета, который и будет передан в моноканал и т.д.

Таким образом, по каждому импульсу на выходе переполнения счетчика 11 в моноканал передает очередной разряд приоритета. После передачи первого байта приоритета пакета (значения логического таймера в момент поступления этого пакета) в сети за право занять моноканал могут бороться только те абоненты, у которых пакеты поступили одновременно (т.е. первые байты их приоритетов равны). Для однозначного предоставления моноканала только одному абоненту в моноканале далее сравниваются абсолютные приоритеты абонентов - их номера в сети (т.е. значения вторых байтов их приоритетов).

После передачи байта информации в моноканал на выходе переполнения счетчика 10 появится единичный импульс, который поступит на вход 46 преобразователя 5 и по его заднему фронту на выходе 48 преобразователя 5 появится первый разряд второго байта приоритета, который передается в моноканал.

Второй байт приоритета пакета передается поразрядно аналогично передаче первого байта. Если устройство передало два байта приоритета (что возможно, если за это время на выходе элемента И 20 не был сформирован единичный сигнал), то оно получает право на занятие моноканала, т.е. обладает наивысшим приоритетом среди абонентов сети, пытавшихся занять моноканал.

После передачи второго байта приоритета переполняется счетчик 12, на его выходе появляется единичный сигнал, который откроет элементы И 26 и 28, закроет элемент И 25 и поступит на вход элемента 35.1 задержки. В результате тактовые импульсы, формируемые генератором 32, не поступают на счетный вход счетчика 11, а начнут поступать через элементы И 26 и ИЛИ 31 на вход 47 преобразователя 5 и на счетный вход счетчика 10. Таким образом, устройство начнет передачу пакета с тактовой частотой, определяемой генератором 32 тактовых импульсов (т.е. астота передачи пакета будет выше частоты, с которой передавался его приоритет).

Импульсы переполнения счетчика 10 поступают не только на вход 46 преобразователя 5 (осуществляя его синхронизацию по байтам), но и через элемент И 28 - на вычитающий вход счетчика 9, который вычитает из общего числа байтов в пакете число переданных. Когда передан весь пакет, счетчик 9 обнулится и на выходе элемента И 24 появится единичный сигнал, который,

пройдя через элементы ИЛИ 29 и ИЛИ 30 установит в исходное состояние преобразователь 5, обнулит счетчики 11 и 12 и триггер 15, з также, поступив на R-вход триггера 14, 5 переведет его в нулевое состояние Нулевой сигнал с выхода триггера 15 закроет элемент И 21, прекращая тем самым передачу информации с выхода коммутатора 18 в моноканал. Единичный сигнал с нулевого вы0 хода триггера 14 поступает на вход 41 источника 4 информации, свидетельствуя о том, что устройство готово к приему от него следующего пакета для передачи. Для исключения циркулирования по моноканалу пг5 реданного пакета через время задержки, определяемое временем распространения сигнала в моноканале, после начала передачи пакета (появления единичного сигнала на выходе счетчика 12) на выходе элемента 35.1

0 задержки появится единичный сигнал, который поступит на управляющий вход переключателя 2, и последний разъединит моноканал. По окончании передачи пакета, те. после обнуления счетчика 12, единич5 ный сигнал на выходе элемента 35.1 пропадает через то же время задержки, и переключатель 2 замкнет моноканал.

Время ожидания передачи пакета в устройстве складывается из передачи пакетов

0 с приоритетами, большими чем у данного В наихудшем случае число таких пакетов равно N-1, а в пучшем - ни одного.

При равномерном распределении числа пакетов с большими, чем у данного приори5 тетами, среднее время ожидания передачи пакета в предлагаемом устройстве определяется выражением

Тож ср

0

N -1

-.2, 1 ( Тп + Тв ) - 2 ( Тп + Тв ) .

I -О

где Тв - время, необходимое на занятие моноканала абонентом с высшим приоритетом (время передачи приоритета на его тактовой частоте).

Формула изобретения Устройство для передачи информации, содержащее приемник, переключатель каналов, передатчик, преобразователь параллельного кода в последовательный, первый счатчик, первый, второй и третий триггеры, первый, второй и третий элементы И, первый элемент задержки, вход приемника является первым информационным входом

устройства, выход соединен с первыми входами переключателя каналов и первого элемента И, второй вход переключателя каналов подключен к выходу первого элемента задержки, выход переключателя каналов соединен с первым входом

передатчика, выход которого является информационным выходом устройства, второй вход передатчика соединен с выходом второго элемента И, единичный выход второго триггера - с первым входом третьего элемента И, единичный выход третьего триггера - с первым входом второго элемента И, первый вход преобразователя параллельного кода в последовательный является вторым информационным входом устройст- ва, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены блок контроля занятости канала, второй, третий, четвертый, пятый и шестой счетчики, четвертый триггер, мультиплексор, коммутатор, сумматор по модулю два, с четвертого по девятый элементы И, первый, второй и третий элементы ИЛИ, генератор тактовых импульсов, формирователь адреса, одновибратор и второй элемент задержки, вход блока контроля занятости канала объединен с первым входом hepeoro элемента И, выход соединен со счетным входом первого счетчика и с вторым входом третьего элемента И, выход которого через одновибратор подключен к S-входам третьего и четвертого триггеров, выход переполнения первого счетчика соединен с входом первого триггера, выход которого подключен к первому входу сумматора по модулю два и к старшему разряду первого информационного входа мультиплексора, ,остальные разряды первого информационного входа мультиплексора подключены к инверсным выходам первого счетчика, второй информационный вход мультиплексора соединен с выходом формирователя адреса, третий информационный вход является третьим информационным входом устройства, управляющий вход мультиплексора соединен с первым выходом второго счетчика, выход мультиплексора подключен к второму входу преобразователя параллельного кода 6 последовательный, третий вход которого объединен со счетным входом четвертого счетчика и подключен к выходу третьего элемента ИЛИ, объединенные вход обнуления второго счетчика, первый вход первого элемента ИЛИ и S-вход второго триггера являются четвертым информационным входом устройства, R-вход которого объединен с вторым входом первого элемента ИЛИ и первым входом второго элемента ИЛИ и подключен к выходу пятого элемента И, инверсный выход второго триггера является первым управляющим выходом устройства, второй управляющий выход которого объединен с третьим входом первого элемента

ИЛИ и входом второго элемента задержки и подключен к выходу переполнения третьего счетчика, инверсные выходы которого соединены с соответствующими входами пятого элемента И, выход первого элемента И

подключен к второму входу второго элемен- тг ИЛИ, четвертому входу первого элемента ИЛИ и входу обнуления четвертого счетчика, выход второго элемента ИЛИ соединен с входами обнуления третьего и четвертого

триггеров и пятого и шестого счетчиков, выход первого элемента ИЛИ подключен к четвертому входу преобразователя параллельного кода в последовательный, пятый вход которого объединен с первым

вх одом девятого элемента И и соединен с выходом четвертого счетчика, выход шестого счетчика подключен к входу первого элемента задержки, второму входу девятого элемента И и первым входам шестого и

седьмого элементов И, вход генератора тактовых импульсов соединен с единичным выходом третьего триггера, выход генератора тактовых импульсов подключен к вторым входам шестого и седьмого элементов И,

выход шестого элемента И соединен со счетным входом пятого счетчика, выход ко- торого подключен к второму входу первого элемента И, счетному входу шестого счетчика, СК-входам четвертого триггера и первому входу третьего элемента ИЛИ, второй вход которого соединен с выходом седьмого элемента И, выход преобразователя параллельного кода в последовательный соединен с вторым входом сумматора по модулю

два и первым информационным входом коммутатора, второй информационный вход которого подключен к выходу сумматора по модулю два, выход четвертого триггера соединен с управляющим входом коммутатора,

выход которого подключен к второму входу второго элемента И, выходы девятого и восьмого элементов И подключены соответственно к вычитающему и суммирующему входам третьего счетчика, второй выход второго счетчика подключен к первым входам четвертого и восьмого элементов И, вторые объединенные входы которых соединены с вторым информационным входом устройства, третий вход первого элемента И подключен к выходу второго элемента И.

Фиг.1

с

53

55

О

к

ц

Я

4

5.7

5Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи информации в кольцевом канале связи | 1989 |

|

SU1691864A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Станция локальной вычислительной сети | 1990 |

|

SU1805474A1 |

| Устройство для приема и передачи данных | 1988 |

|

SU1596478A1 |

| Устройство для передачи дискретной информации в кольцевом канале связи | 1989 |

|

SU1795497A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Устройство для преобразования телеграфного кода в видеокод | 1985 |

|

SU1314461A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для сопряжения абонента с каналом связи | 1987 |

|

SU1499358A1 |

| Устройство для передачи информации | 1988 |

|

SU1509970A1 |

Изобретение относится к вычислительной технике и средствам передачи данных, в частности к средствам, обеспечивающим сопряжение вычислительных устройств с передающей средой, например, в локальной вычислительной сети. Цель изобретения - повышение быстродействия устройс-за. Устройство содержит приемник, переключатель каналов, передатчик, источник информации, преобразователь параллельного кода в последовательный, блок контроля занятости канала, счетчики, триггеры, мультиплексор, коммутатор, сумматор по модулю два, элементы И, элементы ИЛИ, генератор тактовых импульсов, формирователь адреса, одновибратор, элементы задержки. Изобретение обеспечивает бесконфликтную передачу пакетов и организацию общей очереди пакетов в сети за счет предоставления права на занятие моноканала устройству, имеющему пакет для передачи с наивысшим приоритетом, причем в качестве приоритета пакета используется значение логического таймера. Таким образов, устройство обеспечивает предельное время ожидания и исключает возможность блокировки, а также создает и поддерживает распределенную очередь пакетов. 4 ил.

#

tt

58

0аа2

feJ

Нет

| Устройство для передачи информации в кольцевом канале связи | 1982 |

|

SU1043715A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1991-12-23—Публикация

1989-11-14—Подача