Изобретение относится к цифровой технике и может быть использовано дл защиты информации в запоминающих устройствах при отключении питания.

Цель изобретения - повьшение надежности устройства.

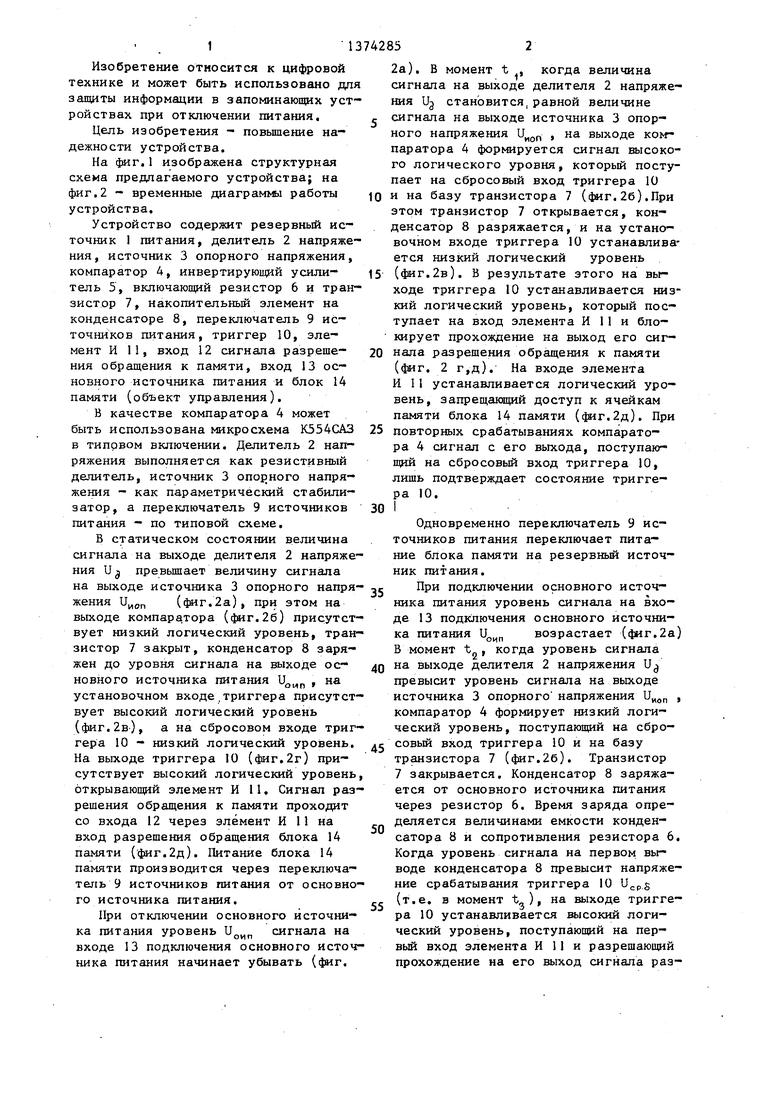

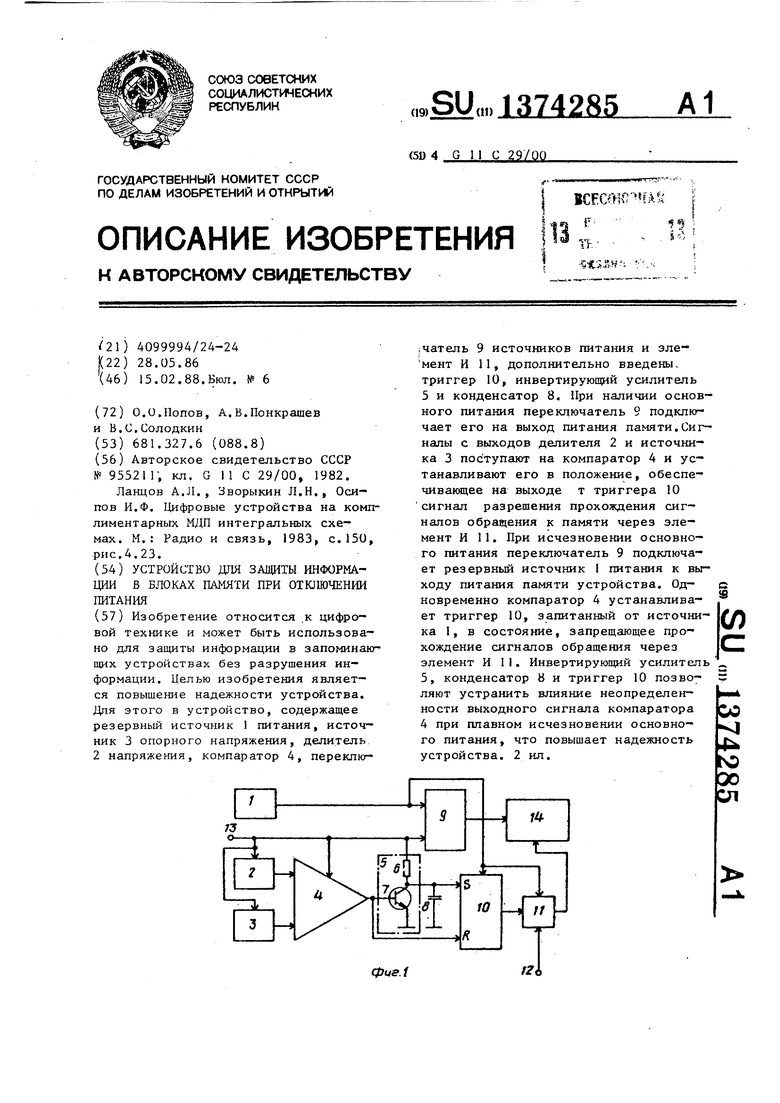

На фиг.1 изображена структурная схема предлагаемого устройства; на фиг.2 - временные диаграммы работы устройства.

Устройство содержит резервный источник 1 питания, делитель 2 напряжения, источник 3 опорного напряжения компаратор 4, инвертирующий усилитель 5, включающий резистор 6 и транзистор 7, накопительньш элемент на конденсаторе 8, переключатель 9 источников питания, триггер 10, элемент И 11, вход 12 сигнала разрешения обращения к памяти, вход 13 основного источника питания и блок 14 памяти (объект управления).

В качестве компаратора 4 может быть использована микросхема К554САЗ в типрвом включении. Делитель 2 напряжения выполняется как резистивный делитель, источник 3 опорного напряжения - как параметрический стабилизатор, а переключатель 9 источников питания - по типовой схеме.

В статическом состоянии величина сигнала на выходе делителя 2 напряжния и превьшает величину сигнала на выходе источника 3 опорного напр жения (ii«r.2a), при этом на выходе компаратора (фяг,2б} присутсвует низкий логический уровень, тразистор 7 закрыт, конденсатор 8 заряжен до уровня сигнала на выходе основного источника питания U . на

оип

установочном входе.триггера присутсвует высокий логический уровень (фиг.2в), а на сбросовом входе тригера 10 - низкий логический уровень На выходе триггера 10 (фиг.2г) присутствует высокий логический уровен открывающий элемент И 11. Сигнал рарешения обращения к памяти проходит со входа 12 через элемент И 11 на вход разрешения обращения блока 14 памяти ( фиг.2д). Питание блока 14 памяти производится через переключатель 9 источников питания от основнго источника питания.

При отключении основного источника питания уровень U сигнала на входе 13 подключения основного истоника питания начинает убывать (иг.

когда величина

сигнала на выходе делителя 2 напряжения Ug становится, равной величине сигнала на выходе источника 3 опорного напряжения , , на выходе паратора 4 формируется сигнал высокого логического уровня, который поступает на сбросовый вход триггера 10 и на базу транзистора 7 (фиг.2б).При этом транзистор 7 открывается, конденсатор 8 разряжается, и на установочном входе триггера 10 устанавливается низкий логический уровень

(фиг.2в). В результате этого на выходе триггера 10 устанавливается низкий логический уровень, который поступает на вход элемента И 11 и бло- кирует прохождение на выход его сигнала разрешения обращения к памяти (4иг. 2 г,д). На входе элемента И 1I устанавливается логический уровень, запрещающий доступ к ячейкам памяти блока 14 памяти (фиг.2д). При

повторных срабатываниях компаратора 4 сигнал с его выхода, поступающий иа сбросовый вход триггера 10, лищь подтверждает состояние триггера 10.

Одновременно переключатель 9 источников питания переключает питание блока памяти на резервньй источник питания.

При подключении основного источника питания уровень сигнала на входе 13 подключения основного источника питания возрастает (фиг.2а) В момент t , когда уровень сигнала

на выходе делителя 2 напряжения U превысит уровень сигнала на вьи-оде источника 3 опорного напряжения и„оп , компаратор 4 формирует низкий логический уровень, поступающий на сбросовый вход триггера 10 и на базу транзистора 7 (фиг.2б). Транзистор 7 закрывается. Конденсатор 8 заряжается от основного источника питания через резистор 6. Время заряда определяется величинами емкости конденсатора 8 и сопротивления резистора 6. Когда уровень сигнала на первом выводе конденсатора 8 превысит напряжение срабатывания триггера 10 U;.pg (т.е. в момент t), на выходе триггера 10 устанавливается высокий логический уровень, поступающий на первый вход элемента И 11 и разрешающий прохождение на его выход сигнала раз

гге

ffiffi

Vff Vuon

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с сохранением информации при отключении питания | 1987 |

|

SU1448362A1 |

| УСТРОЙСТВО ЗАЩИТЫ ПАМЯТИ | 1991 |

|

RU2006923C1 |

| Устройство для сохранения информации в полупроводниковой памяти при аварийном отключении питания | 1988 |

|

SU1599901A1 |

| Устройство для цифрового измерения частоты | 1989 |

|

SU1666965A2 |

| Запоминающее устройство с сохранением информации при аварийном отключении питания | 1987 |

|

SU1434504A1 |

| СЧЕТЧИК ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ | 2001 |

|

RU2190860C2 |

| Устройство для блокировки и перезапуска ЭВМ при сбоях питания | 1987 |

|

SU1464161A1 |

| Способ управления подачей инструмента на электроэрозионном станке с емкостным генератором импульсов и устройство для его осуществления | 1980 |

|

SU1351523A3 |

| Устройство для исследования внимания человека | 1985 |

|

SU1303141A1 |

| Устройство для автоматизированного контроля параметров реле | 1985 |

|

SU1265704A1 |

Изобретение относится .к цифровой технике и может быть использовано для защиты информации в запоминающих устройствах без разрушения информации. Целью изобретения является повышение надежности устройства. Для этого в устройство, содержащее резервный источник 1 питания, источник 3 опорного напряжения, делитель 2 напряжения, компаратор 4, переклю- ;чатель 9 источников питания и зле- мент И 11, дополнительно введены, триггер 10, инвертирующий усилитель 5 и конденсатор 8, При наличии основного питания переключатель 9 подключает его на выход питания памяти.Сигналы с выходов делителя 2 и источника 3 поступают на компаратор 4 и устанавливают его в положение, обеспечивающее на выходе т триггера 10 сигнал разрешения прохождения сигналов обращения к памяти через элемент И 11, При исчезновении основного питания переключатель 9 подключает резервный источник I питания к выходу питания памяти устройства. Одновременно компаратор 4 устанавливает триггер 10, запитанный от источника 1 , в состояние, запрещающее прохождение сигналов обращения через элемент И II. Инвертирующий усилитель 5, конденсатор 8 и триггер 10 позволяют устранить влияние неопределенности выходного сигнала компаратора 4 при плавном исчезновении основного питания, что повышает надежность устройства. 2 ил. с $8 (Л со о 00 ел фиг.1 ffi

Усрд

| Устройство для защиты информации в блоках памяти при отключении питания | 1981 |

|

SU955211A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Ланцов АЛ | |||

| , Зворыкин Л.Н | |||

| , Осипов И.Ф | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| М.: Радио и связь, 1983, с.150, рис.4.23. | |||

Авторы

Даты

1988-02-15—Публикация

1986-05-28—Подача