k

Р

ff

f2

4ib

со

4 СП

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с сохранением информации при отключении питания | 1986 |

|

SU1458892A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИСПРАВНОСТИ И ПЕРЕКЛЮЧЕНИЯ НИТЕЙ НАКАЛА ДВУХНИТЕВОЙ ЛАМПЫ СВЕТОФОРА | 1993 |

|

RU2064875C1 |

| Запоминающее устройство | 1983 |

|

SU1112412A1 |

| Устройство для управления резервным аппаратом магнитной записи | 1983 |

|

SU1062776A1 |

| УСТРОЙСТВО-КОНТРОЛЛЕР ДЛЯ УПРАВЛЕНИЯ СВЕРХЪЯРКИМИ СВЕТОДИОДАМИ В АКТИВНЫХ СВЕТОФОРНЫХ ГОЛОВКАХ | 2008 |

|

RU2378706C1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1989 |

|

SU1615809A1 |

| СИСТЕМА ИНДИКАЦИИ ЛЕТАТЕЛЬНОГО АППАРАТА | 2001 |

|

RU2206872C2 |

| Оперативное запоминающее устройство с резервированием строк | 1986 |

|

SU1462426A1 |

| УСТРОЙСТВО ДЛЯ ПОДГОТОВКИ К ПУСКУ РАКЕТЫ | 2022 |

|

RU2801840C1 |

| Устройство для защиты информации в блоке памяти | 1982 |

|

SU1084904A1 |

Изобретение относится к запоминающим устройствам и может быть использовано в специализированных цифровых вычислительных машинах или системах обработки цифровых данных, для сохранения информации при кратковременных перерывах энергоснабжения. Целью изобретения является повышение надежности запоминающего устройства. Устройство содержит блок 1 оперативной памяти.резервный источник 2 питания, элементы 4, 10 развязки, формирователь 6 сигнала блокировки, элемент И-НЕ 5 с открытым коллектором, управляемый стабилизатор 8 напряжения, стабилизатор 9 на- пряжения, компаратор 11 напряжения. Использование стабилизатора напряжения 9 и второго элемента развязки 10 позволяет избежать скачков напряжения на входе питания блока 1 оперативной памяти при переключении микро- о схем памяти из активного режима в ре- жим невыборки из-за большого различия токов потребления микросхем памяти в различных режимах. 3 ил. (Л

Фuz,i

Изобретение относится к .запоминающим устройствам и может быть использовано в составе спехщализиро- ванных цифровых вычислительных ма- шин или систем обработки цифровых данных, где требуется сохранение информации при кратковременных перерывах энергоснабжения.

Цель изобретения - повышение на- дежности запоминающего устройства.

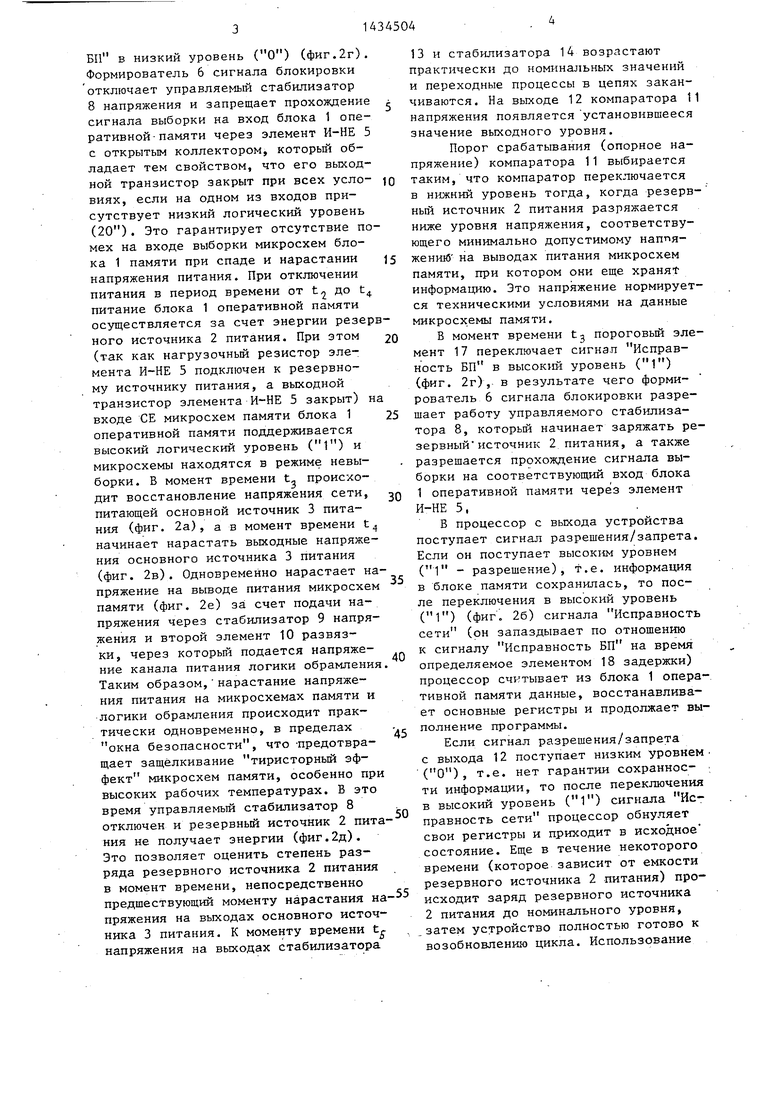

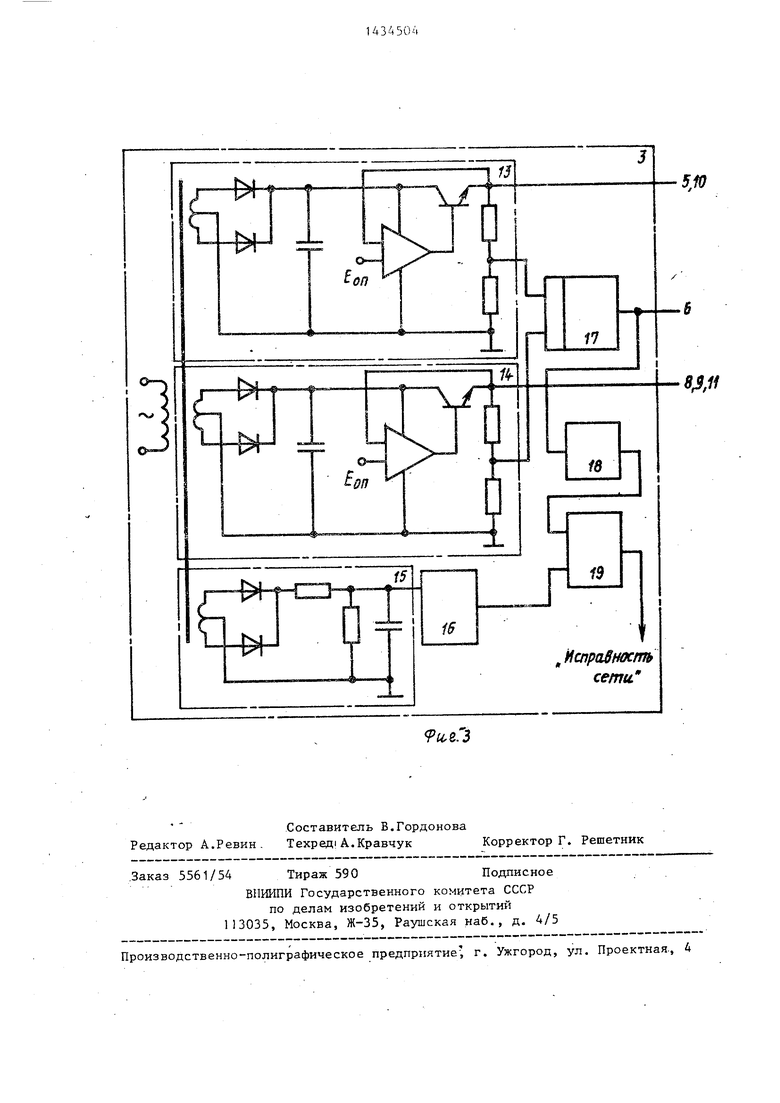

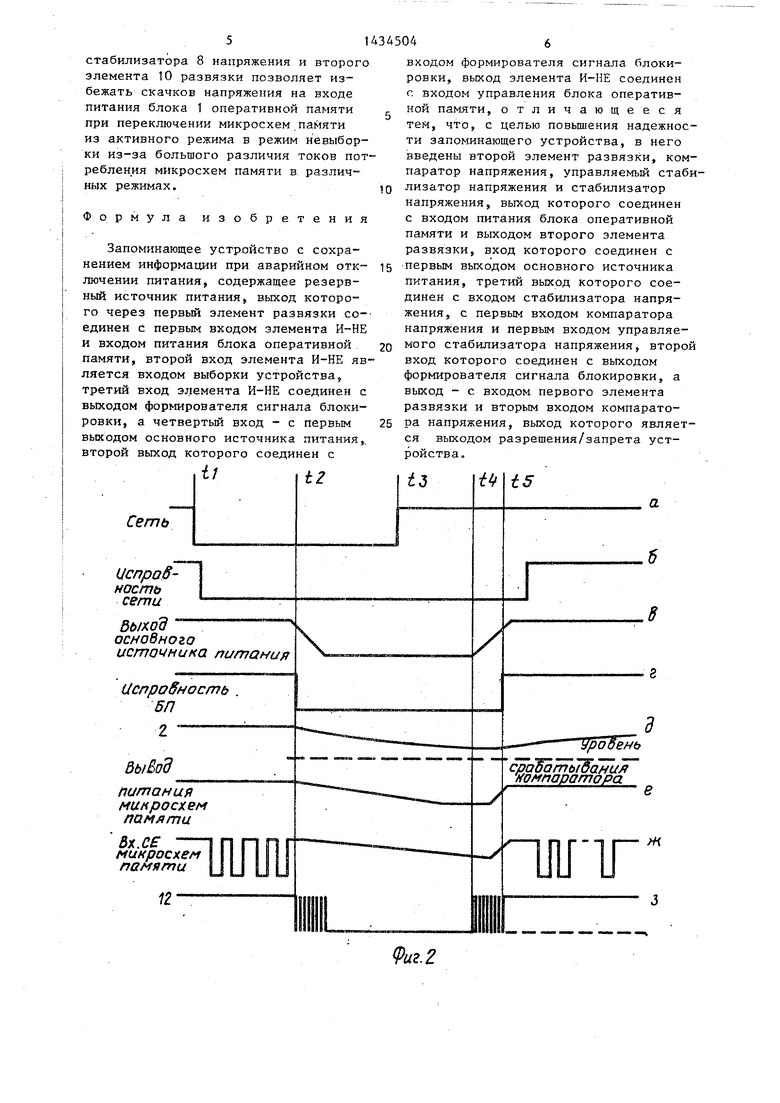

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2 - временные диаграммы, поясняющие работу устройства; на фиг.3 принципиальная схема основного источника питания.

Устройство содержит блок 1 оперативной памяти, резервный источник 2 питания, выполненный, например, на конденсаторе, основной источник 3 питания, первый элемент 4 развязки, например, диод, элемент И-НЕ 5 с открытым коллектором, например, микросхема 133ЛА7, формирователь 6 сигнала блокировки, вход 7 выборки устройства, управляемый стабилизатор 8 напряжения, стабилизатор 9 напряжения, второй элемент 10 развязки например, диод, компаратор 11 напряжения и выход 12 разрешения/запрета устройства

Основной источник 3 питания со- Держит стабилизатор 13 напряжения канала питания логики обрамления, стабилизатор 14 напряжения канала питания микросхем памяти, выпрямитель датчик 15 сетевого напряжения, пороговый элемент 16, пороговый элемент 17 с логикой 2И на входе, выход которого является выходом сигнала Исправность БП, элемент 18 задержки, элемент 2И 19, выход которого является вькодом сигнала сети.

Устройство работает следующим образом.

Если основной источник 3 питания исправен и напряжение сети находит™ ся в пределах допустимых значений, то на рыходах стабилизатора 13 напряжения канала питания логики обрамления и стабилизатора 14 напряжения канала питания микросхем памяти присутствуют номинальные напряжения, пороговый элемент 17 формирует высокий уровень (1) Сигнала Исправ- ность БП (исправность блока пита-, ния). Этот сигнал через элемент 18 задержки поступает на вход элемента

O

5

0 5

0

5

0

5

0

2И 19, на второй вход которого через пороговый элемент 16 подается сигнал от выпрямителя датчика 15 сетевого напряжения, в результате чего на выходе элемента 2И 19 появляется высокий уровень (1) сигнала Исправность сети.

Таким образом, все устройство питается от основного источника 3 питания, при этом сигнал Исправность БП на вькоде формирователя 6 сигнала блокировки имеет высокий уровень (1), т.е. открывает элемент Н-НЕ 5, через который сигнал выборки проходит на входы СЕ (выборка кристалла) микросхем памяти блока 1 оперативной памяти и разрешает работу управляемого стабилизатора 8 напряжения, который подает напряжение на резервный источник 2 питания и заряжает его до номинального значения, равного сумме напряжения на входе питания блока 1 оперативной памяти и падения напряжения на первом элементе 4 развязки. На вход питания 1 оперативной, памяти подается также напряжение через стабилизатор 9 напряжения, а через второй элемент 10 развязки - напряжение от канала питания логики обрамления. На выходе 12 компаратора 11 напряжения сигнал разрешения/ запрета имеет высокий уровень (1).

Пусть в момент времени t, (фиг.2а) произошло аварийное отключение сети, питающей основной источник 3 питания, при этом его выходное напряжение остается в пределах номинальных значений в течение некоторого времени (единицы миллисекунд) за счет энергии, накопленной в емкостях фильтров стабилизаторов 13 и 14 напряжений. Одновременно вьтрямитель - датчик 15 сетевого напряжения через пороговый элемент 16 и элемент 2И 19 .устанавливает сигнал Исправность сети в низкий уровень (О) (фиг.26). Этот сигнал поступает в процессор (не показан), что инициирует прерывание выполняемой программы, запись всех жизненно важных данных процессора (например, текущее значение основных регистров) в блок 1 оперативной памяти и останов,

В момент времени t, когда выходное напряжение основного источника. 3 питания уходят за пределы нижйих допусков(фиг. 2в), пороговый элемент 17 переключает сигнал Исправность

БП в низкий уровень (О) (фиг.2г). Формирователь 6 сигнала блокировки отключает управляемый стабилизатор 8 напряжения и запрещает прохождение сигнала выборки на вход блока 1 оперативной- памяти через элемент И-НЕ 5 с открытым коллектором, которьш обладает тем свойством, что его выходной транзистор закрыт при всех условиях, если на одном из входов присутствует низкий логический уровень (20). Это гарантирует отсутствие помех на входе выборки микросхем блока 1 памяти при спаде и нарастании напряжения питания. При отключении питания в период времени от t до t питание блока 1 оперативной памяти осуществляется за счет энергии резер ного источника 2 питания. При этом (так как нагрузочный резистор элемента И-НЕ 5 подключен к резервному источнику питания, а выходной транзистор элемента И-НЕ 5 закрыт) н входе СЕ микросхем памяти блока 1 оперативной памяти поддерживается высокий логический уровень (1) и микросхемы находятся в режиме невыборки. В момент времени t происходит восстановление напряжения сети, питающей основной источник 3 питания (фиг. 2а), а в момент времени t начинает нарастать выходные напряжения основного источника 3 питания (фиг. 2в). Одновременно нарастает напряжение на выводе питания микросхем памяти (фиг. 2е) за счет подачи напряжения через стабилизатор 9 напряжения и второй элемент 10 развязки, через которьй подается напряжение канала питания логики обрамления Таким образом, нарастание напряжения питания на микросхемах памяти и логики обрамления происходит практически одновременно, в пределах окна безопасности, что -предотвращает защёлкивание тиристорный эффект микросхем памяти, особенно при высоких рабочих температурах. В это время управляемьш стабилизатор 8 отключен и резервный источник 2 питания не получает энергии (фиг.2д). Это позволяет оценить степень разряда резервного источника 2 питания в момент времени, непосредственно предшествующий моменту нарастания напряжения на выходах основного источника 3 питания. К моменту времени tr- напряжения на выходах стабилизатора

5

0

13 и стабилизатора 14 возрастают практически до номинальных значений и переходные процессы в цепях заканчиваются. На выходе 12 компаратора 11 напряжения появляется установившееся значение выходного уровня.

Порог срабатывания (опорное напряжение) компаратора 11 выбирается

0 таким, что компаратор переключается в нижний уровень тогда, когда резервный источник 2 питания разряжается ниже уровня напряжения, соответствующего минимально допустимому наппя- жений на выводах питания микросхем памяти, при котором они еще xpaняt информацию. Это напряжение нормируется техническими условиями на данные микросхемы памяти.

В момент времени tg пороговый элемент 17 переключает сигнал Исправность БП в высокий уровень (1) (фиг. 2г), в результате чего формирователь 6 сигнала блокировки разрешает работу управляемого стабилизатора 8, которьм начинает заряжать резервный источник 2 питания, а также разрешается прохождение сигнала выборки на соответствующий вход блока

1оперативной памяти через элемент И-НЕ 5,

В процессор с выхода устройства поступает сигнал разрешения/запрета. Если он поступает высоким уровнем (1 - разрешение), т.е. информация в блоке памяти сохранилась, то после переключения в высокий уровень (1) (фиг. 2б) сигнала Исправность сети (он запаздывает по отношению к сигналу Исправность БП на время определяемое элементом 18 задержки) процессор считывает из блока 1 оперативной памяти данные, восстанавливает основные регистры и продолжает выполнение программы.

Если сигнал разрешения/запрета с выхода 12 поступает низким уровнем. (О), т.е. нет гарантии сохранное- ти информации, то после переключения в высокий уровень (1) сигнала Исправность сети процессор обнуляет свои регистры и приходит в исходное состояние. Еще в течение некоторого времени (которое зависит от емкости резервного источника 2 питания) происходит заряд резервного источника

2питания до номинального уровня,

,затем устройство полностью готово к возобновлению цикла. Использование

0

5

0

5

0

5

51

стабилизатора 8 напряжения и второго элемента 10 развязки позволяет избежать скачков напряжения на входе питания блока 1 оперативной памяти при переключении микросхем памяти из активного режима в режим невыбор- ки из-за большого различия токов пот ребления микросхем памяти в различных режимах.

Формула изобретения

Запоминающее устройство с сохранением информации при аварийном отк лючении питания, содержащее резервный источник питания, выход которого через первый элемент развязки соединен с первым входом элемента и входом питания блока оперативной памяти, второй вход элемента И-НЕ яв ляется входом выборки устройства, третий вход элемента И-НЕ соединен с выходом формирователя сигнала блокировки, а четвертый вход - с первым выходом основного источника питанияj. второй выход которого соединен с

if

iZ

Сеть

исправностьсети

5ь/ход

основного источника пит

Ucrtpo Hocmb БП

Вь/Вод

питания микрос)С.вм памяти

5х.С

микросхем

памяти

г -

345046

входом формирователя сигнала блокировки, выход элемента И-НЕ соединен г. входом управления блока оперативной памяти, отличающееся тем, что, с целью повьшения надежности запоминающего устройства, в него введены второй элемент развязки, компаратор напряжения, управляемый стабиIQ лизатор напряжения и стабилизатор напряжения, вьпсод которого соединен с входом питания блока оперативной памяти и выходом второго элемента развязки, вход которого соединен с

15 первым выходом основного источника питания, третий выход которого соединен с входом стабилизатора напряжения, с первым входом компаратора напряжения и первым входом управляе2Q мого стабилизатора напряжения, второй вход которого соединен с выходом

формирователя сигнала блокировки, а выход - с входом первого элемента развязки и вторым входом компарато25 ра напряжения, выход которого является выходом разрешения/запрета устройства.

td

iff

i5

ruu ir

лЧ

(раг.2

и,е:з

| Оперативное запоминающее устройство на микросхемах памяти | 1983 |

|

SU1173448A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Авторское свидетельство СССР № 1179436, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-10-30—Публикация

1987-03-04—Подача