(21)4104921/24-24

(22)15.08.86

(46) 23.02.88. Бюл. # 7 . (72) Г.В.Майзель и А В;Стеняев

(53)681.325(088.8)

(56)Таблично-знаковый индикатор РИН-608С ЭП 1.620.136-09 ПФ.

Авторское свидетельство СССР 1211739, кл. G Об F 13/00, 1984.

(54)УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ МИКРОЭВМ С ТАБЛО ИНДИКАЦИИ

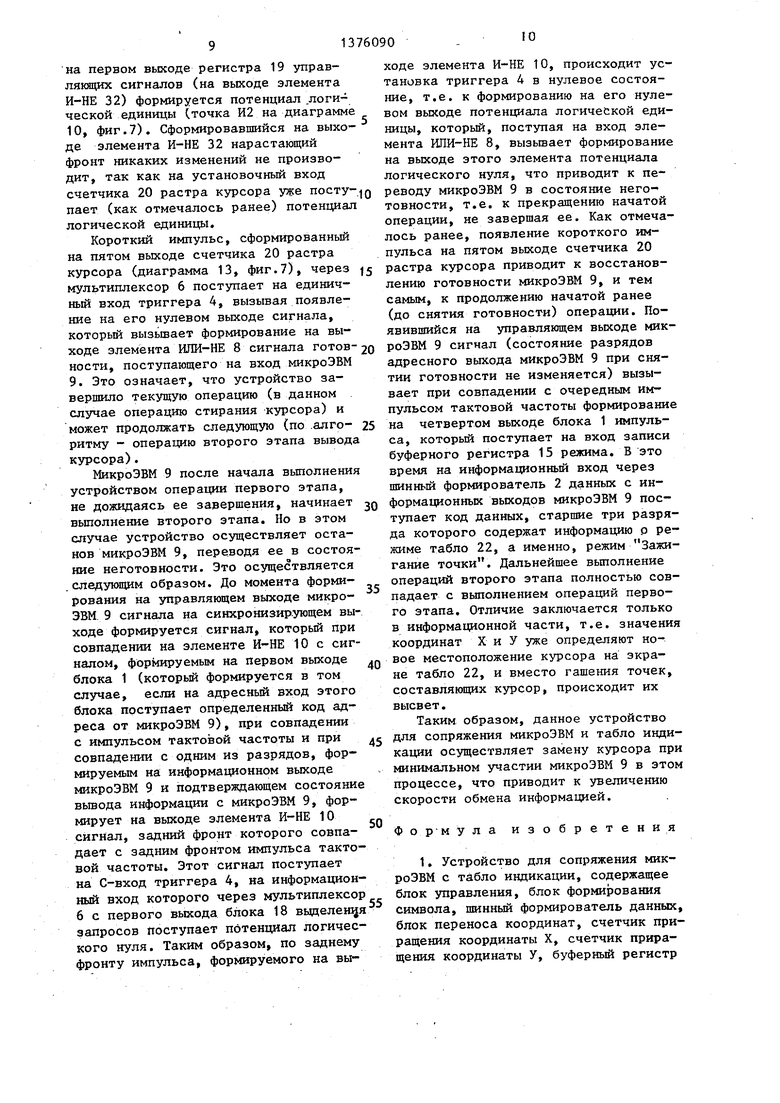

(57)Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройстве отображения информации, где в качестве блока управления используется микроЭВМ, а в качестве блока отображения - табло индикации. Целью изобретения является повышение быстродействия.. Устройство содержит блок управления, блок формирования символа, шинный формирователь данных, мультиплексор, счетчик приращения координаты X и координаты У, буферный регистр режима, регистры координаты X и координаты У, регистр режима, блок переноса координат, блок вьщеления запросов, регистр управляющих сигналов, счетчик растра курсора, блок памяти приращения координат, триггер, элемент И-НЕ, элемент ИПИ-НЕ, элемент ИЛИ и элемент И. 1 з.п. ф-лы, 7 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вывода информации | 1986 |

|

SU1377849A1 |

| Устройство для сопряжения электронно-вычислительной машины с табло индикации | 1984 |

|

SU1211739A1 |

| Устройство для обмена информацией | 1986 |

|

SU1424001A1 |

| Устройство для отображения информацииНА эКРАНЕ ТЕлЕВизиОННОгО пРиЕМНиКА | 1979 |

|

SU842933A1 |

| Устройство для контроля выполнения программ (его варианты) | 1985 |

|

SU1315981A1 |

| Устройство для отображения векторов на экране телевизионного приемника | 1977 |

|

SU739591A1 |

| Устройство формирования телевизионного графического изображения | 1990 |

|

SU1728983A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Устройство для отображения информации | 1985 |

|

SU1354183A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1983 |

|

SU1182568A1 |

00

Од

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройстве отображения информации, где в качестве блока управления используется микро- ЭВМ, а в качестве блока отображения - табло индикации.

Цель изобретения - повышение быстродействия.

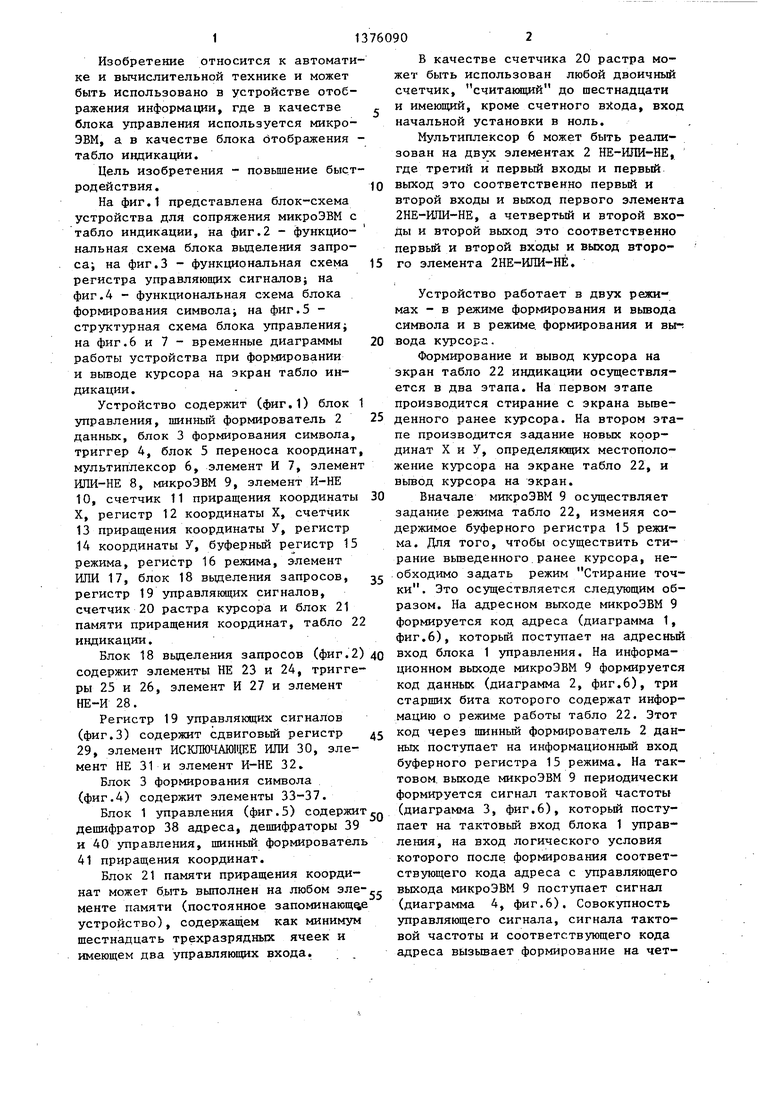

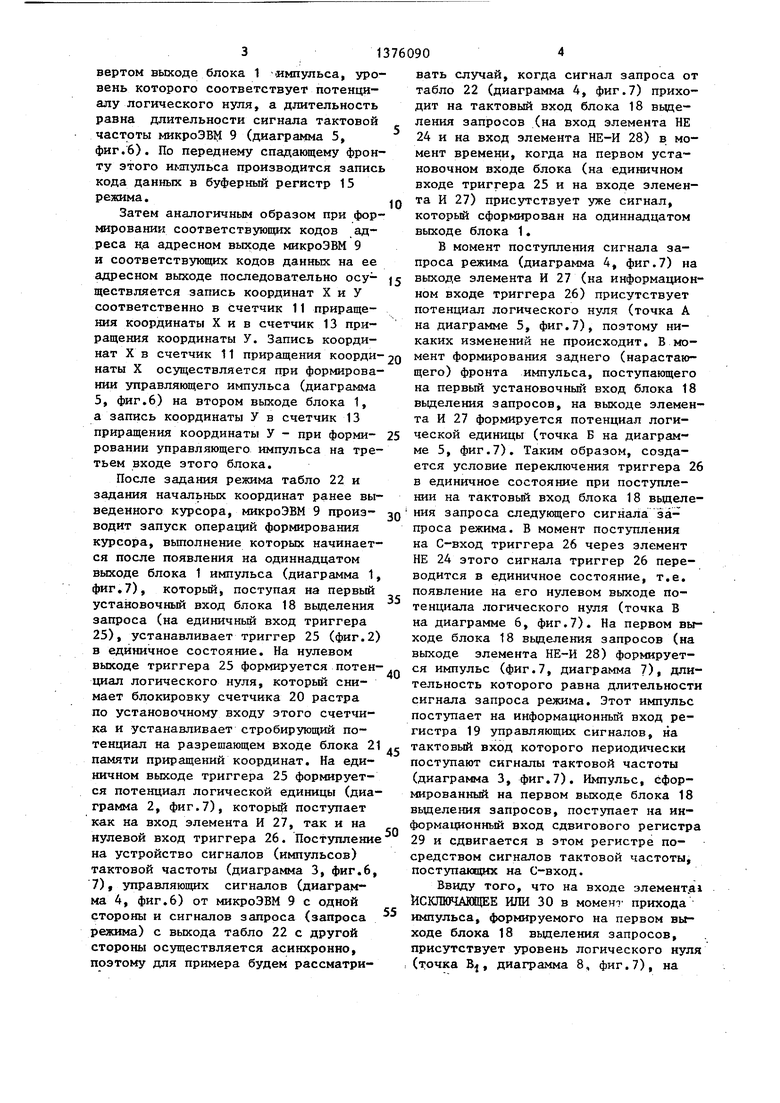

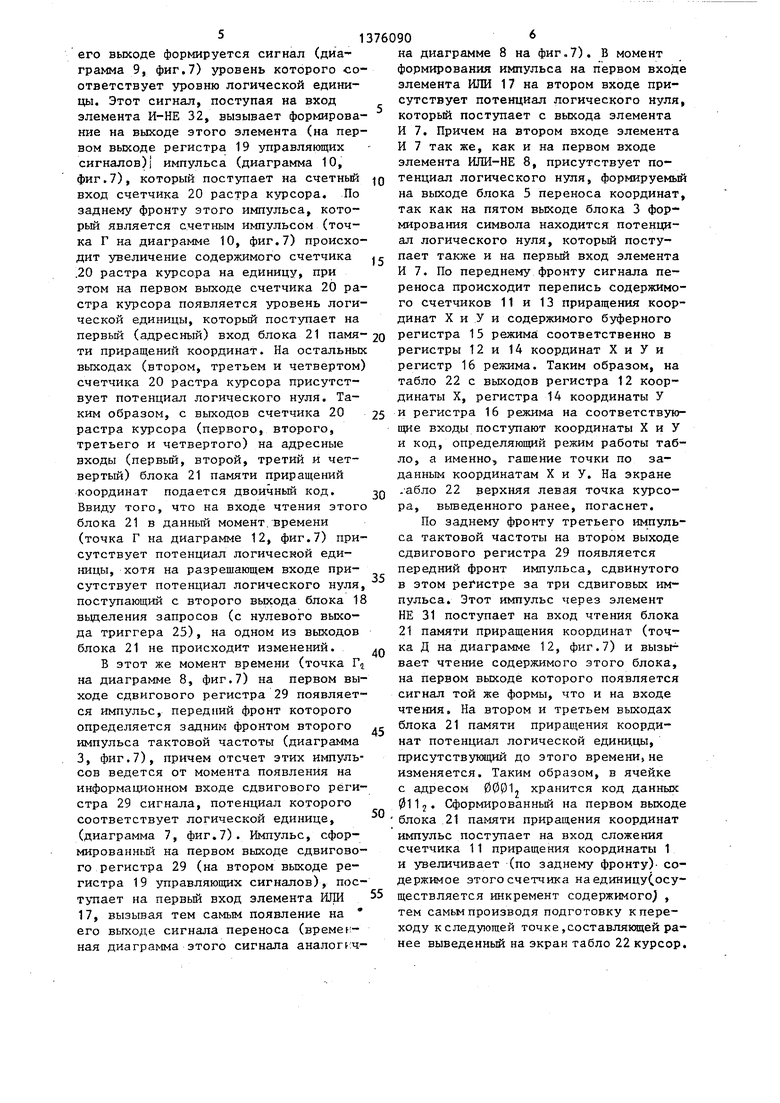

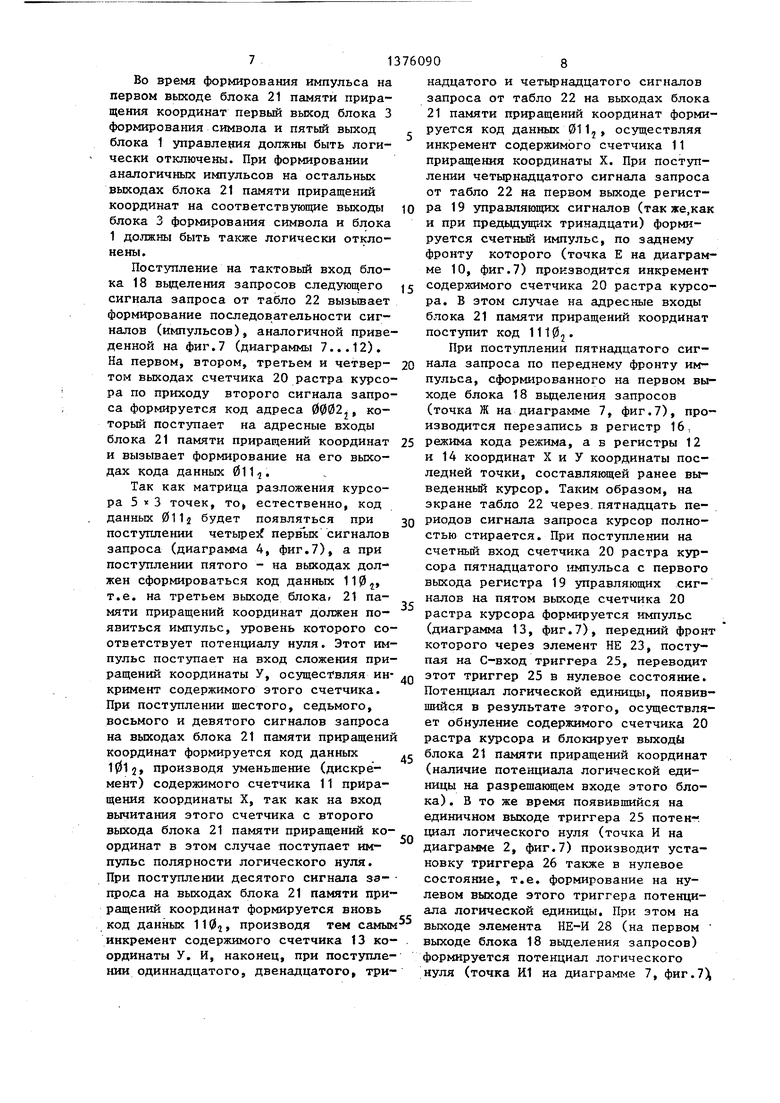

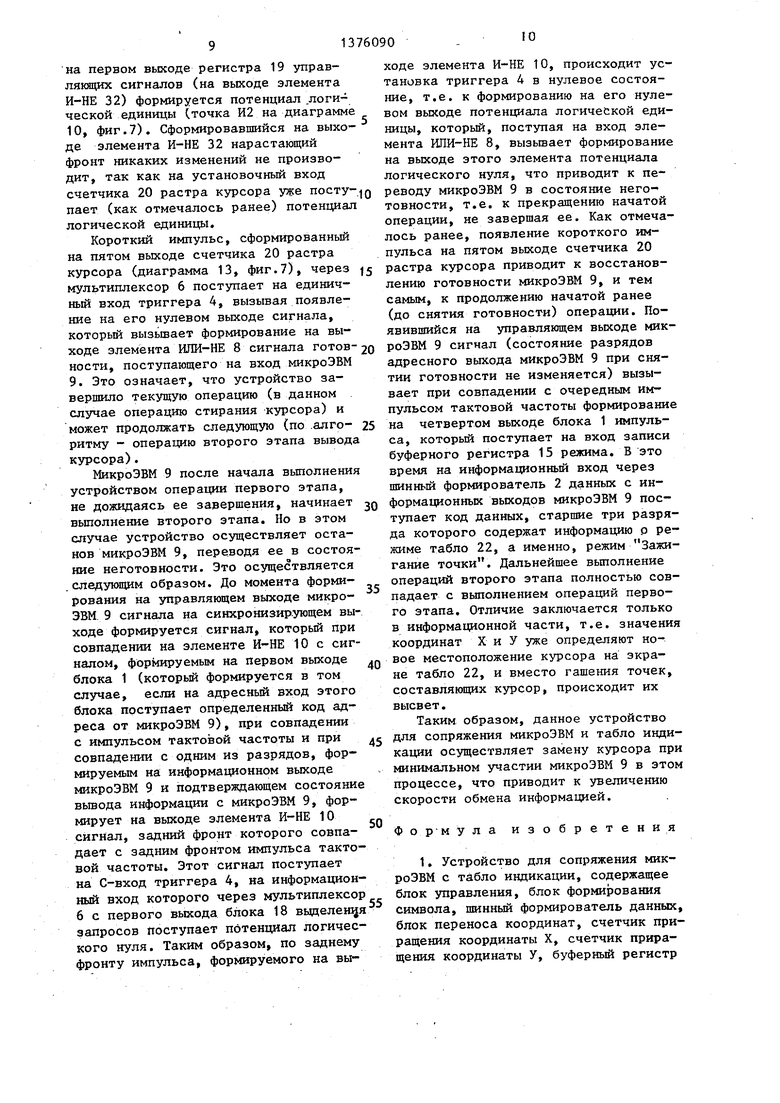

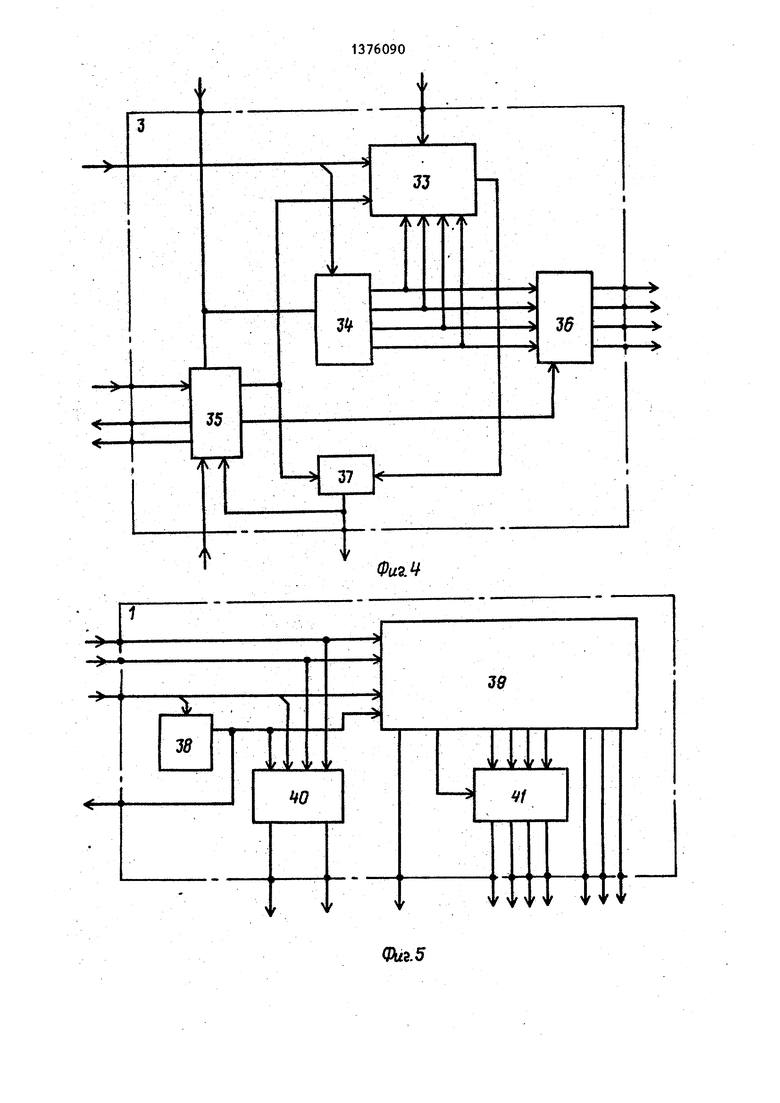

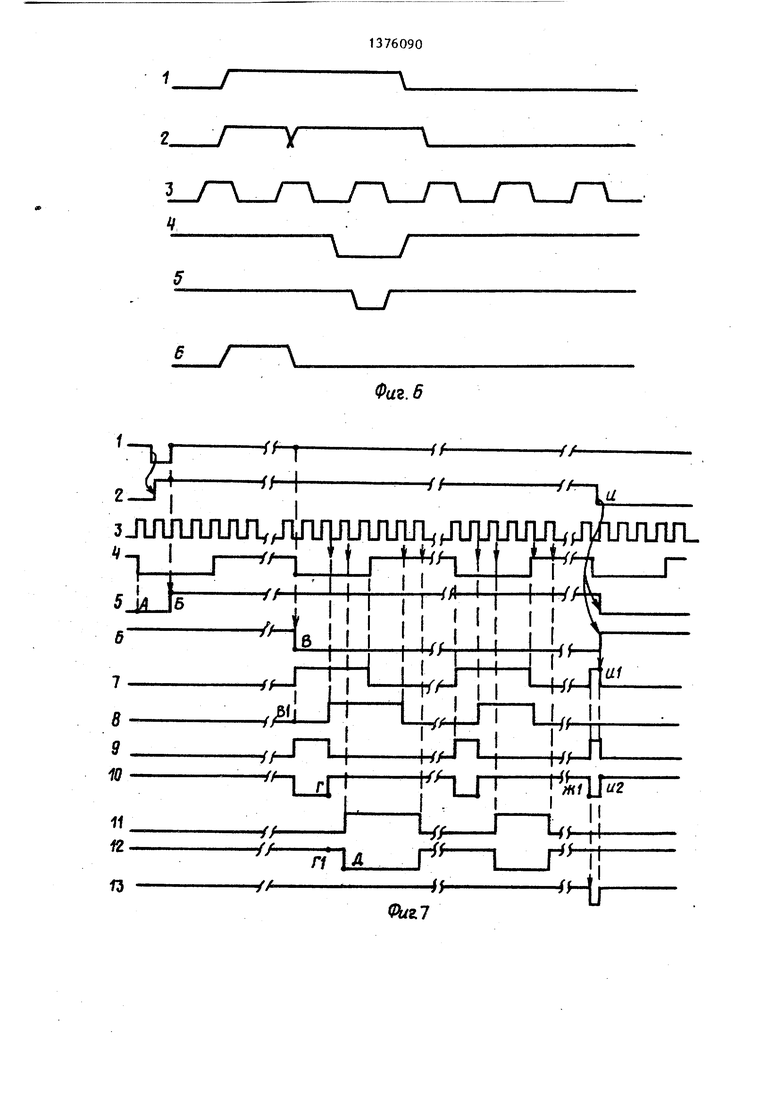

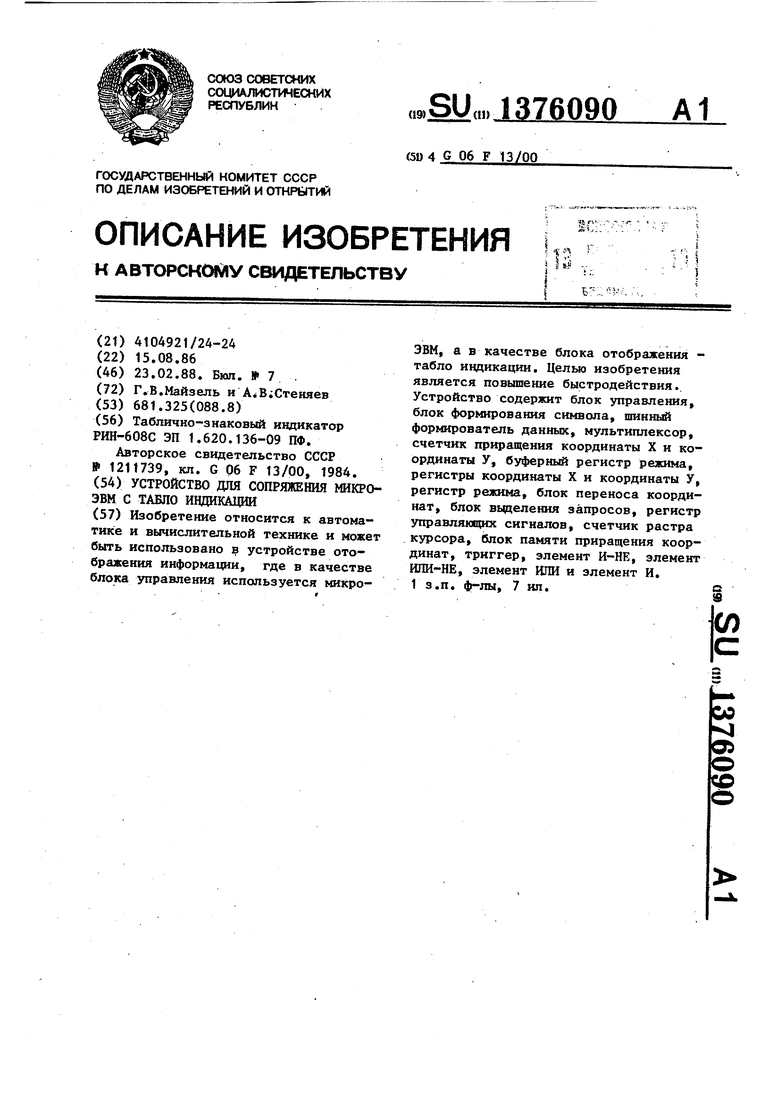

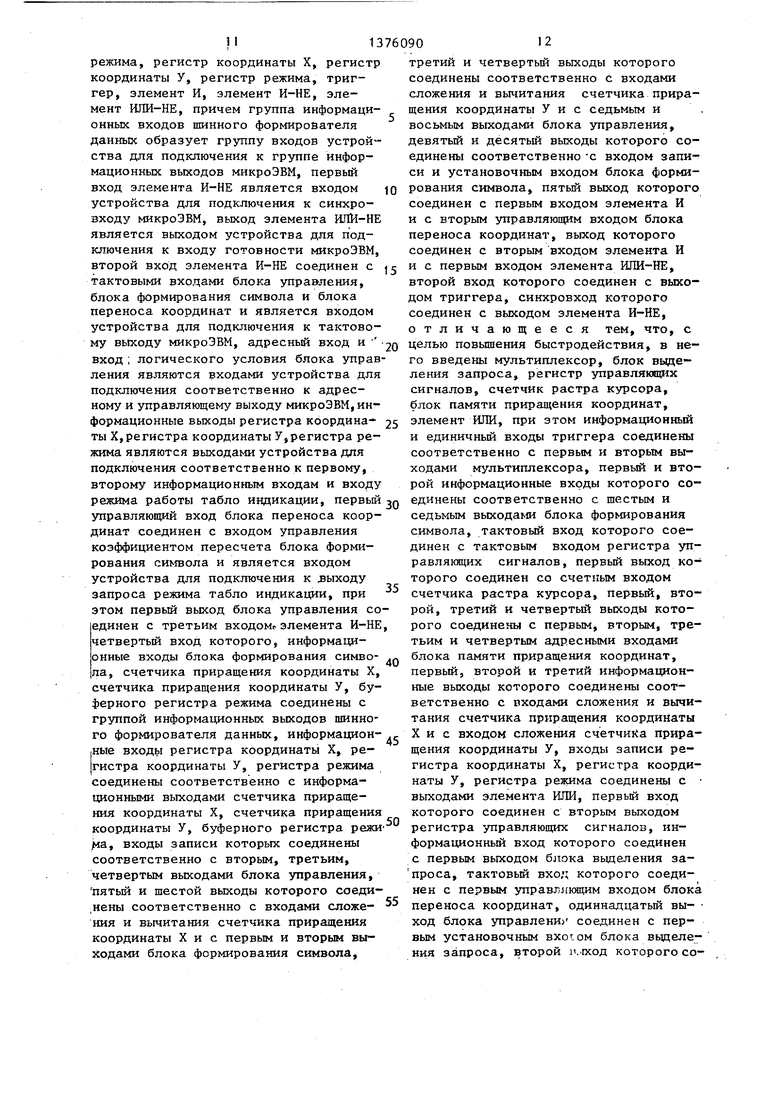

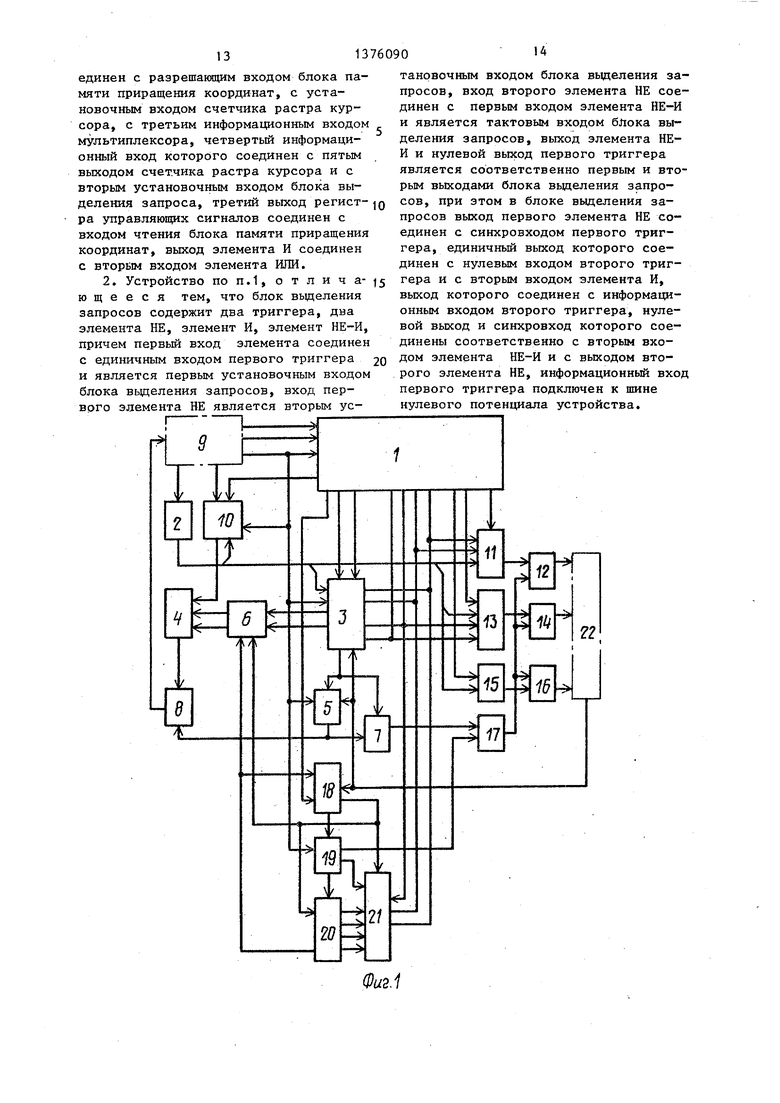

На фиг.1 представлена блок-схема устройства для сопряжения микроЭВМ с табло индикации, на фиг.2 - функцио- нальная схема блока вьщеления запроса j на фиг.З - функциональная схема регистра управляющих сигналов; на фиг.4 - функциональная схема блока формирования символа; на фиг.З - структурная схема блока управления; на фиг.6 и 7 - временные диаграммы работы устройства при формировании и вьтоде курсора на экран табло индикации .

Устройство содержит (фиг.1) блок 1 управления, шинный формирователь 2 данных, блок 3 формирования символа, триггер 4, блок 5 переноса координат, мультиплексор 6, элемент И 7, элемент ИЛИ-НЕ 8, микроэвм 9, элемент И-НЕ 10, счетчик 11 приращения координаты X, регистр 12 координаты X, счетчик

13приращения координаты У, регистр

14координаты У, буферный регистр 15 режима, регистр 16 режима, элемент

ИЛИ 17, блок 18 выделения запросов, регистр 19 управляющих сигналов, счетчик 20 растра курсора и блок 21 памяти приращения координат, табло 22 индикации.

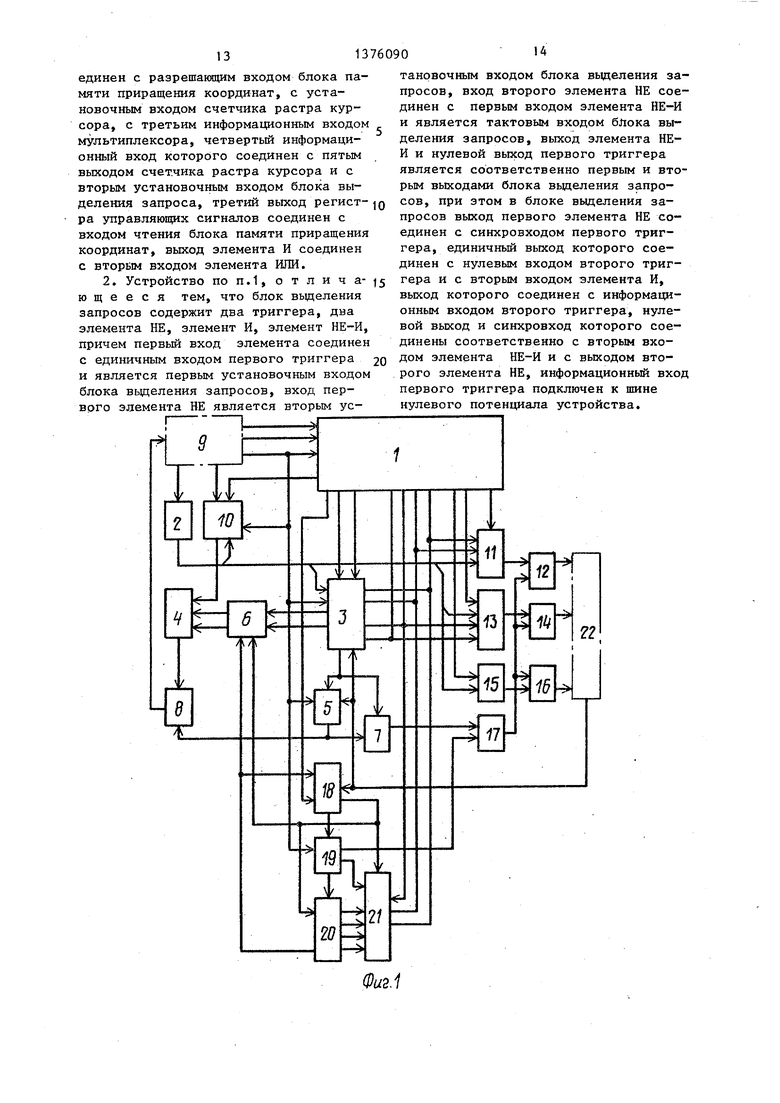

Блок 18 выделения запросов (фиг.2) содержит элементы НЕ 23 и 24, триггеры 25 и 26, элемент И 27 я элемент НЕ-И 28.

Регистр 19 управляющих сигналов (фиг.З) содержит сдвиговый регистр 29, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 30, элемент НЕ 31 и элемент И-НЕ 32.

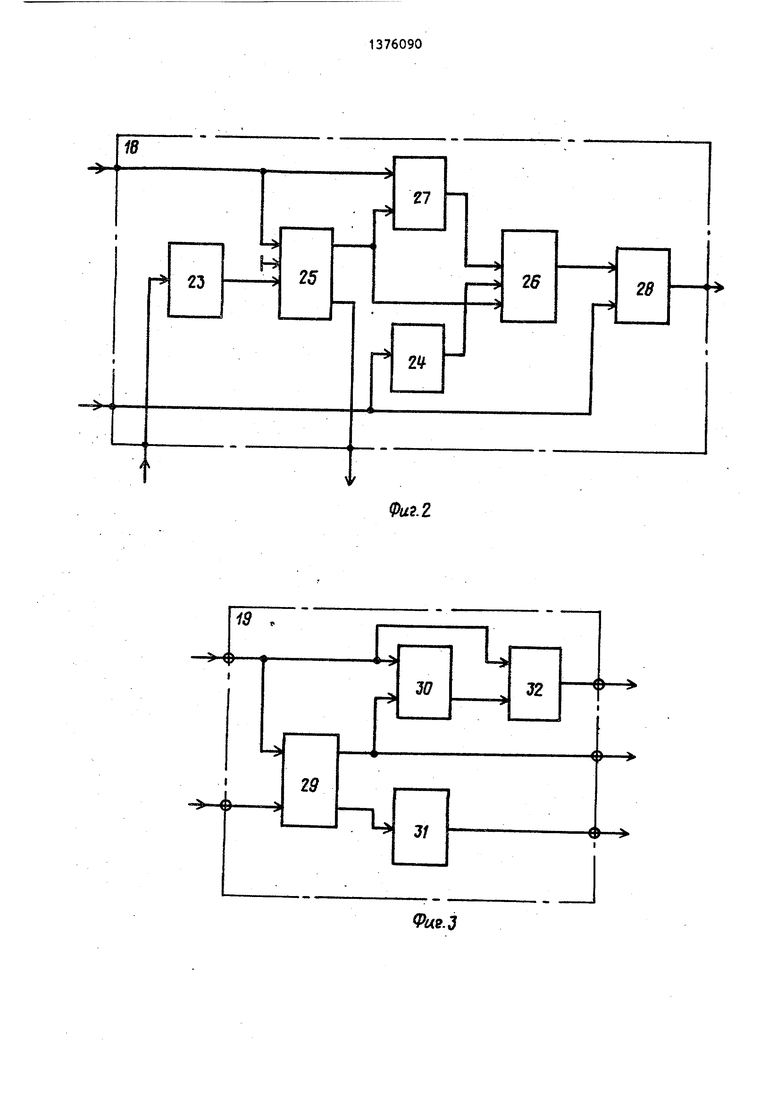

Блок 3 формирования символа (фиг.4) содержит элементы 33-37.

Блок 1 управления (фиг. 5) содержит дешифратор 38 адреса, дешифраторы 39 и 40 управления, шинный формирователь 41 приращения координат.

Блок 21 памяти приращения координат может быть выполнен на любом элементе памяти (постоянное запоминающее устройство), содержащем как минимум шестнадцать трехразрядных ячеек и имеющем два управляющих входа.

В качестве счетчика 20 растра может быть использован любой двоичный счетчик, считакяций до шестнадцати и имеющий, кроме счетного вз{ода, вход начальной установки в ноль.

Мультиплексор 6 может быть реализован на двух элементах 2 НЕ-ИЛИ-НЕ, где третий и первый входы и первый выход это соответственно первый и второй входы и выход первого элемента 2НЕ-ИПИ-НЕ, а четвертый и второй входы и второй выход это соответственно первый и второй входы и выход второго элемента 2НЕ-ИЛИ-НЕ.

Устройство работает в двух режимах - в режиме формирования и вьшода символа и в режиме, формирования и вывода курсора.

Формирование и вывод курсора на экран табло 22 индикации осуществляется в два этапа. На первом этапе производится стирание с экрана вьше- денного ранее курсора. На втором этапе производится задание новых координат X и У, определяющих местоположение курсора на экране табло 22, и вьшод курсора на экран.

Вначале микроЭВМ 9 осуществляет задание режима табло 22, изменяя содержимое буферного регистра 15 режима. Для того, чтобы осуществить стирание вьшеденного.ранее курсора, не- ,обходимо задать режим Стирание точки . Это осуществляется следующим образом. На адресном выходе микроЭВМ 9 формируется код адреса (диаграмма 1, фиг.6), которьй поступает на адресный вход блока 1 управления. На информационном выходе микроэвм 9 формируется код данных (диаграмма 2, фиг.6), три старших бита которого содержат информацию о режиме работы табло 22. Этот код через шинный формирователь 2 данных поступает на информационный вход буферного регистра 15 режима. На тактовом, выходе микроэвм 9 периодически формируется сигнал тактовой частоты (диаграмма 3, фиг.6), который поступает на тактовый вход блока 1 управления, на вход логического условия которого после формирования соответствующего кода адреса с управляющего выхода микроэвм 9 поступает сигнал (диаграмма 4, фиг.6). Совокупность управляющего сигнала, сигнала тактовой частоты и соответствующего кода адреса вЫзьтает формирование на чет-

вертом выходе блока 1 импульса, уровень которого соответствует потенциалу логического нуля, а длительность равна длительности сигнала тактовой частоты микроэвм 9 (диаграмма 5, фиг.6). По переднему спадающему фронту этого и шyльca производится запись кода данных в буферный регистр 15 режима.

Затем аналогичным образом при формировании соответствующих кодов адреса на адресном выходе микроЭВМ 9 и соответствующих кодов данных на ее адресном выходе последовательно осу- ществляется запись координат X и У соответственно в счетчик 11 приращения координаты X и в счетчик 13 приращения координаты У. Запись координат X в счетчик 11 приращения коорди-20 мент формирования заднего (нарастаюнаты X осуществляется при формировании управляющего импульса (диаграмма 5, фиг.6) на втором выходе блока 1, а запись координаты У в счетчик 13 приращения координаты У - при форми- 25 ровании управляющего импульса на третьем входе этого блока.

После задания режима табло 22 и задания начальных координат ранее выведенного курсора, микроэвм 9 проиэ- JQ водит запуск операций формирования курсора, выполнение которых начинается после появления на одиннадцатом выходе блока 1 импульса (диаграмма 1, фиг,7), который, поступая на первый установочный вход блока 18 вьщеления запроса (на единичный вход триггера 25), устанавливает триггер 25 (фиг.2) в единичное состояние. На нулевом выходе триггера 25 формируется потенциал логического нуля, который снимает блокировку счетчика 20 растра по установочному входу этого счетчика и устанавливает стробирующий по-

35

40

щего) фронта импульса, поступающего на первый установочный вход блока 18 выделения запросов, на выходе элемента И 27 формируется потенциал логической единицы (точка Б на диаграмме 5, фиг.7). Таким образом, создается условие переключения триггера 26 в единичное состояние при поступле- 1ШИ на тактовый вход блока 18 вьщеления запроса следующего сигнала запроса режима. В момент поступления на С-вход триггера 26 через элемент НЕ 24 этого сигнала триггер 26 переводится в единичное состояние, т.е. появление на его нулевом выходе потенциала логического нуля (точка В на диаграмме 6, фиг.7). На первом выходе блока 18 вьщеления запросов (на выходе элемента НЕ-И 28) формируется импульс (фиг.7, диаграмма 7) длительность которого равна длительности сигнала запроса режима. Этот импульс поступает на информационный вход регистра 19 управляющих сигналов, на

тенциал на разрешающем входе блока 21 . тактовый вход которого периодически

памяти приращений координат. На единичном выходе триггера 25 формируется потенциал логической единицы (диаграмма 2, фиг.7), который поступает как на вход элемента И 27, так и на

нулевой вход триггера 26. Поступление 29 и сдвигается

поступают сигналы тактовой частоты (диаграмма 3, фиг.7). Импульс, сформированный на первом выходе блока 18 вьщелекия запросов, поступает на информационный вход сдвигового регистр

на устройство сигналов (импульсов) тактовой частоты (диаграмма 3, фиг.6, 7), управляющих сигналов (диаграмма 4, фиг.6) от микроэвм 9 с одной стороны и сигналов запроса (запроса режима) с выхода табло 22 с другой стороны осуществляется асинхронно, поэтому для примера будем рассматрив этом регистре по55

средством сигналов тактовой частоты, поступающих на С-вход.

Ввиду того, что на входе элементд ЙСКЛЮЧАВЩЕ ИЛИ 30 в момент прихода импульса, формируемого на первом выходе блока 18 вьщеления запросов, присутствует уровень логического нул : (точка В, диаграмма 8, фиг.7), на

вать случай, когда сигнал запроса от табло 22 (диаграмма 4, фиг.7) приходит на тактовый вход блока 18 вьще- ления запросов (на вход элемента НЕ 24 и на вход элемента НЕ-И 28) в момент времени, когда на первом установочном входе блока (на единичном входе триггера 25 и на входе элемента И 27) присутствует уже сигнал, который сформирован на одиннадцатом выходе блока 1.

В момент поступления сигнала запроса режима (диаграмма 4, фиг.7) на выходе элемента И 27 (на информационном входе триггера 26) присутствует потенциал логического нуля (точка А на диаграмме 5, фиг.7), поэтому никаких изменений не происходит. В момент формирования заднего (нарастаю

щего) фронта импульса, поступающего на первый установочный вход блока 18 выделения запросов, на выходе элемента И 27 формируется потенциал логической единицы (точка Б на диаграмме 5, фиг.7). Таким образом, создается условие переключения триггера 26 в единичное состояние при поступле- 1ШИ на тактовый вход блока 18 вьщеления запроса следующего сигнала запроса режима. В момент поступления на С-вход триггера 26 через элемент НЕ 24 этого сигнала триггер 26 переводится в единичное состояние, т.е. появление на его нулевом выходе потенциала логического нуля (точка В на диаграмме 6, фиг.7). На первом выходе блока 18 вьщеления запросов (на выходе элемента НЕ-И 28) формируется импульс (фиг.7, диаграмма 7) длительность которого равна длительности сигнала запроса режима. Этот импульс поступает на информационный вход регистра 19 управляющих сигналов, на

поступают сигналы тактовой частоты (диаграмма 3, фиг.7). Импульс, сформированный на первом выходе блока 18 вьщелекия запросов, поступает на информационный вход сдвигового регистра

в этом регистре по55

средством сигналов тактовой частоты, поступающих на С-вход.

Ввиду того, что на входе элементд ЙСКЛЮЧАВЩЕ ИЛИ 30 в момент прихода импульса, формируемого на первом выходе блока 18 вьщеления запросов, присутствует уровень логического нуля : (точка В, диаграмма 8, фиг.7), на

его выходе формируется сигнал (диаграмма 9, фиг.7) уровень которого соответствует уровню логической единицы. Этот сигнал, поступая на вход элемента И-НЕ 32, вызывает формирование на выходе этого элемента (на первом выходе регистра 19 управляющих сигналов) импульса (диаграмма 10, фиг,7), который поступает на счетный Q вход счетчика 20 растра курсора. По заднему фронту этого импульса, который является счетным импульсом (точка Г на диаграмме 10, фиг.7) происходит увеличение содержимого счетчика jr .20 растра курсора на единицу, при этом на первом выходе счетчика 20 растра курсора появляется уровень логической единицы, который поступает на

на диаграмме 8 на фиг.7). В момент формирования импульса на первом вход элемента ИЛИ 17 на втором входе присутствует потенциал логического нуля который поступает с выхода элемента И 7. Причем на втором входе элемента И 7 так же, как и на первом входе элемента ШШ-НЕ 8, присутствует потенциал логического нуля, формируемь на выходе блока 5 переноса координат так как на пятом выходе блока 3 формирования символа находится потенциал логического нуля, который поступает также и на первый вход элемента И 7. По переднему фронту сигнала переноса происходит перепись содержимо го счетчиков 11 и 13 приращения коор динат X и У и содержимого буферного

25

30

35

первый (адресный) вход блока 21 памя-20 регистра 15 режима соответственно в ти приращений координат. На остальных выходах (втором, третьем и четвертом) счетчика 20 растра курсора присутствует потенциал логического нуля. Таким образом, с выходов счетчика 20 растра курсора (первого, второго, третьего и четвертого) на адресные входы (первый, второй, третий и четвертый) блока 21 памяти приращений координат подается двоичный код. Ввиду того, что на входе чтения этого блока 21 в данный момент, времени (точка Г на диаграмме 12, фиг.7) присутствует потенциал логической единицы, хотя на разрешающем входе присутствует потенциал логического нуля, поступающий с второго выхода блока 18 вьщеления запросов (с нулевого выхода триггера 25), на одном из выходов блока 21 не происходит изменений, Q

В этот же момент времени (точка Г на диаграмме 8, фиг,7) на первом выходе сдвигового регистра 29 появляется импульс, передний фронт которого определяется задним фронтом второго импульса тактовой частоты (диаграмма 3, фиг,7), причем отсчет этих импульсов ведется от момента появления на информационном входе сдвигового регистра 29 сигнала, потенциал которого соответствует логической единице, (диаграмма 7, фиг.7), Импульс, сформированный на первом выходе сдвигового регистра 29 (на втором выходе регистра 19 управляющих сигналов), поступает на первьй вход элемента ИЛИ 55 17, вызывая тем самым появление на его выходе сигнала переноса (временная диаграмма этого сигнала aнaлoг :ч45

50

регистры 12 и 14 координат X и У и регистр 16 режима. Таким образом, на табло 22 с выходов регистра 12 координаты X, регистра 14 координаты У и регистра 16 режима на соответствую щие входы поступают координаты X и У и код, определяющий режим работы таб ло, а именно, гашение точки по заданным координатам X и У. На экране -абло 22 верхняя левая точка курсора, вьшеденного ранее, погаснет.

По заднему фронту третьего импуль са тактовой частоты на втором выходе сдвигового регистра 29 появляется передний фронт импульса, сдвинутого в этом ре1 истре за три сдвиговых импульса. Этот импульс через элемент НЕ 31 поступает на вход чтения блока 21 памяти приращения координат (точка Д на диаграмме 12, фиг, 7) и вызьг вает чтение содержимого этого блока, на первом выходе которого появляется сигнал той же формы, что и на входе чтения. На втором и третьем выходах блока 21 памяти приргщения координат потенциал логической единдцы, присутствующий до этого времени,не изменяется. Таким образом, в ячейке с адресом 0001. хранится код данных 011,. Сформированный на первом выход блока 21 памяти приращения координат импульс поступает на вход сложения счетчика 11 приращения координаты 1 и увеличивает (по заднему фронту)- со держимое этого счетчика наединицу(осу ществляется инкремент содержимого , тем самьм производя подготовку к переходу к следующей точке ,составляклцей ра нее выведенный на экран табло 22 курсор

на диаграмме 8 на фиг.7). В момент формирования импульса на первом входе элемента ИЛИ 17 на втором входе присутствует потенциал логического нуля, который поступает с выхода элемента И 7. Причем на втором входе элемента И 7 так же, как и на первом входе элемента ШШ-НЕ 8, присутствует потенциал логического нуля, формируемьй на выходе блока 5 переноса координат, так как на пятом выходе блока 3 формирования символа находится потенциал логического нуля, который поступает также и на первый вход элемента И 7. По переднему фронту сигнала переноса происходит перепись содержимого счетчиков 11 и 13 приращения координат X и У и содержимого буферного

5

0

5

0 регистра 15 режима соответственно в Q

5

5

0

регистры 12 и 14 координат X и У и регистр 16 режима. Таким образом, на табло 22 с выходов регистра 12 координаты X, регистра 14 координаты У и регистра 16 режима на соответствующие входы поступают координаты X и У и код, определяющий режим работы табло, а именно, гашение точки по заданным координатам X и У. На экране -абло 22 верхняя левая точка курсора, вьшеденного ранее, погаснет.

По заднему фронту третьего импульса тактовой частоты на втором выходе сдвигового регистра 29 появляется передний фронт импульса, сдвинутого в этом ре1 истре за три сдвиговых импульса. Этот импульс через элемент НЕ 31 поступает на вход чтения блока 21 памяти приращения координат (точка Д на диаграмме 12, фиг, 7) и вызьг вает чтение содержимого этого блока, на первом выходе которого появляется сигнал той же формы, что и на входе чтения. На втором и третьем выходах блока 21 памяти приргщения координат потенциал логической единдцы, присутствующий до этого времени,не изменяется. Таким образом, в ячейке с адресом 0001. хранится код данных 011,. Сформированный на первом выходе блока 21 памяти приращения координат импульс поступает на вход сложения счетчика 11 приращения координаты 1 и увеличивает (по заднему фронту)- содержимое этого счетчика наединицу(осу- ществляется инкремент содержимого , тем самьм производя подготовку к переходу к следующей точке ,составляклцей ранее выведенный на экран табло 22 курсор.

Во время формирования импульса на первом выходе блока 21 памяти приращения координат первый выход блока 3 формирования символа и пятый выход блока 1 управления должны быть логически отключены. При формировании аналогичных импульсов на остальных выходах блока 21 памяти приращений координат на соответствующие выходы блока 3 формирования символа и блока 1 должны быть также логически отклонены.

Поступление на тактовый вход блока 18 вьщеления запросов следующего сигнала запроса от табло 22 вызьшает формирование последовательности сигналов (импульсов), аналогичной приведенной на фиг.7 (диаграммы 7... 12). На первом, втором, третьем и четвер- том выходах счетчика 20 растра курсора по приходу второго сигнала запро

са формируется код адреса 0002,, который поступает на адресные входы блока 21 памяти приращений координат и вызывает формирование на его выходах кода данных 01 Ц.

Так как матрица разложения курсора 5 3 точек, то, естественно, код данных 011j будет появляться при поступлении четыре перв ых сигналов запроса (диаграмма 4, фиг.7), а при поступлении пятого - на выходах должен сформироваться код данных 110, т.е. на третьем выходе блока 21 памяти приращений координат должен появиться импульс, уровень которого соответствует потенциалу нуля. Этот импульс поступает на вход сложения приращений координаты У, осуществляя ин- кримент содержимого этого счетчика. При поступлении шестого, седьмого, восьмого и девятого сигналов запроса на выходах блока 21 памяти приращений координат формируется код данных 1012, производя уменьшение (дискре- мент) содержимого счётчика 11 приращения координаты X, так как на вход вычитания этого счетчика с второго выхода блока 21 памяти приращений координат в этом случае поступает импульс полярности логического нуля. При поступлении десятого сигнала зз- про/са на выходах блока 21 памяти приращений координат формируется вновь код данных 110i производя тем самым инкремент содержимого счетчика 13 координаты У. И, наконец, при поступлении одиннадцатого, двенадцатого, три

0

0

5

5

0

5

Q

надцатого и четырнадцатого сигналов запроса от табло 22 на выходах блока 21 памяти приращений координат формируется код данных 011j, осуществляя инкремент содержимого счетчика 11 приращения координаты X. При поступлении четырнадцатого сигнала запроса от табло 22 на первом выходе регистра 19 управляющих сигналов (так же.как и при предццущих тринадцати) формируется счетньй импульс, по заднему фронту которого (точка Е на диаграмме 10, фиг.7) производится инкремент содержимого счетчика 20 растра курсора. В этом случае на адресные входы блока 21 памяти приращений координат поступит код 11102.

При поступлении пятнадцатого сигнала запроса по переднему фронту импульса, сформированного на первом выходе блока 18 вьвделения запросов (точка Ж на диаграмме 7, фиг.7), производится перезапись в регистр 16. режима кода режима, а в регистры 12 и 14 координат X и У координаты последней точки, составляющей ранее выведенный курсор. Таким образом, на экране табло 22 через, пятнадцать периодов сигнала запроса курсор полностью стирается. При поступлении на счетньй вход счетчика 20 растра курсора пятнадцатого импульса с первого выхода регистра 19 управляющих сигналов на пятом выходе счетчика 20 растра курсора формируется импульс (диаграмма 13, фиг.7), передний фронт которого через элемент НЕ 23, поступая на С-вход триггера 25, переводит этот триггер 25 в нулевое состояние. Потенциал логической единицы, появившийся в результате этого, осуществляет обнуление содержимого счетчика 20 растра курсора и блокирует выходи с блока 21 памяти приращений координат (наличие потенциала логической единицы на разрешающем входе этого блока) . В то же время появившийся на единичном выходе триггера 25 потен-. циал логического нуля (точка И на диаграмме 2, фиг.7) производит установку триггера 26 также в нулевое состояние, т.е. формирование на нулевом выходе этого триггера потенциала логической единицы. При этом на выходе элемента НЕ-И 28 (на первом выходе блока 18 выделения запросов) формируется потенциал логического нуля (точка И1 на диаграмме 7, фиг.7

0

5

на первом выходе регистра 19 управляющих сигналов (на выходе элемента И-НЕ 32) формируется потенциал .логической единицы (точка И2 на диаграмме 10, фиг.7). Сформировавшийся на выходе элемента И-НЕ 32 нарастающий фронт никаких изменений не производит, так как на установочный вход счетчика 20 растра курсора уже поступает (как отмечалось ранее) потенциал логической единицы.

Короткий импульс, сформированный на пятом выходе счетчика 20 растра курсора (диаграмма 13, фиг.7), через мультиплексор 6 поступает на единичный вход триггера 4, вызывая появление на его нулевом выходе сигнала, который вызьтает формирование на выходе элемента ИЛИ-НЕ 8 сигнала готовности, поступающего на вход микроэвм 9. Это означает, что устройство завершило текущую операцию (в данном слзгчае операцию стирания курсора) и может продолжать следующую (по .алго- ритму - операцию второго этапа вывода курсора).

Микроэвм 9 после начала выполнения устройством операции первого этапа, не дожидаясь ее завершения, начинает выполнение второго этапа. Но в этом случае устройство осуществляет останов микроЭВМ 9, переводя ее в состояние неготовности. Это осуществляется .следующим образом. До момента формирования на управляющем выходе микро- ЭВМ 9 сигнала на синхронизир-злощем выходе формируется сигнал, который при совпадении на элементе И-НЕ 10 с сигналом, формируемым на первом выходе блока 1 (которьй формируется в том случае, если на адресный вход этого блока поступает определенный код адреса от микроэвм 9), при совпадении с импульсом такто1вой частоты и при совпадении с одним из разрядов, формируемым на информационном выходе микроэвм 9 и подтверждающем состояние вывода информации с микроЭВМ 9, формирует на выходе элемента И-НЕ 10 сигнал, задний фронт которого совпадает с задним фронтом импульса тактовой частоты. Этот сигнал поступает на С-вход триггера 4, на информационный вход которого через мультиплексор 6 с первого выхода блока 18 вьщелеш}я запросов поступает потенциал логического нуля. Таким образом, по заднему фронту импульса, формируемого на вы

п

5 2о 5

JQ Q д „

35

5

ходе элемента И-НЕ 10, происходит установка триггера 4 в нулевое состояние, т.е. к формированию на его нулевом выходе потенциала логической единицы, который, поступая на вход элемента ИЛИ-НЕ 8, вызывает формирование на выходе этого элемента потенциала логического нуля, что приводит к переводу микроэвм 9 в состояние неготовности, т.е. к прекращению начатой операции, не завершая ее. Как отмечалось ранее, появление короткого импульса на пятом выходе счетчика 20 растра курсора приводит к восстановлению готовности микроэвм 9, и тем самым, к продолжению начатой ранее (до снятия готовности) операции. Появившийся на управляющем выходе микроэвм 9 сигнал (состояние разрядов адресного выхода микроЭВМ 9 при снятии готовности не изменяется) вызывает при совпадении с очередным импульсом тактовой частоты формирование на четвертом выходе блока 1 импульса, который поступает на вход записи буферного регистра 15 режима. В это время на информационный вход через шинный формирователь 2 данных с информационных выходов микроэвм 9 поступает код данных, старшие три разряда которого содержат информацию о режиме табло 22, а именно, режим Зажигание точки. Дальнейшее выполнение операций второго этапа полностью совпадает с выполнением операций первого этапа. Отличие заключается только в информационной части, т.е. значения координат X и У уже определяют новое местоположение курсора на экране табло 22, и вместо гашения точек, составляющих курсор, происходит их высвет.

Таким образом, данное устройство для сопряжения микроЭВМ и табло индикации осуществляет замену курсора при минимальном участии микроЭВМ 9 в этом процессе, что приводит к увеличению скорости обмена информацией.

Формула изобретения

режима, регистр координаты X, регистр координаты У, регистр режима, триггер, элемент И, элемент И-НЕ, элемент ИЛИ-НЕ, причем группа информационных входов шинного формирователя данньк образует группу входов устройства для подключения к группе информационных выходов микроэвм, первый вход элемента И-НЕ является входом Q устройства для подключения к синхро- входу микроэвм, выход элемента ИЛИ-НЕ является выходом устройства для подключения к входу готовности микроэвм, второй вход элемента И-НЕ соединен с г тактовыми входами блока управления, блока формирования символа и блока переноса координат и является входом устройства для подключения к тактовому выходу микроэвм, адресный вход и - -JQ целью повышения быстродействия, в невход ; логического условия блока управления являются входами устройства для подключения соответственно к адресному и управляющему выходу микроЭВМ, информационные выходы регистра координа- 25 элемент ИЛИ, при этом информационный ты X,регистра координаты У,регистра режима являются выходами устройства для подключения соответственно к первому, второму информационным входам и входу

режима работы табло индикации, первьй Q единены соответственно с шестым управляющий вход блока переноса координат соединен с входом управления коэффициентом пересчета блока формирования сиьшола и является входом устройства для подключения к зыходу запроса режима табло индикации, при этом первый выход блока управления соединен с третьим входомгэлемента И-НЕ, четвертый вход которого, информацитретий и четвертьй выходы которого соединены соответственно с входами сложения и вычитания счетчика приращения координаты У и с седьмым и восьмым выходами блока управления, девятый и десятый выходы которого соединены соответственно с входом записи и установочным входом блока формирования символа, пятый выход которого соединен с первь М входом элемента И и с вторым управляющим входом блока переноса координат, выход которого соединен с вторым входом элемента И и с первым входом элемента ИЛИ-НЕ, второй вход которого соединен с выходом триггера, синхровход которого соединен с выходом элемента И-НЕ, отличающееся тем, что, с

го введены мультиплексор, блок выделения запроса, регистр управляющих сигналов, счетчик растра курсора, блок памяти приращения координат.

35

и единичньй входы триггера соединены соответственно с первым и вторым выходами мультиплексора, первый и второй информационные входы которого сои

седьмым выходами блока формирования символа, тактовый вход которого соединен с тактовым входом регистра уп- равлякщих сигналов, первый выход которого соединен со счетным входом счетчика растра курсора, первый, второй, третий и четвертый выходы которого соединены с первым, вторым, третьим и четвертым адресными входами

онные входы блока формирования симво- .- блока памяти приращения координат.

ла, счетчика приращения координаты X, счетчика приращения координаты У, буферного регистра режима соединены с группой информационных выходов шиннопервый, второй и третий информацио ные выходы которого соединены соот ветственно с входами сложения и вы тания счетчика приращения координа

го формирователя данных, информацион- . X и с входом сложения счетчика прира50

ные входь регистра координаты X, регистра координаты У, регистра режима соединены соответственно с информационными выходами счетчика приращения координаты X, счетчика приращения координаты У, буферного регистра режИ а, входы записи которых соединены соответственно с вторым, третьим, четвертым выходами блока управления, пятый и шестой выходы которого соеди- ,нены соответственно с входами сложе- ния и вычитания счетчика приращения координаты X и с первым и вторым выходами блока формирования символа.

щения координаты У, входы записи регистра координаты X, регистра координаты У, регистра режима соединены с выходами элемента ИЛИ, первьй вход которого соединен с вторым выходом регистра управляющих сигналов, информационный вход которого соединен с первым выходом блока вьщеления запроса, тактовый вход которого соединен с первым управляклцим входом блока переноса координат, одиннадцатый вы- ход блока управление соединен с первым установочным вхоюм блока вьщеления запроса, второй ..гход которого соцелью повышения быстродействия, в неэлемент ИЛИ, при этом информационный

третий и четвертьй выходы которого соединены соответственно с входами сложения и вычитания счетчика приращения координаты У и с седьмым и восьмым выходами блока управления, девятый и десятый выходы которого соединены соответственно с входом записи и установочным входом блока формирования символа, пятый выход которого соединен с первь М входом элемента И и с вторым управляющим входом блока переноса координат, выход которого соединен с вторым входом элемента И и с первым входом элемента ИЛИ-НЕ, второй вход которого соединен с выходом триггера, синхровход которого соединен с выходом элемента И-НЕ, отличающееся тем, что, с

целью повышения быстродействия, в неэлемент ИЛИ, при этом информационный

го введены мультиплексор, блок выделения запроса, регистр управляющих сигналов, счетчик растра курсора, блок памяти приращения координат.

целью повышения быстродействия, в неэлемент ИЛИ, при этом информационный

единены соответственно с шестым

и единичньй входы триггера соединены соответственно с первым и вторым выходами мультиплексора, первый и второй информационные входы которого сои

седьмым выходами блока формирования символа, тактовый вход которого соединен с тактовым входом регистра уп- равлякщих сигналов, первый выход которого соединен со счетным входом счетчика растра курсора, первый, второй, третий и четвертый выходы которого соединены с первым, вторым, третьим и четвертым адресными входами

первый, второй и третий информационные выходы которого соединены соответственно с входами сложения и вычитания счетчика приращения координаты

0

щения координаты У, входы записи регистра координаты X, регистра координаты У, регистра режима соединены с выходами элемента ИЛИ, первьй вход которого соединен с вторым выходом регистра управляющих сигналов, информационный вход которого соединен с первым выходом блока вьщеления запроса, тактовый вход которого соединен с первым управляклцим входом блока переноса координат, одиннадцатый вы- ход блока управление соединен с первым установочным вхоюм блока вьщеле ния запроса, второй ..гход которого соединен с раэрешаннцим входом блока памяти приращения координат, с установочным входом счетчика растра курсора, с третьим информационным входом мультиплексора, четвертый информационный вход которого соединен с пятым выходом счетчика растра курсора и с вторым установочным входом блока выделения запроса, третий выход регистpa управляющих сигналов соединен с входом чтения блока памяти приращения координат, выход элемента И соединен с вторБм входом элемента ИЛИ.

19

Фиг.2

30

32

)-

31

Ф-

. J

«e.J

f

f

ffO

rj M L

Vf

ч r V U

Дгг.5

3

ляш

V

-ff

/А

TTLL-J

Фиг. 6

-//-//м

тr

rff

Авторы

Даты

1988-02-23—Публикация

1986-08-15—Подача