Изобретение относится к цифровой вычислительной т.ехнике и может быть использовано для контроля выполнения программ в цифровых вычислительных машинах и программируемых контрол- лерах, построенных по принципу общей магистрали.

Цель изобретения - повьшение достоверности контроля за ходом вьтол- нения программ.

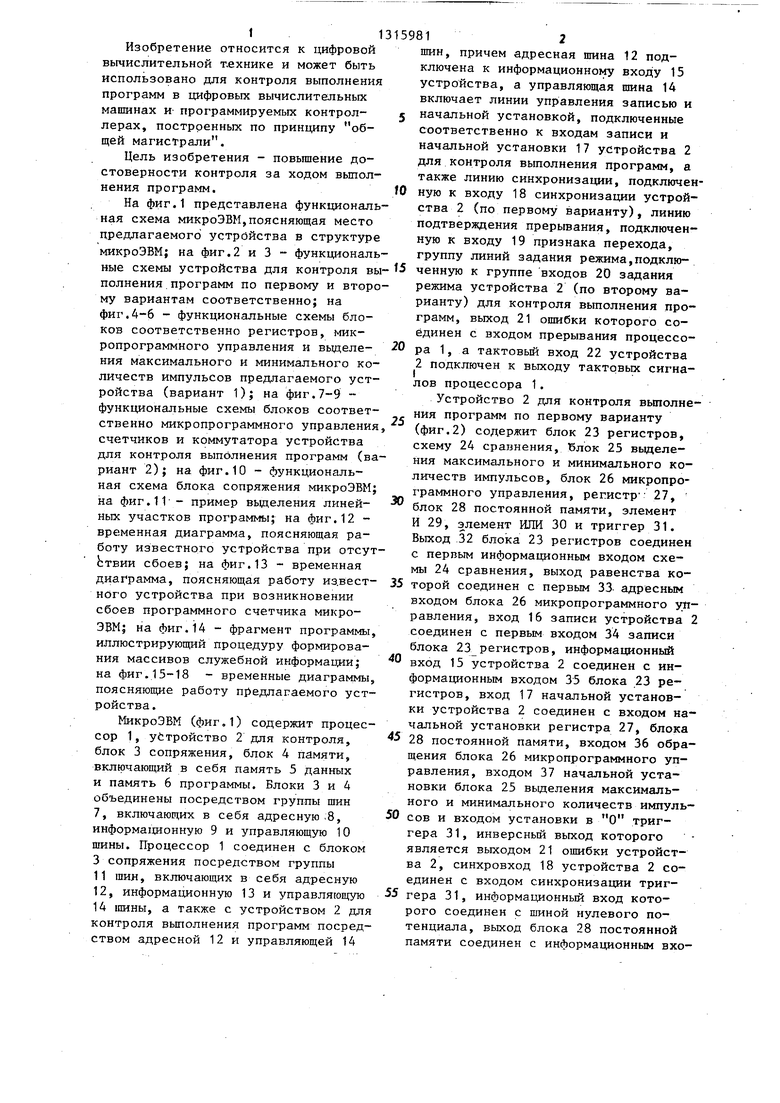

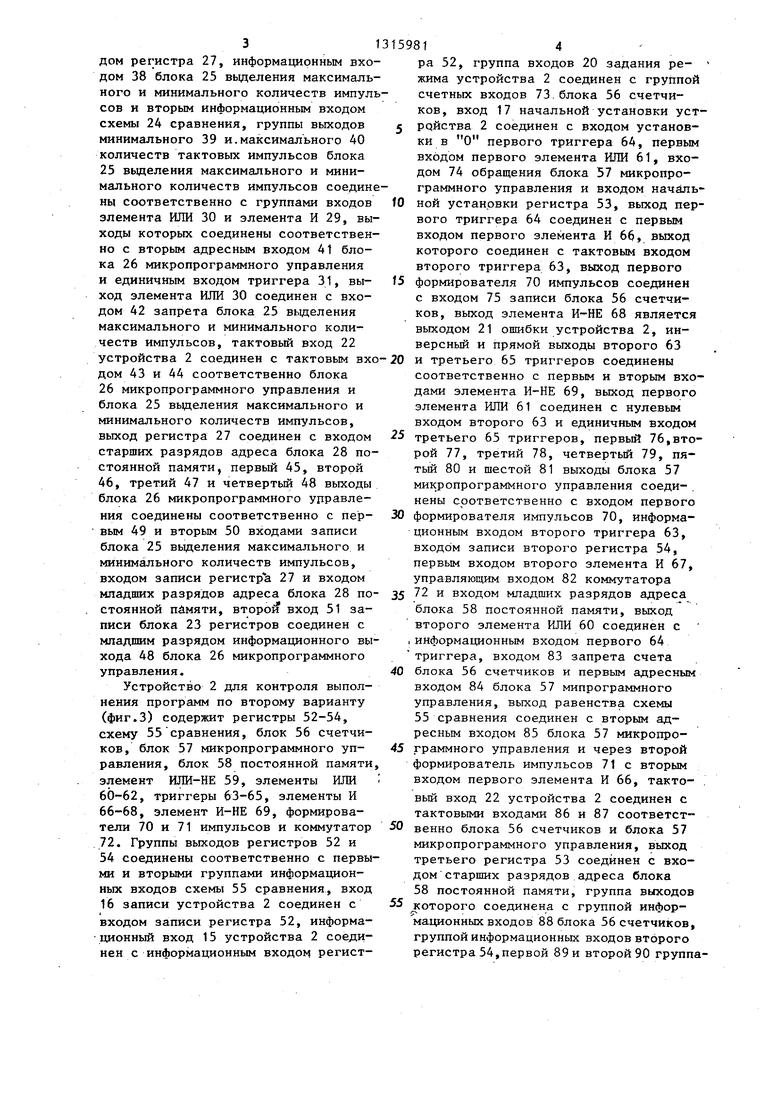

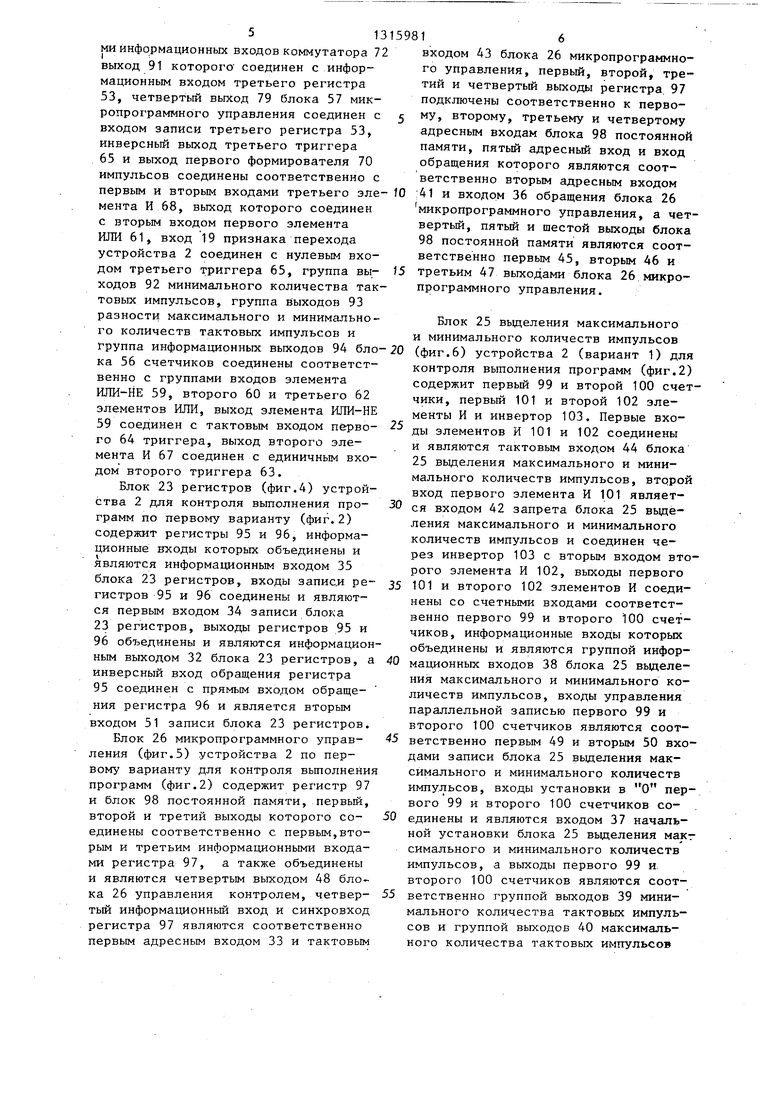

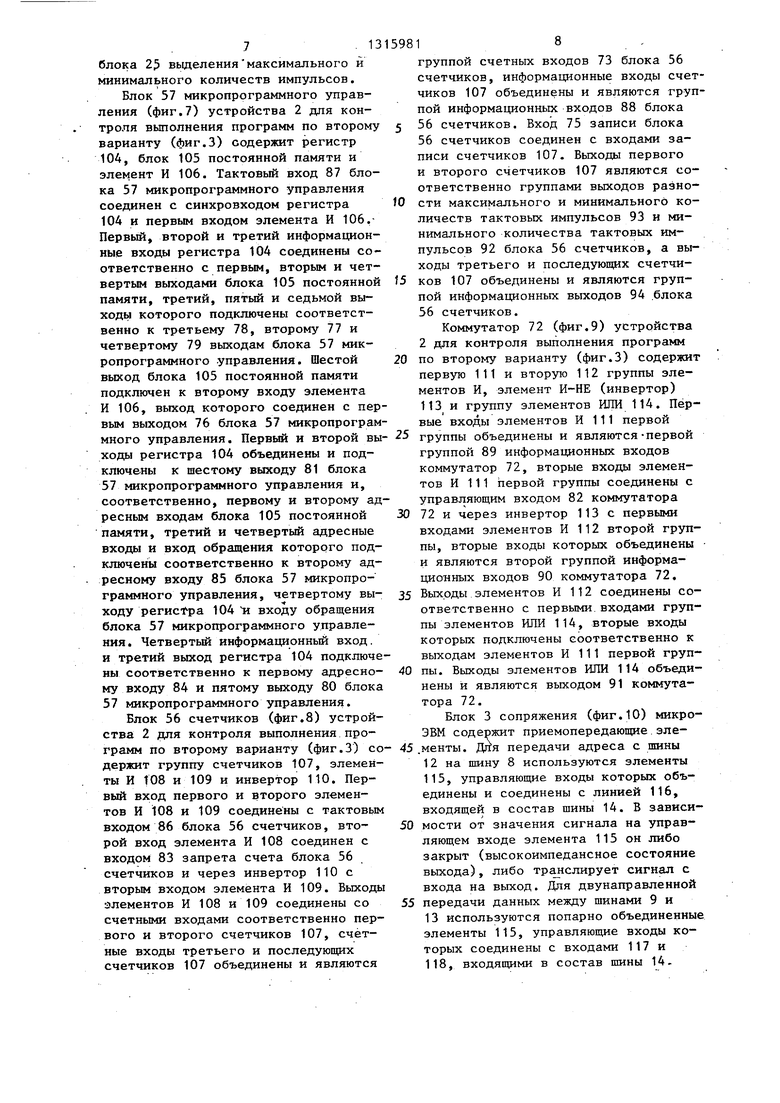

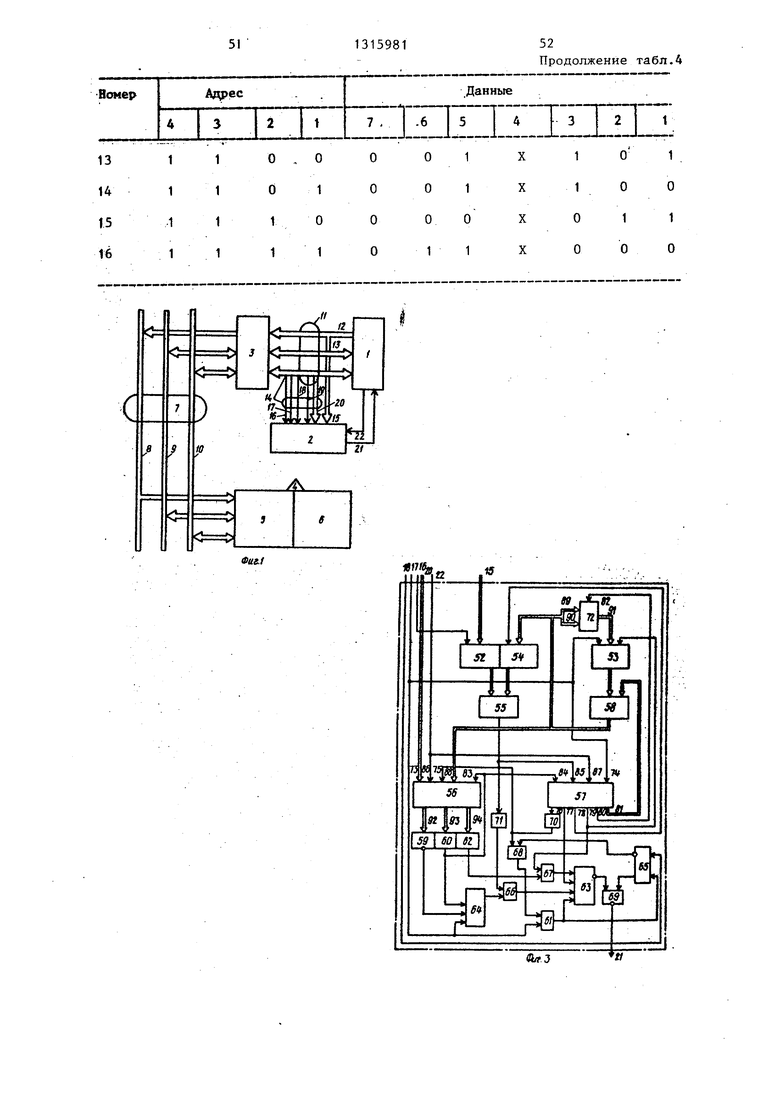

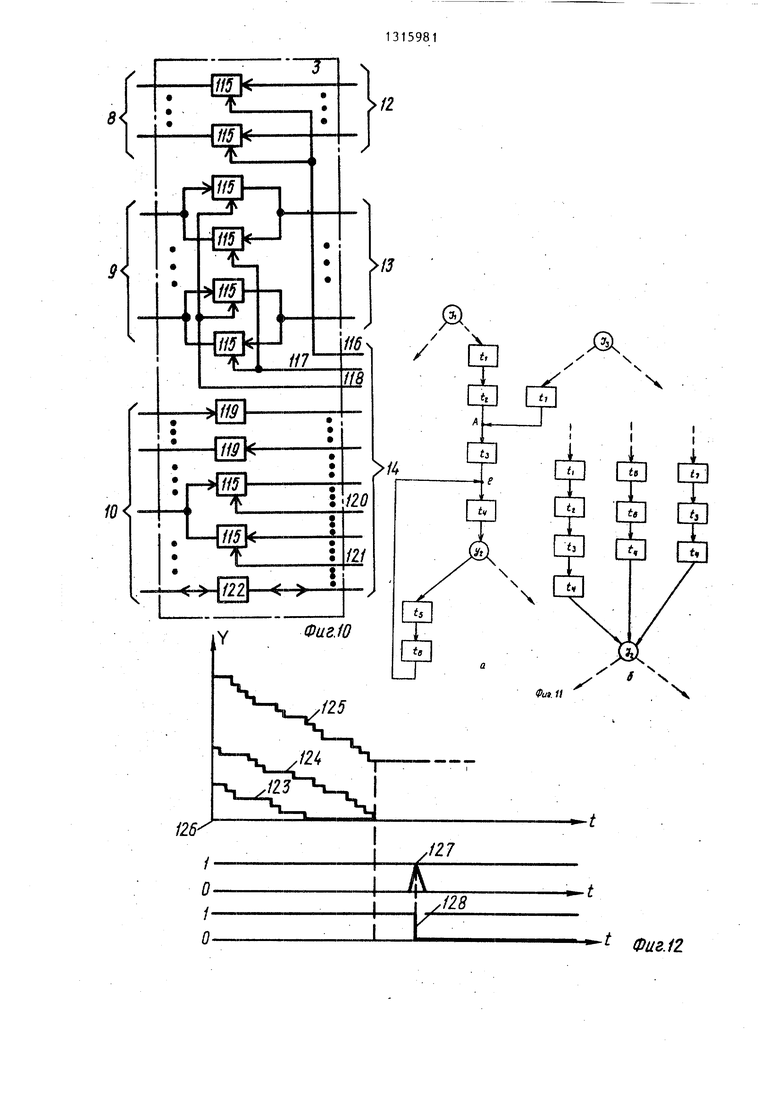

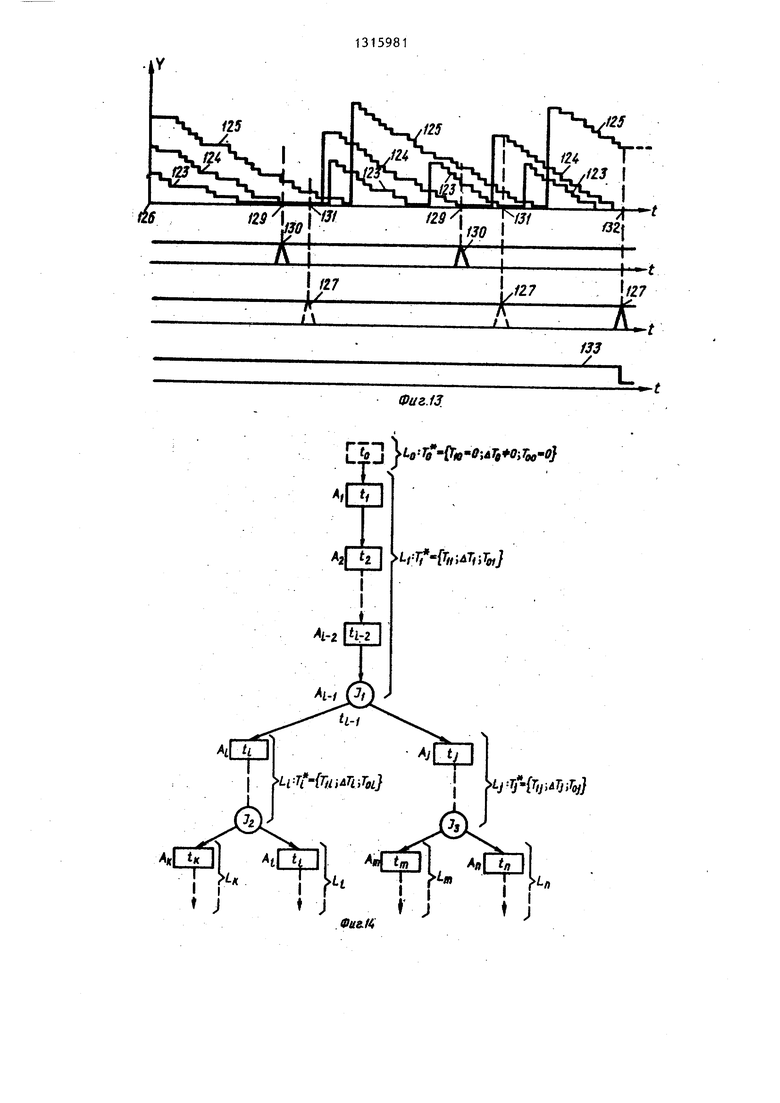

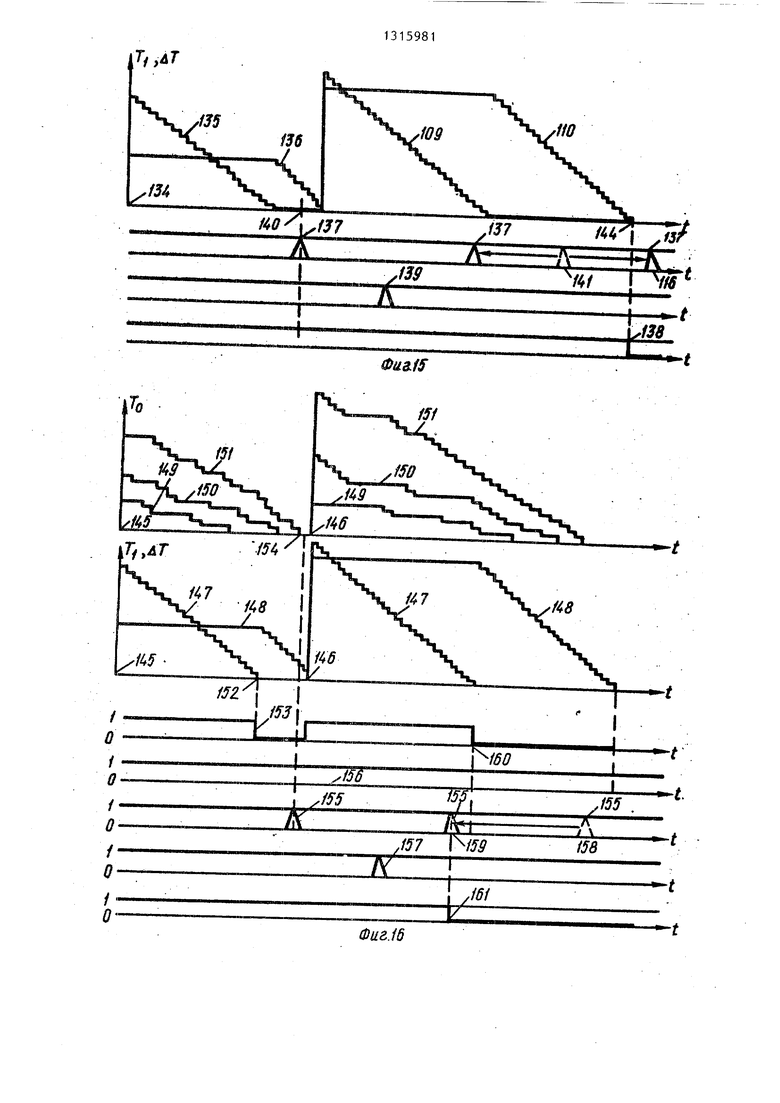

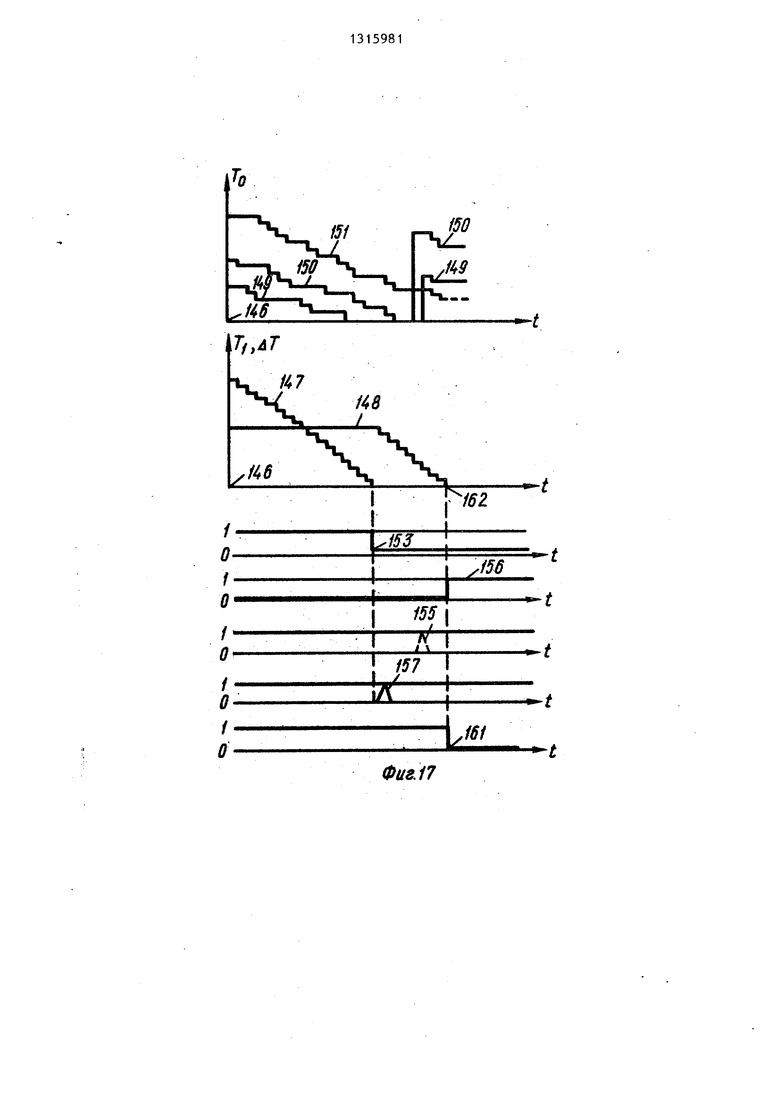

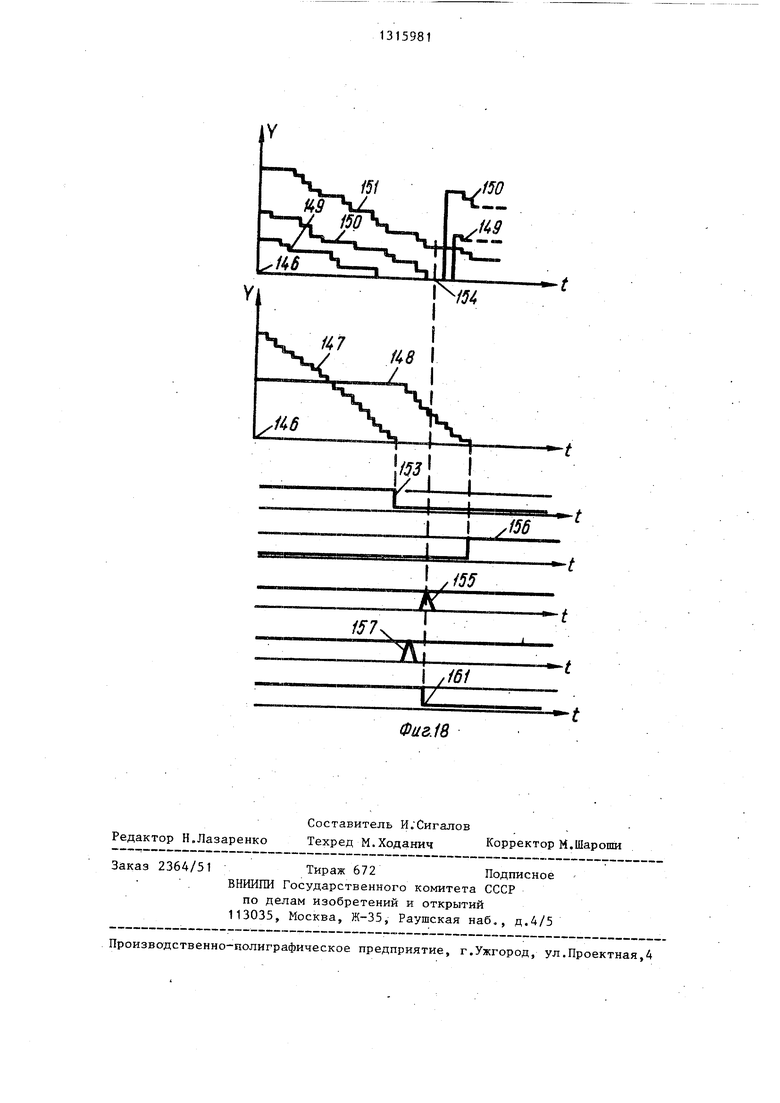

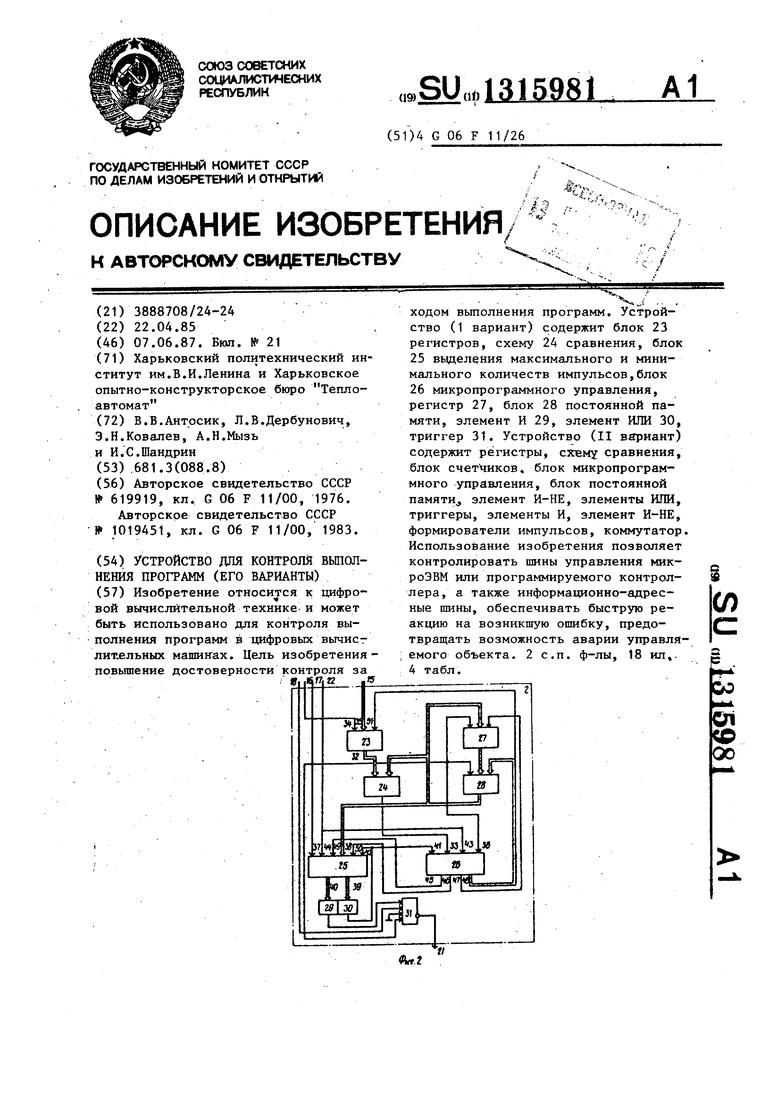

На фиг.1 представлена функциональная схема микроэвм,поясняющая место предлагаемого устрййства в структуре микроэвм; на фиг.2 и 3 функциональные схемы устройства для контроля вы полнения.программ по первому и второму вариантам соответственно; на фиг.4-6 - функциональные схемы блоков соответственно регистров, микропрограммного управления и выделе- ния максимального и минимального количеств импульсов предлагаемого устройства (вариант 1); на фиг.7-9 функциональные схемы блоков соответственно микропрограммного управления счетчиков и коммутатора устройства для контроля выполнения программ (вариант 2); на фиг.10 - функциональная схема блока сопряжения микроЭВМ; на фиг,11- пример выделения линей- ных участков программы; на фиг.12 - временная диаграмма, поясняющая работу известного устройства при отсут Ьтвии сбоев; на фиг.13 - временная диаграмма, поясняющая работу из.вест- ного устройства при возникновении сбоев программного счетчика микро- ЭВМ; на фиг.14 - фрагмент программы, иллюстрирующий процедуру формирования массивов служебной информации; на фиг.15-18 - временные диаграммы, поясняющие работу предлагаемого устройства.

Микроэвм (фиг,1) содержит процессор 1, устройство 2 для контроля, блок 3 сопряжения, блок 4 памяти, включающий в себя память 5 данных и память 6 программы. Блоки 3 и 4 объединены посредством группы пгин 7, включающих в себя адресную .8, информационную 9 и управляющую 10 шины. Процессор 1 соединен с блоком 3 сопряжения посредством группы 11 шин, включающих в себя адресную 12, информационную 13 и управляющую 14 юины, а также с устройством 2 для контроля выполнения программ посредством адресной 12 и управляющей 14

5

0 5

5

шин, причем адресная шина 12 подключена к информационному входу 15 устройства, а управляющая шина 14 включает линии управления записью и начальной установкой, подключенные соответственно к входам записи и начальной установки 17 устройства 2 для контроля выполнения программ, а также линию синхронизации, подключенную к входу 18 синхронизации устройства 2 (по первому варианту), линию подтверждения прерывания, подключенную к входу 19 признака перехода, группу линий задания режима,подключенную к группе входов 20 задания режима устройства 2 (по второму варианту) для контроля выполнения программ, выход 21 ошибки которого соединен с входом прерывания процессора 1, а тактовьй вход 22 устройства 2 подключен к выходу тактовых сигналов процессора 1.

Устройство 2 для контроля выполнения программ по первому варианту (фиг.2) содержит блок 23 регистров, схему 24 сравнения, Блок 25 выделения максимсшьного и минимального количеств импульсов, блок 26 микропрограммного управления, регистр 27, блок 28 постоянной памяти, элемент И 29, элемент ШШ 30 и триггер 31. Выход 32 блока 23 регистров соединен с первым информационным входом схе- 24 сравнения, выход равенства которой соединен с первым 33 адресным входом блока 26 микропрограммного управления, вход 16 записи устройства 2 соединен с первым входом 34 записи блока 23 регистров, информационный вход 15 устройства 2 соединен с информационным входом 35 блока 23 регистров, вход 17 начальной установки устройства 2 соединен с входом начальной установки регистра 27, блока 28 постоянной памяти, входом 36 обращения блока 26 микропрограммного управления, входом 37 начальной установки блока 25 выделения максимального и минимального количеств импульсов и входом установки в О триггера 31, инверсный выход которого является выходом 21 ошибки устройства 2, синхровход 18 устройства 2 соединен с входом синхронизации триггера 31, информационный вход которого соединен с шиной нулевого потенциала, выход блока 28 постоянной памяти соединен с информационным вхо3

дом регистра 27, информационным входом 38 блока 25 выделения максимального и минимального количеств импуль сов и вторым информационным входом схемы 24 сравнения, группы выходов минимального 39 и.максимального 40 количеств тактовых импульсов блока

25вьщеления максимального и минимального количеств импульсов соедине ны соответственно с группами входов элемента ИЛИ 30 и элемента И 29, выходы которых соединены соответственно с вторым адресным входом 41 блока 26 микропрограммного управления

и единичным входом триггера 31, выход элемента ИЛИ 30 соединен с входом 42 запрета блока 25 выделения максимального и минимального количеств импульсов, тактовый вход 22 устройства 2 соединен с тактовым вхо дом 43 и 44 соответственно блока

26микропрограммного управления и блока 25 выделения максимального и минимального количеств импульсов, выход регистра 27 соединен с входом старших разрядов адреса блока 28 постоянной памяти, первый 45, второй 46, третий 47 и четвертьш 48 выходы блока 26 микропрограммного управления соединены соответственно с первым 49 и вторым 50 входами записи блока 25 вьщеления максимального и минимального количеств импульсов, входом записи регистр а 27 и входом младших разрядов адреса блока 28 постоянной пймяти, второй вход 51 записи блока 23 регистров соединен с младшим разрядом информационного выхода 48 блока 26 микропрограммного управления.

Устройство 2 для контроля выполнения программ по второму варианту (фиг.З) содержит регистры 52-54, схему 55 сравнения, блок 56 счетчиков, блок 57 микропрограммного управления, блок 58 постоянной памяти элемент ИЛИ-НЕ 59, элементы ИЛИ 60-62, триггеры 63-65, элементы И 66-68, элемент И-НЕ 69, формирователи 70 и 71 импульсов и коммутатор 72. Группы выходов регистров 52 и 54 соединены соответственно с первыми и вторыми группами информационных входов схемы 55 сравнения, вход 16 записи устройства 2 соединен с входом записи регистра 52, информационный вход 15 устройства 2 соединен с информационным входом регист

159814

ра 52, группа входов 20 задания ре- жима устройства 2 соединен с группой счетных входов 73.блока 56 счетчиков, вход 17 начальной установки уст5 ройства 2 соединен с входом установки в О первого триггера 64, первым входом первого элемента ИЛИ 61, входом 74 обращения блока 57 микропро- граммного управления и входом начальfO ной установки регистра 53, выход первого триггера 64 соединен с первым входом первого элемента И 66 выход которого соединен с тактовым входом второго триггера 63, выход первого

15 формирователя 70 импульсов соединен с входом 75 записи блока 56 счетчиков, выход элемента И-НЕ 68 является выходом 21 опшбки устройства 2, инверсный и прямой выходы второго 63 20 и третьего 65 триггеров соединены

соответственно с первым и вторым входами элемента И-НЕ 69, выход первого элемента ИЛИ 61 соединен с нулевым входом второго 63 и единичным входом

25 третьего 65 триггеров, первый 76,второй 77, третий 78, четвертый 79, пятый 80 и шестой 81 выходы блока 57 микропрограммного управления соединены соответственно с входом первого

30 формирователя импульсов 70, информа- ционньм входом второго триггера 63, входом записи второго регистра 54, первым входом второго элемента И 67, управляющим входом 82 коммутатора

35 72 и входом младших разрядов адреса блока 58 постоянной памяти, выход второго элемента ИЛИ 60 соединен с , информационным входом первого 64 триггера, входом 83 запрета счета

40 блока 56 счетчиков и первым адресным входом 84 блока 57 мипрограммного управления, выход равенства схемы 55 сравнения соединен с вторым адресным входом 85 блока 57 микропро45 граммного управления и через второй формирователь импульсов 71 с вторым входом первого элемента И 66, такто- . вый вход 22 устройства 2 соединен с тактовыми входами 86 и 87 соответст50 венно блока 56 счетчиков и блока 57 микропрограммного управления, выход третьего регистра 53 соединен с входом старших разрядов адреса блока 58 постоянной памяти, группа выходов

55 которого соединена с группой информационных входов 88 блока 56 счетчиков, группой информационных входов второго регистра 54,первой 89 и второй 90 группа513

ми информационных входов коммутатора 7 выход 91 которого соединен с информационным входом третьего регистра 53, четвертый выход 79 блока 57 микропрограммного управления соединен с входом записи третьего регистра 53, инверсный выход третьего триггера 65 и выход первого формирователя 70 импульсов соединены соответственно с первым и вторым входами третьего элемента И 68, выход которого соединен с вторым входом первого элемента ИЛИ 61, вход 19 признака перехода устройства 2 соединен с нулевьм входом третьего триггера 65, группа выходов 92 минимального количества тактовых импульсов, группа выходов 93 разности максимального и минимального количеств тактовых импульсов и группа информационньш выходов 94 блока 56 счетчиков соединены соответственно с группами входов элемента ШТИ-НЕ 59, второго 60 и третьего 62 элементов ИЛИ, выход элемента ИЛИ-НЕ 59 соединен с тактовым входом первого 64 триггера, выход второго элемента И 67 соединен с единичным входом второго триггера 63.

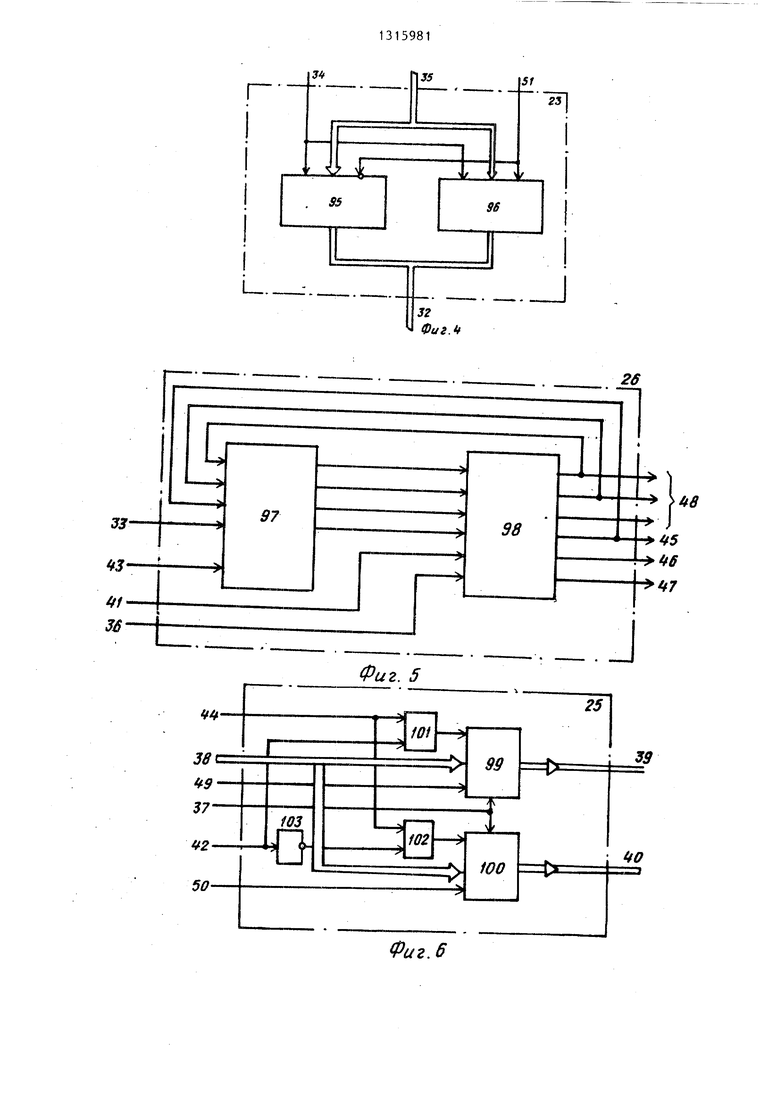

Блок 23 регистров (фиг.4) устройства 2 для контроля выполнения программ по первому варианту (фиг.2) содержит регистры 95 и 96, информационные входы которых объединены и Являются информационным входом 35 блока 23 регистров, входы запис.и регистров 95 и 96 соединены и являются первым входом 34 записи блока 23 регистров, выходы регистров 95 и 96 объединены и являются информационным выходом 32 блока 23 регистров, а инверсный вход обращения регистра 95 соединен с прямым входом обращения регистра 96 и является вторым входом 51 записи блока 23 регистров.

Блок 26 микропрограммного управления (фиг.5) устройства 2 по первому варианту для контроля вьтолнения программ (фиг.2) содержит регистр 97 и блок 98 постоянной памяти, первый, второй и третий выходы которого соединены соответственно с первым,вторым и третьим информационными входами регистра 97, а также объединены и являются четвертым выходом 48 блока 26 управления контролем, четвертый информационный вход и синхровход регистра 97 являются соответственно первым адресным входом 33 и тактовым

16

входом 43 блока 26 микропрограммного управления, первый, второй, третий и четвертый выходы регистра. 97 подключены соответственно к первому, второму, третьему и четвертому адресным входам блока 98 постоянной памяти, пятый адресный вход и вход обращения которого являются соответственно вторым адресным входом

:41 и входом 36 обращения блока 26 микропрограммного управления, а чет- вертьш, пятый и шестой выходы блока 98 постоянной памяти являются соответственно первым 45, вторым 46 и

третьим 47 выходами блока 26 микропрограммного управления.

Блок 25 выделения максимального и минимального количеств импульсов

(фиг.6) устройства 2 (вариант 1) для контроля выполнения программ (фиг.2) содержит первый 99 и второй 100 счетчики, первый 101 и второй 102 элементы И и инвертор 103. Первые вхо

ды элементов И 101 и 102 соединены

и являются тактовьм входом 44 блока 25 вьщеления максимального и минимального количеств импульсов, второй вход первого элемента И 101 является входом 42 запрета блока 25 выделения максимального и минимального количеств импульсов и соединен через инвертор 103 с вторым входом второго элемента И 102, выходы первого

101 и второго 102 элементов И соединены со счетными входами соответственно первого 99 и второго 100 счетчиков, информационные входы которых объединены и являются группой информационных входов 38 блока 25 вьщеления максимального и минимального количеств импульсов, входы управления параллельной записью первого 99 и второго 100 счетчиков являются соответственно первым 49 и вторым 50 входами записи блока 25 выделения максимального и минимального количеств импульсов, входы установки в О первого 99 и второго 100 счетчиков со- единены и являются входом 37 начальной установки блока 25 выделения макт симального и минимального количеств импульсов, а выходы первого 99 и второго 100 счетчиков являются соот- ветственно группой выходов 39 минимального количества тактовых импульсов и группой выходов 40 максимального количества тактовых импульсов

.7. 13

блока 25 выделения максимального и минимального количеств импульсов.

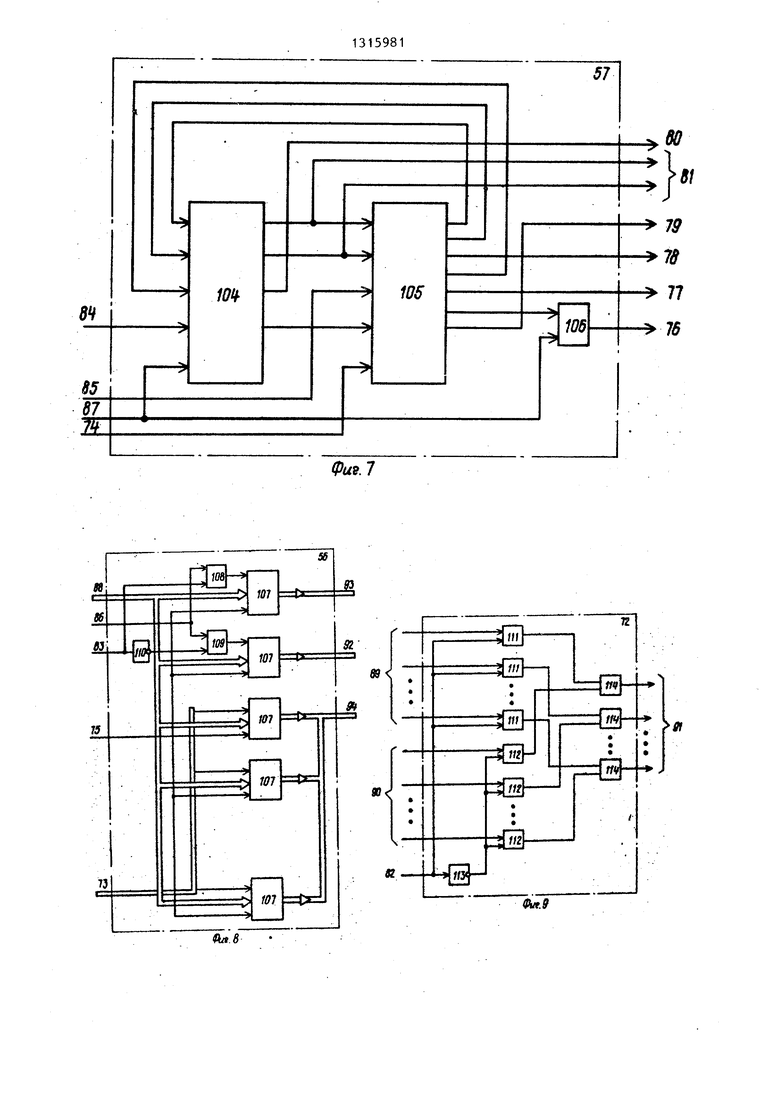

Блок 57 микропрограммного управления (фиг.7) устройства 2 для контроля вьтолнения программ по второму варианту (фиг.З) содержит регистр 104, блок 105 постоянной памяти и элемент И 106. Тактовый вход 87 блока 57 микропрограммного управления соединен с синхровходом регистра 104 и первым входом элемента И 106,- Первый, второй и третий информационные входы регистра 104 соединены соответственно с первым, вторым и четвертым выходами блока 105 постоянной памяти, третий, пятый и седьмой выходы которого подключены соответственно к третьему 78, второму 77 и четвертому 79 выходам блока 57 микропрограммного управления. Шестой выход блока 105 постоянной памяти подключен к второму входу элемента И 106, выход которого соединен с первым выходом 76 блока 57 микропрограммного управления. Первый и второй выходы регистра 104 объединены и подключены к шестому выходу 81 блока 57 микропрограммного управления и, соответственно, первому и второму адресным входам блока 105 постоянной памяти, третий и четвертый адресные входы и вход обращения которого подключены соответственно к второму адресному входу 85 блока 57 микропрограммного управления, четвертому выходу регист ра 104 и входу обращения блока 57 микропрограммного управления. Четвертый информационный вход. и третий выход регистра 104 подключены соответственно к первому адресному входу 84 и пятому выходу 80 блока 57 микропрограммного управления.

Блок 56 счетчиков (фиг.8) устройства 2 для контроля выполнения программ по второму варианту (фиг.З) содержит группу счетчиков 107, элементы И 108 и 109 и инвертор 110. Первый вход первого и второго элементов И 108 и 109 соединены с тактовьм входом 86 блока 56 счетчиков, второй вход элемента И 108 соединен с входом 83 запрета счета блока 56 счетчиков и через инвертор 110 с вторым входом элемента И 109. Выходы элементов И 108 и 109 соединены со счетными входами соответственно первого и второго счетчиков 107, счётные входы третьего и последующих счетчиков 107 объединены и являются

18

группой счетных входов 73 блока 56 счетчиков, информационные входы счетчиков 107 объединены и являются группой информационных входов 88 блока

56 счетчиков. Вход 75 записи блока 56 счетчиков соединен с входами записи счетчиков 107. Выходы первого и второго счетчиков 107 являются соответственно группами выходов разности максимального и минимального количеств тактовых импульсов 93 и минимального количества тактовых импульсов 92 блока 56 счетчиков, а выходы третьего и последующих счетчиков 107 объединены и являются группой информационных выходов 94 блока 56 счетчиков.

Коммутатор 72 (фиг.9) устройства 2 для контроля выполнения программ

по второму варианту (фиг.З) содержит первую 111 и вторую 112 группы элементов И, элемент И-НЕ (инвертор) 113 и группу элементов ИЛИ 114. Первые входы элементов И 111 первой

группы объединены и являются-первой группой 89 информационных входов коммутатор 72, вторые входы элементов И 111 первой группы соединены с управляющим входом 82 коммутатора

72 и через инвертор 113 с первыми входами элементов И 112 второй группы, вторые входы которых объединены и являются второй группой информационных входов 90 коммутатора 72.

Выходы элементов И 112 соединены соответственно с первыми, входами группы элементов ИЛИ 114, вторые входы которых подключены соответственно к выходам элементов И 111 первой группы. Выходы элементов ИЛИ 114 объединены и являются выходом 91 коммутатора 72.

Блок 3 сопряжения (фиг.10) микро- ЭВМ содержит приемопередающие.эле-

.менты. Д1ТЯ передачи адреса с шины

12на шину В используются элементы 115, управляющие входы которых объединены и соединены с линией 116, входящей в состав шины 14. В зависимости от значения сигнала на управляющем входе элемента 115 он либо закрыт (высокоимпедансное состояние выхода), либо тра11слирует сигнал с входа на выход. Для двунаправленной

передачи данных между шинами 9 и

13используются попарно объединенные элементы 115, управляющие входы которых соединены с входами 117 и 118, входящими в состав шины 14.

913

В зависимости от значений сигналов на входах 117 и 118 выбирается то или иное направление передачи данных. Для сопряжения шины 10 с шиной 14 используются элементы разных ти-- нов: кабельные усилители 119 (без управления), элементы 115, управление которыми производится по линиям 120 и 121, а также асинхронные самоуправляемые двунаправленные элементы 122, выполненные на стандартных логических элементах.

Любую программу, записанную в машинных кодах в памяти микроЭВМ, можно представить в виде набора линей- ных участков, связанных между собой командами передачи управления по условию. Команда перехода по условию является завершающей командой линейного участка, если это не последний линейный участок программы - в этом случае линейный участок может завершаться, например, командой Останов Начальной командой линейного участка может быть либо команда, являю- щаяся внешним входом программы, либо команда, на которую производится передача управления одной из команд перехода по условию. Если некоторый фрагмент программы (фиг.11 а) содержи линейный участок (t - I,, , где 1 - команды перехода по условрпо; t - прочие команды микроЭВМ) с несколькими точками вхождения (А и В), он может быть представлен в виде линей- ных участков, каждый иэ которых имеет одну начальную команду (t , t., t), включает общие команды ветвей фрагмента (t,,, t.) и общую конечную

/

команду условного перехода (Ij) (фиг.116).

Таким образом, любую программу можно разбить на отдельные линейные участки, на которых поведение ЭВМ строго детерминировано в том смысле, что при правильном прохождении микроэвм через данный линейный учас- ток программы должно быть зарегистрировано определенное число (в заданном интервале Т - Т) тактовых импульсов и строго определенное число Tj, импульсов на интерфейсных управляющих линиях, которое известно для каждого линейного участка еще до начала работы микроЭВМ по про- грамме.

Наличие интервала Т - Т, объясняется широким использованием в управляющих микроэвм режима Ожидание 110

Совокупность интерфейсных управляку- щих сигналов, которыми сопровождается выполнение команд условных переходов, не зависит от того, вьтолне- но ли проверяемое условие или нет.

Любому линейному участку программы соответствует свой вектор перехода В { А|, А- J - пара адресов Aj, А: начальных команд линейных участков, на которые передается управление конечной командой условного перехода данного линейного участка.

Основную идею работы устройства для контроля выполнения программ микроэвм или программируемого контроллера можно выразить следующим образом.

После (или в процессе) трансляции исходной программы на язык машинных команд рабочую программу анализируют с целью выявления всех линейных участков. Список адресов начальных команд линейных участков запоминают .

Для каждого линейного участка предсказывают): минимальное Т и максимальное Т числа тактовых импульсов, характеризующих прохождение данного линейного участка программы; число TO импульсов на тех или иных управляющих линиях, которое находят путем последовательного арифметического сложения некоторых констант, каждая из которых соответствует своей команде и зависит от конструктивных особенностей конкретной микроэвм (для второго варианта); вектор перехода данного участка, определяющий пару адресов А,, А-, появление которых ожидается в момент окончания прохождения данного линейного участка Программы.

Эту информацию заносят в блок постоянной памяти и в дальнейшем в процессе функплонирования устройства она используется для контроля прохождения линейного участка при выходе на его начало.

Кроме того, производят пуск рабочей программ1з1. Правильность ее выполнения контролируется специальными аппаратными средствами. Одновременно с выбором из основной памяти начальной- команды некоторого линейного участка программы из блока постоянной памяти устройства контроля выполнения прог рамм микроэвм извлекается служебная информация, определяющая ожидаемые минимальное число Т,

1113

тактовьрс импульсов, разность jT Т. Т между максимальным и минимальным числами тактовых импульсов, число 1д импульсов на интерфейсных линиях управления (для второго варианта) и вектор В {A,,A-Z перехода этого линейного участка. Множество Т {т,, 4Т ; (Т Т, ЛТ, Тр) будем называть характеристическим множеством линейного участка. Эта информация помещается в счетчики, содержимое которых в дальнейшем уменьшается по мере прохождения данного участка программы, т.е. по мере передачи импульсных сигналов тактовой и интерфейсными линия- ,ми. По приходу Т тактовых импуль- сов устройство контроля начинает отсчет лТ и проверку на равенство

нулю содержимого счетчиков Т. Если это условие вьшолнено, т.е. микроЭВМ достигла начальной команды нового линейного участка, происходит сравнение вектора перехода и текущего адреса А программы, и если текущий адрес AI оказался равным одному из ожидаемых адресов А. или А- вектора В, счетчики загружаются новой информацией, соответствующей новому линейному участку программы..

Затем устройство 2 для контроля выполнения программ по первому варианту (фиг.2) посылает сигнал прерывания в процессор если при получении Tj тактовых импульсов процессор не перешел к вьшолнению одного из линейных участков, начальные адреса которых указаны в векторе перехода этого участка. Сигнал прерывания анализируется процессором и вызывает переход на заранее запланированный режим управления объектом, подключенным к микроэвм, после чего устройство 2 устанавливается в исходное состояние и микроЭВМ начинает выполнение программы с нулевого адреса.

При этом устройство 2 для контроля вьшолнения программ (второй вариант, фиг.З) посыпает сигнал прерывания в процессор при вьшолнении следующих условий: если в результате сбоя или неисправности процессор переходит к вьшолнению команды, адрес которой указан в векторе перехода данного линейного участка, до получения Т импульсов; если при получении Т. тактовых импульсов процессор

598112

не перешел к выполнению очередного линейного участка программы; если в интервале между Т. и Т импульсов получен адрес начальной команды сле- 5 дующего линейного участка программы и не произошло обнуление содержимого счетчиков Тд.

Сигнал прерывания анализируется процессором и либо вызывает переход

10 на заранее запланированный режим управления объектом, подключенным к микроэвм, либо процессор разрешает дальнейшую работу и происходит самосинхронизация устройства контроля и

15 микроэвм.

образом, существенно уменьшается вероятность появления аварий- ньк ситуаций, которые могут возникнуть в управляемом объекте в резуль0 тате беспорядочного блуждания микроЭВМ по рабочей программе, минуя операторы условной передачи управления (выполняя ошибочные переходы) вследствие сбоя или отказа,

5 Работа известного устройства в отсутствие и при возникновении указанных сбоев поясняется временными диаграммами (соответственно фиг.12 и 13).,

0 Эпюры 123-125 (фиг.12) отображают процесс загрузки (момент 126 времени) и постепенного уменьшения содержимого трех счетчиков. ИмпуЛьс 127 формируется в момент несовпа5 дения содержимого ячейки памяти программ и ячейки дополнительного блока памяти.

При обнаружении ошибки сигнал на выходе устройства принимает нулевое

0 значение (эпюра 128).

Эпюры 123-125 (фиг.13) также отображают процесс загрузки (момент 126 времени) и постепенного уменьшения содержимого трех счетчиков.Пред5 положим, что в моменты 129 времени программа непредвиденного дважды изменила свой ход и выполнила ошибочные Переходы к последующим линейным участкам, минуя начальные коман0 ды этих участков вследствие воздействия помехи (эпюра 130). При этом в известном устройстве не формируются импульсы 127 (показаны пунктиром) в моменты 131 ожидаемого завершения ли5 нейных участков. На отрезке времени 126-132 один из счетчиков (эпюра 123) переполняется три раза, а два другие (эпюры 124 и 125) - дважды.

131

Импульс 127 несовпадения и сигнал прерывания (эпюра 133) формируются только в момент 132 времени при выходе ЭВМ на начало четвертого (с момента 126 времени) линейного участка. Из этого .следует, что время между возникновением сбоя, приводящего к обходу начальной вершины очередного линейного участка, и его обнаружением в известном устройстве может превысить время прохождения линейного участка в случае накопления подобных сбоев, связанных с производственными помеха-ми, может оказаться достаточно большим (соизмеримым с временем срабатьшания исполнительного механизма управления объектом).

В результате сбоев в программном счетчике, линии связи, согласующем блоке и т.п. процессор вместо очередной команды линейного участка программы может перейти к выполнению команды ошибочного останова. При этом в известном устройстве формирование импульсов 127 прекращается и сигнал прерывания в процессор в дальнейшем не поступает, что в ряде случаев недопустимо.

Время между возникновением сбоя и его обнаружением в предлагаемом ус тройстве не превышает длительности прохождения линейного участка про- граммы, что позволяет организовать с воевременную реакцию устройства управления в случае аварийной ситуации.

Память 6 программ микроЭВМ, как правило, вьтолняется в виде постоянного или полупостоянного запоминающего устройства. Вводимая в память 6 программа представлена в виде последовательности машинных кодов. Ее ввод в память 6 должен сопровождаться вводом заранее подготовленного массива вспомогательной информации в блок 28 (58) постоянной памяти устройства 2 для контроля выполнения программ микроэвм.

Процедура подготовки массива вспомогательной информации выполняется следуюпщм образом.

Преобразовывают рабочую программу занесенную в память 6 микроЭВМ, выделяя линейные участки, как показано на фиг.11 а, б и определяют характеристические множества Т fT, ЛТ , (Т Т, ЛТ, Т) для каждого полученного линейного участка. На фиг. 14 показан пример фрагмента про598114

граммы, разделенного на линейные участки L..

При этом необходимо ввести в блок 28 постоянной памяти устройства 2 для

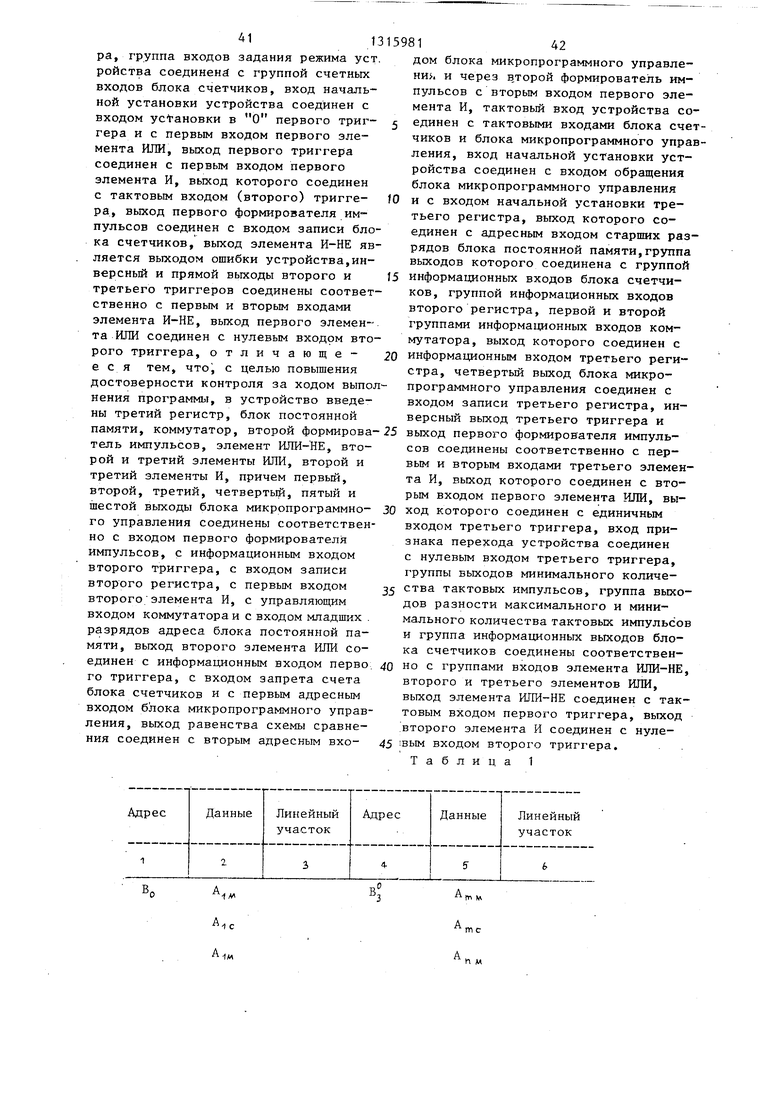

5 контроля выполнения программ (первый вариант, фиг.2) вспомогательную информацию о линейном участке рабочей программы, информацию о любом линейном участке L. разместить в восьми ячейках блока 28 постоянной памяти (табл.1), а в ячейки с адресами в и в + 1 ввести первый адрес А,- вектора перехода, т.е. соответственно младщую AJ „ и старшую части

15 адреса А; начальной команды первого из двух линейных участков, на которые передается управление завершающей командой J данного линейного участка. В ячейки с адресами в + 2 и

0 В + 3 вводят второй адрес А. вектора перехода., т.е. соответственно младшую А , и старшую А j части адреса А; начальной команды второго из двух линейных участков, на которые

5 передается управление завершающей командой J данного линейного участка. В ячейки с адресами В + 3 и В° + 5 вводят соответственно адреса двух ячеек блока 28 постоянной памя0 ти, в которых хранятся первые элементы массивов вспомогательной информации линейных: участков, на которые передается управление командой J (В

В-г В°; В; В°; В

В

f

35 В В-, ; В° и т.д.). В ячейку с адресом В + 6 вводят ожидаемое минимальное число Т тактовых импуЛь- сов, а в ячейку с адресом В + 7 - разность 4Т Т - Т между макси0 мальным и минимальным числами тактовых импульсов для данного линейного участка Lj.

В первые восемь ячеек блока 28 постоянной памяти вводят служебную

5 информацию, служащую для установки в исходное состояние устройства 2 для контроля выполнения программ. В первую и вторую пары ячеек вводят начальный адрес А программы так,

0 что в первой ячейке каждой пары мож- но расположить младшую часть А , а во второй - старшую часть А . начального адреса А программы. В пятую и шестую ячейки вводят адрес

5 В ячейки 28 постоянной памяти,хранящей первый элемент массива вспомогательной информации начального линейного участка программы. В седьмую и восьмую ячейки блока 28 по15131

стоянно.й памяти вводят соответственно установочные числа импульсов Т,р 0 и 4Тр О, Это необходимо для обеспечения начальной синхронизации устройства 2 контроля с работой микроэвм.

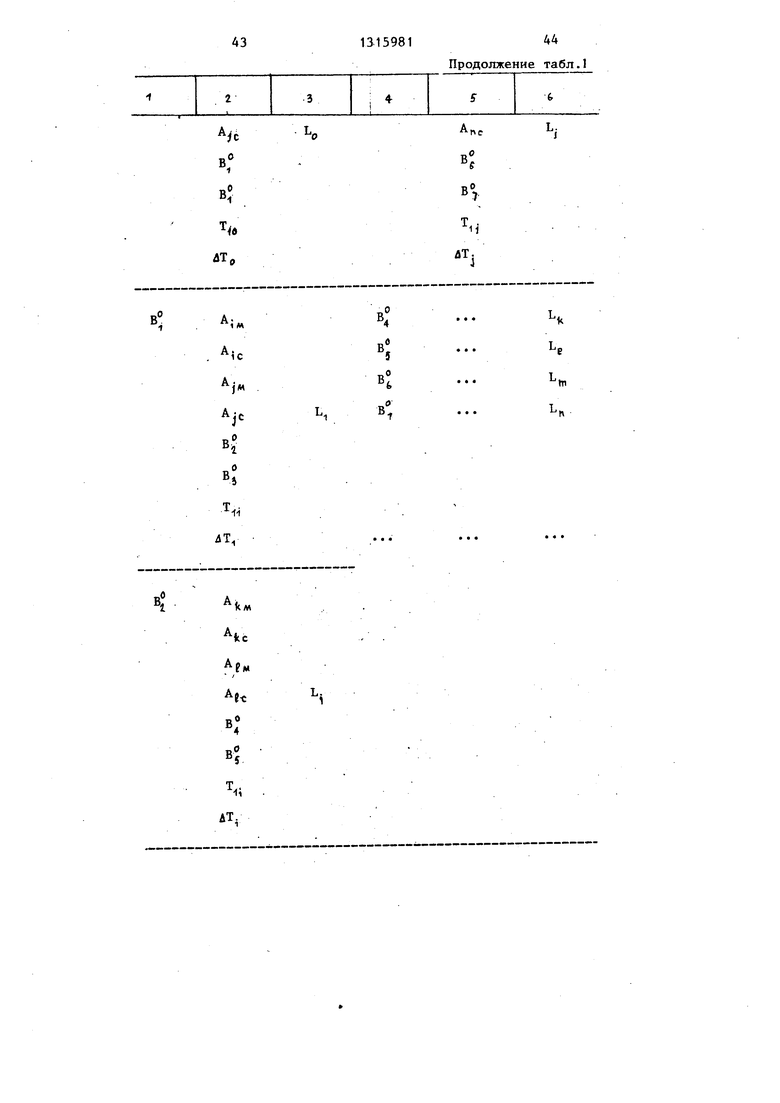

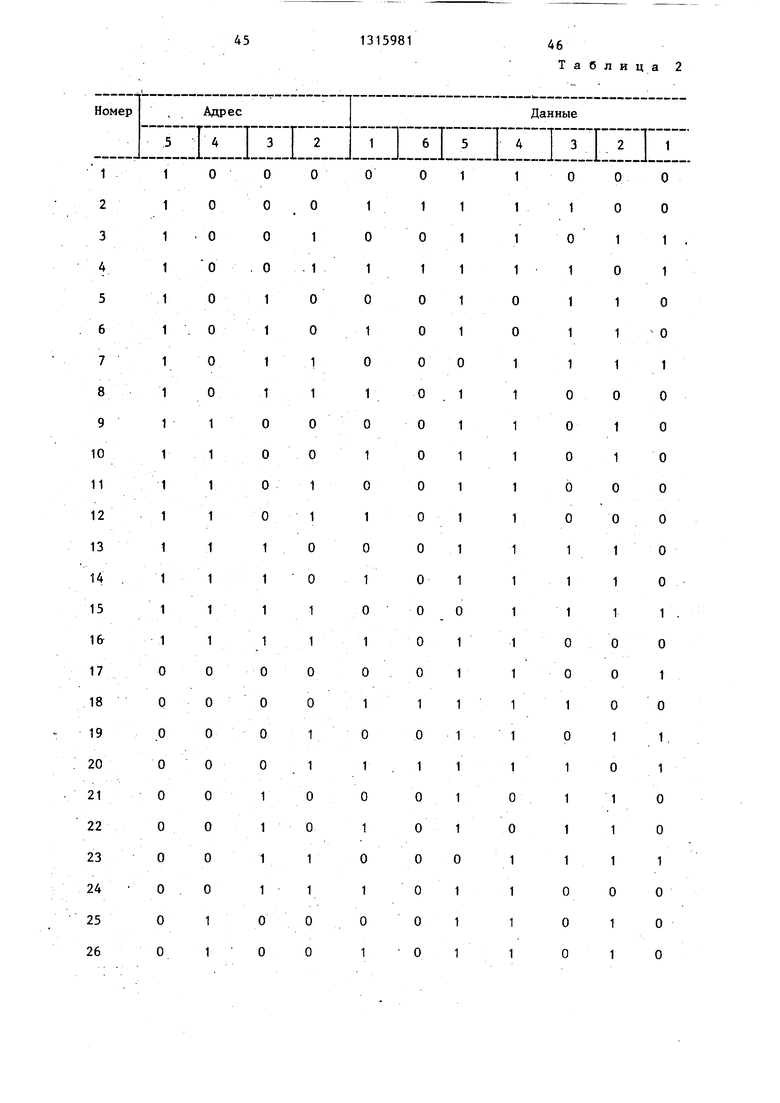

Блок 98 постоянной памяти блока 26 микропрограммного управления запрограммирован в соответствии с табл.2.

Кроме того, вводят в блок 58 постоянной памяти устройства 2 для контроля микроэвм (второй вариант, фиг.З) вспомогательную информацию о линейных участках рабочей программы. Информация о любом линейном участке размещается в четырех ячейках блока 58 постоянной памяти (табл.3), при этом в ячейки с адресами В° и в + 1 вводят вектор перехода, т.е. соответственно адреса двух начальных команд линейных участков, на которые передается управление завершающей командой J данного линейного участка. В ячейку с адресом В° + 2 вводят адреса двух ячеек блока 58 постоянной памяти, в которых хранятся первые элементы массивов вспомогательной информации линейных участков, на которые передается управление командой J (Вр , В в|Вз и т.д.). В ячейку с адресом В + 3 вводят характеристическое множество Т {Т, ЛТ, Те J данного линейного участка L..

В первые четьфе ячейки блока 58 постоянной памяти вводят служебную информацию, служащую для установки в исходное состояние устройства 2 для контроля вьшолнения программ микроэвм. В первую и вторую ячейки вводят начальный адрес программы А, в третью ячейку - двойной адрес ячейки (Bj, ), хранящей первый элемент массива вспомогательной информации начального линейного участка LJ программы, в четвертую ячейку - установочное характеристическое множество Т {Т, 0; ЛТ, Ф 0; Tgj, 0} Это необходимо для обеспечения начальной синхронизации устройства 2 контроля выполнения программ с работой микроэвм.

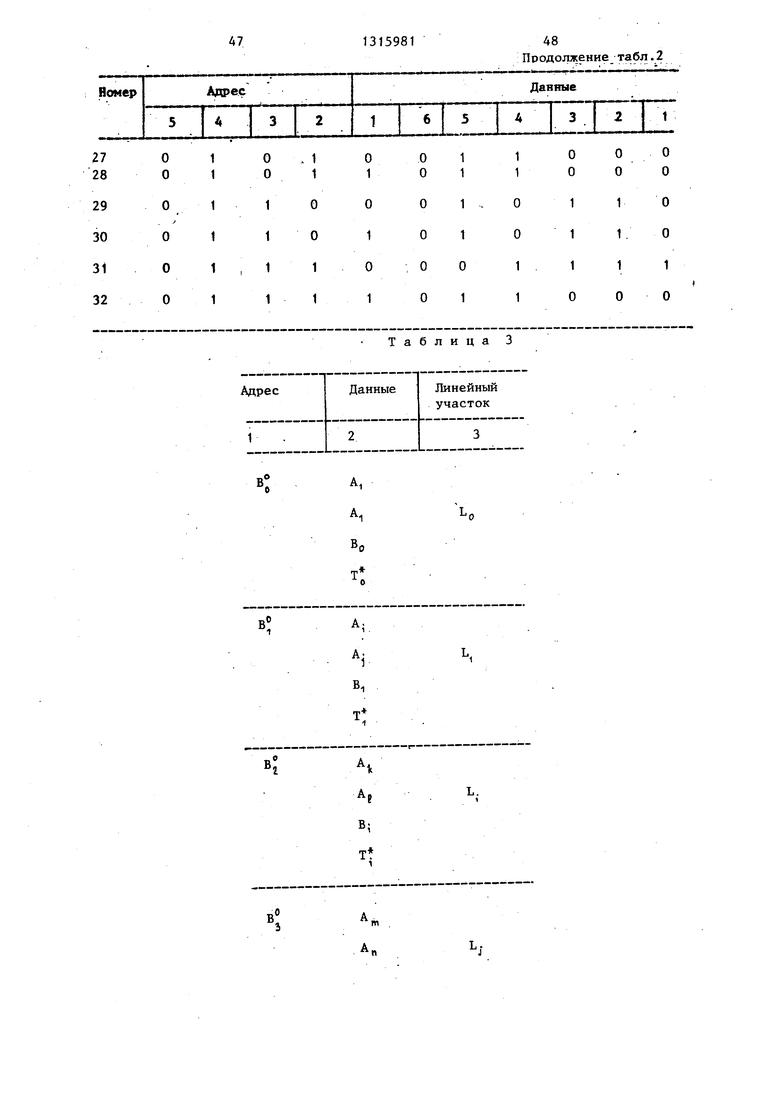

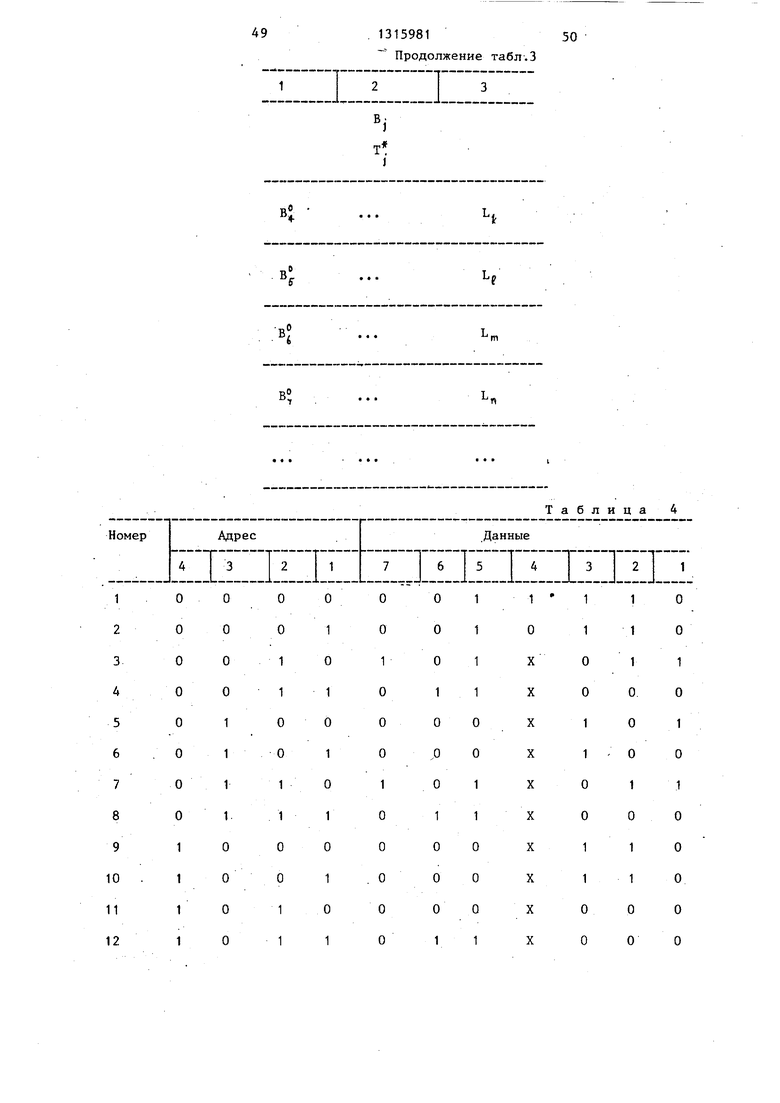

Блок 105 постоянной памяти блока 57 микропрограммного управления за- программирован в соответствии с табл.4.

1 6

Устройство 2 для контроля выполнения программ по первому варианту (фиг.2) работает следующим образом. Микроэвм приводится в исходное

состояние путем подачи логической . 1 в линию Общий сброс, входящую в состав шин 10 и 14. Сигнал на этой линии формируется автоматически после включения питания или, например,

появляется в результате нажатия соответствующей кнопки на пульте управления.

Сигнал Общий сброс приводит в исходное состояние процессор 1 и управляющую часть памяти 5 и 6, а

также поступает на вход 17 начальной установки устройства 2, подготавливает вьщачу сигнала прерывания из устройства 2 в процессор 1 по линии

21 в случае обнаружения сбоя и настраивает устройство 2 так, что первому адресу первого линейного участка программы соответствует адрес ячейки блока 28 постоянной памяти,

хранящей служебную информацию о первом линейном участке.

Подготовка выдачи сигнала прерывания производится следующим образом. Сигнал Общий сброс поступает

с шины 14 (фиг.2) на вход 17 начальной установки устройства 2 и далее на вход установки в О триггера 31. Сигнал на инверсном выходе триггера 31 принимает значение логической 1 и поступает на выход 21

устройства 2 для контроля выполнения программ. Это состояние соответствует отсутствию прерывания.

Настройка устройства 2 для контроля выполнения программ на соответствие адресов памяти 6 микроЭВМ и бло- ;ка 28 постоянной памяти производит- ся при поступлении сигнала Общий сброс с шины 14 на вход 17 начапь,ной установки устройства 2 и далее на вход начальной установки регистра 27, в результате чего сигналы на выходах этого регистра принимают нулевые значения. Эти сигналы поступают на вход старших разрядов адреса блока 28 постоянной памяти. Одновременно сигнал Общий сброс поступает с входа 17 устройства 2 на вход 36 начальной установки блока 26 микропрограммного управления и далее на вход обращения блока 98 постоянной памяти (фиг.5) В результате воздействия сигнала Общий сброс на всех выходах блока 98 постоянной памяти устанавливается высокоимпеданс- ное состояние. Это состояние на выходных линиях блока 98 воспринимается на входах связанных с ними элементов как сигнал логической 1.

На информационном входе 15 устройства 2 процессор 1 устанавливает начальный адрес рабочей программы. При наличии сигнала сопровождения по цепи 16-ЗА на сихровходы регистров 95 и 96 младший А. и старший А части текущего адреса запоминаются соответственно в этих регистрах. Высо- коимпедансное .состояние управляющего входа 51 блока 23 регистров восприни- мается на прямом входе обращения регистра 96 как сигнал логической 1 (фиг.4), и старшая часть А ос началь- ого адреса программы поступает с информационного выхода 32 блока 23 ре- гистров на первый вход схемь 24 сравнения.

Сигнал Общий сброс поступает с шины 14 на вход 17 начальной установки устройства 2 и .далее на вход на- чальной установки блока 28 постоянной памяти, и на его выходах устанавливается высокоимпедансное состояние, к которое воспринимается на втором входе схемы 24 сравнения как число все единицы. При этом сигнал на выходе схемы 24 сравнения принимает значение логической 1, так как коды на входах схемы 24 сравнения не совпадают. Этот сигнал поступает на вход 33 блока 26 микропрограммного управления и далее на четвертый вход регистра 97 Запись в регистр 97 исходного состояния (1111) производится тактовым сигналом процессора .1 по цепи 22-43-26 (фиг.2) и далее на синхровход регистра 97 (фиг.5), в результате чего сигналы на первом, втором, третьем и четвертом выходах этого регистра при- .нимают единичное значение и поступа- гют соответственно на первый, второй, третий и четвертый адресные входы блока 98 постоянной памяти. Одновременно высокоимпедансное состояние первого, второго и третьего выходов блока 98 постоянной памяти (выход 48 блока 26 микропрограммного управления) воспринимается на входе младших разрядов адреса блока 28 постоянной памяти как сигналы логической 1. Сигнал Общий сброс поступает с входа 17 начальной установки устройства 2 на вход обращения блока 28 постоянной памяти и запрещает поступление содержимого ячейки блока 28 постоянной памяти с адресом 00-0111 (БО + 7) (табл.1) на его выход до завершения сигнала Общий сброс.

Кроме того, сигнал Общий сброс поступает с входа 17 начальной установки на вход 37 начальной установки блока 25 выделения максимального и минимального количеств импульсов и далее на входы установки в О первого 99 и второго 100 счетчиков (фиг.6). Счетчики 99 и 100 устанавливаются в нулевое состояние и сигналы на выходах группы выходов 39 и 40 принимают нулевые значения. В результате воздействия нулевых сигналов. Поступающих с группы выходов 40 блока 25 вьщеления максимального и минимального количества импульсов соответственно на входы группы входов элемента И 29, сигнал на вькоде этого элемента также принимает нулевое значение и устанавливается на входе установки в 1 триггера 31 (фиг.2)

В результате воздействия нулевых сигналов, поступающих с выходов группы выходов 39 блока 25 выделения минимального и максимального количеств импульсов соответственно на входы группы входов элемента ИЛИ 30, сигнал на выходе этого элемента также принимает нулевое значение, Этот сигнал поступает на вход 42 запрета блока 25 выделения минимального и максимального количеств импульсов и далее на второй вход элемента И 101 (фиг.6), запрещая прохождение тактовых сигналов по цепи 22-44-101- -99 на счетный вход в режиме вычитания -1 счетчика 99. Одновременно сигнал логического О с входа 42 зй прета блока 25 выделения минимального и максимального количеств импульсов поступает через инвертор 103 на второй вход элемента И 102, разрешая прохождение тактовых сигналов по цепи 22-44-102-100 на счетный вход в режиме суммирования +1 счетчика 100.

Нулевой сигнал с выхода элемента ИЛИ 30 поступает на вход 41 блока 26 микропрограммного управления и далее на пятый адресный вход блока 98 постоянной памяти.

После- окончания сигнала Общий сброс процессор 1 автоматически или по инициативе оператора переходит к

1913

вьтолнеяию рабочей программы, записанной в постоянной памяти 6 микро- ЭВМ. При этом счетчик 100 блока 25 вьщеления минимального и максимального количеств импульсов начинает подсчет тактовых импульсов, поступающих по цепи 22-44-102-100. Одновременно снятие сигнала Общий сброс разрешает обращение к блоку 98 постоянной памяти, и содержимое ячей- ки с адресом 01111 устанавхшвается на соответствующих его выходах (табл.2, строка 32).

Нулевые сигналы с первого, второго и третьего выходов блока 98 постоянной памяти поступают на выход 48 блока 26 микропрограммного управления и далее по линиям млад- щих разрядов шины адреса на входы младших разрядов адреса блока 28 постоянной памяти. Таким образом, на адресных входах блока 28 постоянной памяти устанавливается адрес 00-000 (Вр (табл.О. Вместе со снятием сигнала Общий сброс на входе обращения блока 28 постоянной памяти с его выходов на второй вход схемы 24 сравнения поступает младшая часть ожидаемого адресного слова (табл.1). Одновременно нулевой сигнал с линии мпадшего разряда информационного выхода 48 блока 26 микропрограммного управления поступает на управляющий вход S1 блока 23 регистров и далее на инверсный вход обращения регистра 95, в результате чего младшая часть А начального адреса программы с выходов регистра 95 поступает на выход 32 блока 23 регистров и далее на первый вход схе мы 24 сравнения. В результате совпадения ожидаемой А. и действительной А . младших частей начального адреса программы сигнал на выходе схемы 24 сравнения принимает значе- ние логического О. Этот сигнал поступает на вход 33 блока 26 микропрограммного управления и далее на четвертый информационный вход регист эа 97, на первый, второй и третий инфор мационные входы которого поступают сигналы 000 с первого, второго и третьего выходов блока 98 постоянной памяти (табл.2, строка 32). Тактовый сигнал, поступакиций по цепи 22-43 на тактовый вход блока 26 микропрограммного управления и далее на синхро- вход регистра 97, производит запись информационного слова 0000 в этот ре120

гистр. Таким образом, на первом, втором, третьем и четвертом адресных входах блока 98 постоянной памяти устанавливаются нулевые значения сигналов, и, так как на пятом адресном входе присутствует нулевой сигнал, на выходах блока 97 постоянной памяти устанавливаются значения сигналов, соответствукщие строке 17 табл.2 (содержимре ячейки памяти с адресом 00000) .

Единичный сигнал с первого и нулевые с второго и третьего выходов блока 97 постоянной памяти поступают на выход 48 блока 26 микропрограммного управления и далее на вход мпадших разрядов адреса блока 28 постоянной памяти, в результате чего на адресных шинах устанавливается адрес 00-001 (В + 1) и с его выходов на второй вход схемы 24 сравнения поступает старшая часть ожидаемого адресного слова А:,. (табл. 1). Одновременно единичный сигнал с линии мпадшего разряда информационного выхода 48 блока 26 микропрограммного управления поступает на вход 51 записи блока 23 регистров и далее на прямой вход обращения регистра 96, в результате чего старшая часть AIJ. начального адреса программы с выходов регистра 96 поступает на выход 32 блока 23 регистров и далее на первый вход схемы 24 сравнения. Нулевой сигнал сравнения ожидаемой А и действительной А старших частей начального адреса программы с выхода схемы 24 сравнения поступают на вход 33 блока 26 микропрограммного управления и далее на четвертый информационный вход регистра 97, на первый, второй и третий информационные входы которого поступают соответственно сигналы 1, О, О с первого, второго и третьего выходов блока 98 постоянной памяти (строка 17, табл.2).Очередной Тактовый сигнал, поступающий на синхровход регистра 97, производит запись информационного слова 0001 в этот регистр, и на адресных входах блока 98 постоянной памяти устанавливается адрес 00001, в результате чего на выходах этого блока устанавливалются значения сигналов, соответствующие строке 18 табл.2.

Нулевые сигналы с первого и второго и единичный с третьего выходов блока 98 постоянной памяти поступа211

ют на вход младших разрядов адреса блока 28 постоянной памяти - (адрес 00-100 (В + 4), с выходов которого на информационный вход регистра 27 поступает информационное слово В , - адрес в блоке 28 постоянно памяти массива служебной информации для первого линейного участка рабочей программы (табл.1). Одновременно с шестого выхода блока 98 постоя ной памяти (выхода 47 блока 26 мик- ропрогр аммного управления) на вход записи регистра 27 поступает единичный сигнал, производяш;ий запись информационного слова В в этот регистр. Адрес в с выходов регистра 27 поступает на вход старших разрядов адреса блока 28 постоянной памяти.

Кроме того, единичный сигнал с первого и нулевые с второго и третьего выходов блока 98 постоянной памяти поступают соответственно на первый, второй и третий информаци онные входы регистра 97. Очередной тактовый сигнал, поступающий на син хровход, производит запись информационного слова 0100 в этот регистр, и на адресных входах блока 98 постоянной памяти устанавливается адрес 00100, в результате чего на выходах этого блока устанавливаются значения сигналов, соответствующие строке 21 табл.2. Нулевой сигнал с первого и единичный с второго и третьего выходов блока 98 постоянной памяти поступают на вход младших разрядов адреса блока 28 постоянной памяти - адрес (В° 6), с выхода которого на информационный вход 38 блока 25 вьщеления минимального и максимального количеств импульсов поступает код числа Т импульсов первого линейного участка (табл.1). Одновременно с четвертого выхода блка 98 постоянной памяти по цепи 45- 49 на первый вход записи счетчика 99 блока 25 вьщеления минимального и максимального количеств импульсов поступает нулевой сигнал, и код Т запоминается в счетчике 99, с выходов которого этот код поступает на группу выходов 39 блока 25 выделени минимального и максимального количеств импульсов и далее на группу входов элемента ИЛИ 30. Сигнал на входе элемента ИЛИ 30 принимает единичное значение, если Т,, О и сохраняет нулевое хначение в противно

598122

случае. Очередным тактовым сигналом в регистр 97 записывается информационное слово 0110.

Если Тх| О, значение сигнала на 5 пятом входе блока 98 постоянной памяти и входе 42 запрета счета блока 25 вьщеления минимального и максимального количеств импульсов не изменяется. При этом на адресных вхоW дах блока 98 постоянной памяти устанавливается адрес 00110 и сигналы на его выходах принимают значения в соответствии со строкой 23 табл.2, а счетчик 100 блока 25 вьщеления мак- 15 симального и минимального количеств импульсов продолжает подсчет тактовых импульсов.

При Т , на адресных входах

20 блока 98 постоянной памяти устанавливается адрес 10110 и сигналы на . его выходах принимают значения в соответствии со строкой 7 табл.2, а единичное значение сигнала на входе

25 42 запрета блока 25 вьщеления минимального и максимального количеств импульсов поступает на вход элемента И 101 и через инвертор 103 на вход элемента И 102, соответственно

30 отпирая элемент И 101 для прохождения тактовых сигналов с входа 44 блока 25 вьщеления минимального и максимального количеств импульсов на счет- ньш вход в режиме вычитания счетчи35 ка 99 и запирая элемент И 102 для прохождения тактовых сигналов на счетный вход в режиме суммирования счетчика 100 (фиг,6).

Единичные значения сигналов с

40 первого, второго и третьего выходов блока 98 постоянной памяти поступают на вход младших разрядов адреса блока 28 постоянной памяти - адрес (в + 7), с выходов которого на ин- 45 формационный вход 38 блока 25 вьщеления минимального и максимального количеств импульсов поступает в дополнительном коде число Т импульсов первого линейного участка

50 (табл.1). Одновременно с пятого выхода блока 98 постоянной памяти по цепи 46-50 на второй вход записи счетчика 100 блока 25 вьщеления минимального и максимального количеств

55 импульсов поступает нулевой сигнал, и код дТ запоминается в счетчике 100. Для правильной работы устройства 2 для контроля выполнения программ (фиг.2) число импульсов для каж23

дого линейного участка выбирается из условия йТ , где п - разрядность счетчика 100. Сигнал на выходе элемента И 29 после установки на выходе 40 блока 25 вьщеления минимального и максимального количеств импульсов дополнительного кода числа л Т, импульсов сохраняется нулевое значение, и состояние триггера 31 не изменяется.

После загрузки в блок 25 выделения ьтнимального и максимального количеств импульсов числа Л Т, устройства 2 начинает сравнение текущих адресов программы А, с вектором перехода линейного участка. Сравнение вьшолняется следующим образом. При поступлении очередного тактового импульса на синхровход регистра 97 блока 26 микропрограммного управления в регистре запоминается информационное слово Х111, и на адресных входах блока 98 постоянной памяти устанавловия Т О (счетчик 99 блока 25 выделения минимального и максимального количеств импульсов установится в О по приходу на его счетный вход в режиме вычитания Т тактовых импульсов) . При Т О с выхода элемен та ИЛИ 30 на вход 41 блока 26 микропрограммного управления и далее на пятый адресный вход блока 98 постоянной памяти поступает нулевой сигнал, и на вькодах этого блока устанавливаются значения сигналов в соответствии со строкой 17 табл.2. Одновременно нулевой сигнал с выхода элеливается адрес ХХ111 одной из четырех

его ячеек (табл.2, строки 8, 16, 24,, 25мента ИЛИ 30 поступает на вход 42

32) в зависимости от состояний выхо-запрета счета блока 25 вьщеления мидов схемы 24 сравнения и элементанимального и максимального количеств

ИЛИ 30. При этом нулевые значенияимпульсов и устанавливает этот блок

сигналов с выхода 48 блока 26 микро-в режим счета лТ (открывает элемент

30И 103 для прохождения тактовых сигнапрограммного управления поступают на вход младших разрядов адреса блока 28 постоянной памяти (адрес Вр, с выходов которого на второй вход схемы 24 сравнения поступает младшая

лов на счетный вход в режиме суммирования счетчика 100 и закрывает элемент И 101). После выполнения условий , 0с выхода 48

часть А

первого ожидаемого адреса 35 блока 26 микропрограммного управле- линейного участка L . Одновременно единичный сигнал с первого выхода блока 98 постоянной памяти блока 26 микропрограммного управления поступает на управляющий вход 51 блока регистров и далее на прямой вход обращения регистра 96, с выходов которого на выход 32 блока регистров и далее на первый вход схемы 24 сравнения поступает младшая часть А, те- 45 гичным путем поступает значение А кущего адреса, записанная в этот ре- старшей части текущего адреса. Оче- гистр очередным управляющим сигналом, поступаклцим с .входа 16. записи на вход 34 записи блока 23 регистров.

Если А{. А,-„, сигнал на выходе 50 на адресных входах блока 98 постоян- схемы 24 сравнения принимает нулевое ной памяти при А А,- устанавли- значение. Этот сигнал поступает на вается адрес 00001 и на выходах это- вход 33 блока 26 микропрограммного го блока устанавливаются значения управления и далее на четвертый вход сигналов в соответствии со строкой регистра 97. Очередным тактовым сиг- 55 18 табл.2. На этом цикл контроля линия на вход младших разрядов адреса блока 28 постоянной памяти поступает информационное слово 001 и значение A.j(. старшей части первого ожидаемо- 40 го адреса вектора перехода линейного участка L из ячейки блока 28 постоянной памяти с адресом В + 1 поступает на второй вход схемы 24 сравнения, на первый вход которой аналоредной тактовый сигнал на синхровхо- де 43 регистра 97 записывает в этот регистр информационное слово 0001,

налом в регистр 97 заносится информационное слово 0000, и на адресных входах блока 98 постоянной памяти устанавливается адрес одной из-двух

- а

131598124

его ячеек ХОООО (табл.2, строки 1 и 17) в зависимости от состояния выхода элемента ИЛИ 30. Если Т, О, на адресных входах блока 98 постоянной с памяти - адрес 10000 и на его выходах устанавливаются значения сигналов в соответствии со строкой 1 табл.2. В дальнейшем состояния выходов блока 26 микропрограммного управления не изменяются до выполнения усfO

5

0

ловия Т О (счетчик 99 блока 25 выделения минимального и максимального количеств импульсов установится в О по приходу на его счетный вход в режиме вычитания Т тактовых импульсов) . При Т О с выхода элемента ИЛИ 30 на вход 41 блока 26 микропрограммного управления и далее на пятый адресный вход блока 98 постоянной памяти поступает нулевой сигнал, и на вькодах этого блока устанавливаются значения сигналов в соответствии со строкой 17 табл.2. Одновременно нулевой сигнал с выхода элелов на счетный вход в режиме суммирования счетчика 100 и закрывает элемент И 101). После выполнения условий , 0с выхода 48

35 блока 26 микропрограммного управле- 45 гичным путем поступает значение А старшей части текущего адреса. Оче-

ния на вход младших разрядов адреса блока 28 постоянной памяти поступает информационное слово 001 и значение A.j(. старшей части первого ожидаемо- 40 го адреса вектора перехода линейного участка L из ячейки блока 28 постоянной памяти с адресом В + 1 поступает на второй вход схемы 24 сравнения, на первый вход которой аналоблока 26 микропрограммного управле- гичным путем поступает значение А старшей части текущего адреса. Оче-

редной тактовый сигнал на синхровхо- де 43 регистра 97 записывает в этот регистр информационное слово 0001,

нейного участка L завершается и производится загрузка В в регистр 27 для контроля линейного участка Li..251

Если А А. или . А,-р,аналогичным путем в соответствии с табл.2 производится проверка условий иА(./с и Р выполнений этих условий производится загрузка В° в регистр 27 для контроля линейного участка L.

Таким образом, при правильном выполнении программы микроэвм в начале каждого очередного линейного участка производится загрузка блока 25 вьщеления минимального и максимального количеств импульсов соответствующими значениями Т и Л Т и счетчик 100 блока 25 выделения минимального и максимального количеств импульсов никогда не установится в состояние Все единицы. Если при поступлении Tj тактовых импульсов не выполняются условия А А,. и А А,(А . Аj.), т.е. в результате сбоя или неисправности процессор 1 перешел к выполнению команды с произвольным адресом, минуя адрес А-(А сигнал на выходе элемента И 29 принимает единичное значение. Этот сигнал поступает на вход установки в 1 триггера 31, и он переходит в единичное состояние. Нулевой сигнал с инверсного выхода этого триггера поступает на выход 21 устройства 2 контроля выполнения программ в ка- естве сигнала Запрос прерывания. После обработки прерывания в микро- ЭВМ устройство 2 для контроля приводится в исходное состояние описанным путем и микроэвм начинает выполнение рабочей программы с нулевого адреса.

Работа устройства 2 (фиг.2) поясняется временной диаграммой (фиг.15) отображающей процесс загрузки (момент 134 времени) и постепенного уменьшения содержимого счетчиков Т (эпюра 135) и лТ (эпюра 136) и формирования сигналов сравнения 137 и прерывания 138 в случае возникновения сбоя 139.

В момент 140 времени происходит совпадение текущего адреса программы А и одного из ожидаемых адресов AJ (или А.). Импульсы совпадения 137 формируются на входе 33 блока 26 микропрограммного управления в моменты перехода микроЭВМ на начало следую- .щего линейного участка. Содержимое счетчика зТ при этом остается ненулевым и сигнал на входе установки

126

в 1 триггера 31 сохраняет нулевое значение. Если в результате возникновения помехи (условно представлена импульсом 139), приводящей к выполнению ошибочного перехода в пределах линейного участка программы (или к другому линейному участку программы) , сравнение текущего адреса А . и одного из ожидаемых адресов А. произойдет не в запланированный момент 141 времени, а в момент 142 (не показан) до обнуления счетчика Т, т.е. в момент 143 времени (не показан) после переполнения счетчика аТ, в момент времени 144 переполнения счетчика 100 импульсов Т сигнал на выходе 21 устройства 2 (эпюра 138) принимает нулевое значение.

Эпюры на фиг.15 свидетельствуют о том, что время между возникновением сбоя и его обнаружением в предпагае- мом устройстве не превышает длитель-

ности прохождения линейного участка

программы, что позволяет организовать своевременную реакцию устройства управления в случае аварийной ситуации. Устройство 2 для контроля микроэвм по второму варианту (фиг.З) работает

следующим образом.

Й1кроЭВМ приводится в исходное состояние путем подачи логической 1 в линию Общий сброс, входящую в состав шин 10 и 14.

Сигнал на этой линии формируется автоматически после включения питания или, например, появляется в результате нажатия соответствующей кнопки на пульте управления.

Сигнал Общий сброс приводит в исходное состояние процессор 1 и управляющую часть памяти 5 и 6, а также подготавливает вьщачу сигнала прерывания из устройства 2 в процессор 1 по линии 21 при обнаружении сбоя и настраивает устройство 2 так, что первому адресу первого линейного участка программы соответствует адрес ячейки блока 58 постоянной памяти, хранящей характеристическое множество этого участка.

Подготовка выдачи сигнала прерывания производится следующим образом.

Сигнал Общий сброс поступает с шины 14 (фиг.З) на вход 17 начальной установки устройства 2, и далее на вход элемента ИЛИ 61, ас его вы,271315981

хода - на входы установки в единичное

состояние триггеров 63 и 65. Единичный сигнал с прямого выхода триггера 65 отпирает элемент И-НЕ 69, в результате чего нулевой сигнал с инверсного выхода триггера 63 поступает на первый вход элемента И-НЕ 69, сигнал на выходе 21 которого принимает единичное значение. Это состояние соответствует отсутствию прерывания.

ва Т с информационного входа 88 в счетчики 107. Значения Т 0 AT(j 1 О и Т 0 поступают с выходов первого, второго и последующих счетчиков 107 соответственно на выходы 93, 92 и 94 и далее на группы входов элементов ИЛИ 60, ИЛИ-НЕ 59 и ИЛИ 62. На выходе элемента ИЛИ 60 устанавливается нулевое значение сигнала, который присутствует на информационном входе триггера 64,входе запрета счетчика 83 блока 56 счетчиков и Первом адресном входе 84 блока 57 микропрограммного управле-

Настройка устройства 2 для контроля на соответствие адресов памяти 6

микроэвм и блока 58 постоянной памя- ния.на выходе элемента иЛИ-НЕ 59 ти производится при поступлении сиг- устанавливается нулевое значение сигнала Общий сброс с шины 14 на .вход „ала, который поступает на счетный

вход триггера 64. На выходе элемента ИЛИ 62 устанавливается нулевое 20 значение сигнала, который присутствует на втором входе элемента И 67 и

17 начальной установки устройства 2 и далее на вход сброса регистра 53, в результате чего сигналы на выходах этого регистра принимают нулевые значения. Эти сигналы поступают на вход старших разрядов адреса блока 58 постоянной памяти. Одновременно сигнал Общий сброс поступает на вход 74 блока 57 микропрограммного управления и далее на вход обращения блока 105 постоянной памяти (фиг.7). В резуль- . .тате воздействия сигнала Общий

запирает его для прохождения сигнала сброса триггера 63 с седьмого выхода 79 блока 105 постоянной памя- 25 ти по цепи 79-67-63 (фиг.З).. После окончания сигнала Общий сброс процессор 1 автоматически или по инициативе оператора переходит к выполнению рабочей программы, запи- сброс на всех выходах блока 105 по- саной в постоянной памяти 6 микроЭВМ. . стоянной памяти устанавливается вы- сокоимпедансное состояние. Это состояние на выходных линиях блока 105 постоянной памяти воспринимается на

входах связанных с ними элементов как р запоминается в регистре 52 и сигнал логической 1 .«Записьвре- с его выхода поступает на первый вход гистр 104 исходного состояния производится тактовым сигналом процессора 1 по цепи 22-87-57 (фиг.З) и далее на сихровход регистра 104 (фиг.7), в результате чего сигналы на первом и втором вьгходах этого регистра принимают единичное значение. Эти сигналы поступают по линии 81 на вход младпшх разрядов адреса блока 58 постоянной памяти. Содержимое ячейки блока 58 постоянной памяти

На информационном входе 15 устройства 2 процессор 1 устанавливает начальный адрес рабочей программы.При наличии сигнала сопровождения этот

схемы 55 сравнения. При включении питания регистр 54 устанавливаемся в произвольное состояние и с его вы- 40 хода на первый вход схемы 55 сравнения поступает произвольный ожидаемый адрес. На выходе схемы 55 сравнения устанавливается единичный сигнал в случае, если состояние реги- 45-стра 54 совпадает с начальным адресом и нулевой - в противном случае. Это соответствует неопределенному значению сигнала на втором адресном входе 85 блока 57 микропрограммного

с адресом 00-001 (В +2) (табл.3)

емый адрес. На выходе схемы 55 сравнения устанавливается единичный сигнал в случае, если состояние реги- 45-стра 54 совпадает с начальным адресом и нулевой - в противном случае. Это соответствует неопределенному значению сигнала на втором адресном входе 85 блока 57 микропрограммного

поступает на информационный вход 88

блока 56 счетчиков. Сигнал с шестого50 управления и на третьем адресном вхо- выхода блока 105 постоянной памяти де блока 105 постоянной памяти.Таким (фиг.7) поступает на второй вход эле- образом, в соответствии с начальной мента И 106 и открывает его для про- установкой на адресных входах блока хождения сигнала по цепи 22-87-57 105 постоянной памяти формируется

(фиг.З), 87-106-76 (фиг.7),76-70-7555 адрес 0X11. Снятие сигнала Обшлй

(фиг.З) на вход 75 записи блока 56 счетчиков и далее на входы записи счетчиков 107 (фиг.8),что вызывает запись характеристического множестсброс соответствует обращению к блоку 105 постоянной памяти. Сигналы на его выходах принимают значения в соответствии со строками 4 или 8 табл.4.

28

ва Т с информационного входа 88 в счетчики 107. Значения Т 0 AT(j 1 О и Т 0 поступают с выходов первого, второго и последующих счетчиков 107 соответственно на выходы 93, 92 и 94 и далее на группы входов элементов ИЛИ 60, ИЛИ-НЕ 59 и ИЛИ 62. На выходе элемента ИЛИ 60 устанавливается нулевое значение сигнала, который присутствует на информационном входе триггера 64,входе запрета счетчика 83 блока 56 счетчиков и Первом адресном входе 84 блока 57 микропрограммного управле-

ния.на выходе элемента иЛИ-НЕ 59 устанавливается нулевое значение сиг„ала, который поступает на счетный

. После окончания сигнала Общий сброс процессор 1 автоматически или по инициативе оператора переходит к выполнению рабочей программы, запи- саной в постоянной памяти 6 микроЭВМ.

На информационном входе 15 устройства 2 процессор 1 устанавливает начальный адрес рабочей программы.При наличии сигнала сопровождения этот

р запоминается в регистре 52 и с его выхода поступает на первый вход

схемы 55 сравнения. При включении питания регистр 54 устанавливаемся в произвольное состояние и с его вы- хода на первый вход схемы 55 сравнения поступает произвольный ожида р запоминается в регистре 52 и с его выхода поступает на первый вход

емый адрес. На выходе схемы 55 сравнения устанавливается единичный сигнал в случае, если состояние реги- 5-стра 54 совпадает с начальным адресом и нулевой - в противном случае. Это соответствует неопределенному значению сигнала на втором адресном входе 85 блока 57 микропрограммного

адрес 0X11. Снятие сигнала Обшлй

сброс соответствует обращению к блоку 105 постоянной памяти. Сигналы на его выходах принимают значения в соответствии со строками 4 или 8 табл.4.

2913

Единичным сигналом с шестого выхода блока 105 ndCTOHHHofl памяти отпирается элемент И 106 и тактовый сигнал поступает по цепи 22-87-106- -76-70-75 на вход 39 записи информации блока 56 счетчиков. Происходит повторная запись характеристического множества Т в блок 56 счетчиков.

Первый тактовый сигнал по цепи 22-83-104 производит запись в регист 10А информационного слова 0X00. На адресных входах блока 105 постоянной памяти формируется адрес 0X00, и сигналы на его выходах принимают значения в соответствии со строками 1 или 5 табл,4.

Информационное слово 00 с выхода 81 блока 57 микропрограммного управления поступает на вход младших разрядов адреса блока 58 постоянной памяти, и на его выходах устанавливается содержимое первой (В°) ячейки А, Оиждаемый адрес А поступает на информационные входы регистра 54 и запоминается в нем при поступлении единичного сигнала с третьего выхода 78 блока 105 постоянной памяти на вход записи этого регистра. На выходе схемы 55 сравнения устанавливается нулевое значение сигнала о совпадении текущего адреса А, и ожидаемого , Этот сигнал поступает по цепи 55-85 на второй адресньш вход 8 блока 57 микропрограммного управления и далее на третий вход блока 105 постоянной памяти. Таким образом,, независимо от исходного состояния регистра 54 до прихода второго тактового сигнала на входах блока 105 постоянной памяти устанавливается адрес 0000 и сигналы на его выходах принимают значения, соответствующие строке 1.табл,4. Единичный сигнал с выхода 77 блока 57 микропрограммного управления поступает на информационный вход триггера 63 и, в случае изменения сигнала на его синхровхо- де, подтверждает единичное состояние отсутствия прерывания.

При поступлении второго тактового сигнала в регистре 104 запоминается информапзионное слово 0110. Единичное значение сигнала с третьего выхода 80 регистра 104 поступает на управляющий вход 82 коммутатора 72 и подключает к его выходам 91 первую группу входов 89, Одновременно информационное слово 10 с выхода 81 блока

130

57микропрограммного управления поступает на вход младших разрядов адреса блока 58 постоянной памяти, и на его выходах появляется содержимое

третьей BS + 2 ячейки В, , Первая часть В этого информационного слова поступает с выходов блока

58постоянной памяти на первую группу 89 входов коммутатора 72 и с его

выходов на информационные входы регистра 53, На входах блока 105 постоянной памяти блока 57 микропрограммного управления устанавливается адрес 0010, и сигналы на его выходах принимают значения, соответствующие строке 3 табл,4. Единичный сигнал с выхода 79 блока 57 микропрограммного управления поступает на вход записи регистра 53, и в регистре запоминается информационное слово В - адрес массива служебной информации для первого линейного участка L программ, . При поступлении третьего тактового сигнала в регистре 104 запоминается информационное слово 0X11, на адресных входах блока 105 постоянной памяти блока 57 микропрограммного управления устанавливается адрес

0011 и сигналы на его выходах принимают значения, указанные в строке 4 табл.4, в результате чего содержимое Т ячейки В + 3 блока 58 постоянной памяти (табл,3) загружается в блок

56 счетчиков.

Код элементов Т и Тд характеристического множества выбивается таким, чтобы к моменту выбора из памяти 6 микроэвм команды с адресом А

или А содержимое первого, третьего и последующих счетчиков 107, работа.ю- щих в режиме вычитания (подсчета сигналов на тактовом входе 22 и линиях 20 шины 14), бьшо равно нулю.

Код 4 Т выбирается из соотношения ДТ Т, где Т„ - суммарное количество тактов на линейном участке, в течение которых процессор 1 находится в режиме ожидания при работе

с внешними устройствами, В качестве импульсов на интерфейсных управляющих линиях могут быть использованы сигналы управления записью в запоминающее устройство (ЗУ), чтение из

ЗУ, вводом информации с внешних устройств, выводом на внешние устройства, а также сигналы управления арифметико-логическим устро1 ством

311

при выполнении той или иной операци (или группы операций). Количество таких сигналов зависит только от чила соответствующих команд в рассматриваемом линейном участке программы и не связано с быстродействием внешних устройств. Таким образом, линейный участок программы однозначно определен количеством-импульсов на интерфейсных управляющих линиях. В качестве тактовых импульсов могут быть использованы сигналы синхронизации выборки или выполнения команды. Например, для микропроцессора КР580ИК8 в качестве тактовых импульсов на тактовый вход устройства могут быть поданы сигналы М выборки команд. При этом число Т Т. тактовых импульсов строго детерминировано и определяется количеством команд в данном линейном участке программы. Аналогично строго определенное число тактовых импульсов, равное суммарному числу машинных циклов прохождения команд данного линейного участка программы, может быть получено при использовании в качестве сигналов на тактовом входе устройства импульсов SYNC микропроцессора.

В качестве тактовых импульсов могут быть использованы также сигналы тактового генератора микроЭВМ (для микропроцессора К580ИК80 ). В этом случае число тактовых импульсов на заданном линейном участке программы определяется в интервале Т f7 Использование режима Ожидание связано с тем, что в состав управляющих микроЭВМ могут входить специальные процессоры обмена (каналы, работающие по своей программе .и потому асинхронные по отношению К центральному процессору).

Во многих приложениях время , ожидания асинхронного ответа о готовности внешнего устройства к обмену может быть ограничено из разумных соображений максимальным числом TW я Р этом минимальное число тактовых импульсов Т равно суммарному числу тактов 1/,ТТЛ прохождения команд данного линейного участка программы, а максимальное число тактовых импульсов

f WMCIKC

I

о

TI т, +

Т

Ч

132

где Т - такты ожидания микропроцессора.

Если в обмене с микроЭВМ участвует внешнее устройство, для которого невозможно установить это время заведомо велико (например, при работе микроЭВМ в мультипроцессорной системе), команда,обеспечивающая такой обмен, может быть

вьщелена, как самостоятельный линейный участок программы, для которого один из ожидаемых адресов А- - адрес следующей команды, а другой Ау - адрес данной команды, число тактовых

импульсов Т равно числу тактов прохождения данной команды.При этом уст- .ройство выполняет данный линейный участок в соответствии с описанием до момента прихода сигнала Готовность

бнешнего устройства.

Прием информации в счетчик 107 производится и при наличии импульса на его счётном входе (т.е. безусловно), так как управление по.

R,S-BXOAaM D-триггеров, составляющих счетчик 107, более приоритетно, чем управление по входу синхронизации С.

После загрузки Т на выходах

элементов ИЛИ 60 и 62 устанавливается единичное значение сигналов, а на выходе элемента ИЛИ-НЕ 59 - нулевое. Единичный сигнал с выхода элемента ИЛИ 60 поступает на входы 83 блока 56 счетчиков и 84 блока 57 мик-. ропрограммного управления. Единичное значение сигнала управления счетом тактов с входа 83 (фиг.8) поступает на второй вход элемента И 108 и открывают его для прохождения тактовых сигналов с входа 86 на счетный вход первого счетчика 107. Одновременно единичный сигнал с входа 83 поступает на вход инвертора 110, и

.нулевой сигнал с его выхода запирает элемент И 109, запрещая прохождение тактовых сигналов с входа 86 на счетный вход второго счетчика 107. Единичный сигнал с входа 81 бло-

ка 57 микропрограммного управления (фиг.7) поступает на четвертый вход регистра 104, на первом и втором входах которого присутствуют нулевые сигналы. Следующим тактовым сигналом информационное слово 1X00 записывается в регистр 104. На входах блока 105 постоянной памяти блока 57 микропрограммного управления устанавливается адрес 1100 и сигналы

33

на его выходах принимают значения, указанные в строке 13 табл.4. Единичный сигнал с выхода 78 блока 57 микропрограммного управления поступает на вход записи регистра 54, на информационный вход которого с выхода блока 58 постоянной памяти поступает информационное слово А, так как на вход младших разрядов адреса поступает с выхода 81 блока 57 микропрограммного управления информационное слово 00, в блоке 58 постоянной памяти выбирается ячейка В , В регистре 54 запоминается ожидаемый адрес Aj, Если очередной текущий адрес А, поступающий в регистр 52 с информационного входа 15 не равен ожидаемому А, сигнал на выходе схемы 55 сравнения сохраняет единичное значение, и в случае выполнения условия Т f О (единичный сигнал на первом адресном входе 84 блока 57 микропрограммного управления) на входах блока 105 постоянной памяти формируется адрес 1101, после чего процедура сравнения с текущим адресом повторяется для ожидаемого адреса А-. При выполнении условия А f А- цикл сравнения текущего адреса и вектора перехода повторяется для адресов следующих коман данного линейного участка рабочей программы.

Вьфаботка управляющих сигналов блоком 105 постоянной памяти в соответствии с табл.4 обеспечивается следующим образом.

Каждому из 16 наборов входных переменных на четырех адресных шин блока 105 постоянной памяти соответствуют значения сигналов на выходных линиях этого блока, представленные в табл.4. После снятия сигнала Общий сброс на входе 74 обращения блока 105 постоянной памяти устанавливается значение сигнала, соответству ющее режиму чтения информации из блока 105. В дальнейшем в процессе функционирования устройства блок 105 постоянной памяти постоянно находится в этом режиме. Каждое изменение значения хотя бы одного сигнала на адресных входах блока 105 постоянной памяти приводит к изменению его входных сигналов в соответствии с табл.4 Так, например, при изменении значе- ния сигнала на третьем входе 85 блок 105 из нуля в единицу при нулевых значениях сигналов на первом, втором и четвертом его входах значения вы

20зо

598134

ходных сигналов, установив1пиеся до этого изменения в соответствии с первой строкой табл.4, устанавливаются в соответствии со второй строкой с табл.4, т.е. значение сигнала на четвертом выходе 79 блока 105 переходит из единицы в нуль, причем сигналы на остальных его выходах сохраняют прежние значения.

fO В случае возникновения сбоя или неисправности, приводящей к обходу одной или нескольких команд, процес5

0 о

; 0 5

сор 1 может прийти в адрес А или

5

0

А до истечения установленного минимального числа Т тактовых импульсов. В этом случае сигнал на выходе схемы 55 сравнения принимает нулевое значение. Этот сигнал поступает на второй вход 85 блока 57 микропрограммного управления и далее на третий вход блока 105 постоянной памяти.На ,адресных входах блока 105 постоянной, 1памяти формируется адрес 1000 (выполнение условия А i А) или 1001 5 (вьтолнение условия А Ау), и на его выходах устанавливаются значения сигналов, указанные соответственно в строках 9 или 10 табл.4. Нулевой сигнал с выхода 77 блока 57 микропрограммного управления поступает на информационный вход триггера 63. На синхровход этого триггера с выхода схемы 55 сравнения по цепи 55-71-66- -63 поступает синхросигнал, и триггер 63 устанавливается в нулевое состояние. Единичный сигнал с инверсного выхода триггера 63 поступает на вход элемента И-НЕ 69, и сигнал на его выходе принимает нулевое значение. Этот сигнал поступает в процес- .сор 1 в качестве сигнала Запрос прерывания. Сигнал Подтверждение прерывания поступает по шине 14 управления на вход 19 признака перехода устройства 2 и далее на вход установки в О триггера 65, устанавливая его в нулевое состояние. Нулевой сигнал с прямого выхода триггера 65 поступает на второй вход элемента И-НЕ 69 и запрещает вьщачу сигнала Запрос прерывания. Одновременно единичный сигнал с инверсного выхода триггера 65 отпирает элемент И 68 для прохождения сигнала управления.

Процессор 1 приступает к обработке прерывания, связанного с сигналом от устройства 2 для контроля, и на адресном входе-выходе устанавли- .

35 - 13 ваются адреса программы прерывания. Ожидаемые адреса и А- продолжают поочередно сравнивать с текущими адресами А и на выходе схемы 55 устанавливается единичное значение сигнала. Блок 57 микропрограммного управ ления вьщает сигналы управления в соответствии со строками 13 и 14 табл.4 т.е. устройство 2 для контроля выполнения программ находится в состоянии ожидания.

Если при вьтолнении процессором 1 линейного участка L программы достигается условие Т, 0, сигнал на выходе элемента ИЛИ 60 принимает нулевое значение. Этот сигнал поступает на вход 83 блока 56 счетчиков и далее на второй вход элемента И 108 и через ин вертор 110 на второй вход элемента И 109. Элемент И 108 запирается, и первый счетчик 107 в дальнейшем находится в нулевом состоянии. Элемент И 109 отпирается для прохождения тактовых сигналов с входа 86 блока 56 счетчиков на счетный вход второго счетчика 107, где в дальнейшем происходит отсчет йТ. Одновременно нулевой сигнал с выхода элемента ИЛИ 60 Поступает на первый адресный вход J34 блока 57 микропрограммного управления, на выходах которого устанавливаются управляющие сигналы в соответствии со строками 5 или 6 табл.4, т.е. он продолжает оставаться в состоянии ожидания совпадения адресов.

Если при обработке процессором 1 линейного участка вьтолняется условие А А(А А-), блок 57 микропрограммного управления устанавливает на выходах значения сигналов, указанные в строке 1 (2) табл.4. Очередным тактовым сигналом в регистр 104 записывается информационное слово 0110 (0010), на адресных входах блока 105 постоянной памяти появляется адрес 0010, на выходах блока 57 микропрограммного управления устанавливаются управляющие сигналы в соответствии со строкой 3 табл.4.

Информационное слово 10 поступает С выхода 81 на вход младших разрядов адреса блока 58 постоянной памяти. Единичный (нулевой) сигнал с выхода 80 блока 57 микропрограммного управления поступает на управляющий вход 82 коммутатора 72 и подключает к выходам первую 89 или вторую 90 группу

входов. Информационное слово В J из ячейки 58 постоянной памя

98136

ти с адресом В + 3 поступает на вхо- ды коммутатора 72, и с его выхода на информационные входы регистра 53 поступает информационное слово Bj(B|).

Таким образом, происходит выбор массива информации для контроля следующего линейного участка L|(L-). Единичный сигнал с выхода 79 блока 57 микропрограммного управления посту0 пает на первьш вход элемента И 67 и

открьгоает его для прохождения сигна- . ла с выхода элемента ИЛИ 62 на вход сброса триггера 63. Если к моменту перехода на следующий линейный уча5 сток программы выполняется условие Т, 0, с выхода элемента ИЛИ 62 на вход сброса триггера 63 поступает нулевой сигнал и его состояние не изменяется. Если условие TO О не

0 выполняется, единичный сигнал с выхода элемента ИЛИ 62 сбрасывает триггер 63 в нулевое состояние и на его инверсном выходе устанавливается сигнал логической 1. Сигнал запроса

5 прерывания с выхода 21 устройства 2 для контроля выполнения программы поступает на вход прерывания процессора 1. Запрос прерывания в устройстве 2 для контроля выполнения про0 грамм микроэвм снимается сигналом Подтверждение прерывания процессора 1 в аналогичном порядке.

Следующим тактовым импульсом производится загрузка регистра 104, на

адресных входах блока 105 постоянной памяти устанавливается информационное слово 0011 и на выходах блока 57 микропрограммного управления устанавливаются управляющие сигналы в соот0 ветствии со строкой 4 табл.4. В результате воздействия этих сигналов на элементы устройства 2 для контроля вьшолнения программ происходит загрузка характеристического множе5 -ства Т.(тр в блок 56 счетчиков,после чего устройство подготовлено к контролю вьшолнения линейного участка L.(L-) программы микроЭВМ.

Если при поступлении Tj тактовых

0 импульсов не вьтолняется условие А А,-(А А j) , т.е. в результате сбоя или неисправности процессор 1 перешел к выполнению команды с произвольным адресом, минуя адрес А(А;),

5 сигнал на выходе схемы ИЛИ-НЕ 59 принимает единичное значение. Этот сигнал поступает на синхровход триггера 64 и под воздействием нулевого сигнала на информационный вход это-

го триггера, поступающего с выхода элемента ИЛИ 60, он переходит в нулевое состояние. Сигнал с выхода триггера 64 поступает на вход элемен- та И 66, а с его выхода - на синхро- вход триггера 63. Нулевой сигнал, поступающий на информационный вход триггера 63 с выхода 77 блока 57 микропрограммного управления (табл.4,строки 5 и 6), запоминается в триггере 63, на его инверсном выходе устанавливается сигнал логической 1 и с выхода элемента И-НЕ 69 на вход прерывания процессора 1 поступает сигнал запроса прерьшания. Процессор 1 обрабатывает этот запрос в рассмотренном ранее порядке.

Снятие сигнала запрета прерывания в устройстве 2 для контролй выполнения программ микроэвм происходит либо 20 ка лТ при этом остается ненулевым и

по сигналу Общий сброс по цепи 17-61-63(65), либо по сигналу записи информации, поступающему в такте загрузки блока 56 счетчиков (табл.4, строки 4, 8, ,12 и 16) с выхода 76 блока 57 микропрограммного управления по цепи 76-70-68-61-63(65) на установочные входы триггера 63 и 65.

При поступлении в процессор 1 сигнала прерывания от внешнего устро- ЗО в запланированный момент 158 времени.

сигнал на синхровходе триггера 64 сохраняет нулевое значение (эпюра 156)

Если в результате воздействия помехи (условно представлена импульсом 25 157), приводящей к выполнению ошибочного перехода в пределах линейного участка программы, сравнение текущего адреса А и одного из ожидаемых адресов А . (или А;) произойдет не

йства управление с линейного участка передается программе прерывания. Устройство 2 для контроля выполнения программ микроэвм обнаруживает выход из рабочей программы по прерыванию по истечении Tj тактов с момента начала данного линейного участка и устанавливает триггер 63 в нулевое состояние. В момент передачи управлени на программу обработки внешнего прерывания процессор 1 вьщает сигнал Подтверждение прерывания, который запрещает выдачу сигнала прерывания из устройства 2 для контроля выполнения программ. После возвращения процессора 1 из программы обработки прерьшания на незавершенный линейный участок он достигает одного из ожидаемых адресов и происходит самосинхронизация устройства 2 для контроля и процессора 1 путем загрузки служебной информации о следующем линейном участке в блок 56 счетчиков и регистр 53 и установки триггеров 63 и 65 в единичное состояние.

Работа устройства 2 по второму варианту (фиг.З) поясняется временными диаграммами (фиг.16, а, б, в), отображающими процесс загрузки (моменты 145 и 146 времени) и постепенного уменьшения содержимого счетчиков Т (эюра 147), лТ (эпюра 148) и трех счетчиков Т,, (эпюры 149-151). В момент 152 времени (фиг.16,а) содержимое счетчика Т становится равным нулю (эпюра 147) и на информационном входе триггера 64 устанавливается нулевое значение сигнала (эпюра 153). С этого момента времени происходит уменьшение .содержимого счетчика Т. В момент 154 времени происходит совпадение текущего адреса программы А и одного из ожидаемых адресов А, (нпи А,-). Импульс 155 совпадения формируется на синхронизирующем входе триггера 63 в момент перехода микроэвм на начало следующего линейного участка. Содержимое счетчив запланированный момент 158 времени.

сигнал на синхровходе триггера 64 сохраняет нулевое значение (эпюра 156).

Если в результате воздействия помехи (условно представлена импульсом 157), приводящей к выполнению ошибочного перехода в пределах линейного участка программы, сравнение текущего адреса А и одного из ожидаемых адресов А . (или А;) произойдет не