4 ND

4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения микро-ЭВМ с табло индикации | 1986 |

|

SU1376090A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИСПРАВЛЯЮЩЕЙ СПОСОБНОСТИ ПРИЕМНИКОВ ДИСКРЕТНЫХ СИГНАЛОВ | 1992 |

|

RU2040118C1 |

| Программное устройство для фиксации и документирования времени | 1989 |

|

SU1677691A1 |

| Устройство для вывода информации | 1986 |

|

SU1377849A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Телеизмерительное устройство | 1983 |

|

SU1116448A1 |

| Устройство для формирования тестов | 1988 |

|

SU1573457A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1988 |

|

SU1594554A1 |

| Устройство для отображения многоугольников на экране растрового графического видеоконтрольного блока | 1987 |

|

SU1534454A1 |

| Устройство для сопряжения электронно-вычислительной машины с табло индикации | 1984 |

|

SU1211739A1 |

Изобретение относится к оГласти автоматики и вычислительной техники и может быть использовано в устройствах, обеспечивающих информационный обмен с ЭВМ по двухпроводному интерфейсу ввода-вывода. Цель изобретения - повьшение надежности работы устройства за счет уменьшения количества оборудования и линий связи между блоками устройства. Устройство для обмена информацией содержит элемент ИЛИ 1, блок формирования сдвигающих импульсов 2, регистр сдвига 3, блок формирования флагов 4, два блока памяти 3, 6, шинный формирователь данных 7, элемент НЕ-ИЛИ-НЕ 8, блок формирования управляющих сигналов 9, элемент И 10, три инвертора 11,12,13, 5 ил.

f

Изобретение (пкн ится к ап с мати- ке н вычислительной технике и может быть исполгззовано R устройствах, обеспечивающих шгформационный с ЭВМ по двухпронодкому интер(Ьейсу ввода - вывода.

Целью изобретения является i.oBt.me ние надежности работы устройства путем умен1,шения количества оборудова- ния и линий связи между блоками устройства .

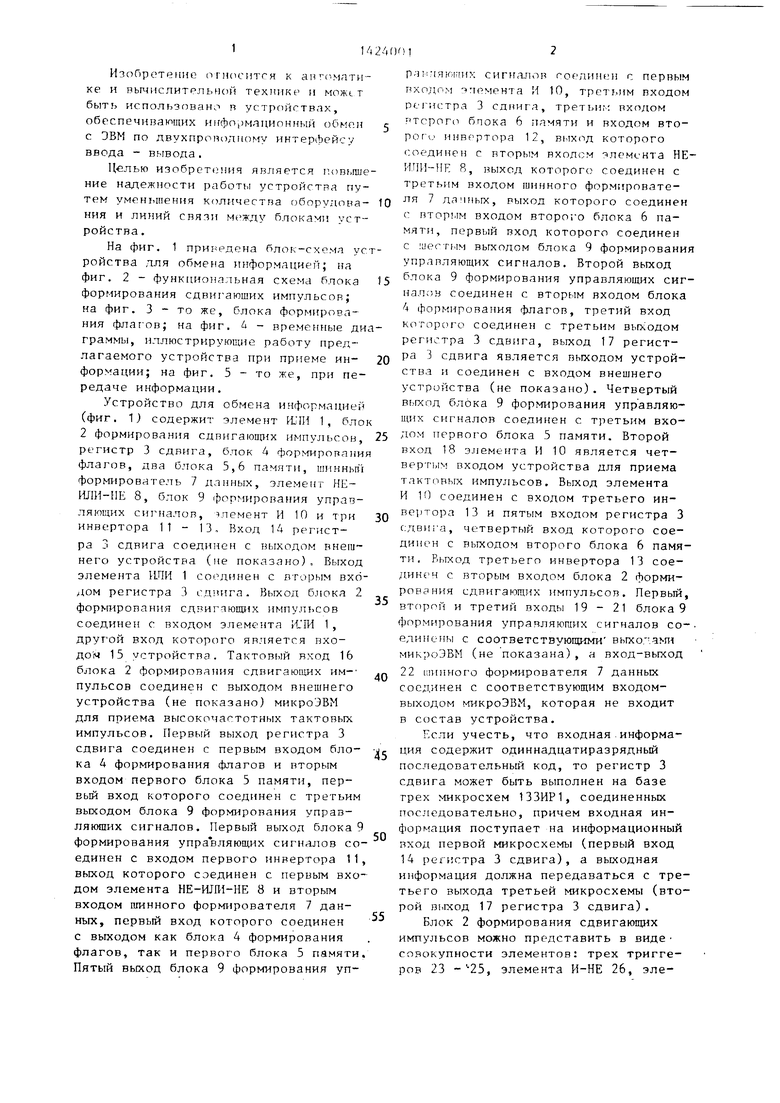

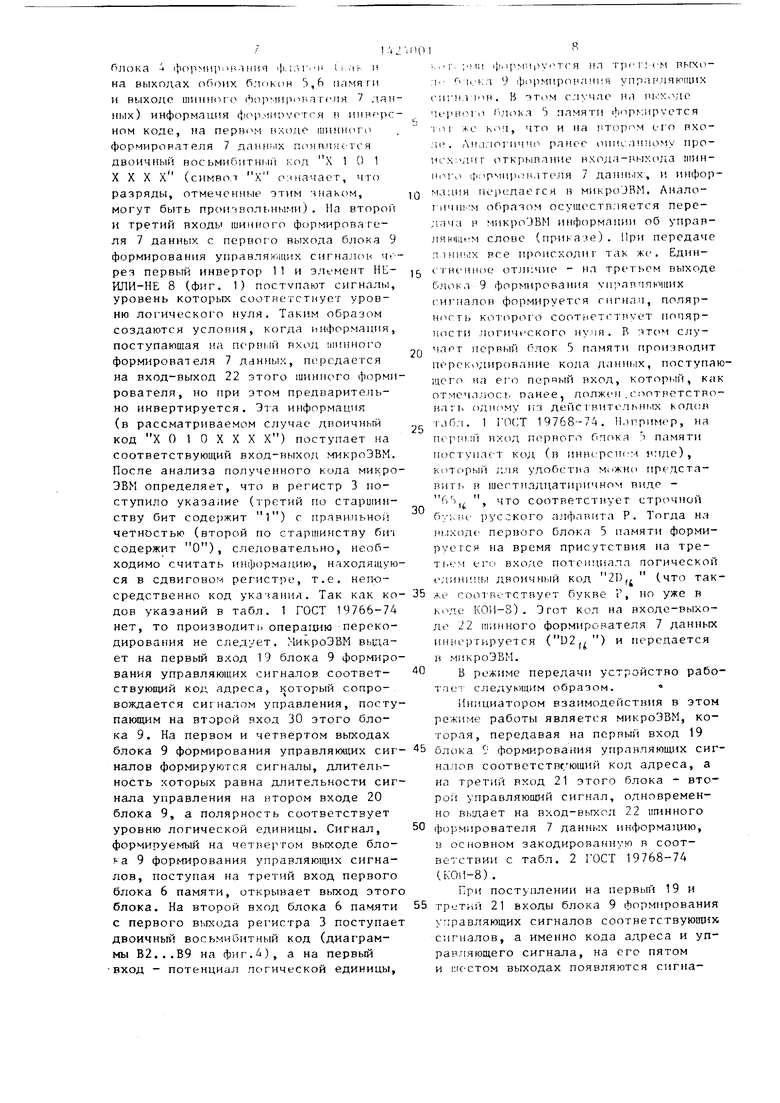

На фиг, 1 приредена блок-схема усройства для обмена информацией; на фиг. 2 - функцио}1альная схема блока формирования сдвигающих импульсов; на фиг. 3 - то же, блока формирования флагов; на фиг, - временные диграммы, иллюстрирующие работу предлагаемого устройства при приеме ин- формации; на фиг, 5 - то же, при передаче информации.

Устройство для обмена информацией (фиг, 1) содержит элемент FL IH 1, бло 2 формирования сдвигаюишх импульсов, регистр 3 сдвига, блок 4 формиропани флагов, два блока 5,6 памяти, шинны формирователь 7 данных, элемент НЕ- 8, блок 9 формирования управляющих сигналов, элемент И 10 и три инвертора П - 13, Вход 14 регистра 3 сдвига соединен с выходом внега него устройства (не показано). Выход элемента 1ШИ 1 соединен с вторым входом регистра 3 сдвига. Выход блока 2 формирования сдвигающих импульсов соединен с входом элемента ИЛИ 1, другой вход которого является вхо- до м 15 устройства. Тактов 1й вход 16 блока 2 формирования сдвигающих им-- пудьсов соединен с выходом внешнего устройства (не показано) микроЭВМ для приема высокочастотных тактовых импульсов. Первый выход регистра 3 сдвига соединен с первым входом бдо- ка А формирования флагов и вторым входом первого блока 5 памяти, первый вход которого соединен с третьим выходом блока 9 формирования управляющих сигналов. Первый выход блока 9 формирования упра вляющих сигналов соединен с входом первого инвертора 11 выход которого сэединен с первым входом элемента НЕ-ИЛИ-НЕ 8 и вторым входом шинного формирователя 7 данных, первый вход которого соединен с выходом как блока 4 формирования флагов, так и первого блока 5 памяти Пятый выход блока 9 формирования уп

O

50

5 0 Q ,

5

0

5

сигналов соединен с первым г ходом элемента Н 10, третьим входом pti-истра 3 сдгшга, третьи;: входом ртсрого бпока 6 памяти и входом вто- роги инвертора 12, выход которого соединен с вторым входом элемента НЕ- ИЛ11- 1Е 8, выход которого соединен с третьим входом шинного формирователя 7 данных, выход которого соединен с вторым входом второго блока 6 памяти, первый вход которого соединен с шестым выходом блока 9 формирования управляющих сигналов. Второй выход блока 9 формирования управляющих сиг- нал;)в соединен с вторым входом блока 4 формирования флагов, третий вход которого соединен с третьим выходом регистра 3 сдвига, выход 17 регистра 3 сдвига является выходом устройства и соединен с входом внешнего устройства (не показано). Четвертый вькод блока 9 формирования управляющих сигналов соединен с третьим входом первого блока 5 памяти. Второй вход 18 элемента И 10 является четвертым входом устройства для приема тактовых импульсов. Выход элемента И Ю соединен с входом третьего инвертора 13 и пятым входом регистра 3 сдвига, четвертый вход которого соединен с выходом второго блока 6 памяти. Вькод третьего инвертора 13 соединен с вторым входом блока 2 формирования сдвигающих импульсов. Первый, второй и третий входы 19 - 21 блока 9 формирования управляющих сигналов со-. единены с соответствующими Bhrxo: aNni микроэвм (не показана) , а вход-выход 22 шинного формирователя 7 данных соединен с соответствующим входом- выходом микроэвм, которая не входит в состав устройства.

Если учесть, что входная информация содержит одиннадцатиразрядный последовательный код, то регистр 3 сдвига может быть выполнен на базе трех микросхем 133ИР1, соединенных последовательно, причем входная информация поступает на информационный вход первой микросхемы (первый вход 14 регистра 3 сдвига), а выходная информация должна передаваться с третьего выхода третьей микросхемы (вто рой выход 17 регистра 3 сдвига),

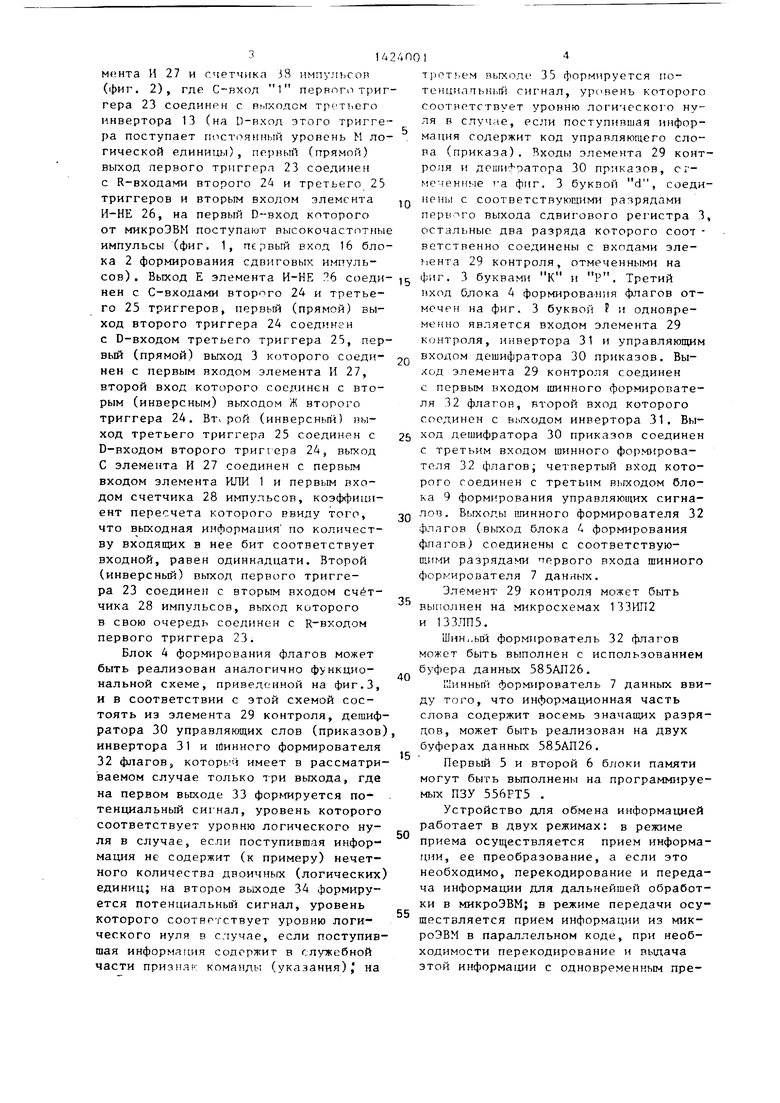

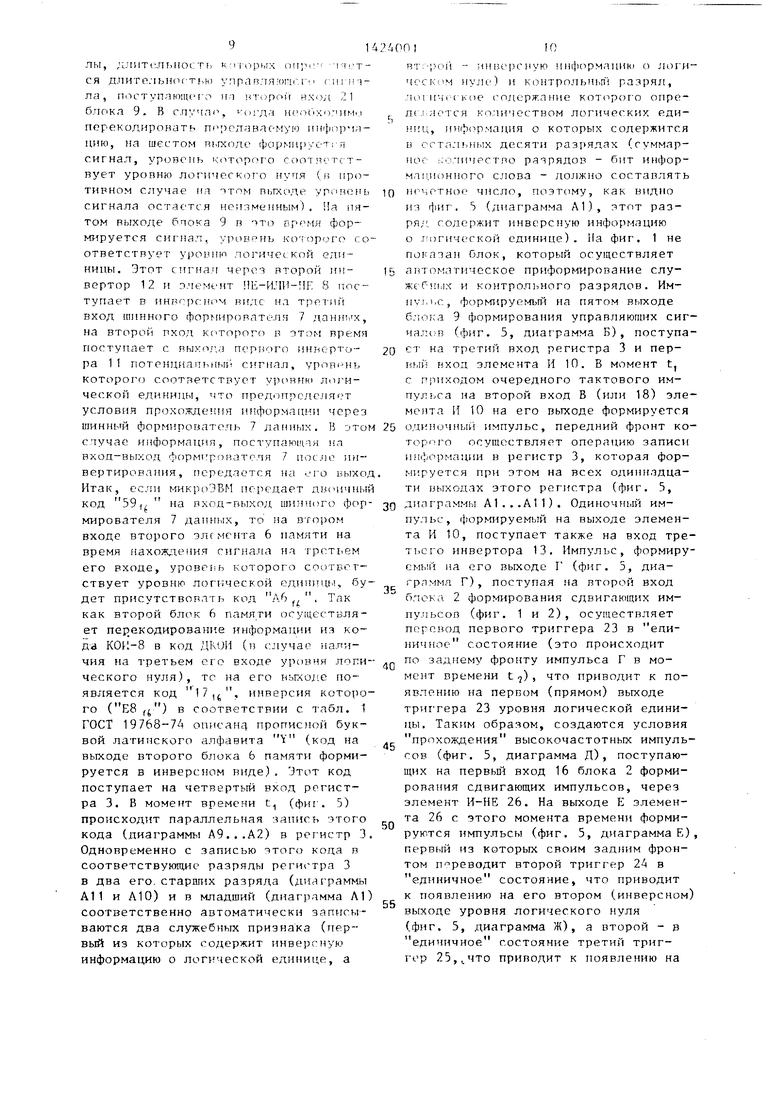

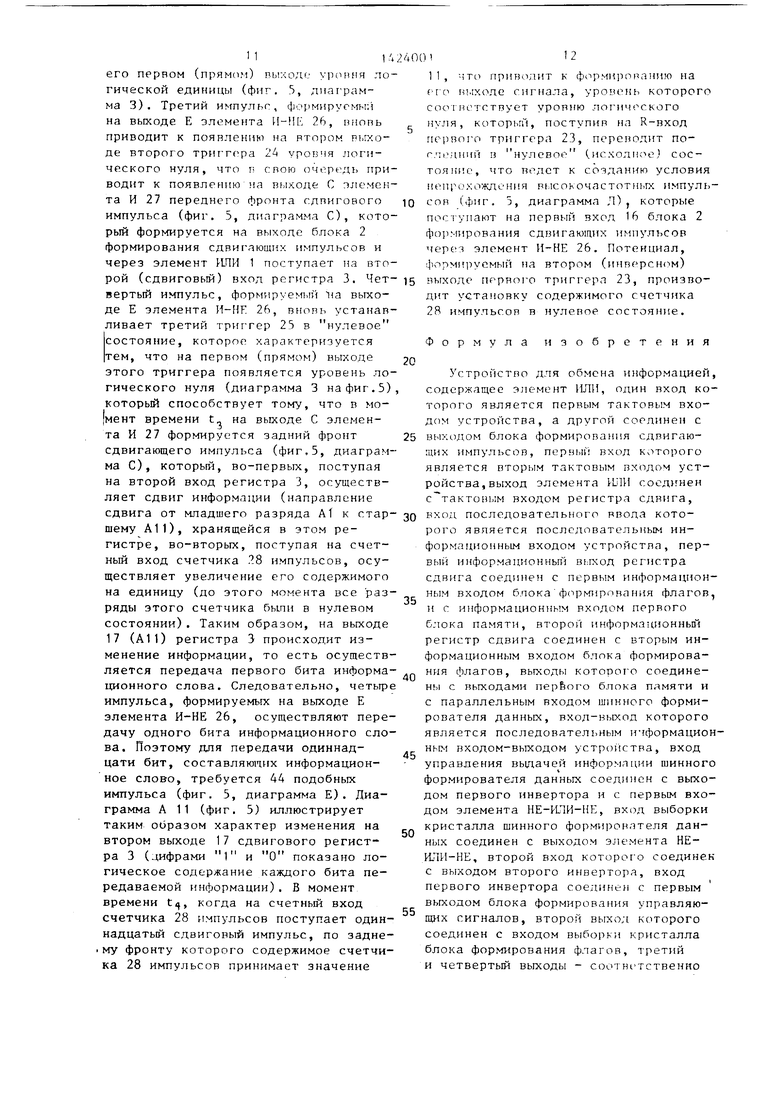

Блок 2 формирования сдвигающих импульсов можно представить в виде совокупности элементов: трех триггеров 23 , элемента И-НЕ 26, элем нта И 27 и счетчика 38 импульсов (фиг. 2), где С-вход 1 первого триггера 23 соединен с Bf.rxoACM третьего инвертора 13 (на D-вход этого триггера поступает пост1 янный уровень М логической единицы) , первьп (прямой) выход первого трнггерл 23 соедине 1 с R-входами второго 24 и третьего 25 триггеров и вторым входом элемента И-НЕ 26, на первый D-вход которого от микроэвм поступают высокочастотные импульсы (фиг. 1, первый вход 16 блока 2 формирования сдвиговых импульсов) . Выход Е элемента И-НЕ 26 соединен с С-входами второго 24 и третьего 25 триггеров, первый (прямой) выход второго триггера 24 соединен с D-входом третьего триггера 25, первый (прямой) выход 3 которого соединен с первым входом элемента И 27, второй вход которого соединен с вторым (инверсным) вьгходом Ж второго триггера 24. BTi рой (инверсный) выход третьего триггера 25 соединен с D-входом второго триггера 24, выход С элемента И 27 соединен с первым входом элемента ИЛИ 1 и первым входом счетчика 28 импульсов, коэффициент пересчета которого ввиду того, что выходная информация по количеству входящих в нее бит соответствует входной, равен одиннадцати. Второй (инверсный) выход первого триггера 23 соединен с вторым входом чика 28 импульсов, выход которого в свою очередь соединен с R-входом первого триггера 23.

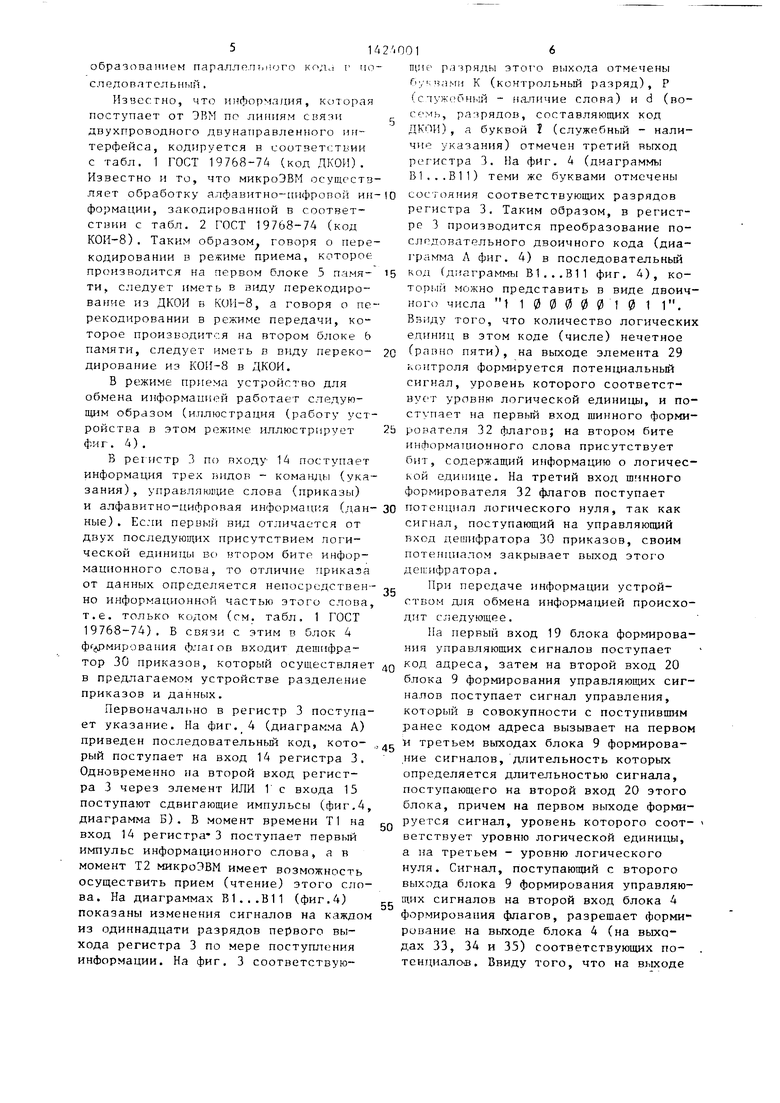

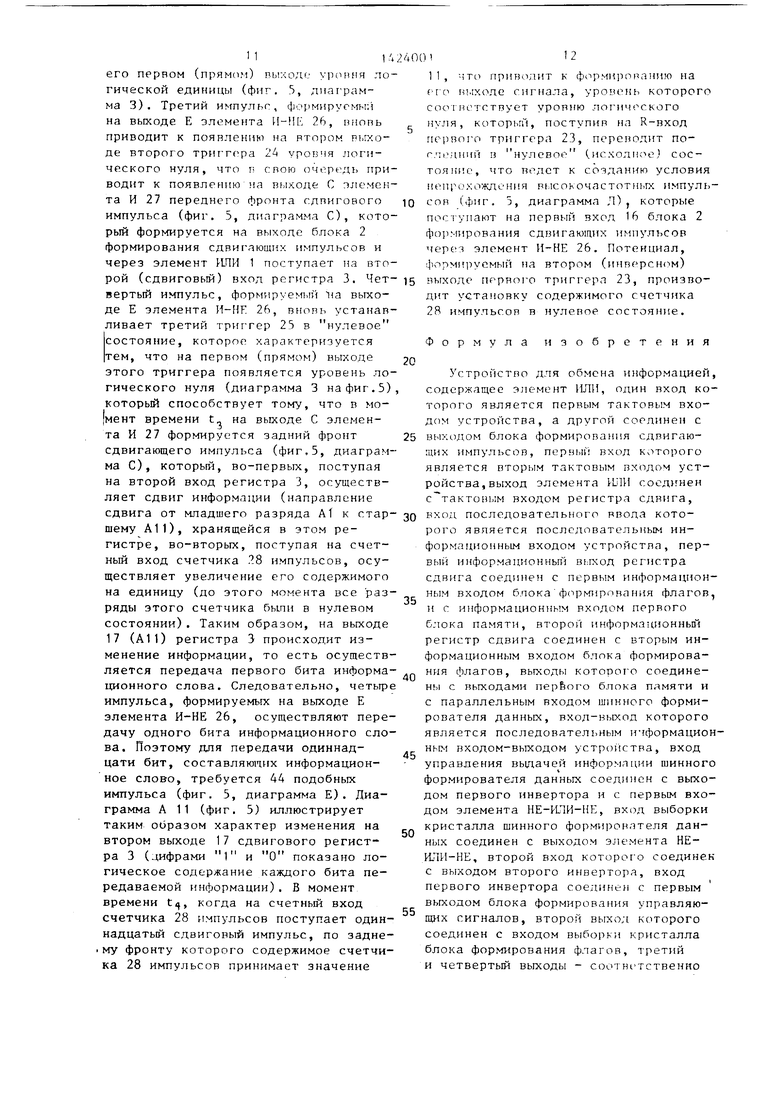

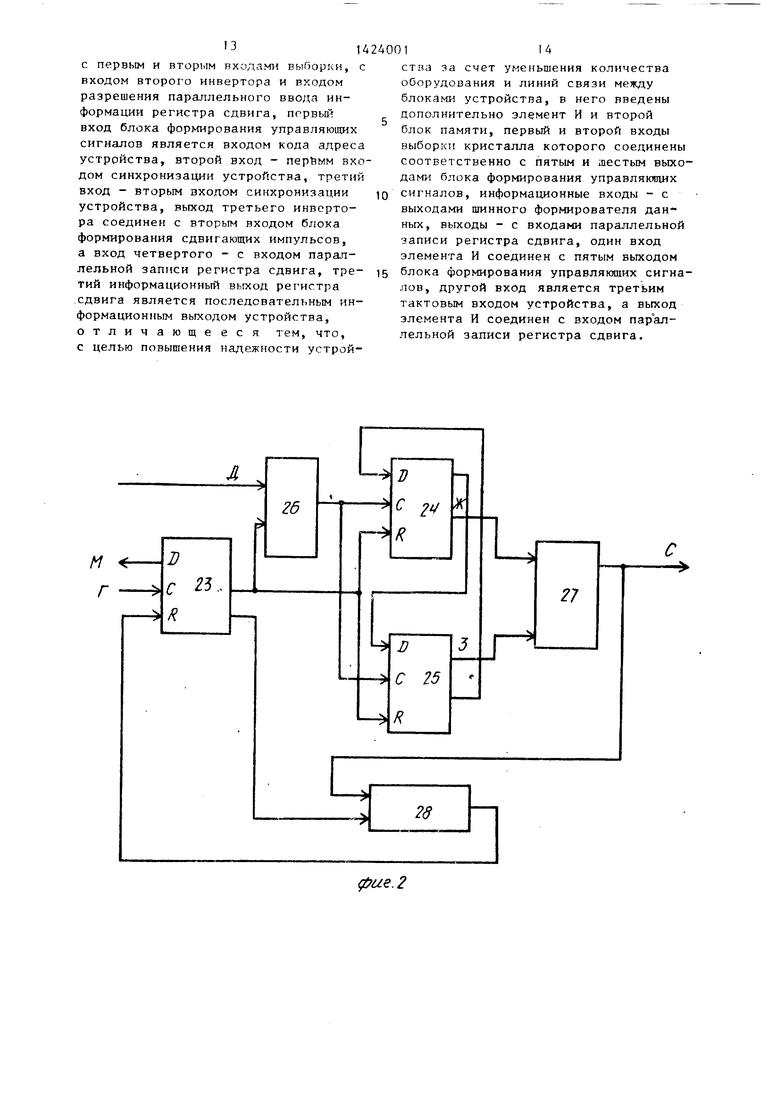

Блок 4 формирования флагов может быть реализован аналогично функциональной схеме, приведенной на фиг.З, и в соответствии с этой схемой состоять из элемента 29 контроля, дешифратора 30 управляющих слов (приказов) инвертора 31 и 1йинного формирователя 32 флагов, который имеет в рассматриваемом случае только три выхода, где на первом выходе 33 форктруется потенциальный сигнал, уровень которого соответствует уровню логического нуля в случае, если поступившая информация не содержит (к примеру) нечетного количества двоичных (логических) единиц; на втором вьосоде 34 формируется потенциальный сигнал, уровень которого соответствует уровню логического нуля в случае, если поступившая информация содержит в служебной части призняк команды (указания), на

0

5

0

5

0

5

0

5

0

5

TjiOTbeM выходе 35 формируется по- тенциллыпл сигнал, уровень которого соответствует уровню логического нуля в случае, если поступившая информация содержит код управляющего слова (приказа). Входы элемента 29 контроля и дeши(paтopa 30 приказов, отмеченные га фиг, 3 буквой d, соединены с соответствующими разрядами первого выхода сдвигового регистра 3, остальные два разряда которого соот ветственно соединены с входами эле- тчента 29 контроля, отмеченными на фиг. 3 буквами К и Р. Третий нход блока 4 формирова-ния флагов отмечен на фиг. 3 буквой f и одновременно является входом элемента 29 контроля, HiiBepTopa 31 и управляющим входом дешифратора 30 приказов. Выход элемента 29 контроля соединен с первым входом шинного формирователя 32 флагов, второй вход которого соединен с выходом инвертора 31. Выход дешифратора 30 приказов соединен с третьим входом шинного формирователя 32 флагов; четвертый вход которого соединен с третьим выходом блока 9 формирования управляющих сигналов. Выходы шинного формирователя 32 фллгов (выход блока 4 формирования ) соединены с соответствующими разрядаьда первого входа шинного формирователя 7 данных.

Элемент 29 контроля может быть выполнен на микросхемах 133ИП2 и 133ЛП5.

Шин,.ый формирователь 32 флагов может быть выполнен с использованием буфера данных 585АП26.

Линный формирователь 7 данных ввиду того, что информационная часть слова содержит восемь значаш 1х разрядов, может быть реализован на двух буферах данных 585АЛ26.

Первый 5 и второй 6 блоки памяти могут быть вьшолнены на программируемых ПЗУ 556РТ5 .

Устройство для обмена информацией работает в двух режимах: в режиме приема осуществляется прием информации, ее преобразование, а если это необходимо, перекодирование и передача информации для дальнейшей обработки в микроэвм; в режиме передачи осуществляется прием информации из мик- роЭВМ в параллельном коде, при необходимости перекодирование и выдача этой инфopмaц)и с одновременным пре5U

образованием паралло.пт.пого KO;U г последовательный .

Известно, что информация, которая поступает от ЭВМ по связи двухпроводного двунаправленного интерфейса, кодируется в соответствии с табл. 1 ГОСТ 19768-74 (код ДКОИ). Известно и то, что микроЭВМ осуществляет обработку алфавитно- П1фровой информации, закодированной в соответствии с табл. 2 ГОСТ 19768-74 (код КОИ-8). Таким образом говоря о перекодировании в режиме приема, которое производится на первом блоке 5 памяти, следует иметь в виду перекодирование из ДКОИ в КОИ-8, а говоря о перекодировании в режиме передачи, которое производится на втором блоке 6 памяти, следует иметь в виду перекодирование из КОИ-8 в ДКОИ,

В режиме приема устройство для обмена информацией работает следующим образом (иллюстрация (работу устройства в этом режиме иллюстрирует фиг, 4).

В регистр 3 по входу- 14 поступает информация трех видов - команды (указания) , управляющие слова (приказы) и алфавитно-цифровая информация (данные) . Если первый вид отличается от двух последующих присутствием логической единицы во втором бите информационного слова, то отличие приказа от данных определяется непосредственно информационной частью этого слова, т.е. только кодом (см. табл, 1 ГОСТ 19768-74). В связи с этим в блок 4 фf миpoвaния флагов входит дешифратор 30 приказов, который осуществляет в предлагаемом устройстве разделение приказов и данных.

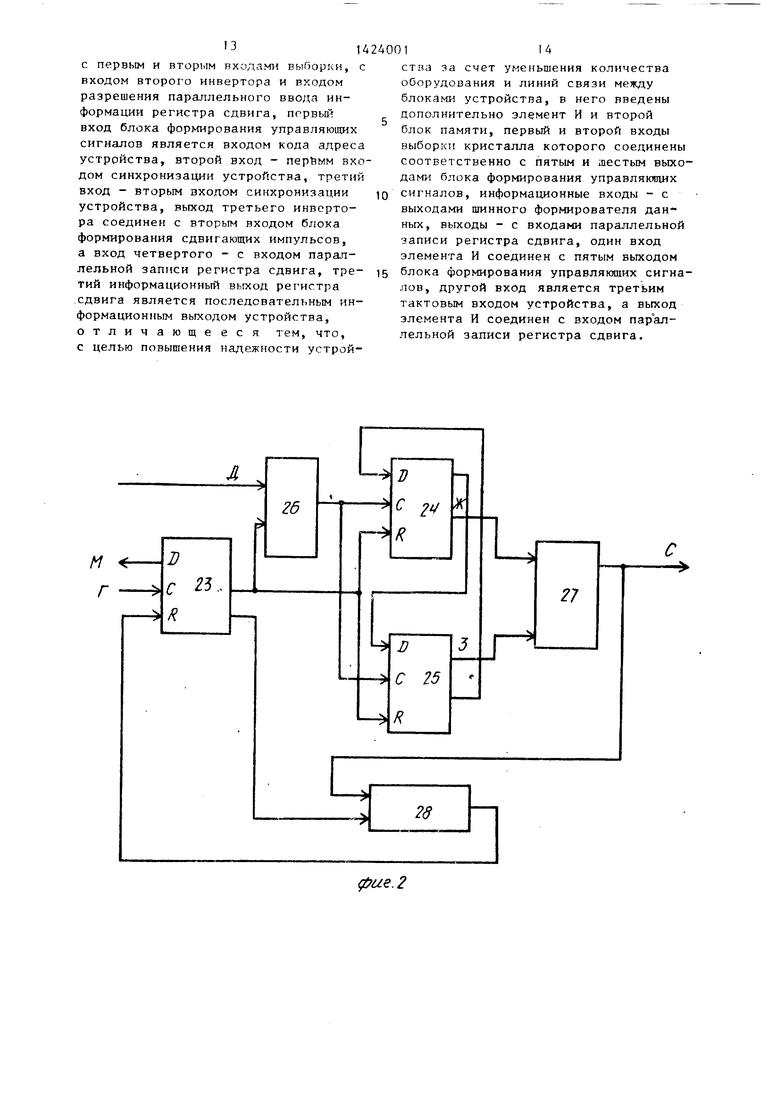

Первоначально в регистр 3 поступает указание. На фиг.4 (диаграмма А) дриведен последовательньш код, кото- рый поступает на вход 14 регистра 3. Одновременно на второй вход регистра 3 через элемент ИЛИ 1 с входа 15 поступают сдвигающие импульсы (фиг,4, диаграмма Б). В момент времени Т1 на вход 14 регистра-3 поступает первый импульс информашюнного слова, а в момент Т2 микроэвм имеет возможность осуществить прием (чтение) этого слова. На диаграммах В1...В11 (фиг.4) показаны изменения сигналов на каждом из одиннадцати разрядов первого выхода регистра 3 по мере поступления информации. На фиг. 3 соответствую5

40016

niHf: разряды этот о выхода отмечены буч нами К (контрольный разряд), Р (служебный - наличие слова) и d (восемь, разрядов, составляющих код ДКОИ), а буквой 1 (служебный - наличие указания) отмечен третий выход регистра 3. На фиг. 4 (диаграммы В1...В11) теми же буквами отмечены

О состояния соответствующих разрядов регистра 3. Таким образом, в регистре 3 производится преобразование последовательного двоичного кода (диа- граьгма Л фиг. 4) в последовательный

5 код (диаграммы В1..,В11 фиг. 4), который можно представить в виде двоич- ног( числа 1 1 000001 0 1 1. Ввиду того, что количество логических единиц в этом коде (числе) нечетное

0 (равно пяти), на выходе элемента 29 контроля формируется потеН1у1альный сигнал, уровень которого соответствует уровню логической единицы, и поступает на первый вход шинного формиЬ рователя 32 флагов; на втором бите информационного слова присутствует бит, содержащий информацию о логической единице. На третий вход шинного формирователя 32 флагов поступает

0 потенциал логического нуля, так как сигнал, поступающий на управляющий вход дешифратора 30 приказов, своим потенциалом закрывает выход этого деп;ифратора.

При передаче информации устройством для обмена информацией происходит следующее.

Па первый вход 19 блока формирования управляющих сигналов поступает

д код адреса, затем на второй вход 20 блока 9 формирования управляющих сигналов поступает сигнал управления, который в совокупности с поступившим ранее кодом адреса вызывает на первом

и третьем выходах блока 9 формирование сигналов, длительность которых определяется длительностью сигнала, поступающего на второй вход 20 этого блока, причем на первом выходе форми руется сигнал, уровень которого соответствует уровню логической единицы, а на третьем - уровню логического нуля. Сигнал, поступающий с второго выхода блока 9 формирования управляющих сигналов на второй вход блока 4 формирования флагов, разрешает формирование на выходе блока 4 (на выхд- дах 33, 34 и 35) соответствующих по- тенциалоа. Ввиду того, что на в гходе

5

/l-Wi(Kn

блока Д форМИ11 Ц.1 ПИЯ фЛГ,Г1 И U., lb и-..iM . ; М1 llj.lJlM .lpVfM Cn НЛ TpcrM. hf РЫХОна выходах обоих блоков 5,6 памяти:i бч.-кл 9 формчро(амин упраг ляющих и выходе ишииогч, форми 1от ателя 7 дан-сигклюн. В этом сгр. чае на пыходс ных) информация фор шпуется и инрерс- .Ч1 ри ч о б. кчка 5 памяти .иpveтcя ном коде, на первом нходо шинного . i i г же , что и на у тором его пхо- формирователя 7 дaнtli,lx Ра1япля :тгя:U . Аналогично ранее oпиcaнIlo гy про- двончиый восьмибитны код Х 1 О 1ис-х:миг (чткрыпаиие входа-ныул да шин- X X X X (символ Х о;1начает, чтоного )Iiaтe,пя 7 данных, и. инфор- разряды, отмеченные этим чнакс)М, IQмлния персшаегся в микро ЗВМ, Лнало- могут быть про1пвол1,ныг-1и) . На второйтичн.:м обраяом осуществляется перо- н третий входь шинного формироваге-Л.пча i микроЭВМ информации об управ- дя 7 данных с первого выхода блока 9лянши м слове (приказе). При передаче формирования управляющих сигналов чг--ллнн лх все происходит так же. Един- рез первый инвертор П и элемент НЕ- с,сч всмпюе отличие - на третьем выходе ИЛИ-НЕ 8 (фиг. 1) поступают сигналы,блока 9 формирования уцравппющих уровень которых соотпетстнует уров-сигналов формируется сигнал, поляр- ню логического нуля. Таким образомн,,,,, которог о соотнетстнует попяр- создаются условия, когда информация,„.„ логического ну.чп. В этом слу- поступающая на первый вход шинного,,,. первый блок 5 памяти производит формирователя 7 данных, передаетсяперекодирование кода данных, поступаю- на вход-выход 22 этого шинного форми-.р., „,, р,,,-, „еряый вход, который, как рователя, но при этом предваритель-отмечплос, панее, должен . соответство- но инвертируется. Эта информациянагь одн(1му из действительных кодон (в рассматриваемом случае двоичный „члб;. 1 ГОСТ 19768-74. Il.), на код Х О 1 О X X X X) поступает нагтер и,й нхс Д первого блока памяти соответствующий вход-выход микроЭВМ.поступает код (в инвс. рснсм имде) , После анализа полученного кода мик:ро-которь|й удобства можно предста- ЭВМ определяет, что в регистр 3 по-вить н шестнадцатирично виде - ступило указа;1ие (третий по старшин- о соответствует строчной

ству бит содержит 1) с правильной русского алфавита Р. Тогда на четностью (второй по старшинству бит выходе первого блока 5 памяти форми- содержит О), следовательно, необ- iv/ется на время присутствия на тре- ходимо считать информацию, находящую- тьем erij входе потенциала аогической ся в сдвиговом регистре, т.е. непо- единицы двоичный код 21, (что так- средственно код указания. Так как ко- 35 же соответствует букве Р, но уже в ДОН указаний в табл. 1 ГОСТ 19766-74 коде КОИ-8). Этот код на входе-выхо- нет, то производить опера1 шю переко- де 22 шинного формирователя 7 данных дирования не следует. МикроЭВМ вьи;а- иинертируется (U2) и передается ет на первый вход 19 блока 9 формиро- в микроЭВМ.

вания управляющих сигналов соответ- В режиме передачи устройство рабо- ствующий код адреса, который сопро- тает следующим образом. вождается сигналом управления, посту- Инициатором взаимодействия в этом пающим на второй вход 30 этого бло- режиме работы является микроЭВМ, кока 9 . На первом и четвертом выходах торая, передавая на первый вход 19 блока 9 формирования управляющих сиг- Ь блока формирования управляющих сигналов формируются сигналы, длитедь- налов соответствующий код адреса, а ность которых равна длительности сиг- на третий вход 21 этого блока - вто- нала управления на втором входе 20 рой управляющий сигнал, одновремен- блока 9, а полярность соответствует но выдает на вход-вьг :од 22 итнного уровню логической единицы. Сигнал, 50 формирователя 7 данных информацию, формируемый на четвертом выходе бло- в основном закодированную в соот- ка 9 формирования управляющих сигна- ветствии с табл. 2 ГОСТ 19768-74 лов, поступая на третий вход первого (KOil-8) .

блока 6 памяти, открывает выход этого При поступлении на первьп 19 и блока. На второй вход блока 6 памяти 55 третий 21 входы блока 9 формирования с первого выхода регистра 3 поступает управляющих сигналов соответствующих двоичный восьмибитный код (диаграм- сигналов, а именно кода адреса и уп- мы В2...В9 на фиг.4), а на первый равляющего сигнала, на его пятом вход - потенциал логической единицы, и текстом выходах появляются сигнаЛЫ, ,ЧЛЯТ(ШТзКО(:ТГ1 К:Г| Г|рьГХ ПЧ М:-- I ll Tся длнтплы-(1(-тьн) упрлпля;о1игл ,1 cnj мч- ла, поступающс го ип нтпрой вхгьч 21 блока 9. В ( когда .- им..) перекодировать псролаваемую иш юрчл- цию, на шестом ш.гхолс формирчч Тсл сигнал, уровснр, icoroporo соотнегс твует уровню логичсгкот о нупя

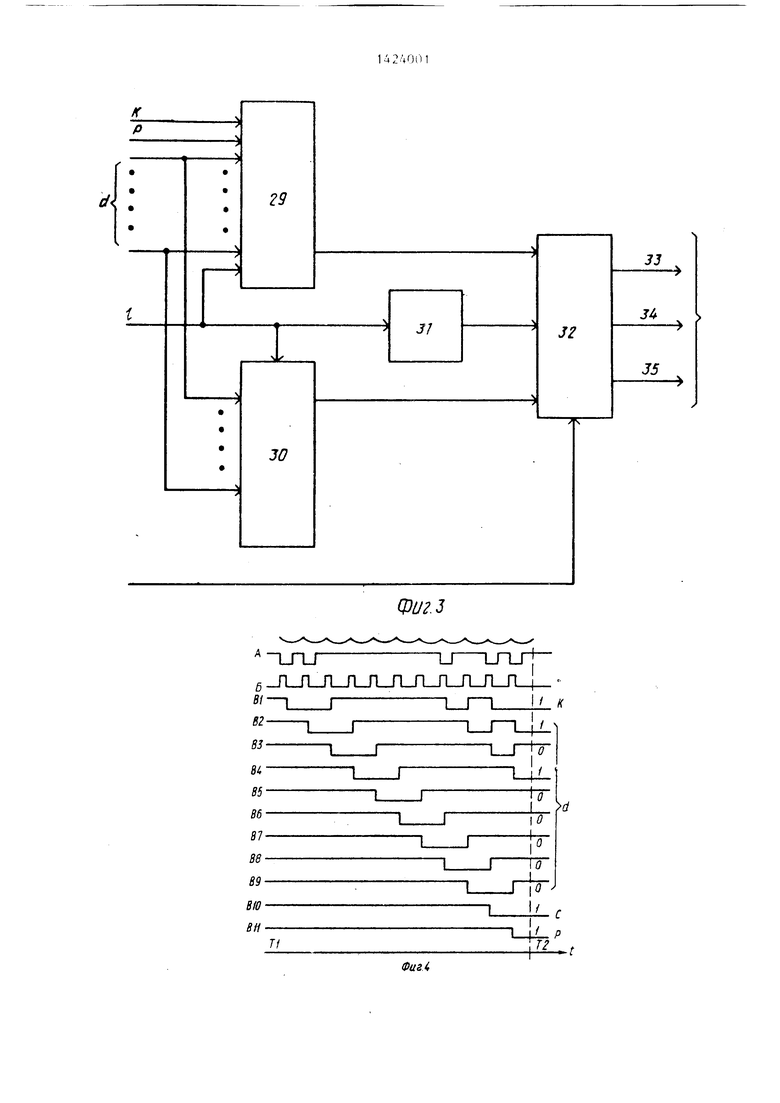

противном случае ип ттпм пькоде yponeiib сигнала остас тся но 1пменным) . Па пятом врлходе блока 9 в время формируется сигнал, yiioBPHb ко Г-ор(.го соответствует уровню логической единицы. Этот сигнал через второй инвертор 12 и элемент 1Е-ИЛ11- Е 8 поступает в инверсном виде нл третий вход шинного формировате.п.ч 7 даннь х, на второй BXO7I которого в этог- время поступает с выхо/ ,:з первого инвертора 11 потенциапттньп сигнал, уровень KOToporcj соответствует yi oBUKi логической единицы, ifTo пред|)прсделя т условия прохожде шя и.иформащп через шинный формирователь 7 данных. В этом случае информация, поступающая на вход-выход формт ропатс-ля 7 после инвертирования, передается на ого выход Итак, селя микроэвм передает двоичн код 591, на вход-выход шилного формирователя 7 данных, то на втором входе второго элcмe ггa 6 памяти на время пахожде 1ия сигнала на третх.ем его входе, уровень которого соответствует уровню лоп;ческой едиштцы, будет присутствовать код Лб, Так как второй блок 6 памяти осуществляет пег екодирование информации из кода КОИ-8 в код (тз случае наличия на третьем его входе уровня логического нуля), тс на его иькоде по- является код /к, инверсия которого (Е8 ) в соответствии с табд. 1 ГОСТ 19768-7А описанд прописной буквой латинского алфавита Y (код на выходе второго блока 6 памяти формируется в инверсном виде) . Эт(.1Т код поступает на четвертый вход регистра 3. В момент времени t (фиг. 5) ПРОИСХОДТ1Т параллельная запись этого кода (диаграммы А9...А2) в регистр 3, Одновременно с записью этогс5 кода в соответствующие разряды регистра 3 в два его. старших разряда (диаг раммы All и А10) ив младший (диаграмма А1) соответственно автоматически записываются два служебных признака (первый из которых содержит инверсную информацию о логической единице, а

Ь

10

40П)К)

тгг:-;)О11 - иние)сную информацию о лог И- ческям нуле) и контрольньп разряд, . НИ 11Ч1-С кое со;(сржание опре- д(ьяется количеством логических единиц, пнг(рмация о которых содержится в сста:1)Ных десяти разрядах (суммарное i.Li.-nniecTno разрядов - бит информационного слова - должно составлять Н 1етное число, поэтому, как видно из фиг, 5 (диаграмма А1), этот раз- ря/ , содержит инверсную информацию о .логической единице). На фиг. 1 не показан блок, который осуществляет

15 amoMaTinjocKoe приформирование слу- ж б плх и KoHTponiiHoro разрядов. Им- нуы.с, формируемый на пятом выходе бло1;а 9 формирования управляющих сиг- нал(: 1з (фиг. 5, диаграмма Б), поступа20 ст на третий вход регистра 3 и пер- иый вход элемента И 10. В момент t, с приходом очередного тактового им- на второй вход В (или 18) элемента И 10 на его выходе формируется

25 одиночный импульс, передний фронт которого осуществляет операцию записи ииф Ормации в регистр 3, которая формируется при этом на всех одиннадцати выходах этого регистра (фиг. 5,

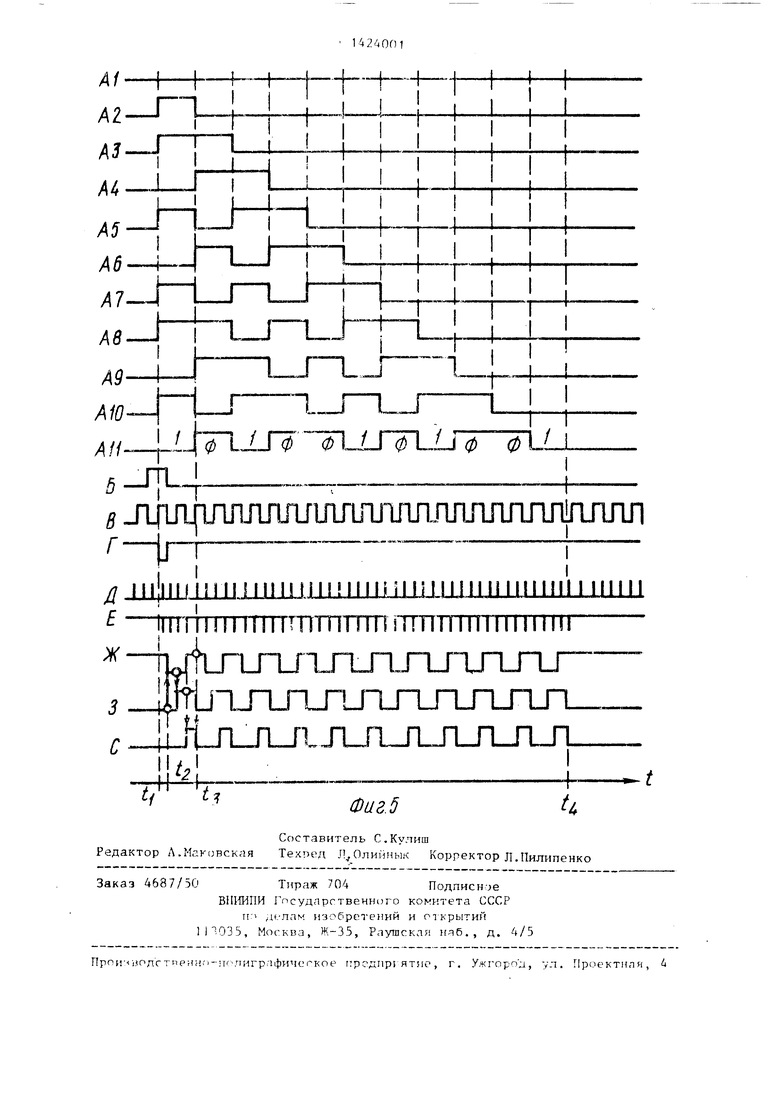

30 диаграммы А1...А11). Одиночный импульс, формируемый на выходе элемента И 10, поступает также на вход третьего инвертора 13. Импульс, формиру- на его вьгходе Г (фиг. 5, диа- грлммл Г), поступая на второй вход блок;. 2 формирования сдвигающих им- пу..пьсов (фиг. 1 и 2) , осуществляет поре1К}Д первого триггера 23 в единичное состояние (это происходит по заднему фронту импульса Г в момент времени t ), что приводит к появлению на первсзм (прямом) вьгходе тригтера 23 уровня логической единицы. Таким образом, создаются условия прохождения высокочастотных импульсов (фиг. 5, диаграмма Д), поступающих на первьпЧ вход 16 блока 2 формирования сдвигающих импульсов, через элемент И-НЕ 26. На выходе Е элемента 26 с этого момента времени формируются импульсы (фиг. 5, диаграмма Е) , первый из которых своим задним фронтом п реводит второй триггер 2А в единичное состояние, что приводит к появлению на его втором (инверсном) выходе уровня логического нуля (фиг. 5, диаграмма Ж), а второй - в единичное состояние третий триггер 25,что приводит к появлению на

40

45

50

55

b . ло-

его первом (прямом) пы:-;оде уровня гической единицы (фиг. 3, диаграмма 3). Третий и fпyльг, формиругм1.1й на выходе Е элемента И-ИЕ 26, онопь приводит к появления на втором рько- де второго тригтора уровня логического нуля, что Г спою очередь гтри- Бодит к появлению на выходе С элемента И 27 переднего фронта сдпигового импульса (фиг, 5, диаграмма С), который формируется на выходе блока 2 формирования сдвигающих импульсов и через элемент ИЛИ 1 поступает на второй (сдвиговый) вход регистра 3. Чет- 15 выходе первого триггера 23, произво- вертый импульс, формируемый на выходе Е элемента И-НЕ 26, внояь устанавливает третий триггер 23 в нулевое состояние, которое характеризуется тем, что на первом (прямом) выходе 2Q этого триггера появляется уровень логического нуля (диаграмма 3 на фиг. 3), который способствует тому, что в мо- мент времени t,. на выходе С элемента И 27 формируется эадний фронт 25 сдвигающего импульса (фиг.З, диаграмма С), которЬЕЙ, во-первых, поступая на второй вход регистра 3, осуществляет сдвиг информации (направление сдвига от младшего разряда At к стар- 30 шему А11), хранящейся в этом регистре, во-вторых, поступая на счетный вход счетчика 28 импульсов, осуществляет увеличение его содержимого на единицу (до этого момента все разряды этого счетчика бьши в нулевом состоянии). Таким образом, на выходе 17 (All) регистра 3 происходит изменение информации, то есть осуществляется передача первого бита информационного слова. Следовательно, четыре импульса, формируемых на выходе Е элемента И-НЕ 26, осуществляют передачу одного бита информационного слова. Поэтому для передачи одиннадцати бит, составляющих информационное слово, требуется 44 подобных импульса (фиг. 3, диаграмма Е). Диаграмма А 11 (фиг. 3) иллюстрирует таким образом характер изменения на втором выходе 17 сдвигового регистра 3 (дифрами 1 и О показано логическое содержание каждого бита передаваемой информации), В момент

35

40

45

50

дит установку содержимого счетчика 28 импульсов в нулевое состояние.

Формула изобретения

Устройство для обмена и)1формацией, содержащее элемент 1ЪПИ, один вход которого является первым тактовым входом устройства, а другой соединен с выходом блока формирования сдвигаю- :цих импульсов, первый вход Кч торого является вторым тактовым входом устройства, выход элемента J} соед1гнен с тактовым входом регистра сдвига, вход последовательного ввода которого является последовательным информационным входом устройства, первый информационньй вьгход регистра сдвига соединен с первым информационным входом блока формирования флагов, и с информационным входом первого блока памяти, второй информац1юнньп1 регистр сдвига соединен с вторым информационным входом блока формирования флагов, выходы которог о соединены с выходами nepfeoro блока памяти и с параллельным входом шинного формирователя данных, вход-выход которого является последовательным информацион ным входом-выходом устройства, вход управления выдачей информации шинного формирователя данных соединен с выходом первого инвертора и с первым входом элемента НЕ-Ш1И-НЕ, вход выборки кристалла шинного формирователя данных соединен с выходом элемента НЕ- ИЛИ-НЕ, второй вход которог о соединен с выходом второго инвертора, вход первого инвертора соединен с первым выходом блока формирования управляющих сигналов, второй выход которого соединен с входом выборки кристалла блока формирования флагов, третий и четвертый выходы - соответственно

времени t,, когда на счетньй вход счетчика 28 импульсов поступает одиннадцатый сдвиговый импульс, до заднему фронту которого содержимое счетчика 28 импульсов принимает значение

400f 1

12

5

IQ1 1 , что приводит к форми11ояанию на fro выходе сигнала, уровень которого соо I нотствует уров)1ю логического нуля, KOTopi.tu, поступив на R-вход первого триггера 23, переводит по- и нулевое (исходпс е) состояние, что ведет к созданию условия непрохождения высокочастотньк импул)- сов (фиг. 5, диаграмма Л), которые поступают на первый вход 16 блока 2 фор. -гирования сдвигающих им11ул1)Сов через элемент И-НЕ 26. Потенциал, форми11уемый на втором (инверсном)

15 выходе первого триггера 23, произво- 2Q 25 30

35

40

45

0

55

дит установку содержимого счетчика 28 импульсов в нулевое состояние.

Формула изобретения

Устройство для обмена и)1формацией, содержащее элемент 1ЪПИ, один вход которого является первым тактовым входом устройства, а другой соединен с выходом блока формирования сдвигаю- :цих импульсов, первый вход Кч торого является вторым тактовым входом устройства, выход элемента J} соед1гнен с тактовым входом регистра сдвига, вход последовательного ввода которого является последовательным информационным входом устройства, первый информационньй вьгход регистра сдвига соединен с первым информационным входом блока формирования флагов, и с информационным входом первого блока памяти, второй информац1юнньп1 регистр сдвига соединен с вторым информационным входом блока формирования флагов, выходы которог о соединены с выходами nepfeoro блока памяти и с параллельным входом шинного формирователя данных, вход-выход которого является последовательным информационным входом-выходом устройства, вход управления выдачей информации шинного формирователя данных соединен с выходом первого инвертора и с первым входом элемента НЕ-Ш1И-НЕ, вход выборки кристалла шинного формирователя данных соединен с выходом элемента НЕ- ИЛИ-НЕ, второй вход которог о соединен с выходом второго инвертора, вход первого инвертора соединен с первым выходом блока формирования управляющих сигналов, второй выход которого соединен с входом выборки кристалла блока формирования флагов, третий и четвертый выходы - соответственно

с первым и вторым входами выборки, с входом второго инвертора и входом разрешения параллельного ввода информации регистра сдвига, первый вход блока формирования управляющих сигналов является входом кода адреса устройства, второй вход - перймм входом синхронизации устройства, третий вход - вторым входом синхронизации устройства, выход третьего инвертора соединен с вторым входом блока формирования сдвигающих импульсов, а вход четвертого - с входом параллельной записи регистра сдвига, третий информационный выход регистра сдвига является последовательным информационным выходом устройства, отличающееся тем, что, с целью повышения надежности устройЛ

26

D

С 3„

/

ства за счет уменьшения количества оборудования и линий связи между блоками устройства, в него введены дополнительно элемент И и второй блок памяти, первый и второй входы выборки кристалла которого соединены соответственно с пятым и шестым выходами блока формирования управляющих

сигналов, информационные входы - с выходами шинного формирователя данных, вьпсоды - с входами параллельной записи регистра сдвига, один вход элемента И соединен с пятым выходом

блока формирования управляющих сигналов, другой вход является третьим тактовьм входом устройства, а выход элемента И соединен с входом пар°ал- лельной записи регистра сдвига.

D С v

-ХС

27

2} С 25

ие.2

В9- BIO- ВН

Л

Фиг.з

d

L.P J2

r

Д М|||1)1МИ111)1ИИП1МПП1111М11Ш1111 111111111 fnrnn I и 111ТТТШТТТЛ 1ТтТТТТТТ| 11111 IN

u

jnJTJTJ JTJnj-LrLrUT .

| АППАРАТ ДЛЯ РАЗРЕЗАНИЯ ПЕРЕДВИГАЮЩЕЙСЯ НА ПОДВИЖНОМ СТОЛЕ ТОРФЯНОЙ ПОЛОСЫ ПРИ ПОМОЩИ НОЖЕЙ, УКРЕПЛЕННЫХ НА ПОВЕРХНОСТИ БАРАБАНА | 1922 |

|

SU602A1 |

| Приспособление для записи звуковых явлений на светочувствительной поверхности | 1919 |

|

SU101A1 |

| АППАРАТ ДЛЯ РАСПРЕДЕЛЕНИЯ ТОРФА НА СУШИЛЬНОМ ПОЛЕ | 1922 |

|

SU608A1 |

Авторы

Даты

1988-09-15—Публикация

1986-11-14—Подача