Известны двухтактные сумматоры комбинационного типа на феррит-транзисторных ячейках с обмотками запрета.

В отличие от известных в предлагаемом сумматоре применены комбинированная логическая схема «ИЛИ - ЗАПРЕТ, состоящая из, например, триода и четырех сердечников с прямоугольной петлей гистерезиса (ГШГ), служащая для образования суммы, и две феррит-транзисторные ячейки, одна из которых предназначена для образования сигнала переноса, а вторая - для его запоминания. Такое выполнение сумматора позволяет уменьшить количество ячеек в «ем.

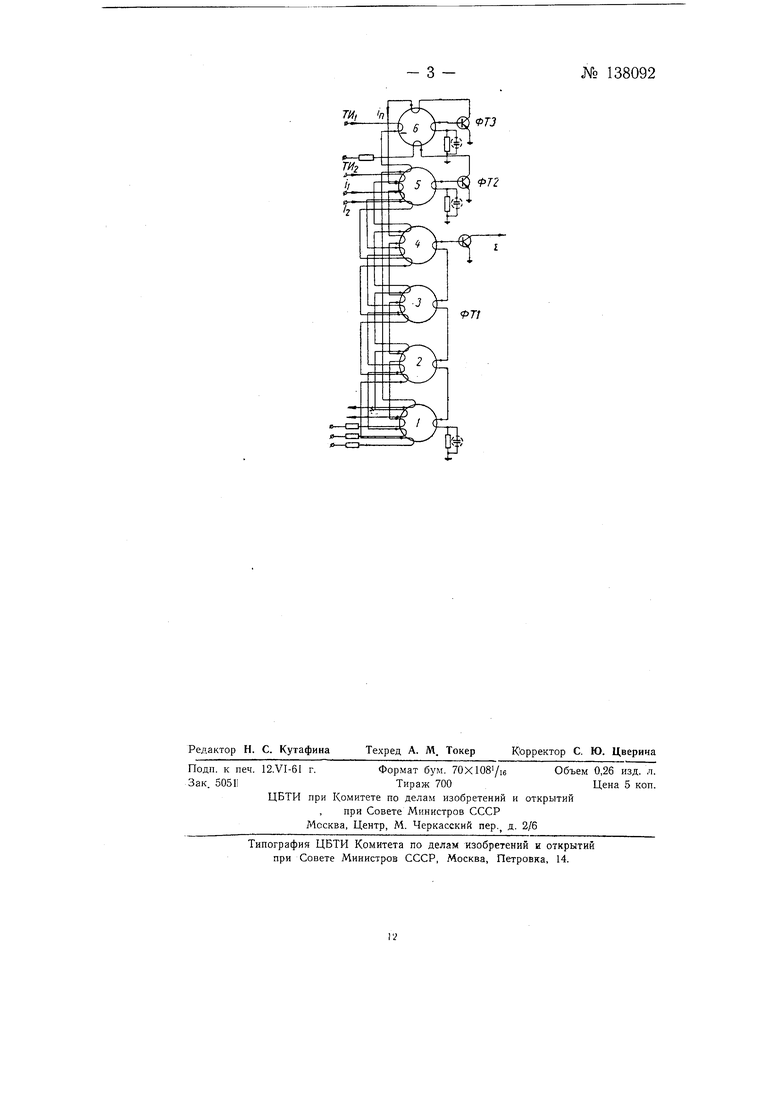

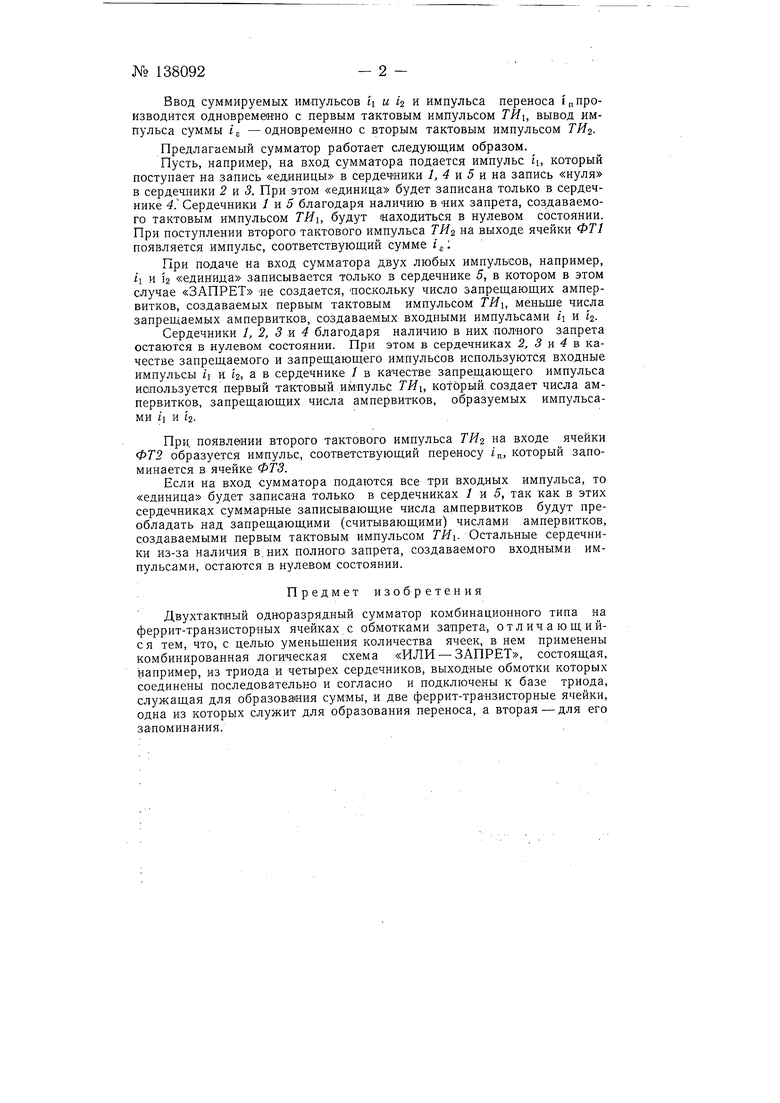

На чертеже изображена схема предлагаемого сумматора.

Сумматор представляет собой комбинацию из трех феррит-транзисторных ячеек ФТ1, ФТ2 и ФТЗ. Ячейка ФТ1, состоящая из одного транзистора и четырех сердечников /, 2, 3, 4 с ППГ, представляет собой комбинированную логическую схему «ИЛИ - ЗАПРЕТ и служит для образования суммы. Импульс i, соответствующий сумме, появляется на выходе ячейки ФТ1 1при подаче на вход сумматора одного из трех возможных входных импульсов или одновременно всех трех, из которых два (/ и /г)-суммируемые, и один (г„)- импульс переноса. Транзистор ячейки ФТ1 управляется выходными обмотками четырех сердечников 1, 2, 3, и 4, соединенными согласно и последовательно и подключенными к базе транзистора.

Ячейка ФТ2, состоящая из одного транзистора и одного сердечника 5, является сложной ячейкой «ЗАПРЕТА и служит для образования импульса переноса г„, когда на вход сумматора подаются любые два из трех входных импульсов.

Ячейка ФТЗ является про.стой ячейкой и служит для запоминания импульса переноса г„, который поступает из ячейки ФТ2. Она состоит из транзистора и сердечника 6.

№ 138092- 2

Ввод суммируемых импульсов и и 4 и импульса переноса „ производится одновременно с первым тактовым импульсом THi, вывод импульса суммы /5 -одновременно с вторым тактовым импульсом ТИ.

Предлагаемый сумматор работает следующим образом.

Пусть, например, на вход сумматора подается импульс k, который поступает на запись «единицы в сердечники 1, 4 и 5 я на запись «нуля в сердечники 2 к 3. При этом «единица будет записана только в сердечнике 4, Сердечники / и 5 благодаря наличию в Них запрета, создаваемого тактовым импульсом ГЯь будут находиться в нулевом состоянии. При поступлении второго тактового импульса ТИ на выходе ячейки ФТ1 появляется импульс, соответствующий сумме i.,.

При подаче на вход сумматора двух любых импульсов, например, /1 и h «единица записывается только в сердечнике 5, в котором в этом случае «ЗАПРЕТ «е создается, поскольку число запрещающих ампервитков, создаваемых первым тактовым импульсом TMi, меньше числа запрещаемых ампервитков, создаваемых входными импульса.ми /i и гг.

Сердечники /, 2, 3 и 4 благодаря наличию в них -полного запрета остаются в нулевом состоянии. При этом в сердечниках 2, 5 и 4 в качестве запрещаемого и запрещающего импульсов используются входные импульсы /I и г2, а в сердечнике / в качестве запрещающего импульса используется первый тактовый импульс ТИ, который создает числа ампервитков, запрещающих числа ампервитков, образуемых импульсами /1 и 1ч.

При. появлении второго тактового импульса ТИ на входе ячейки ФТ2 образуется импульс, соответствующий переносу /„, который запоминается в ячейке ФТЗ.

Если на вход сумматора подаются все три входных импульса, то «единица будет записана только в сердечниках / и 5, так как в этих сердечниках суммарные записывающие числа ампервитков будут преобладать над запрещающими (считывающими) числами ампервитков, создаваемыми первым тактовым импульсом ТИ. Остальные сердечники из-за наличия .в. них полного запрета, создаваемого входными импульсами, остаются в нулевом состоянии.

Предмет изобретения

Двухтакт1ный одноразрядный сумматор комбинационного типа на феррит-транзисторных ячейках с обмотками запрета, отличающийс я тем, что, с целью уменьшения количества ячеек, в нем применены комбинированная логическая схема «ИЛИ - ЗАПРЕТ, состоящая, например, из триода и четырех сердечников, выходные обмотки которых соединены последовательно и согласно и подключены к базе триода, служащая для образования суммы, и две феррит-транзисторные ячейки, одна из которых служит для образования переноса, а вторая - для его запоминания.

ти.

ФТЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухтактный одноразрядный сумматор комбинационного типа | 1960 |

|

SU144641A1 |

| Сумматор на феррит-транзисторных ячейках | 1959 |

|

SU127864A1 |

| Однотактный одноразрядный сумматор на феррит-транзисторных ячейках | 1959 |

|

SU126662A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1969 |

|

SU256399A1 |

| УСТРОЙСТВО ЦИКЛИЧЕСКОЙ, СИНХРОННОЙ, с ВРЕМЕННЫМ | 1970 |

|

SU277009A1 |

| ДВУХТАКТНЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ НА ФЕРРИТ- ТРАНЗИСТОРНЫХ МОДУЛЯХ | 1970 |

|

SU274512A1 |

| НАКАПЛИВАЮЩИЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1966 |

|

SU224164A1 |

| Двоичный сумматор | 1972 |

|

SU439809A1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 1967 |

|

SU197281A1 |

| Однотактный переключатель на феррит-транзисторных ячейках | 1959 |

|

SU124207A1 |

Авторы

Даты

1961-01-01—Публикация

1960-08-17—Подача