Известны двухтактные одноразрядные сумматоры комбинационного типа, выполненные на ферротранзисторных ячейках и диодах.

Предлагаемый сумматор отличается от известных тем, что для упрощения устройства и увеличения его надежности в нем для п тучения схем совпадения выходы ячеек, входы которых служат входами устройства и выходом переноса данного сумматора и через которые проходит шина первого такта, соединены последовательно. Обмотка запрета ячейки суммы соединена с выходной обмоткой ячейки переноса, через которую проходит шина второго такта.

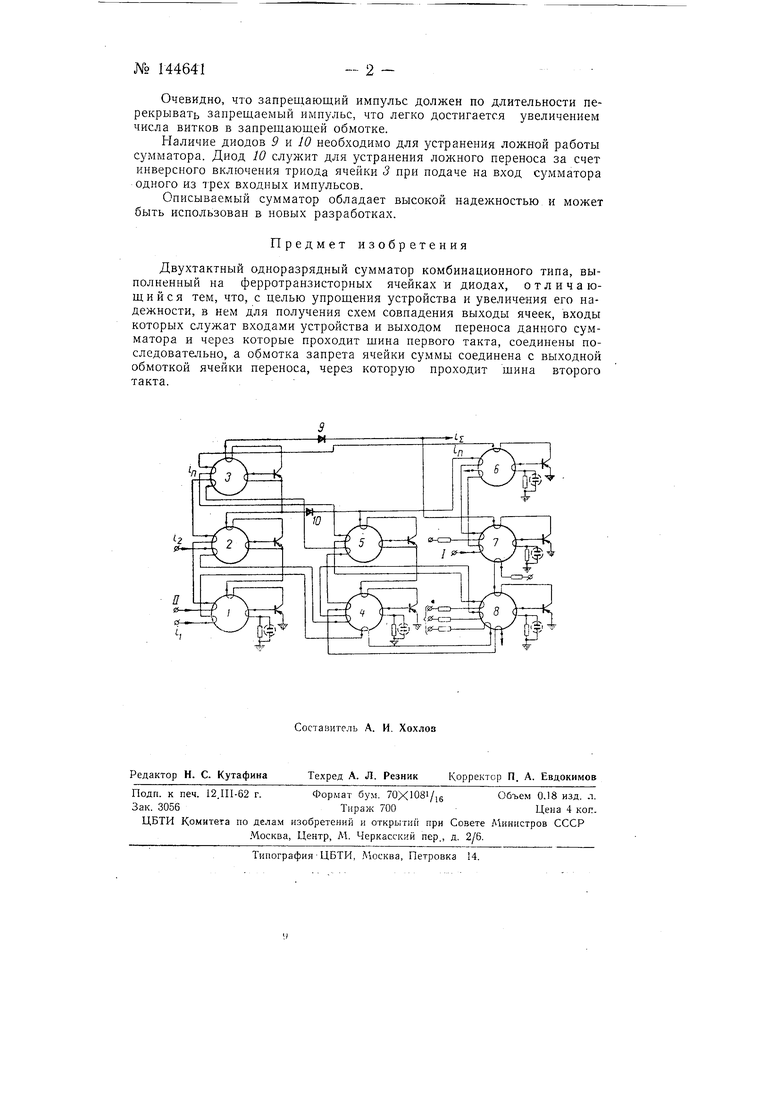

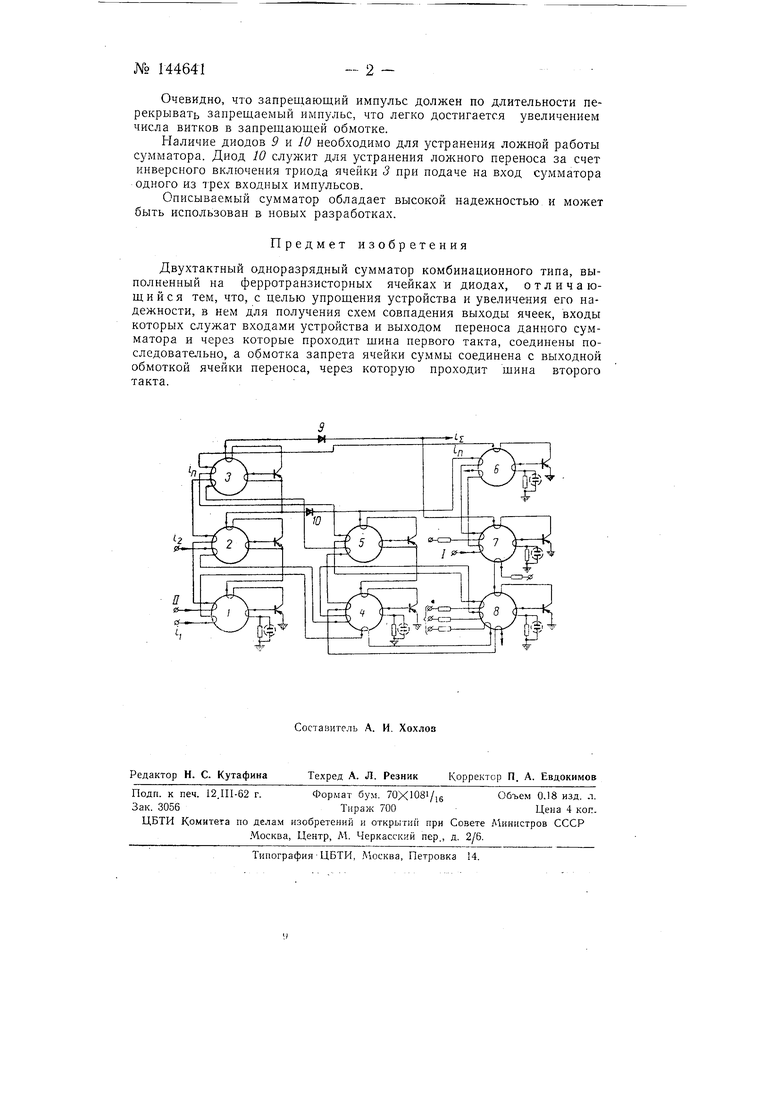

Принципиальная схема описываемого сумматора показана на чертеже.

В описываемом сумматоре ферротранзисторные ячейки /, 2 и 5 об разуют схему совпадения на три входа и служат для получения суммы и переноса, который образуется при наличии на входе двух или трех входных импульсов. Ячейки 4 vt. 5 образуют схему совпадения на два входа. Ячейка 6 служит для хранения переноса, а ячейки 7 и S -для образования суммы, причем ячейка 7 является ячейкой запрета. В качестве импульсов запрета используются импульсы переноса, снимаемые с ячеек 2 и 5. Ввод слагаемых г,, гг и переноса г„ производится по первому такту (шина /), а вывод суммы S - по второму такту (шина //).

При подаче на вход одного из трех входных импульсов на выходе ячейки 7 образуется импульс, соответствующий сумме. При подаче на вход двух любых из трех входных импульсов на выходах ячеек 2 и 5 образуется импульс, соответствующий переносу.

При подаче на вход сумматора трех входных импульсов с ячейки 3 снимается импульс, соответствующий сумме, а с ячеек 2 и 5 - импульс, соответствующий переносу. Последний запоминается в ячейке 6 и одновременно запрещает появление импульса на выходе ячейки 7,

Очевидно, что запрещающий импульс должен по длительности перекрывать запрещаемый импульс, что легко достигается увеличением числа витков в запрещающей обмотке.

Наличие диодов 9 и 10 необходимо для устранения ложной работы сумматора. Диод 10 служит для устранения ложного переноса за счет инверсного включения триода ячейки 3 при подаче на вход сумматора одного из трех входных импульсов.

Описываемый сумматор обладает высокой надежностью и может быть использован в новых разработках.

Предмет изобретения

Двухтактный одноразрядный сумматор комбинационного типа выполн енный на ферротранзисторных ячейках и диодах, отличающийся тем, что, с целью упрощения устройства и увеличения его надежности, в нем для получения схем совпадения выходы ячеек входы которых служат входами устройства и выходом переноса данного сумматора и через которые проходит шина первого такта, соединены последовательно, а обмотка запрета ячейки суммы соединена с выходной обмоткой ячейки переноса, через которую проходит шина второго такта.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухтактный однозарядный сумматор комбинационного типа | 1960 |

|

SU138092A1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР | 1970 |

|

SU263281A1 |

| Сумматор на феррит-транзисторных ячейках | 1959 |

|

SU127864A1 |

| ФЕРРОТРАНЗИСТОРНЫЙ ТРЕХТАКТНЫЙ СЧЕТНЫЙ ТРИГГЕР | 1968 |

|

SU231238A1 |

| Параллельный сумматор | 1981 |

|

SU1018114A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| УСТРОЙСТВО ЦИКЛИЧЕСКОЙ, СИНХРОННОЙ, с ВРЕМЕННЫМ | 1970 |

|

SU277009A1 |

| Конвейрный сумматор | 1990 |

|

SU1795454A1 |

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

Авторы

Даты

1962-01-01—Публикация

1960-08-04—Подача