со

00

со

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задания скорости в системах числового программного управления | 1986 |

|

SU1328793A1 |

| Линейно-круговой интерполятор | 1984 |

|

SU1215090A2 |

| Устройство для управления многокоординатным оборудованием | 1987 |

|

SU1427334A1 |

| Устройство для автоматического разгона и торможения двигателя станка с программным управлением | 1983 |

|

SU1149221A1 |

| Устройство для автоматического разгона и торможения двигателя станка с программным управлением | 1985 |

|

SU1269099A2 |

| Линейно-круговой интерполятор | 1983 |

|

SU1265700A2 |

| Цифровой интерполятор | 1984 |

|

SU1238033A1 |

| Линейно-круговой интерполятор | 1982 |

|

SU1149218A1 |

| Линейно-круговой интерполятор | 1985 |

|

SU1302241A2 |

| Устройство для контроля дискретного объекта | 1984 |

|

SU1218398A1 |

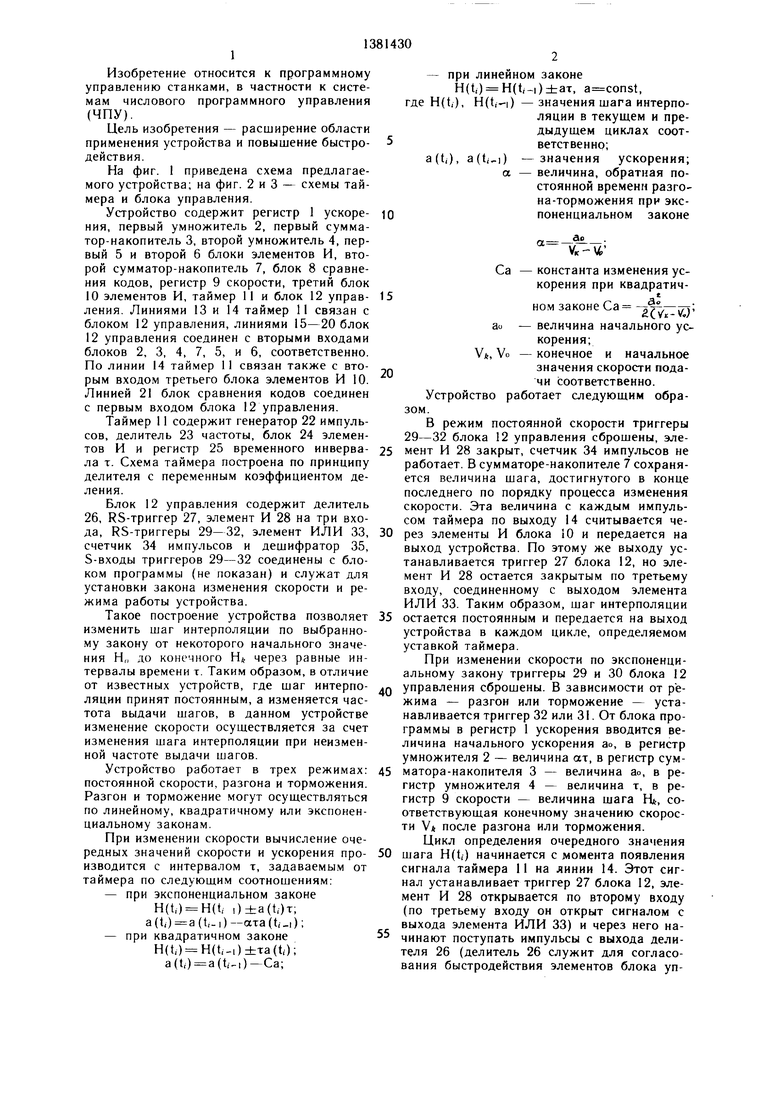

Изобретение может быть использовано в составе управляющих устройств станков с ЧПУ, скоростных координатографов и в аппаратуре ускоренного преобразования и контроля управляющих программ. Цель изобретения - повыщение быстродействия, расщирение области применения. Устройство задания скорости в системах ЧПУ содержит последовательно соединенные регистр ускорения 1, умножитель 2, сумматор-накопитель 3, умножитель 4, блок элементов И 5, сумматор-накопитель 7, блок сравнения кодов 8, а также регистр скорости 9, блоки элементов И 6 и 10, таймер 11 и блок управления 12. Устройство позволяет изменять скорость по линейному, экспоненциальному и квадратичному законам путем изменения щага интерполяции и ускорения, отнесенных к постоянному временному интервалу, задаваемому от таймера. Величина щага может изменяться в щироких пределах. Возможно также изменение частоты дискретизации (или времени цикла) в щироких пределах. Устройство обеспечивает большой диапазон регулирования скорости подачи, высокое быстродействие по выходному параметру при относительно низких требованиях к быстродействию элементов устройства. 1 з. п. ф-лы, 3 ил. с S (Л

е /

Изобретение относится к программному управлению станками, в частности к системам числового программного управления (ЧПУ).

Цель изобретения - расширение области применения устройства и повышение быстродействия.

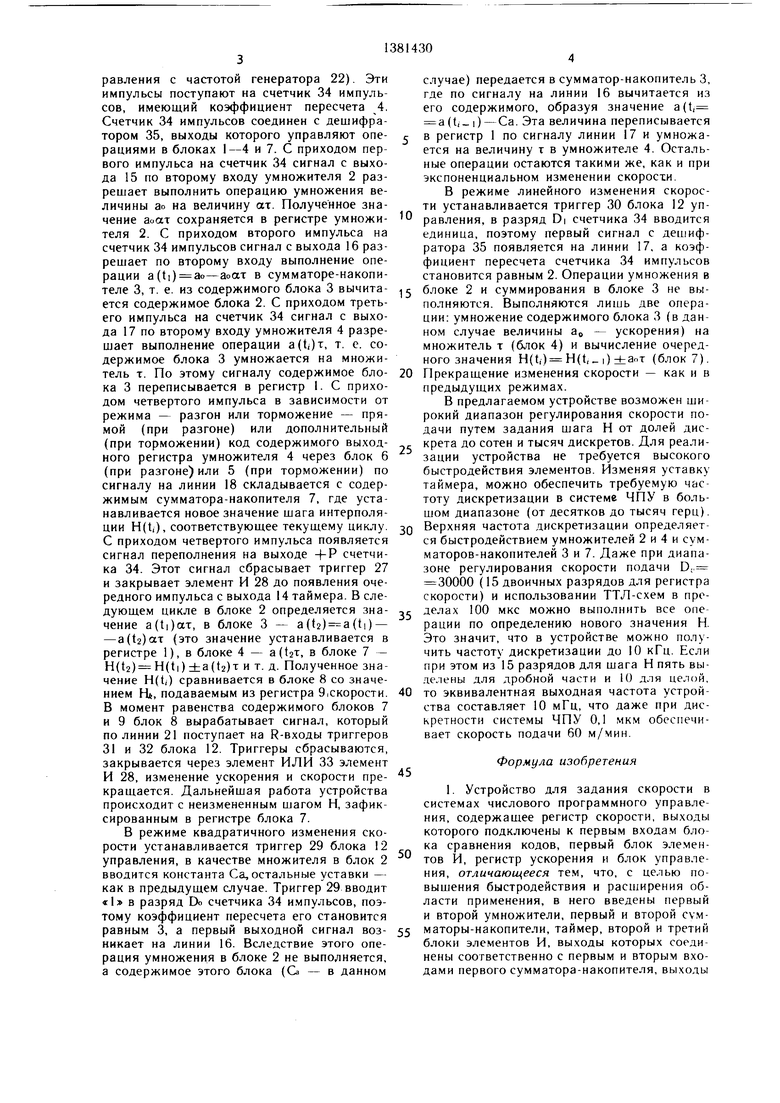

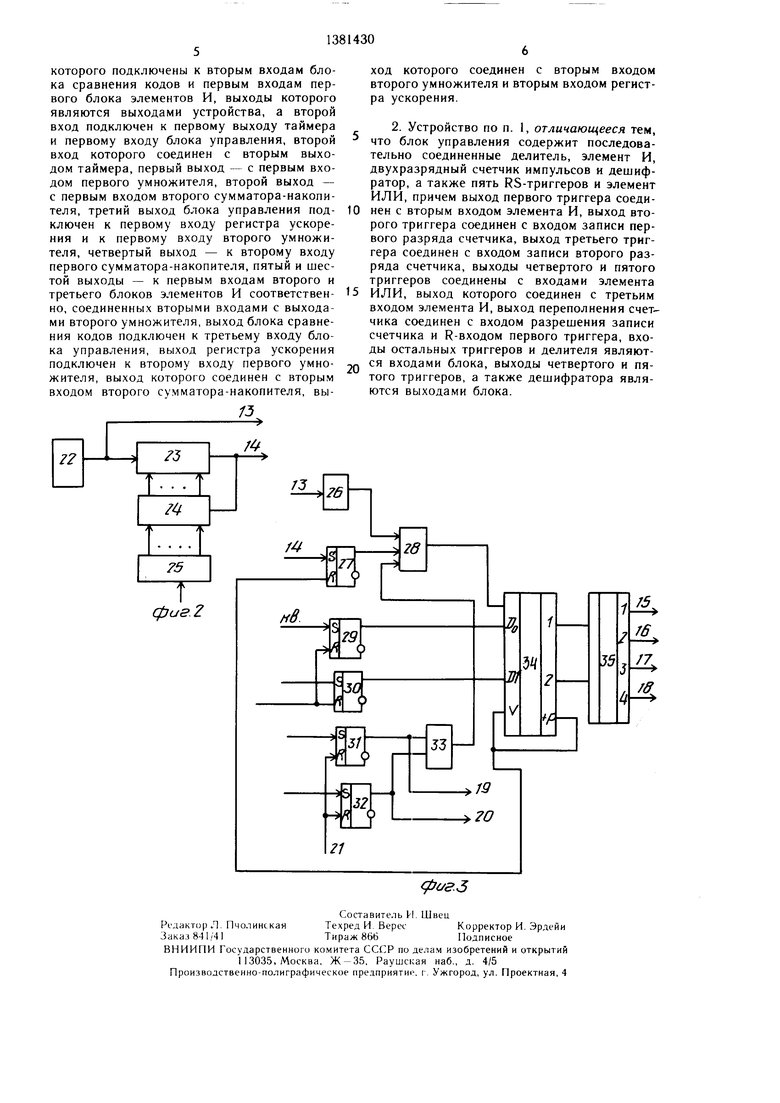

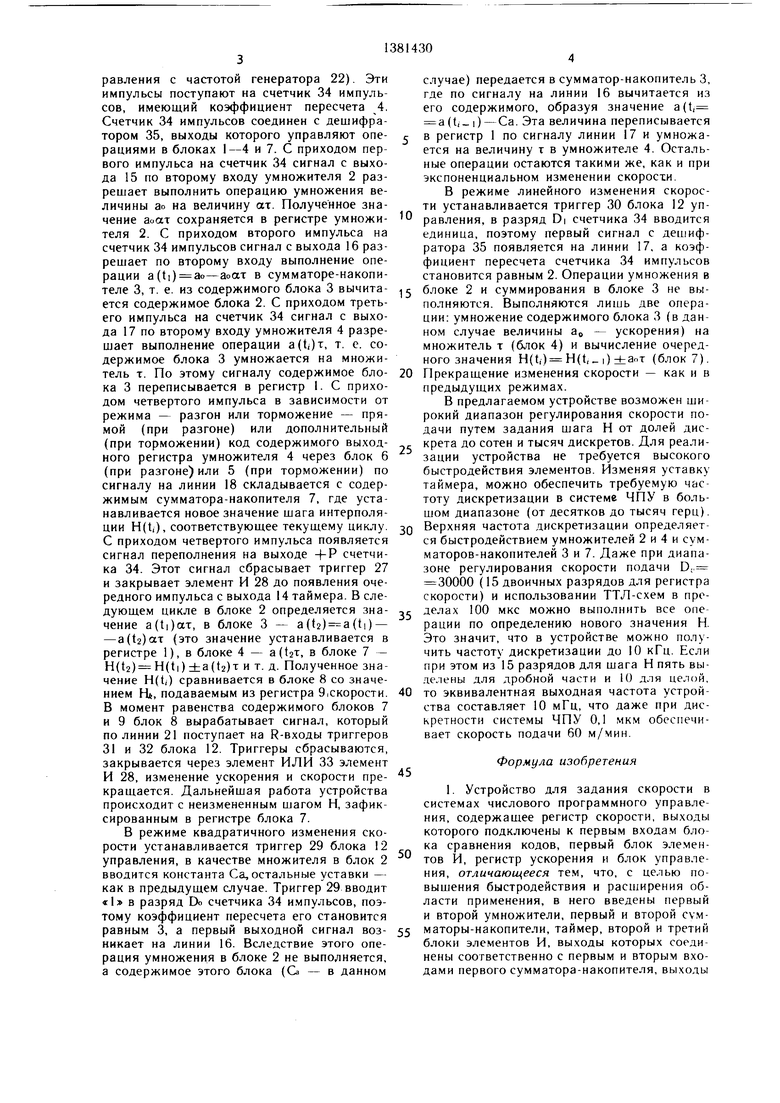

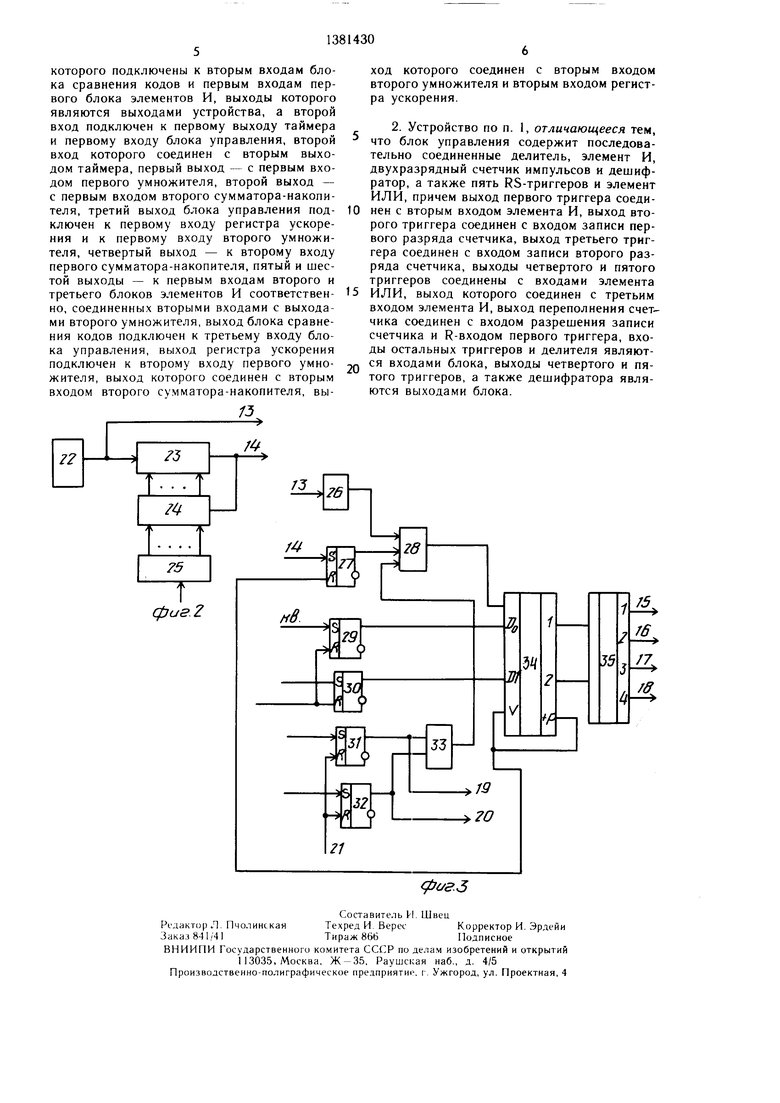

На фиг. 1 приведена схема предлагаемого устройства; на фиг. 2 и 3 - схемы таймера и блока управления.

Устройство содержит регистр 1 ускорения, первый умножитель 2, первый сумматор-накопитель 3, второй умножитель 4, первый 5 и второй 6 блоки элементов И, второй сумматор-накопитель 7, блок 8 сравнения кодов, регистр 9 скорости, третий блок 10 элементов И, таймер 11 и блок 12 управления. Линиями 13 и 14 таймер 11 связан с блоком 12 управления, линиями 15-20 блок 12 управления соединен с вторыми входами блоков 2, 3, 4, 7, 5, и 6, соответственно. По линии 14 таймер 11 связан также с вторым входом третьего блока элементов И 10. Линией 21 блок сравнения кодов соединен с первым входом блока 12 управления.

Таймер 11 содержит генератор 22 импульсов, делитель 23 частоты, блок 24 элемен10

15

20

- при линейном законе

H(t,) H(t,-i)±aT, a const, где H(t,), H(t,-i) - значения шага интерполяции в текущем и пре- дыдушем циклах соответственно;

a(ti), a() -значения ускорения; а. - величина, обратная постоянной временм разгона-торможения при экспоненциальном законе

„ ао

° -v;

Са - константа изменения ускорения при квадратичном законе Са .-тг

«i С. - VW

ао - величина начального ускорения;

V, Vo - конечное и начальное значения скорости подачи соответственно.

Устройство работает следующим образом.

В режим постоянной скорости триггеры 29-32 блока 12 управления сброшены, элетов И и регистр 25 временного инверва- 25 мент И 28 закрыт, счетчик 34 импульсов не

ла т. Схема таймера построена по принципу делителя с переменным коэффициентом деления.

Блок 12 управления содержит делитель 26, RS-триггер 27, элемент И 28 на три входа, RS-триггеры 29-32, элемент ИЛИ 33, счетчик 34 импульсов и дешифратор 35, S-входы триггеров 29-32 соединены с блоком программы (не показан) и служат для установки закона изменения скорости и режима работы устройства.

Такое построение устройства позволяет изменить шаг интерполяции по выбранному закону от некоторого начального значения Н„ до конечного Н через равные интервалы времени т. Таким образом, в отличие от известных устройств, где шаг интерполяции принят постоянным, а изменяется частота выдачи шагов, в данном устройстве изменение скорости осуществляется за счет изменения шага интерполяции при неизменной частоте выдачи шагов.

работает. В сумматоре-накопителе 7 сохраняется величина шага, достигнутого в конце последнего по порядку процесса изменения скорости. Эта величина с каждым импульсом таймера по выходу 14 считывается че30 рез элементы И блока 10 и передается на выход устройства. По этому же выходу устанавливается триггер 27 блока 12, но элемент И 28 остается закрытым по третьему входу, соединенному с выходом элемента ИЛИ 33. Таким образом, шаг интерполяции

35 остается постоянным и передается на выход устройства в каждом цикле, определяемом уставкой таймера.

При изменении скорости по экспоненциальному закону триггеры 29 и 30 блока 12

4Q управления сброшены. В зависимости от режима - разгон или торможение - устанавливается триггер 32 или 31. От блока программы в регистр 1 ускорения вводится величина начального ускорения ао, в регистр умножителя 2 - величина ат, в регистр сум4Q управления сброшены. В зависимости от режима - разгон или торможение - устанавливается триггер 32 или 31. От блока программы в регистр 1 ускорения вводится величина начального ускорения ао, в регистр умножителя 2 - величина ат, в регистр сумУстройство работает в трех режимах: 45 матора-накопителя 3 - величина ао, в репостояннои скорости, разгона и торможения. Разгон и торможение могут осуществляться по линейному, квадратичному или экспоненциальному законам.

При изменении скорости вычисление очегистр умножителя 4 - величина т, в регистр 9 скорости - величина шага Н, соответствующая конечному значению скорости V после разгона или торможения.

Цикл определения очередного значения

редных значений скорости и ускорения про- 50 шага H(t,) начинается с момента появления

сигнала таймера II на линии 14. Этот сигнал устанавливает триггер 27 блока 12, элемент И 28 открывается по второму входу (по третьему входу он открыт сигналом с выхода элемента ИЛИ 33) и через него начинают поступать импульсы с выхода делителя 26 (делитель 26 служит для согласования быстродействия элементов блока упизводится с интервалом т, задаваемым от таймера по следуюшим соотношениям:

-при экспоненциальном законе

H(t,) H(t, ,)±а(1,-)т; а(1,)а (t,-i)-aTa(t,i);

-при квадратичном законе

H(t,) H(t,,)±Ta(t,); a(t,)a(t,-i)-Са;

55

0

5

0

- при линейном законе

H(t,) H(t,-i)±aT, a const, где H(t,), H(t,-i) - значения шага интерполяции в текущем и пре- дыдушем циклах соответственно;

a(ti), a() -значения ускорения; а. - величина, обратная постоянной временм разгона-торможения при экспоненциальном законе

„ ао

° -v;

Са - константа изменения ускорения при квадратичном законе Са .-тг

«i С. - VW

ао - величина начального ускорения;

V, Vo - конечное и начальное значения скорости подачи соответственно.

Устройство работает следующим образом.

В режим постоянной скорости триггеры 29-32 блока 12 управления сброшены, эле5 мент И 28 закрыт, счетчик 34 импульсов не

работает. В сумматоре-накопителе 7 сохраняется величина шага, достигнутого в конце последнего по порядку процесса изменения скорости. Эта величина с каждым импульсом таймера по выходу 14 считывается через элементы И блока 10 и передается на выход устройства. По этому же выходу устанавливается триггер 27 блока 12, но элемент И 28 остается закрытым по третьему входу, соединенному с выходом элемента ИЛИ 33. Таким образом, шаг интерполяции

остается постоянным и передается на выход устройства в каждом цикле, определяемом уставкой таймера.

При изменении скорости по экспоненциальному закону триггеры 29 и 30 блока 12

управления сброшены. В зависимости от режима - разгон или торможение - устанавливается триггер 32 или 31. От блока программы в регистр 1 ускорения вводится величина начального ускорения ао, в регистр умножителя 2 - величина ат, в регистр сумматора-накопителя 3 - величина ао, в рематора-накопителя 3 - величина ао, в регистр умножителя 4 - величина т, в регистр 9 скорости - величина шага Н, соответствующая конечному значению скорости V после разгона или торможения.

Цикл определения очередного значения

шага H(t,) начинается с момента появления

равления с частотой генератора 22). Эти импульсы поступают на счетчнк 34 импульсов, имеющий коэффициент пересчета 4. Счетчик 34 импульсов соединен с дешифратором 35, выходы которого управляют операциями в блоках I-4 и 7. С приходом первого импульса на счетчик 34 сигнал с выхода 15 по второму входу умножителя 2 разрешает выполнить операцию умножения величины ао на величину ат. Полученное значение аоат сохраняется в регистре умиожи- теля 2. С приходом второго импульса на счетчик 34 импульсов сигнал с выхода 16 разрешает по второму входу выполнение операции a(ti) ao-аоат в сумматоре-накопислучае) передается в сумматор-накопитель 3, где по сигналу на линии 16 вычитается из его содержимого, образуя значение a(t, a(t,i)-Са. Эта величина переписывается 5 в регистр 1 по сигналу линии 17 и умножается на величину т в умножителе 4. Остальные операции остаются такими же, как и при экспоненциальном изменении скорости.

В режиме линейного изменения скорости устанавливается триггер 30 блока 12 уп- равления, в разряд DI счетчика 34 вводится единица, поэтому первый сигнал с дешифратора 35 появляется на линии 17, а коэффициент пересчета счетчика 34 импульсов становится равным 2. Операции умножения в

теле 3, т. е. из содержимого блока 3 вычита- блоке 2 и суммирования в блоке 3 не вы- ется содержимое блока 2. С приходом треть-полняются. Выполняются лишь две операего импульса на счетчик 34 сигнал с выхо30

да 17 по второму входу умножителя 4 разрешает выполнение операции a(ti)T, т. е. содержимое блока 3 умножается на множитель т. По этому сигналу содержимое блока 3 переписывается в регистр 1. С приходом четвертого импульса в зависимости от режима - разгон или торможение - прямой (при разгоне) или дополнительный (при торможении) код содержимого выходного регистра умножителя 4 через блок 6 (при разгоне) или 5 (при торможении) по сигналу на линии 18 складывается с содержимым сумматора-накопителя 7, где устанавливается новое значение шага интерполяции H(ti), соответствующее текущему циклу. С приходом четвертого импульса появляется сигнал переполнения на выходе -)-Р счетчика 34. Этот сигнал сбрасывает триггер 27 и закрывает элемент И 28 до появления очередного импульса с выхода 14 таймера. В следующем цикле в блоке 2 определяется зна- or чение а(1|)ат, в блоке 3 - a(t2) a(ti) - -а((2)ат (это значение устанавливается в регистре 1), в блоке 4 - а(12Т, в блоке 7 - H(t2)H(ti) ±а(12)т и т. д. Полученное значение H(t/) сравнивается в блоке 8 со значением Н, подаваемым из регистра Э.скорости. 40 В момент равенства содержимого блоков 7 и 9 блок 8 вырабатывает сигнал, который по линии 21 поступает на R-входы триггеров 31 и 32 блока 12. Триггеры сбрасываются, закрывается через элемент ИЛИ 33 элемент И 28, изменение ускорения и скорости пре- кращается. Дальнейшая работа устройства происходит с неизмененным шагом Н, зафиксированным в регистре блока 7.

В режиме квадратичного изменения скорости устанавливается триггер 29 блока 12 управления, в качестве множителя в блок 2 вводится константа Са, остальные уставки - как в предыдущем случае. Триггер 29 вводит «1 в разряд Do счетчика 34 импульсов, поэтому коэффициент пересчета его становится равным 3, а первый выходной сигнал воз- 55 никает на линии 16. Вследствие этого операция умиожения в блоке 2 не выполняется, а содержимое этого блока (& - в данном

ции: умножение содержимого блока 3 (в данном случае величины а - ускорения) на множитель т (блок 4) и вычисление очередного значения H(t,) H(t, „ |) (блок 7).

20 Прекращение изменения скорости - как и в предыдущих режимах.

В предлагаемом устройстве возможен широкий диапазон регулирования скорости подачи путем задания шага Н от долей дис.,с крета до сотен и тысяч дискретов. Для реализации устройства не требуется высокого быстродействия элементов. Изменяя уставку таймера, можно обеспечить требуемую частоту дискретизации в системе ЧПУ в большом диапазоне (от десятков до тысяч герц). Верхняя частота дискретизации определяется быстродействием умножителей 2 и 4 и сумматоров-накопителей 3 и 7. Даже при диапазоне регулироваиия скорости подачи D; 30000 (15 двоичных разрядов для регистра скорости) и использовании ТТЛ-схем в пределах 100 МКС можно выполнить все one рации по определению нового значения Н. Это значит, что в устройстве можно получить частоту дискретизации до 10 кГц. Если при этом из 15 разрядов для шага Н пять выделены для дробной части и 10 для целой, то эквивалентная выходная частота устройства составляет 10 мГц, что даже при дискретности системы ЧПУ 0,1 мкм обеспечивает скорость подачи 60 м/мин.

50

Формула изобретения

блоке 2 и суммирования в блоке 3 не вы- полняются. Выполняются лишь две опера0

r 0

ции: умножение содержимого блока 3 (в данном случае величины а - ускорения) на множитель т (блок 4) и вычисление очередного значения H(t,) H(t, „ |) (блок 7).

0 Прекращение изменения скорости - как и в предыдущих режимах.

В предлагаемом устройстве возможен широкий диапазон регулирования скорости подачи путем задания шага Н от долей дисс крета до сотен и тысяч дискретов. Для реализации устройства не требуется высокого быстродействия элементов. Изменяя уставку таймера, можно обеспечить требуемую частоту дискретизации в системе ЧПУ в большом диапазоне (от десятков до тысяч герц). Верхняя частота дискретизации определяется быстродействием умножителей 2 и 4 и сумматоров-накопителей 3 и 7. Даже при диапазоне регулироваиия скорости подачи D; 30000 (15 двоичных разрядов для регистра скорости) и использовании ТТЛ-схем в пределах 100 МКС можно выполнить все one рации по определению нового значения Н. Это значит, что в устройстве можно получить частоту дискретизации до 10 кГц. Если при этом из 15 разрядов для шага Н пять выделены для дробной части и 10 для целой, то эквивалентная выходная частота устройства составляет 10 мГц, что даже при дискретности системы ЧПУ 0,1 мкм обеспечивает скорость подачи 60 м/мин.

Формула изобретения

которого подключены к вторым входам блока сравнения кодов и первым входам первого блока элементов И, выходы которого являются выходами устройства, а второй вход подключен к первому выходу таймера и первому входу блока управления, второй вход которого соединен с вторым выходом таймера, первый выход - с первым входом первого умножителя, второй выход - с первым входом второго сумматора-накопиход которого соединен с вторым входом второго умножителя и вторым входом регистра ускорения.

рого триггера соединен с входом записи первого разряда счетчика, выход третьего триггера соединен с входом записи второго разряда счетчика, выходы четвертого и пятого триггеров соединены с входами элемента

третьего блоков элементов И соответствен- 15 ИЛИ, выход которого соединен с третьим но, соединенных вторыми входами с выхода-входом элемента И, выход переполнения счетми второго умножителя, выход блока сравне-чика соединен с входом разрешения записи

ния кодов подключен к третьему входу бло-счетчика и R-входом первого триггера, вхока управления, выход регистра ускорения ды остальных триггеров и делителя являют- подключен к второму входу первого умно- 2п входами блока, выходы четвертого и пя- жителя, выход которого соединен с вторымтого триггеров, а также дешифратора являвходом второго сумматора-накопителя, вы-ются выходами блока.

/

Редактор л. Пчолинская Заказ 841/41

Составитель И. Швец

Техред И. ВересКорректор И. Эрдейи

Тираж 866Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж -35. Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

ход которого соединен с вторым входом второго умножителя и вторым входом регистра ускорения.

| Устройство для автоматического разгона и торможения двигателя станка с программным управлением | 1983 |

|

SU1149221A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для автоматического разгона и торможения двигателя станка с программным управлением | 1985 |

|

SU1269099A2 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-03-15—Публикация

1986-06-01—Подача