Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах числового программного управления.

Цель изобретения - повьпление производительности оборудования за счет снижения выходной частоты.

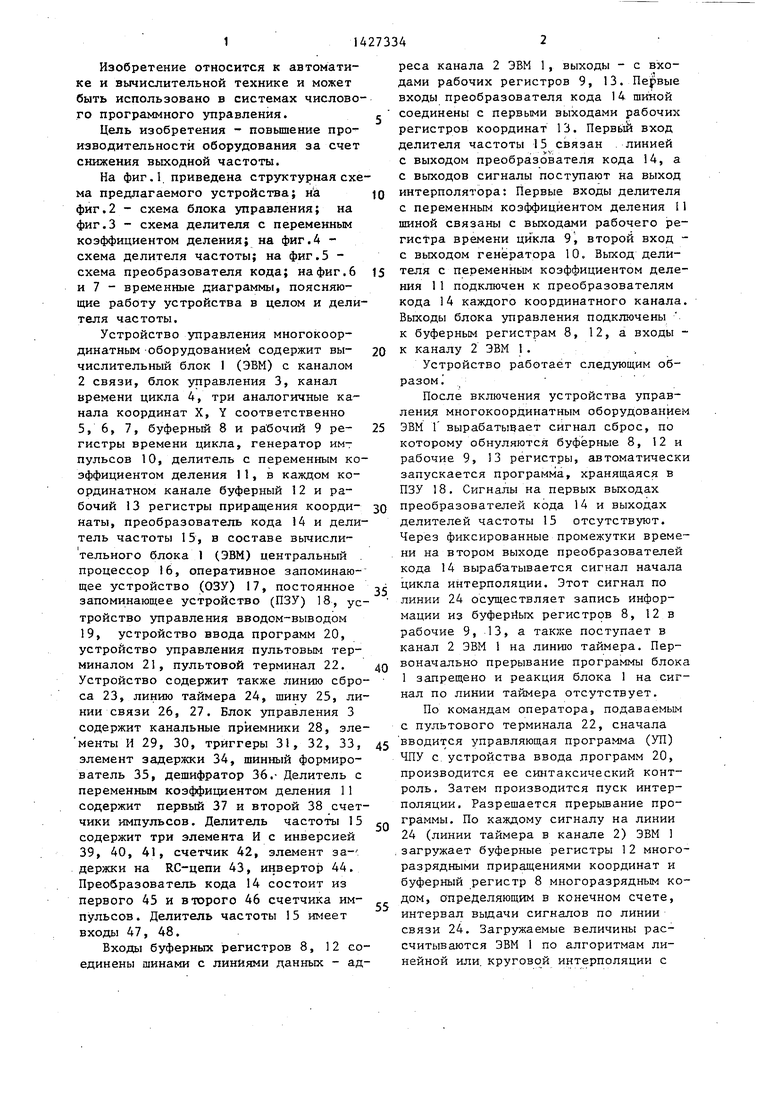

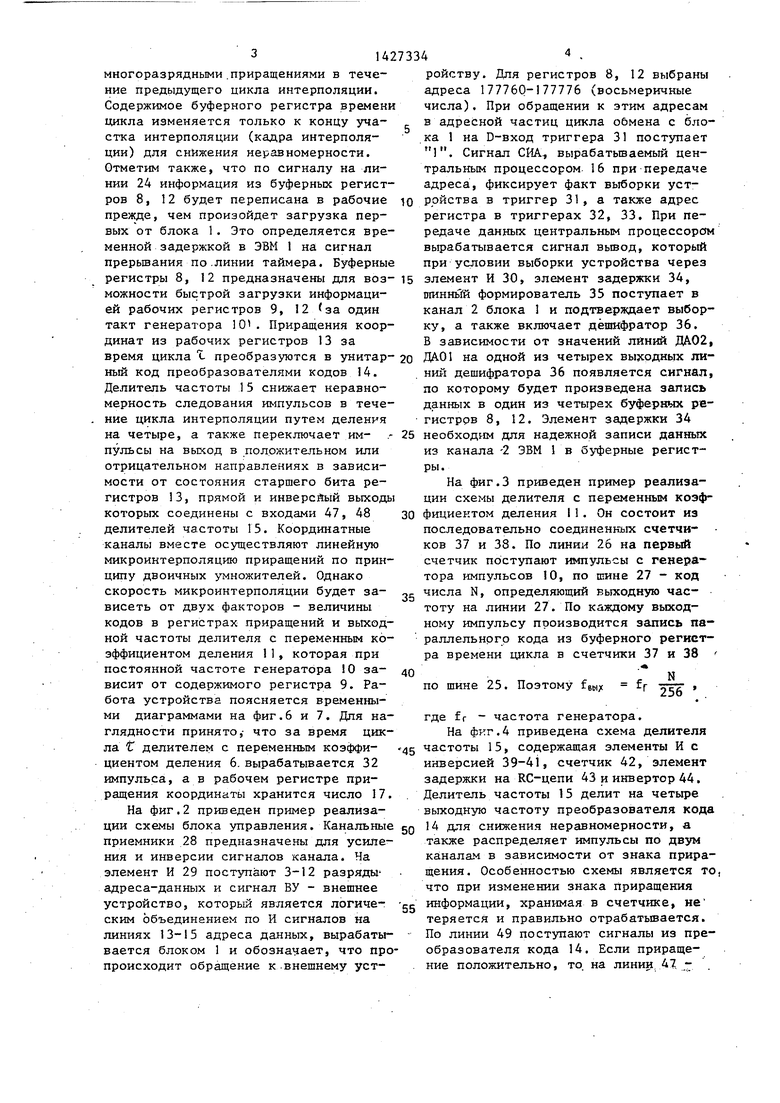

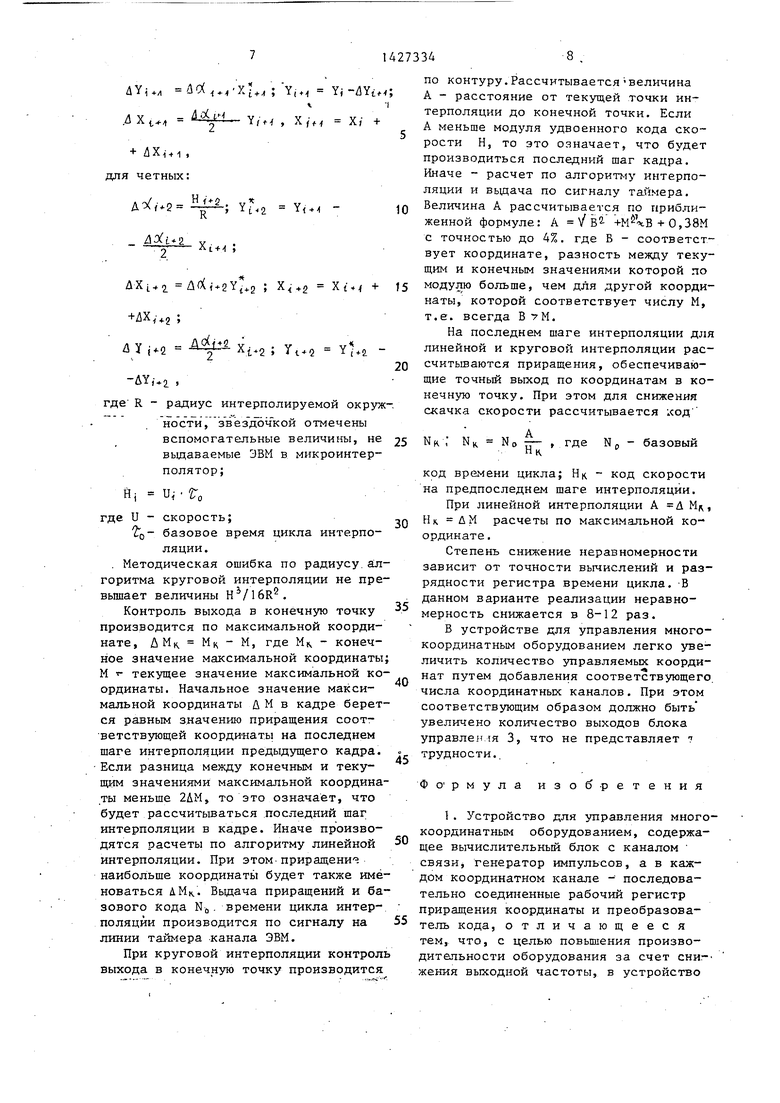

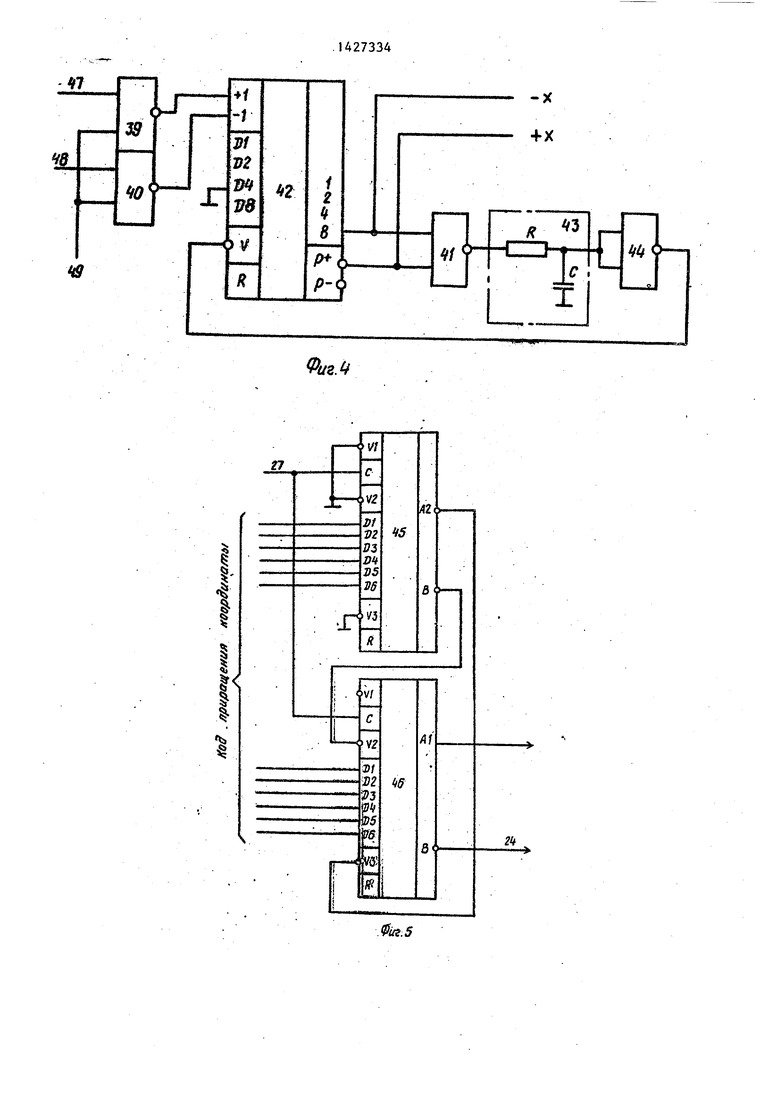

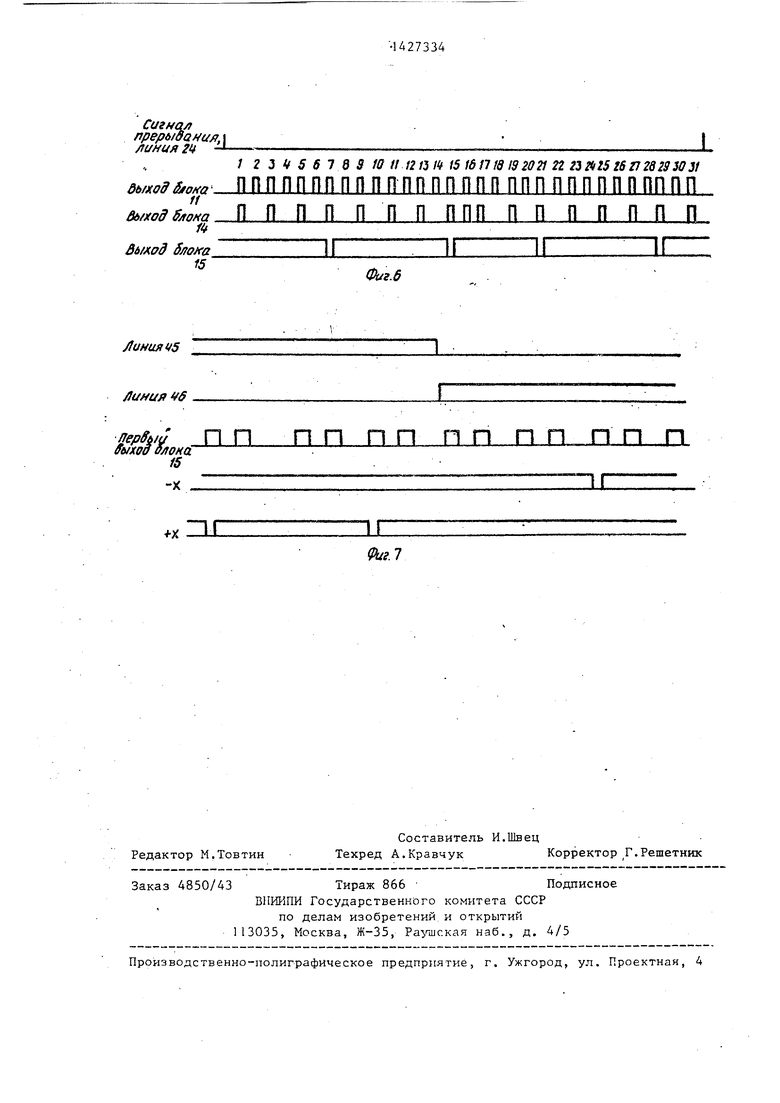

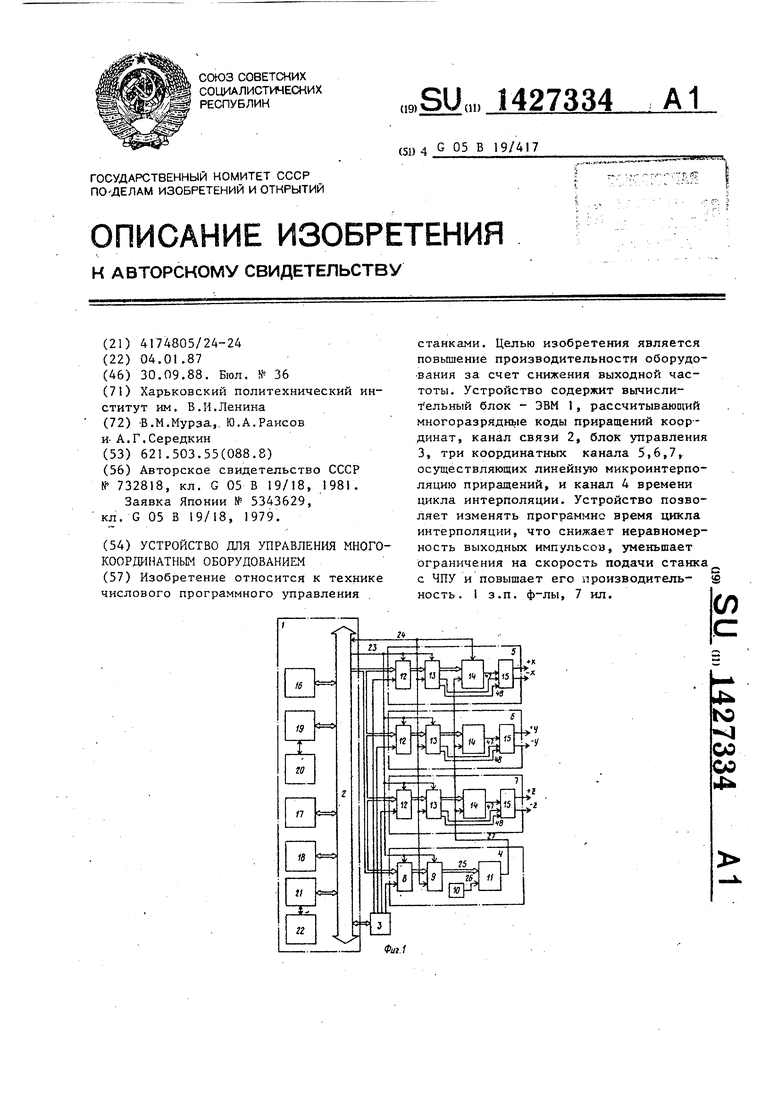

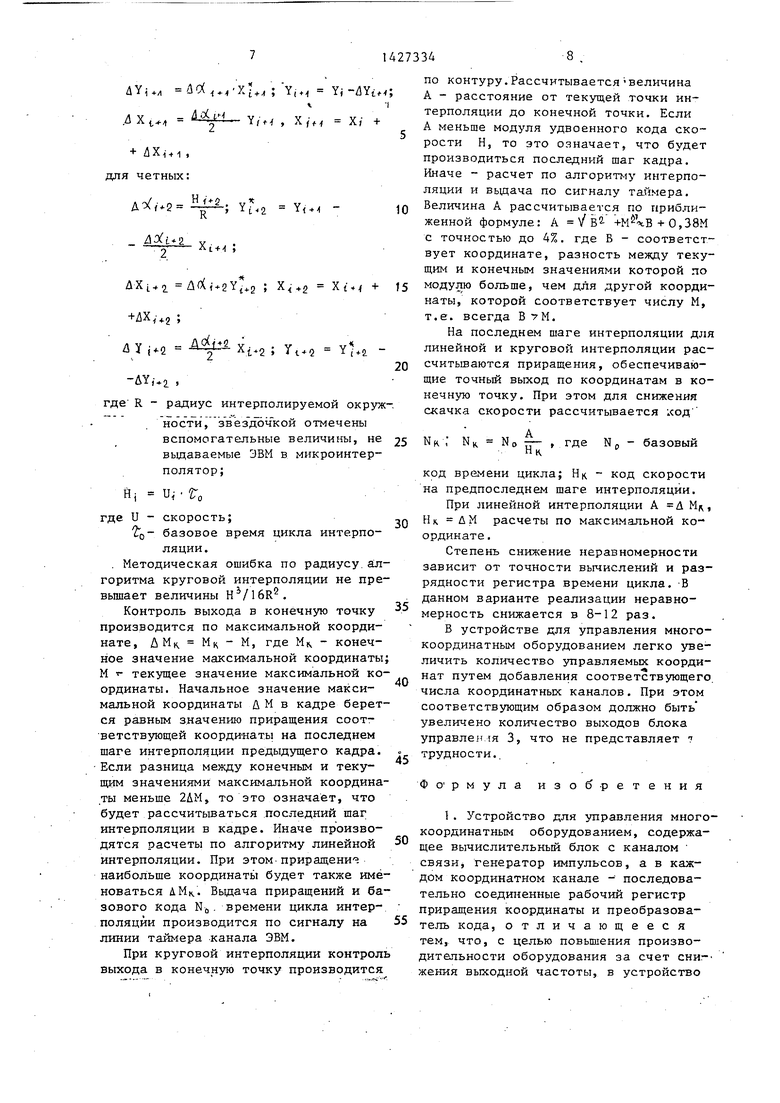

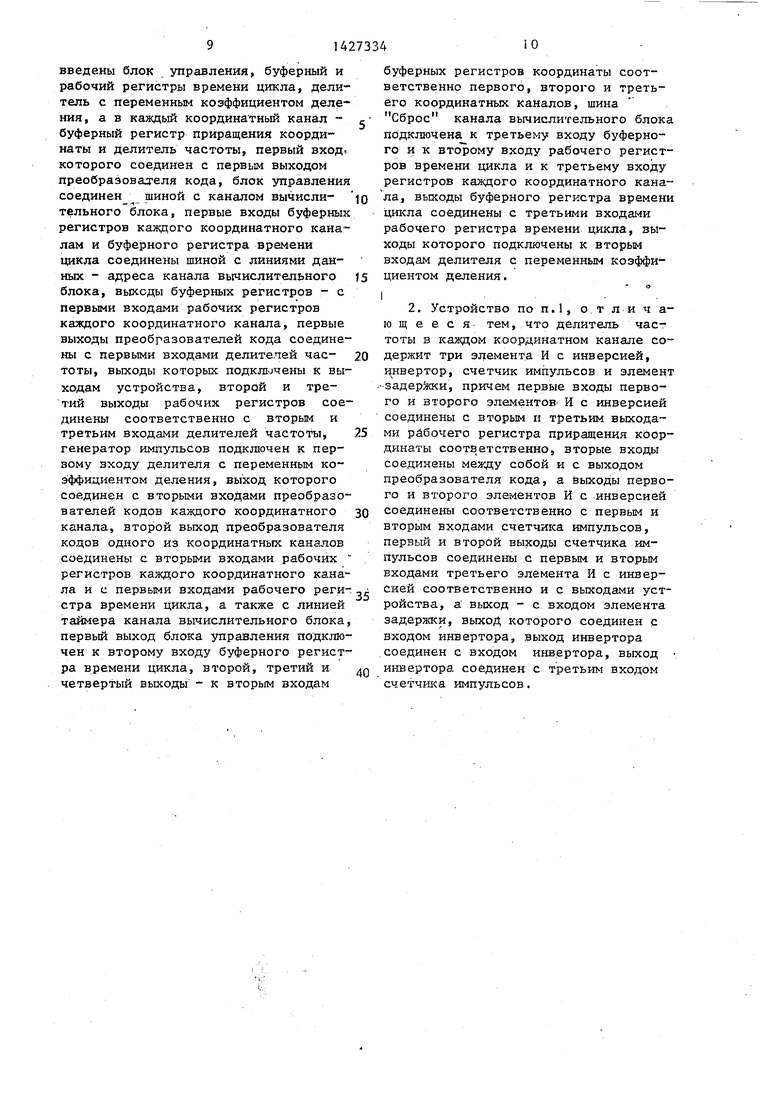

На фиг.1 приведена структурная схема предлагаемого устройства; на фиг.2 - схема блока управления; на фиг.З - схема делителя с переменным коэффициентом деления; на фиг.4 - схема делителя частоты; на фиг.5 - схема преобразователя кода; на фиг.6 и 7 - временные диаграммы, поясняющие работу устройства в целом и делителя частоты.

Устройство управления многокоординатным -оборудованием содержит вы- числительный блок 1 (ЭВМ) с каналом 2 связи, блок управления 3, канал времени цикла 4, три аналогичные канала координат X, Y соответственно 5,6, 7, буферный 8 и рабочий 9 ре- гистры времени цикла, генератор импульсов 10, делитель с переменным коэффициентом деления 11, в каждом координатном канале буферный 12 и рабочий 13 регистры приращения коорди- наты, преобразователь кода 14 и делитель частоты 15, в составе вычислительного блока 1 (ЭВМ) центральный . процессор 16, оперативное запоминающее устройство (ОЗУ) 17, постоянное запоминающее устройство (ПЗУ) 18, устройство управления вводом-выводом 19, устройство ввода программ 20, устройство управления пультовым терминалом 21, пультовой терминал 22. Устройство содержит также линию сброса 23, линию таймера 24, шину 25, линии связи 26, 27. Блок управления 3 содержит канальные приемники 28, эле- менты И 29, 30, триггеры 31, 32, 33, элемент задержки 34, шинный формирователь 35, дешифратор 36.- Делитель с переменным коэффициентом деления 11 содержит первый 37 и второй 38 счетчики импульсов. Делитель частоты 15 содержит три элемента И с инверсией 39, 40, 41, счетчик 42, элемент за- держки на RC-цепи 43, инвертор 44. Преобразователь кода 14 состоит из первого 45 и второго 46 счетчика импульсов. Делитель частоты 15 имеет входы 47, 48.

Входы буферных регистров 8, 12 соединены шинами с линиями данных - ад

реса канала 2 ЭВМ 1, выходы - с входами рабочих регистров 9, 13. входы преобразователя кода 14 шиной соединены с первыми выходами рабочих регистров координат 13. Первьш вход делителя частоты 15 связан линией с выходом преобразователя кода 14, а с выходов сигналы поступают на выход интерполятора: Первые входы делителя с переменньм коэффициентом деления 11 шиной связаны с выходами рабочего регистра времени цикла 9, второй вход - с выходом генератора 10. Выход делителя с переменным коэффициентом деления 11 подключен к преобразователям кода 14 каждого координатного канала. Выходы блока управления подключены к буферным регистрам 8, 12, а входы - к каналу 2 ЭВМ 1.

Устройство работает следующим образом i

После включения устройства управления многокоординатным оборудованием ЭВМ Г вырабатывает сигнал сброс, по которому обнуляются буферные 8, 12 и рабочие 9, 13 регистры, автоматически запускается программа, хранящаяся в ПЗУ 18. Сигналы на первых выходах преобразователей кода 14 и выходах делителей частоты 15 отсутствуют. Через фиксированные промежутки времени на втором выходе преобразователей кода 14 вырабатывается сигнал начала цикла интерполяции. Этот сигнал по линии 24 осуществляет запись информации из буферйых регистров 8, 12 в рабочие 9, 13, а таюке поступает в канал 2 ЭВМ 1 на линию таймера. Первоначально прерывание программы блока 1 запрещено и реакция блока 1 на сигнал по линии таймера отсутствует.

По командам оператора, подаваемым с пультового терминала 22, сначала вводится управляющая программа (УП) ЧПУ с. устройства ввода программ 20, производится ее синтаксический контроль. Затем производится пуск интерполяции. Разрешается прерьшание программы. По каждому сигналу на линии 24 (линии таймера в канале 2) ЭВМ 1 , загружает буферные регистры 12 многоразрядными приращениями координат и буферный регистр 8 многоразрядным кодом, определяющим в конечном счете, интервал выдачи сигналов по линии связи 24-. Загружаемые величины рассчитываются ЭВМ 1 по алгоритмам линейной или. круговой интерполяции с

многоразрядными.приращениями в течение предыдущего цикла интерполяции. Содержимое буферного регистра времени цикла изменяется только к концу участка интерполяции (кадра интерполяции) для снижения неравномерности. Отметим также, что по сигналу на линии 24 информация из буферных регистров 8, 12 будет переписана в рабочие прежде, чем произойдет загрузка первых от блока 1. Это определяется временной задержкой в ЭВМ 1 на сигнал прерьшания по .линии таймера. Буферные регистры 8, 12 предназначены для воз- можности быстрой загрузки информацией рабочих регистров 9, 12 за один такт генератора 10. Приращения координат из рабочих регистров 13 за время цикла t преобразуются в унитар- ный код преобразователями кодов 14. Делитель частоты 15 снижает неравномерность следования импульсов в течение цикла интерполяции путем деления на четыре, а также переключает им- .- пульсы на выход в положительном или отрицательном направлениях в зависимости от состояния старшего бита регистров 13, прямой и инверсйый выходы которых соединены с входами 47, 48 делителей частоты 15. Координатные каналы вместе осуществляют линейную микроинтерполяцию приращений по принципу двоичных умножителей. Однако скорость микроинтерполяции будет зависеть от двух факторов - величины кодов в регистрах приращений и выходной частоты делителя с переменным к6- зффициентом деления 11, которая при постоянной частоте генератора 0 за- висит от содержимого регистра 9. Работа устройства поясняется временными диаграммами на фиг.6 и 7. Для наглядности принято,- что за время цикла f делителем с переменным коэффи- циентом деления 6. вырабатывается 32 импульса, а в рабочем регистре приращения координаты хранится число 17. На фиг.2 приведен пример реализации схемы блока управления. Канальные приемники 28 предназначены для усиления и инверсии сигналов канала. На элемент И 29 поступают 3-12 разряды адреса-данных и сигнал ВУ - внешнее устройство, который является логиче- ским объединением по И сигналов на линиях 13-15 адреса данных, вырабаты- вается блоком 1 и обозначает, что про происходит обращение к.внешнему устройству. Для регистров 8, 12 выбраны адреса 177760-177776 (восьмеричные числа). При обращении к этим адресам в адресной частиц цикла обмена с блока 1 на D-вход триггера 31 поступает 1. Сигнал СИЛ., вырабатьюаемый центральным процессором 16 при передаче адреса, фиксирует факт выборки устройства в триггер 31, а также адрес регистра в триггерах 32, 33, При передаче данных центральным процессорен вырабатывается сигнал вывод, который при условии выборки устройства через злемент И 30, элемент задержки 34, пгиннйй формирователь 35 поступает в канал 2 блока 1 и подтверждает выборку, а также вк.гаочает дешифратор 36. В зависимости от значений линий ДА.02, ДА01 на одной из четырех выходных линий дешифратора 36 появляется сигнал, по которому будет произведена запись данных в один из четырех буферных рв- гистррв 8, 12. Элемент задержки 34 необходим для надежной записи данных из канала -2 ЭВМ 1 в буферные регистры.

На фиг.З прршеден пример реализации схемы делителя с переменным коэффициентом деления II. Он состоит из последовательно соединенных счетчиков 37 и 38. По линии 26 на первьй счетчик поступают импульсы с генератора импульсов 10, по шине 27 - код числа N, определяющий выходную частоту на линии 27. По каждому выходному импульсу производится запись параллельного кода из буферного регистра времени цикла в счетчики 37 и 38

.«

по шине 25. Поэтому fp STT

«

где fr - частота генератора.

На фкг.4 приведена схема делителя частоты 15, содержащая элементы И с инверсией 39-41, счетчик 42, элемент задержки на КС-цепи 43 и инвертор 44. Делитель частоты 15 делит на четьфе выходную частоту преобразователя кода 14 для снижения неравномерности, а также распределяет импульсы по двум каналам в зависимости от знака приращения. Особенностью схемы является то что при изменении знака Приращения информации, хранимая в счетчике, не теряется и правильно отрабатьшается. По линии 49 поступают сигналы из преобразователя кода 14. Если приращение положительно, то. на линии. 47, -

М, а на линии 48 - О, счетчик ра

ботает на суммирование, При отрицательном знаке приращения на линии 47 - О, на линии 48 - 1 и счетчик работает на вычитание. После выдачи каждого импульса на выход Х или -X в счетчик 42 записьшается в режим параллельной записи число ОП (одиннадцать). При этом на выходах -X и tX - 1, на входе V счетчика 19 - также 1. С приходом четвертого импульса на линии +Х появится уровень О. Через время задержкиj определяемое RC-цепью, на вход V счетчика 42 поступит сигнал О, устанавливающий счетчик 42 в состояние 1011. При отрицательном знаке приращения счетчик работает на вычитание и с приходом четвертого импульса нулевой уровень появится на линии -X. В остальном - аналогично предыдущему случаю.

Пусть выбрано основное время цикла и рассчитан код, который будет вьзда- ваться при расчете приращений по горитму интерполяции. Блок 1 -производит интерполяцшо с многоразрядными прира1цениями, вычисляя приращения координат за базовое время цикла с .

Эйлера при линейной интерполяции:

2lL.. L

, Y--.

-;

Xi- X; +ci.

c/z Hi4-i;

Таким образом, выходные сигналы уст

ройства передаются в приводы уровнем Способ интерполяции не имеет сущест- 0. Работа схемы при изменении зна- 5 веннОго значения. Например, хорошие ка приращения демонстрируется диаг- результаты дает расчет по формулам раммой на фиг.6. В предлагаемом примере изменение знака наступило в тот момент, когда в счетчике 42 хранилось число 12. В этом случае на линии -X 30 появится сигнал только с приходом пятого импульса, появивщегося после перемены знака приращения. Таким образом, исключается потеря информации при перемене знака приращения. 35

На фиг.5 приведена схема преобразователя кода 14. Схема содержит два счетчика 45 и 46. По линии 27 поступают импульсы из делителя с переменным коэффициентом деления 11. На выходе А1 счетчика 46 за время цикла появится число импульсов, задаваемое кодом из рабочего регистра. Эти выходы соединены с делителями частоты

15. На линии 24 появляется сигнал на- 45 o(ji , оСу, Ы рассчитываются один раз чала рабочего цикла через каждые 4096 всего участка интерполяции) кадра импульсов, по которому заполняется

4-1 - +0(LjHt4 ;

Z 14 Z-1 +(Xz Vi i14 ,

где Хц,, Y , Zy - координаты, конечной точки;

L - длина участка интерпо- 40 ляции; о(); AY i-, i ;о(у-Н,

AY,4 ,o(z HL- - f AZif приращения ко координат X, Y, Z; i - номер шага; Н;.. - перемещение по контуру интерполяции за время цикла Т о Величины

VII). Разгон и торможение производится путем изменения И.

рабочие регистры и прерьшается программа ЭВМ 1 .

Регистры координатных каналов 13- разрядные. 1-12 разряды - приращение по координате в прямом коде, соединяются с 0-11 разрядами шины адреса- данных канала 2 ЭВМ , 13 разряд - знак приращения, соединяется с 15 разрядом адреса - данных. На преобразователь кода 14 поступают 12 разрядов кода, причем младшие разряды кода .соединяются с нижними линиями

на фиг. 5, старшие - с верхними . Тринадцатый разряд регистров 13 (прямой и инверсный выходы) поступает на входы делителя частоты 15 по линиям 47, 48. Регистры времени цикла - восьмираз- рядные, входы буферного регистра В соединены с 0-7 разрядами шины адреса -. данных канала 2 блока 1. Время рабочего чикла определяется формулой

Г 256 - Nf7

где N - код в рабочем регистре времени цикла 9;

fi- - чайтота генератора 10.

Пусть выбрано основное время цикла и рассчитан код, который будет вьзда- ваться при расчете приращений по горитму интерполяции. Блок 1 -производит интерполяцшо с многоразрядными прира1цениями, вычисляя приращения координат за базовое время цикла с .

Эйлера при линейной интерполяции:

Способ интерполяции не имеет сущес веннОго значения. Например, хороши результаты дает расчет по формулам

2lL.. L

, Y--.

-;

Xi- X; +ci.

c/z Hi4-i;

соб интерполяции не имеет су нОго значения. Например, хор ультаты дает расчет по форму

соб интерполяции не и нОго значения. Наприм ультаты дает расчет п

4-1 - +0(LjHt4 ;

Z 14 Z-1 +(Xz Vi i14 ,

o(ji , оСу, Ы рассчитываются один раз всего участка интерполяции) кадра

где Хц,, Y , Zy - координаты, конечной точки;

L - длина участка интерпо- ляции; о(); AY i-, i ;о(у-Н,

AY,4 ,o(z HL- - f AZif приращения ко- координат X, Y, Z; i - номер шага; Н;.. - перемещение по контуру интерполяции за время цикла Т о Величины

o(ji , оСу, Ы рассчитываются один раз всего участка интерполяции) кадра

VII). Разгон и торможение производится путем изменения И.

Для круговой интерполяции в плос- , кости высокой точностью обладает алгоритм с чередованием порядка расчета приращений второго порядка, в котором для нечетных шагов применяются формулы:

к к X (+ X

Xf +

4-421111 V

+ Y, ,

4Yi., 40(. YiH Yj-/JYi

t

ЛХ. 4fi- Y,M , X/, X/ +

+ 4X1+1, для четных:

-fli Y,., - A3( „

t-f 1 ;

AXi.42 AO(i-b2Yt 2 ; +2 f + +

ЛУ i,2 Д Х.з; y.Q -UY,4i ,

где R - радиус интерполируемой окружности, звездочкой отмечены вспомогательные величины, не вьщаваемые ЭВМ в микроинтерполятор;

Hi Го

где и - скорость;

базовое время цикла интерполяции.

Методическая ошибка по радиусу.алгоритма круговой интерполяции не превышает величины .

Контроль выхода в конечную точку производится по максимальной координате, ДМ MK - И, где Мц, - конечное значение максимальной координаты М - текущее значение максимальной координаты. Начальное значение максимальной координаты Д М в кадре берется равньм значению приращения соот- ветствующей координаты на последнем шаге интерполяции предыдущего кадра. Если разница между конечным и текущим значениями максимальной координаты меньше 2ДМ, то зто означает, что будет рассчитываться последний шаг интерполяции в кадре. Иначе производятся расчеты по алгоритму линейной интерполяции. При этом-приращени наибольше координаты будет также именоваться ДМк. Вьщача приращений и базового кода NO. времени цикла интер- поляцйи производится по сигналу на линии таймера .канала ЭВМ.

При круговой интерполяции контрол выхода в конечную точку производится

0

5

0

5

п

5 5

0

5

по контуру.Рассчитывается величина А - расстояние от текущей точки интерполяции до конечной точки. Если А меньше модуля удвоенного кода скорости Н, то это означает, что будет производиться последний шаг кадра. Иначе - расчет по алгоритму интерполяции и выдача по сигналу таймера. Величина А рассчитывается по приближенной формуле: А /В ,38M с точностью до 4%. где В - соответствует координате, разность между текущим и конечным значениями которой по модулю больше, чем для другой координаты, которой соответствует числу М, т.е. всегда ВтМ.

На последнем шаге интерполяции для линейной и круговой интерполяции рас- считьшаются приращения, обеспечивающие точный выход по координатам в конечную точку. При этом для снижения скачка скорости рассчитывается ;сод

д

NK. , NK, NO гг где NO - базовый HK

код времени цикла; HK - код скорости на предпоследнем шаге интерполяции.

При линейной интерполяции А Д М, Ни. ДМ расчеты по максимальной координате .

Степень снижение неравномерности зависит от точности вычислений и разрядности регистра времени цикла. -В данном варианте реализации неравномерность снижается в 8-12 раз.

В устройстве для управления многокоординатным оборудованием легко увеличить количество управляемых координат путем добавления соответствующего, числа координатных каналов. При этом соответствующим образом должно быть увеличено количество выходов блока управления 3, что не представляет трудности..

Фо рмула изобретения

1. Устройство для управления многокоординатным оборудованием, содержащее вычислительный блок с каналом связиj генератор импульсов, а в каждом координатном канале - последовательно соедш енные рабочий регистр приращения координаты и преобразователь кода, отличающееся тем, что, с целью повьшгения производительности оборудования за счет сни- женин выходной частоты, в устройство

введены блок управления, буферный и рабочий регистры времени цикла, делитель с переменным коэффициентом деления, а в каждый координа тный канал - буферный регистр приращения координаты и делитель частоты, первый вход: которого соединен С первым выходом преобразовад-еля кода, блок зшравления соединен шиной с каналом вычисли- т«ального блока, первые входы буферных регистров каждого координатного кана лам и буферного регистра времени цикла соединены шиной с линиями данных - адреса канала вычислительного блока, выходы буферных регистров - с первыми входами рабочих регистров каждого координатного канала, первые выходы преобразователей кода соединены с первыми входами делителей час- Тоты, выходы которых подключены к выходам устройства, второй и третий выходы рабочих регистров соединены соответственно с вторым и третьим входами делителей частоты, генератор импульсов подключен к первому входу делителя с переменным коэффициентом деления, выход которого соединен с вторыми входами преобразователей кодов каждого координатного канала, второй выход преобразователя кодов одного из координатных каналов соединены с вторыми входами рабочих регистров каждого координатного канала и с первыми входами рабочего регистра времени цикла, а также с линией таймера канала вычислительного блока первый выход блока управления подключен к второму входу буферного регистра времени цикла, второй, третий и четвертый выходы - к вторым входам

буферных регистров координаты соответственно первого, второго и третьего координатных каналов, шина Сброс канала вычислительного блока пйдключена к третьему входу буферного и к второму входу рабочего регистров времени цикла и к третьему входу регистров каждого координатного кана- ла, выходы буферного регистра времени Цикла соединены с третьими входш 1И рабочего регистра времени цикла, выходы которого подключены к вторые входам делителя с переменным коэффициентом деления.

о

2. Устройство по П.1, о.т ли ч аю щ е е с я тем, что делитель частоты в каждом координатном канале содержит три элемента И с инверсией, г нвертор, счетчик импульсов и элемент -задержки, причем первые входы первого и второго элементов- И с инверсией соединены с вторым и третьим выходами рабочего регистра приращения координаты соответственно, вторые входы соединены между собой и с выходом преобразователя кода, а выходы первого и второго элементов И с .инверсией соединены соответственно с первым и вторым входами счетчика импульсов, первый и второй выходы счетчика импульсов соединены с первым и вторым входами третьего элемента И с инверсией соответственно и с выходами устройства, а выход - с входом элемента эадерноси, выход которого соединен с входом инвертора, выход инвертора соединен с входом инвертора, выход инвертора соединен с третьим входом счетчика импульсов.

/

D/ DZ P3

т

V

| название | год | авторы | номер документа |

|---|---|---|---|

| УПРАВЛЯЮЩИЙ АППАРАТНО-ПРОГРАММНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 2001 |

|

RU2222028C2 |

| Устройство для отображенияиНфОРМАции | 1976 |

|

SU798961A1 |

| Система для автоматического числового управления координатными перемещениями при обработке изделий микроэлектроники | 1990 |

|

SU1835534A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Устройство для программного управления намоточным станком | 1984 |

|

SU1232044A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1709269A1 |

| Устройство для считывания графической информации | 1973 |

|

SU667976A1 |

| Устройство для считывания графической информации | 1981 |

|

SU1013989A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1977 |

|

SU732934A1 |

| МУЛЬТИПЛЕКСОР ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2295148C1 |

Изобретение относится к технике числового программного управления станками. Целью изобретения является повышение производительности оборудования за счет снижения выходной частоты. Устройство содержит вычислительный блок - ЭВМ 1, рассчитываюп(ий многоразряднь1е коды приращений координат, канал связи 2, блок управления 3, три координатных канала 5,6,7, осуществляющих линейную микроинтерполяцию приращений, и канал 4 времени цикла интерполяции. Устройство позволяет изменять программно время цикла интерполяции, что снижает неравномерность выходных импульсов, уменьшает ограничения на скорость подачи станка с ЧПУ и повышает его производитель- ность. 1 з.п. ф-лы, 7 ил. (Л 4 to со оо 4 Фиг.1

i 6

P+r

21

Фаг.Ъ

Сигнал

/I иная ч 5 Линия ffS

& La ПП ПП ПП ПП ПП П

t

+х

птizni

| Линейно-круговой интерполятор | 1977 |

|

SU732818A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Заявка Японии № 5343629, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-09-30—Публикация

1987-01-04—Подача