Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах для сопряжения ЭВМ.

Цель изобретения - повьш1ение быстродействия устройства.

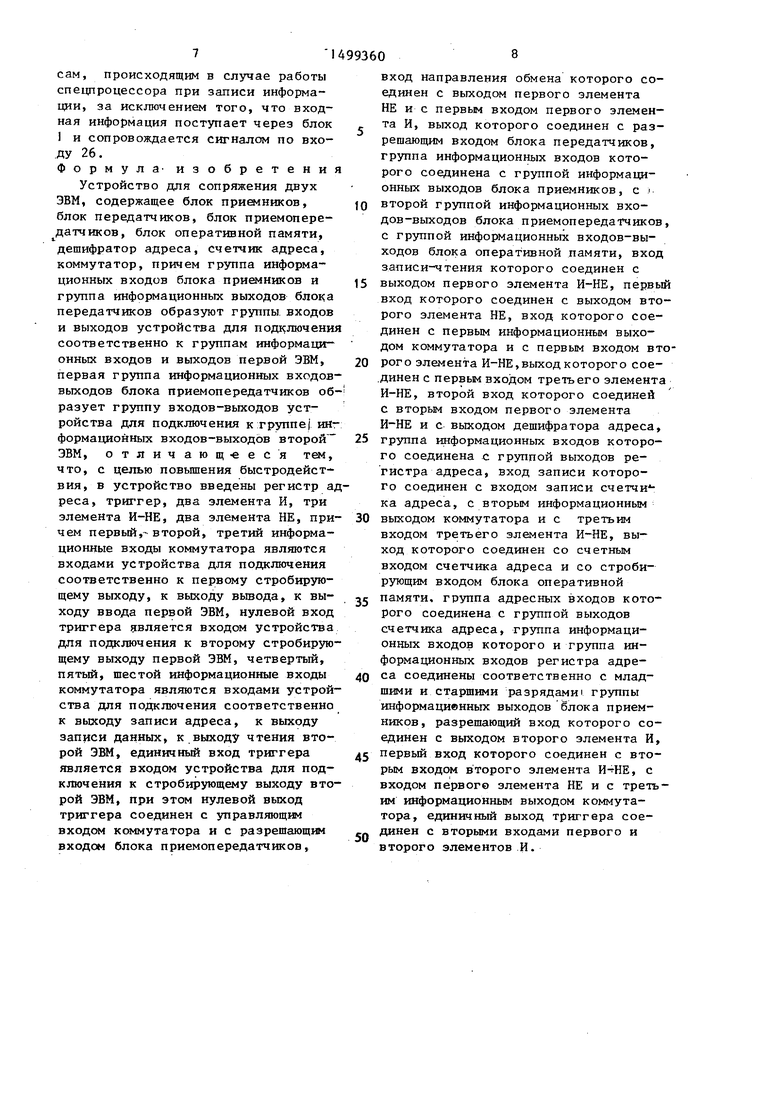

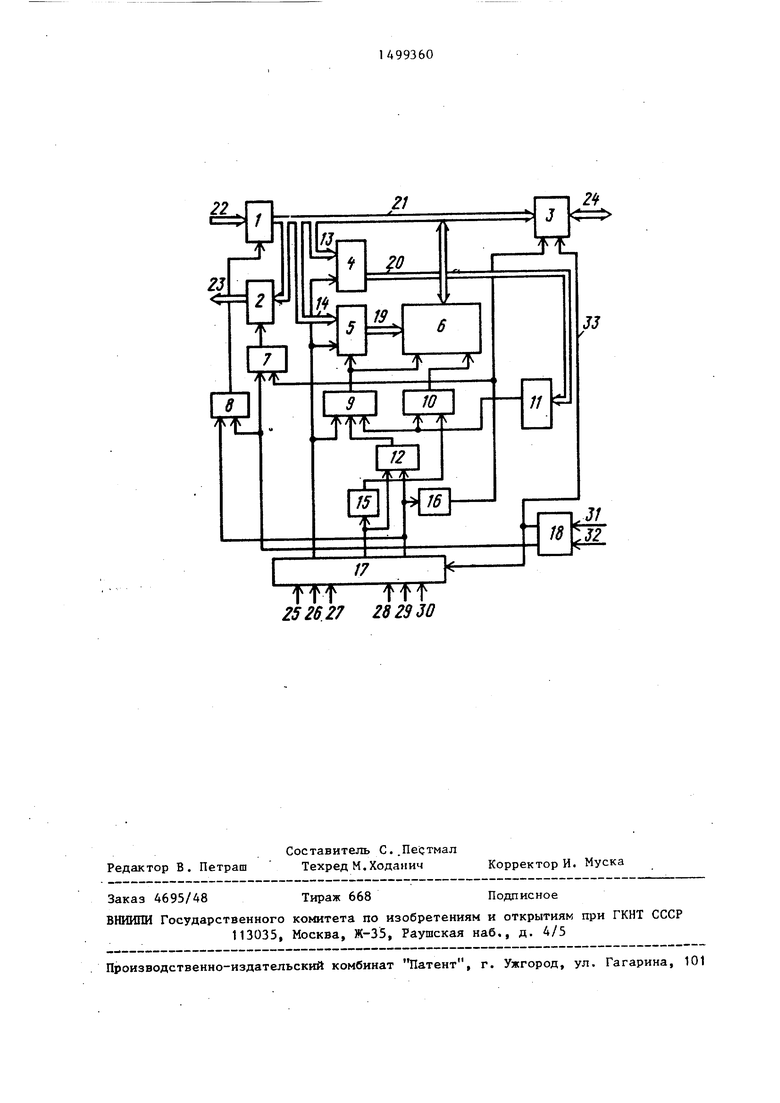

На чертеже приведена структурная схема устройства..

Устройство содержит блок 1 приемников, блок 2 передатчиков, блок 3 приемопередатчиков, регистр 4 адреса, счетчик 5 адреса, блок 6 оперативной памяти, элементы И 7 и 8, элементы И-НЕ 9 и 10, дешифратор 11 адреса, элемент И-НЕ 12, группу старших разрядов 13 и группу младших разрядов 14 внутренней магистрали, элементы НЕ 15 и 16, коммутатор 17, триггер . 18, адресные шины 19 и 20, внутреннюю магистраль 21, группы входов 22 и выходов 23 устройства, группу входов-выходов 24 устройства, входы 25-32 устройства, выход 33 триггера.

Рассмотрим раб;оту устройства на примере обмена массивами информации

между контроллером И2 3.858.383 из состава первой ЭВМ типа Электрони- ка-60 и спецпроцессором, второй ЭВМ, подключаемым к группе входов- выходов 24 устройства.

При этом группу входов 22 подключают к выходным информационным линиям контроллера И2, группу выходов 23 - к входным информационным линиям контроллера И2, вход 25 - к выходу разряда РСО регистра состояния контроллера, вход 31 - к выходу разряда РС1, вход 26 - к линиям Вьшод, вход 27 - к линии Ввод контроллера И2, Входы 28-31 подключают к управляющим цепям магистрали спецпроцессора, группу входов-выходов 24 - к информационно-адресным цепям магистрали спецпроцессора. Для приведения в исходное состояние ведущее устройство (например, контроллер И2) подает по входу 31 импульсный сигнал активного (низкого) уровня, устанавливая триггер 18 в состояние О. При этом на нулевом выходе

§

(Л

4

со со

00 О5

3149

формируется сигнал высокого уровня,

который поступает на управляющий вход коммутатора 17 и обеспечивает коммутацию сигналов по входам 28-30 на второй, первый, третий выходы коммутатора соответственно. Сигнал с нулевого выхода триггера поступает на разрешающий вход блока 3 приемопередатчиков, переводя их в активное состояние.

Сигнал с единичного выхода триггера низким уровнем поступает на вторые входы элементов И 8 и 7, обеспечивая на их выходах сигналы низкого уровня, которые блокируют блоки 1 и 2, т.е. устройство логически подключается к спецпроцессору. Спецпроцессор, получая возможность управления устройством, осуществляет загрузку блока 6 массивом информации через блок 3, магистраль 21 и затем формирует импульсный сигнал активного (низкого) уровня на входе 32, переводящий триггер 8 в состояние 1 и логически подключающий контроллер И2 к устройству. Контроллер И2 осуществляет считьшание информации из блока 6 через В21утреннюю магистраль 21 и блок 2 передатчиков, затем сиг- налом по втсоду 31 возвращает устройство в исходное состояние.

Рассмотрим более подробно процесс записи массива информации спецпроцессором. Магистраль процессора содержи группу входов-выходов 24, обеспечи- вайщих передачу в устройство адресны сигналов блока оперативной памяти и сигналов данных за счет разделения и во времени, а также сигналов управле ния по входам 28, 29, 30 и 32. Сигналы адреса блока 6 сопровождаются сигналом по входу 28, запаздывающим относительно них на время распространения от входов 24 до информационных входов регистра 4 адреса и счетчика адреса через блок 3 и магистраль 21.

В первой фазе Обмена спецпроцессор устанавливает на входах-выходах 24 начальный адрес блока 6. При этом на входах 28-30 обеспечиваются пассивные (низкие) уровни сигналов, а на первом, втором.и третьем выходах коммутатора 18 - пассивные (высокие) уровни сигналов. Сигнал вы- сокого уровня, проходя через элемент НЕ 16, обеспечивает блокировку элемента И 7 и осуществляет установку блока 3 в состояние коммутации информации с входов-выходов 24 на магистраль 21. Далее с задержкой относительно адресных сигналов спецпроцессор формирует импульсный сигнал высокого уровня по входу 28, при этом на втором выходе коммутатора 17 появляется импульсный сигнал низкого уровня, обеспечивающий запись адреса в регистр 4 и счетчик 5, одновременно блокируя элемент И-НЕ 9 по третьему входу.

Младшие разряды 14 адреса, записанные в счетчик 5 адреса, поступают на блок 6, обеспечивая адресацию нулевой ячейки. Старшие разряды 13 адреса, записанные .в регистр 4 адреса, поступают на вход дешифратора 1 1 , который формирует активный сигнал высокого уровня на его выходе при обращении спецпроцессора к блоку 6 и пассивный низкий уровень при обращении спецпроцессора к други устройствам на своей магистрали.

Предположим, что в данной фазе происходит обращение к блоку 6, т.е высокий уровень сигнала с выхода дешифратора 11 поступает на вторые входы элементов И-НЕ 9 и 10. После окончания сигнала по входу 28 спецпроцессор снимает сигналы адреса входов-выходов 24 и во второй фазе обмена устанавливает на входах-выходах 24 первое информ ационное слово массива данных. Затем с задержкой на время распространения информации с входов-выходов 24 до входов-выходо блока 6 спецпроцессор формирует импульсный сигнал высокого уровня на входе 29. При этом на первом выходе коммутатора 17 формируется импульсный сигнал низкого уровня, который, поступая через элемент НЕ 16 на первый вход элемента И-НЕ 1 О, обеспечивает на входе записи-чтения блока 6 сигнал низкого уровня (код операции Запись). Кроме того, сигнал низкого уровня с первого выхода коммутатора 17 через элемент И-НЕ 12 обеспечивает низкий уровень сигнала на выходе элемента И-НЕ 9, сигнал с которого подается на стробирующий вход блока 6, обеспечивая запись первого информационного слова с магистрали 21 в блок 6 по нулевому адресу.

При исчезновении импульсного сигнала (окончание записи)его задний (положительный) фронт осуществляет увеличение содержимого счетчика 5

на единицу, обеспечивая подготовку адреса следующей ячейки памяти. Затем спецпроцессор помещает на входы-выходы 24 следующее слово масси- ва данных и формирует второй импульсный сигнал на входе 29, т.е. запись следующего слова осуществляется без операции загрузки адреса, только за счет приращения значения адреса в предьщущем цикле. Процессы записи последующих информационных слов осуществляются аналогичным образом.

Чтение информации спецпроцессором осуществляется следующим образом: реализуется запись нача льного адреса аналогично рассмотренной первой фазе обмена.

Вторая фаза начинается с момента подачи спецпроцессором сигнала высокого уровня на вход 30. При этом сигнал низкого уровня (активного) с третьего выхода коммутатора 17 через элемент НЕ 16 обеспечивает такой ре- жим работы блока 3, при котором информация с магистрали 21 транслируется на входы-выходы 24. Одновременно сигнал низкого уровня с третьего выхода коммутатора 17 через элемент И-НЕ 12 обеспечивает условия формирования сигнала низкого уровня на выходе элемента И-НЕ 9. На выходе элмента И-НЕ 10 присутствует сигнал высокого уровня (код операции Чтение

Стробирующий сигнал с выхода элемента И-НЕ 9 поступает на вход блока 6, обеспечивая на его выходах и магистрали 21 требуемое слово информации, которое транслируется через бло 3 на входы-выходы 24. Спеирроцессор осуществляет прием информахдаи с входов-выходов 24 и затем снимает сигнал с входа 30. При этом задний фрон сигнала на выходе элемента И-НЕ 9 обеспечивает по счетному входу счетчика 5 увеличение его содержимого на единицу. Считьшание следующих информационных слов осуществляется циклической подачей сигналов по входу 30 без выполнения операций по загрузке счетчика 5 и регистра 6 адреса .

По;, окончании записи (чтения) информации спецпроцессор формирует им-

пульсный сигнал низкого уровня по входу 32, обеспечивая установку триггера 18 в единичное состояние и логическое отключение спецпроцессора .При

ю

15

0 25 О ос

0

g.

5

0

этом коммутатор 17 обеспечивает прохождение сигналов с входов 25-27 на второй, первый и третий выходы соответственно за счет сигнала низкого уровня на его управляющем входе.Функции сигнала на входах 25-27 аналогичны функциям сигналов на входах 28-30.

Сигнал высокого уровня с единичного выхода триггера 18 обеспечивает активные уровни на вторых входах элементов И 7 и 8. Причем в исходном состоянии сигнал пассивного (высок ог Ь) уровня с третьего выхода коммутатора обеспечивает активный уровень на выходе И 8 и обеспечивает включение блока 15тран- слирующего информацию с входов 22 на магистраль 21. Сигнал низкого уровня с выхода элемента НЕ 16 блокирует элемент И 7, а следовательно, и блок 2.

Контроллер И2-осуществляет чтение информации из блока 6 следующим образом; устанавливает на входе 25 активный высокий уровень сигнала, формирует на входах 22 код нулевого адреса, затем снимает сигнал с входа 25, при этом задним фронтом данного сигнала осуществляется запись адреса с магистрали 21 в регистр 4 и счетчик 5 адреса.

Схемная реализация контроллера И2 такова, что в момент смены информации на входах 22 (выходном регистре контроллера) формируется импульсный сигнал по входу 26, однако в момент записи адреса в регистр 4 и счетчик

5Сигнал логического О на третьем входе элемента И-НЕ 9 блокирует блок

6по стробирутощему входу. Затем контроллер И2 осуществляет подачу сигнала высокого уровня по входу 27. При этом процессы, происходящие в устройстве, аналогичны рассмотренным при подаче сигнала по входу 30 .и

в случае работы спецпроцессора за исключением того, что выдача информации из блока 6 осуществляется через блок 2, управляемый с выхода элемента И 7 сигналом высокого уровня с выхода элемента НЕ 16. При этом Сигнал низкого уровня с третьего выхода коммутатора 17 формирует на выходе элемента И 8 потенциал низкого уровня, блокирующий блок 1.

Процессы записи информации в блок 6 контроллером И2 аналогичны процес-

сам, происходящим в случае работы спецпроцессора при записи информации, за исключением того, что входная информация поступает через блок 1 и сопровождается сигналом по входу 26. Формула изобретения

Устройство для сопряжения двух ЭВМ, содержащее блок приемников, блок передатчиков, блок приемопередатчиков, блок оперативной памяти, дешифратор адреса, счетчик адреса, коммутатор, причем группа информационных входов блока приемников и группа информационных выходов блока передатчиков образуют группы, входов и выходов устройства для под1 лючения соответственно к группам информационных входов и выходов первой ЭВМ, первая группа информационных входов- выходов блока приемопередатчиков образует группу входов-выходов устройства для подключения к группе} информационных входов-выходов второй ЭВМ, отличающ-ееся тем, что, с целью повьшения быстродействия, в устройство введены регистр адреса, триггер, два элемента И, три элемента И-НЕ, два элемента НЕ, причем первый,-второй, третий информационные входы коммутатора являются входами устройства для подключения соответственно к первому стробирую- щему выходу, к выходу вьшода, к выходу ввода первой ЭВМ, нулевой вход триггера является входом устройства для подключения к второму стробирую- щему выходу первой ЭВМ, четвертый, пятый, шестой информационные входы коммутатора являются входами устройства для подключения соответственно к выходу записи адреса, к выходу записи данных, к выходу чтения второй ЭВМ, единичный вход триггера является входом устройства для подключения к стробирующему выходу второй ЭВМ, при этом нулевой выход триггера соединен с управляющим входом коммутатора и с разрешающим входом блока приемопередатчиков.

вход направления обмена которого соединен с выходом первого элемента НЕ и с первым входом первого элемента И, выход которого соединен с разрешающим входом блока передатчиков, группа информационных входов которого соединена с группой информационных выходов блока приемников, с j второй группой информационных входов-выходов блока приемопередатчиков, с группой информационных входов-выходов блока оперативной памяти, вход записи-чтения которого соединен с выходом первого элемента И-НЕ, первый вход которого соединен с выходом второго элемента НЕ, вход которого соединен с первым информационным выходом коммутатора и с первым входом второго элемента И-НЕ,выход которого соединен с первьм входом третьего элемента И-НЕ, второй вход которого соединей с вторым входом первого элемента И-НЕ и с выходом дешифратора адреса, группа информационных входов которого соединена с группой выходов регистра адреса, вход записи которого соединен с входом записи счетчи - ка адреса, с вторым информационным выходом коммутатора и с третьим входом третьего элемента И-НЕ, выход которого соединен со счетным входом счетчика адреса и со строби- рующим входом блока оперативной памяти, группа адресных входов которого соединена с группой выходов счетчика адреса, группа информационных входов которого и группа информационных входов регистра адреса соединены соответственно с младшими и старшими разрядами группы информацивнных выходов блока приемников, разрешающий вход которого соединен с выходом второго элемента И, первый вход которого соединен с вторым входом второго элемента И-fHE, с входом первого элемента НЕ и с третьим 1Шформационным выходом коммутатора, единичный выход триггера соединен с вторыми входами первого и второго элементов И.

1L

32

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух ЭВМ | 1990 |

|

SU1751771A1 |

| Устройство для сопряжения вычислительной машины с магистралью обмена | 1986 |

|

SU1381519A1 |

| Устройство для сопряжения ЭВМ с М внешними устройствами | 1986 |

|

SU1374232A1 |

| Устройство для преобразования сейсморазведочной информации | 1987 |

|

SU1497599A1 |

| Электронная вычислительная машина с прямым доступом в память | 1987 |

|

SU1529240A1 |

| Устройство индикации состояния ЭВМ | 1989 |

|

SU1667067A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1988 |

|

SU1605241A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1988 |

|

SU1515167A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1288709A1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах для сопряжения ЭВМ. Целью изобретения является повышение быстродействия. Устройство содержит блок оперативной памяти, блок приемников, блок передатчиков, блок приемопередатчиков, регистр адреса, счетчик адреса, дешифратор адреса, коммутатор, триггер, два элемента И, три элемента И-НЕ, два элемента НЕ. 1 ил.

л л лл А л

252627 282930

| Устройство для сопряжения | 1978 |

|

SU746491A1 |

| Авторское свидетельство СССР 760076, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-07—Публикация

1987-12-29—Подача