Изобретение относится к устройствам вычислительной техники и автоматики и может быть использовано при создании различных систем автоматизированного контроля и автоматического управления,

Целью изобретения является повышение быстродействия за счет исключения зависимости скорости работы устройства от типа управляющей ЭВМ и расширение области применения устройства за счет появления возможности сопряжения ЭВМ с внешними устройствами, имеющими скорости обмена как выше, так и ниже скорости ЭВМ, т.е. с разноскоростными внешними устройствами.

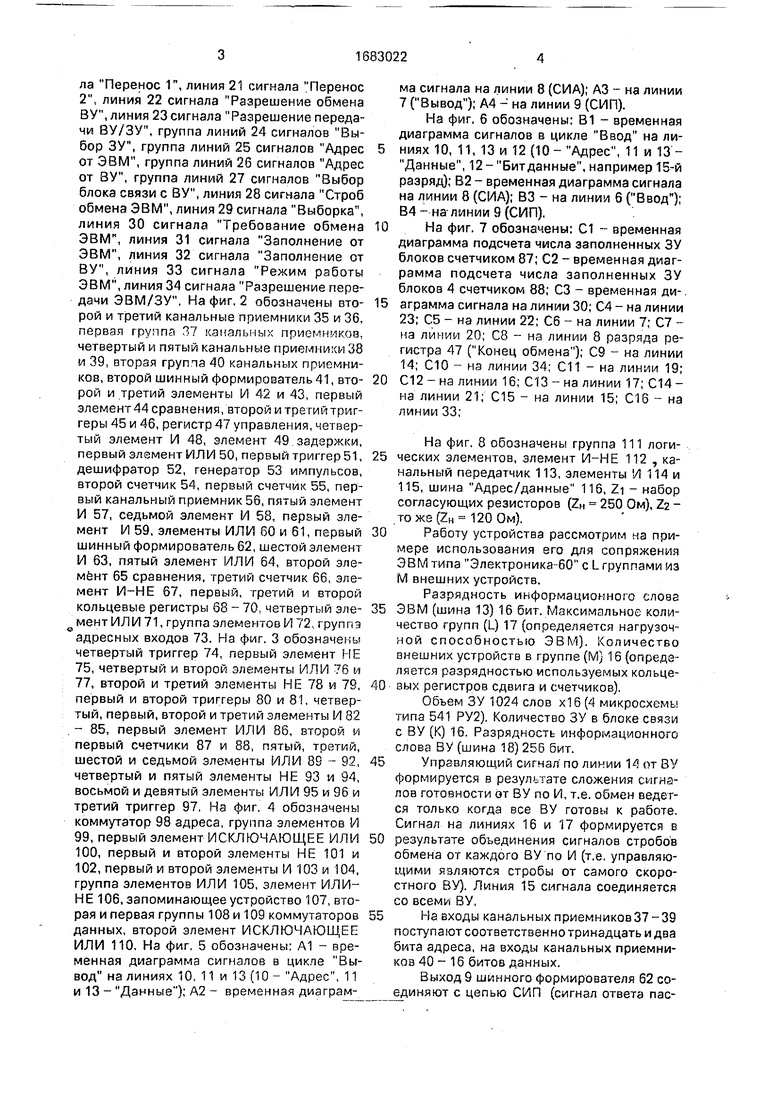

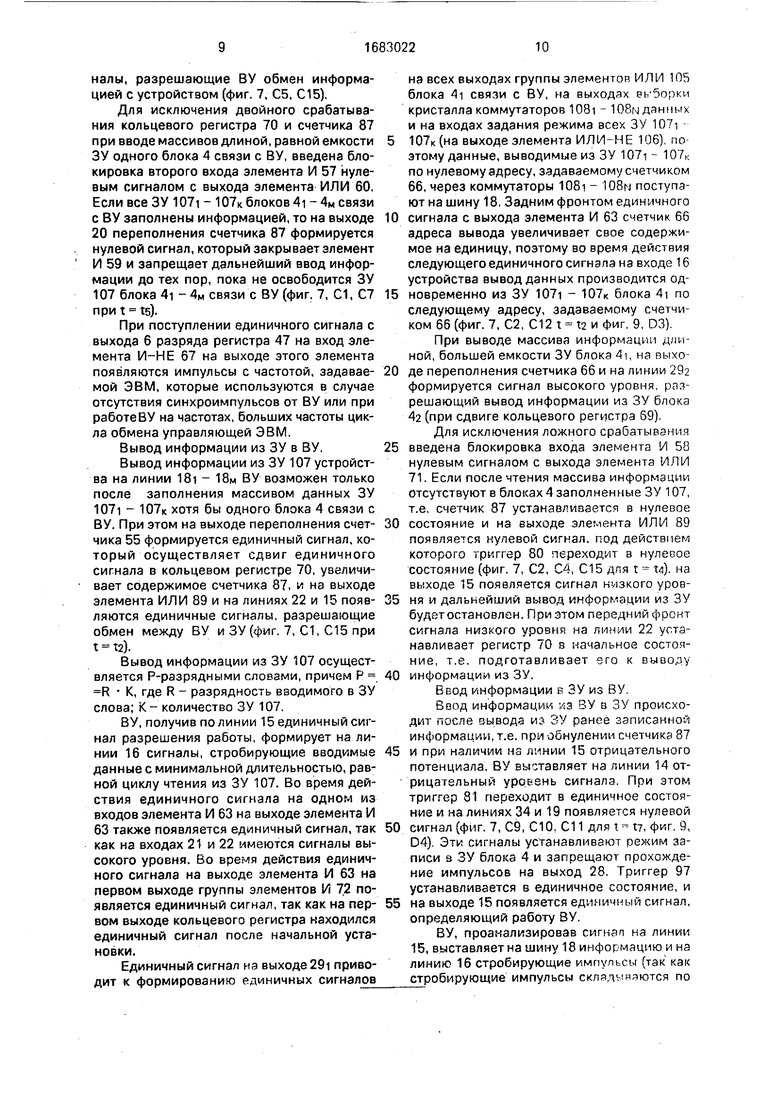

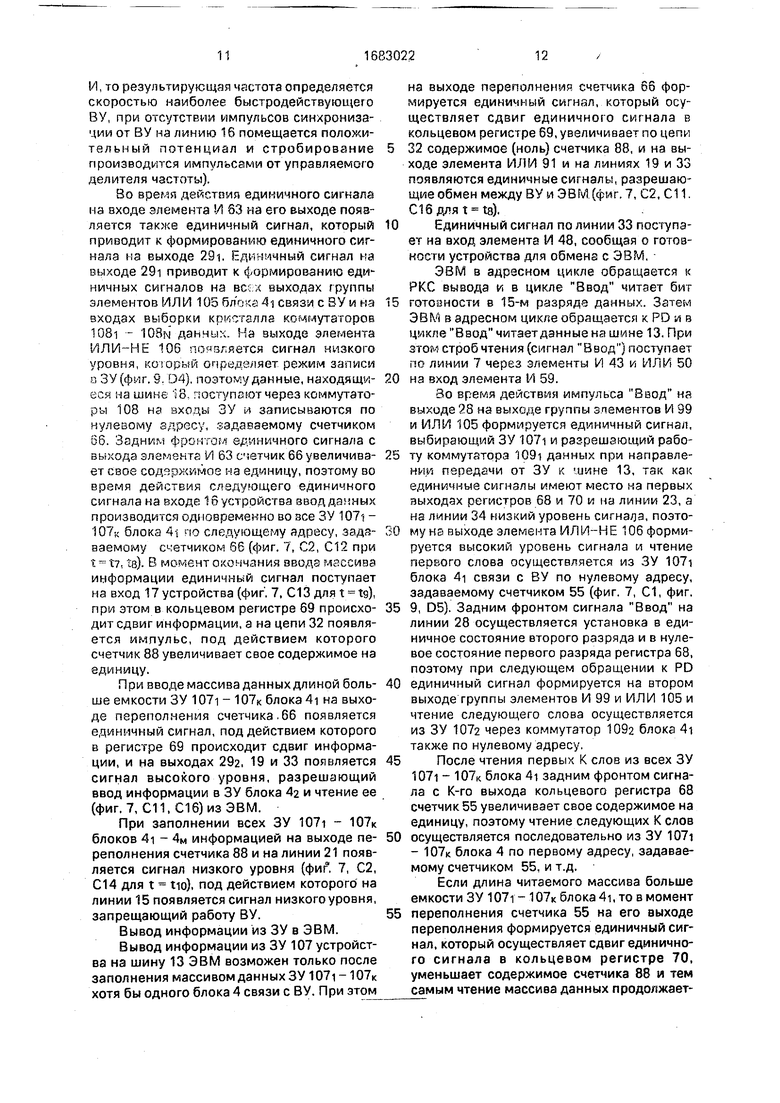

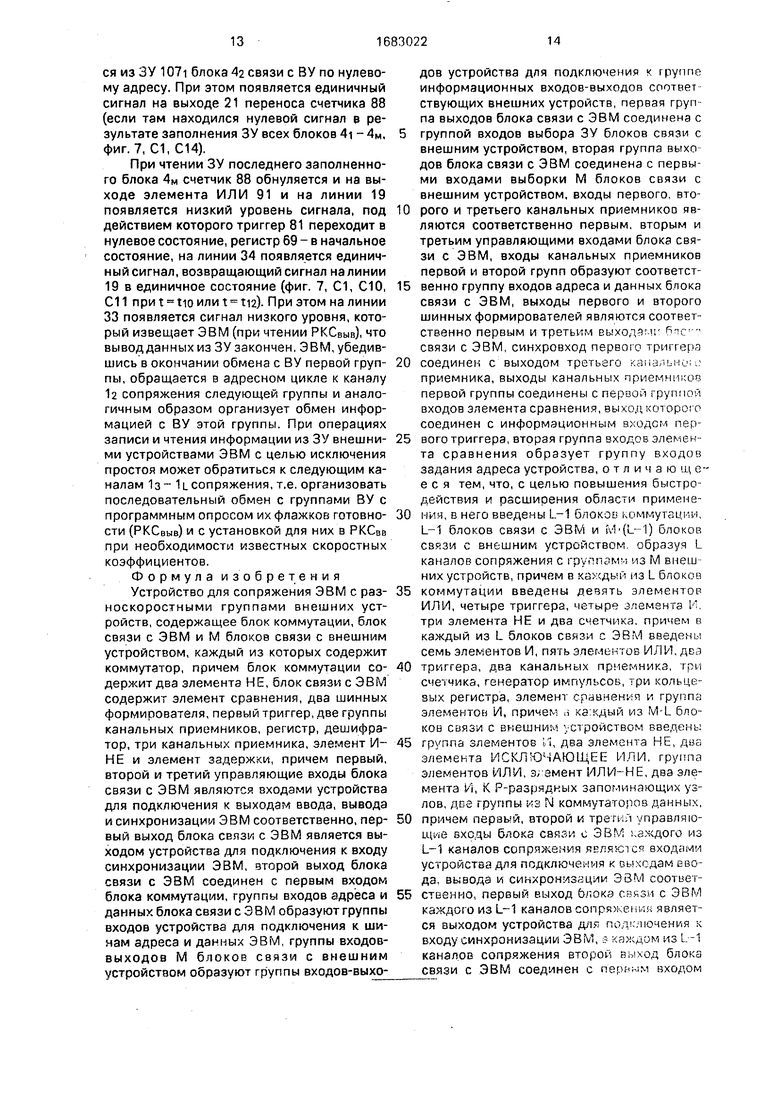

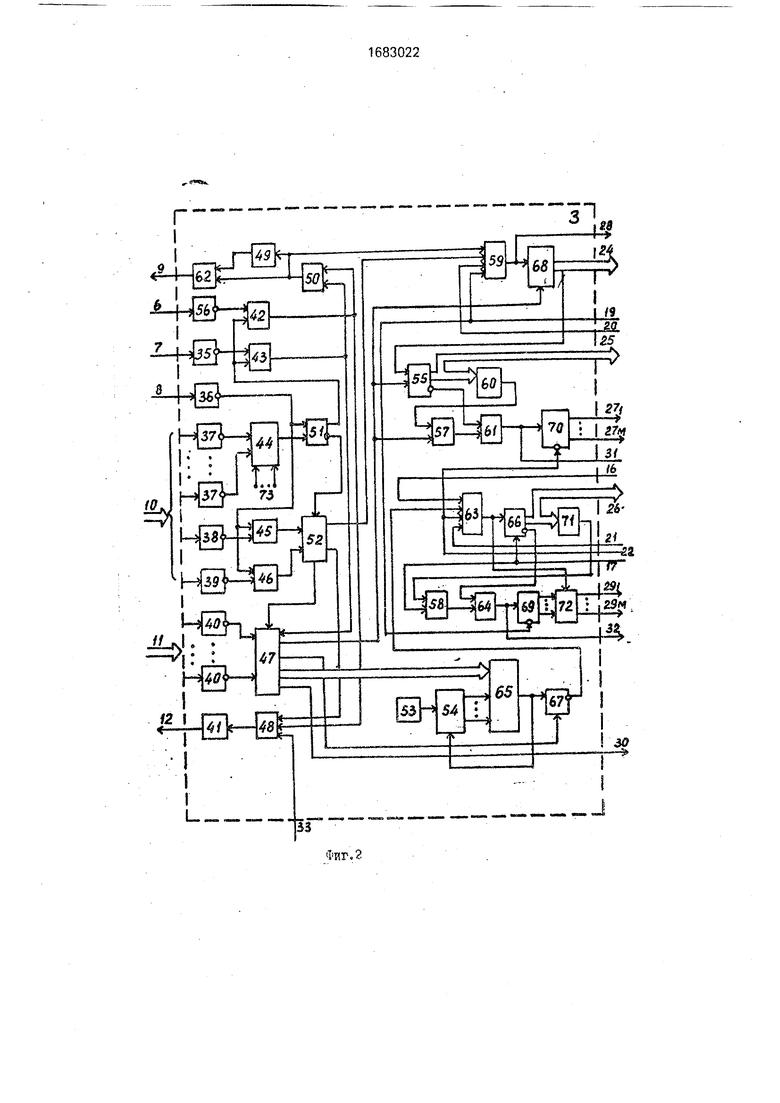

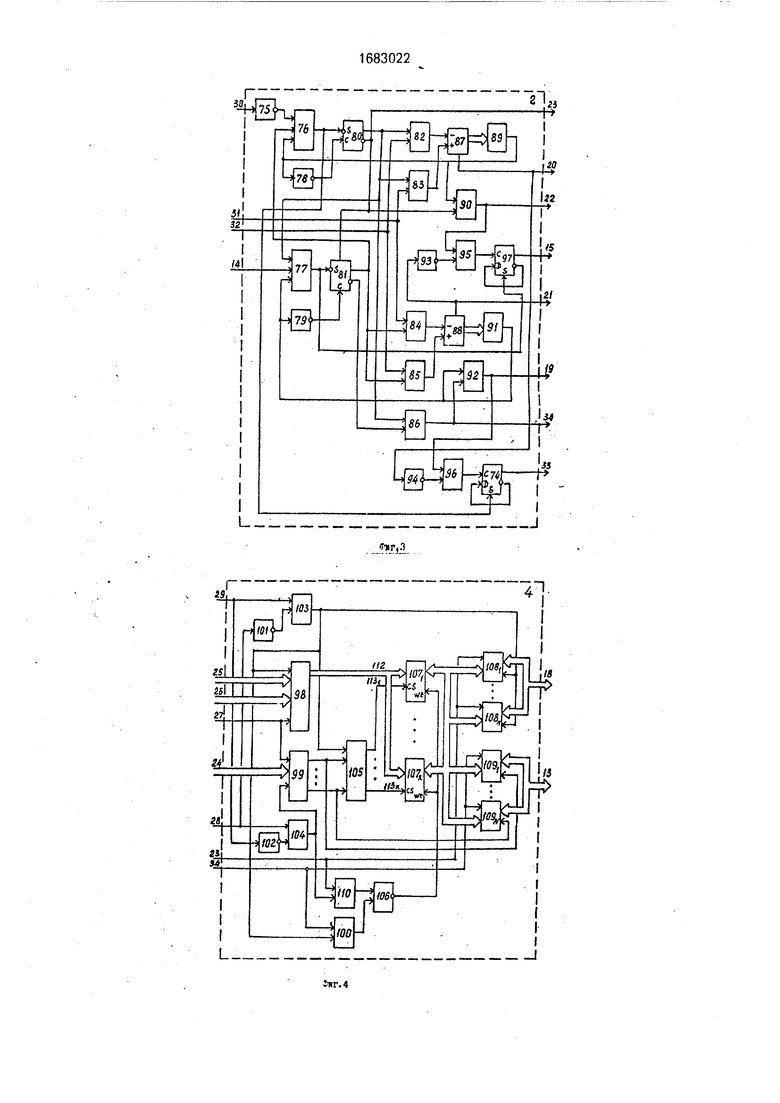

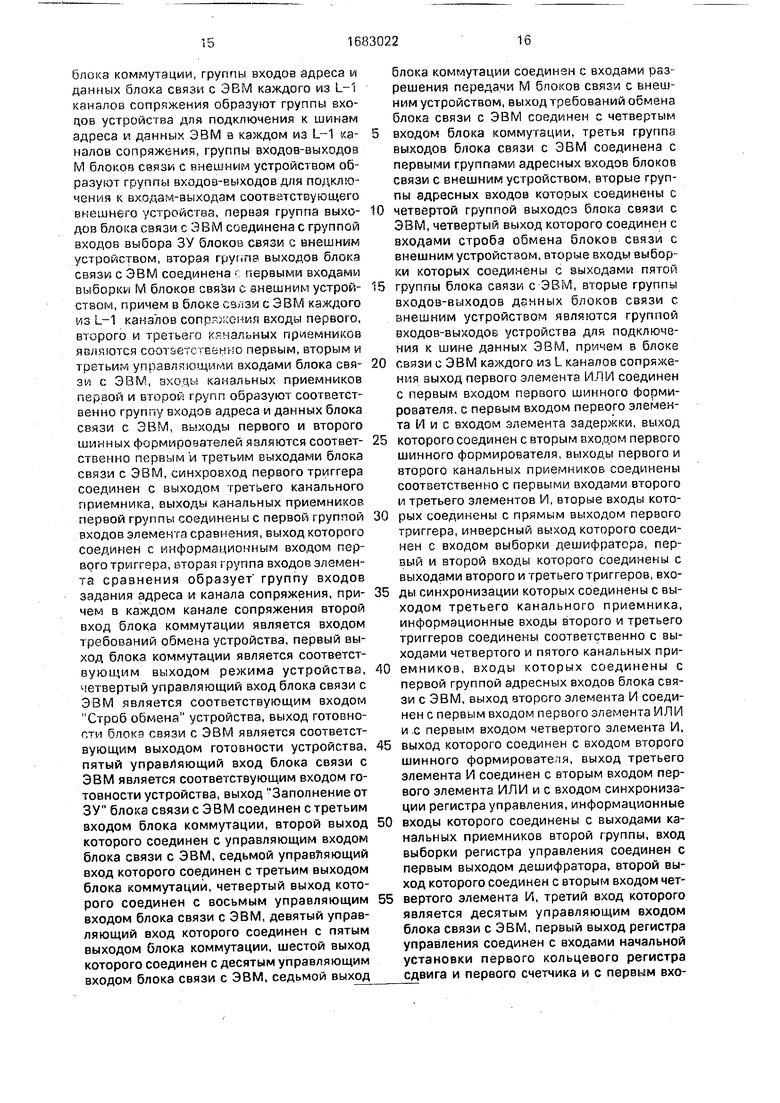

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - структурная схема блока связи с ЭВМ; на фиг, 3 - структурная схема блока коммутации; на фиг. 4 - структурная схема блока связи с внешним устройством (ВУ); на фиг. 5-7 - временные диаграммы работы устройства, на фиг. 8- пример соединения узлов сопряжения устройства с внешними устройствами, на фиг, 9 - таблица сигналов блока связи с ВУ. На фиг. 1 обозначены каналы - U сопряжения, блок 2 коммутации, блок 3 связи с ЭВМ, блок 4 связи с ВУ, магистраль 5 обмена ЭВМ, линия 6 сигнала Ввод, линия 7 сигнала Вывод, линия 8 сигнала СНА, линия 9 сигнала СИП, группа линий 10 сигналов Адрес, группа линий 11 сигналов Данные 1, линия 12 сигнала Готовность, группа линий 13 сигналов Данные 2, линия

14сигнала Требование обмена ВУ, линия

15сигнала Режим работы ВУ, линия 16 сигнала Строб обмена ВУ, линия 17 сигнала Конец обмена ВУ, группа линий 18 сигналов Данные ВУ, линия 19 сигнала Разрешениеобмена ЭВМ, линия 20сигнала Перенос 1, линия 21 сигнала Перенос 2, линия 22 сигнала Разрешение обмена ВУ, линия 23 сигнала Разрешение передачи ВУ/ЗУ, группа линий 24 сигналов Выбор ЗУ, группа линий 25 сигналов Адрес от ЭВМ, группа линий 26 сигналов Адрес от ВУ, группа линий 27 сигналов Выбор блока связи с ВУ, линия 28 сигнала Строб обмена ЭВМ, линия 29 сигнала Выборка, линия 30 сигнала Требование обмена ЭВМ, линия 31 сигнала Заполнение от ЭВМ, линия 32 сигнала Заполнение от ВУ, линия 33 сигнала Режим работы ЭВМ, линия 34 сигнала Разрешение передачи ЭВМ/ЗУ. На фиг, 2 обозначены второй и третий канальные приемники 35 и 36, первая группа 37 канальных приемников, четвертый и пятый канальные приемники 38 и 39, вторая группа 40 канальных приемников, второй шинный формирователь 41, второй и третий элементы И 42 и 43, первый элемент 44 сравнения, второй и третий триггеры 45 и 46,регистр 47 управления,четвертый элемент И 48, элемент 49 задержки, первый элемент ИЛИ 50, первый триггер51, дешифратор 52, генератор 53 импульсов, второй счетчик 54, первый счетчик 55, первый канальный приемник 56, пятый элемент И 57, седьмой элемент И 58, первый элемент И 59, элементы ИЛИ 60 и 61, первый шинный формирователь 62, шестой элемент И 63, пятый элемент ИЛИ 64, второй элемент 65 сравнения, третий счетчик 66, элемент И-НЕ 67, первый, третий и второй кольцевые регистры 68 - 70, четвертый элемент ИЛИ 71, группа элементов И 72. группа адресных входов 73. На фиг. 3 обозначены четвертый триггер 74, первый элемент НЕ 75, четвертый и второй элементы ИЛИ 76 и 77, второй и третий элементы НЕ 78 и 79, первый и второй триггеры 80 и 81, четвертый, первый, второй и третий элементы И 82 - 85, первый элемент ИЛИ 86, второй и первый счетчики 87 и 88, пятый, третий, шестой и седьмой элементы ИЛИ 88 - 92, четвертый и пятый элементы НЕ 93 и 94, восьмой и девятый элементы ИЛИ 95 и 96 и третий триггер 97. На фиг. 4 обозначены коммутатор 98 адреса, группа элементов И

99,первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ

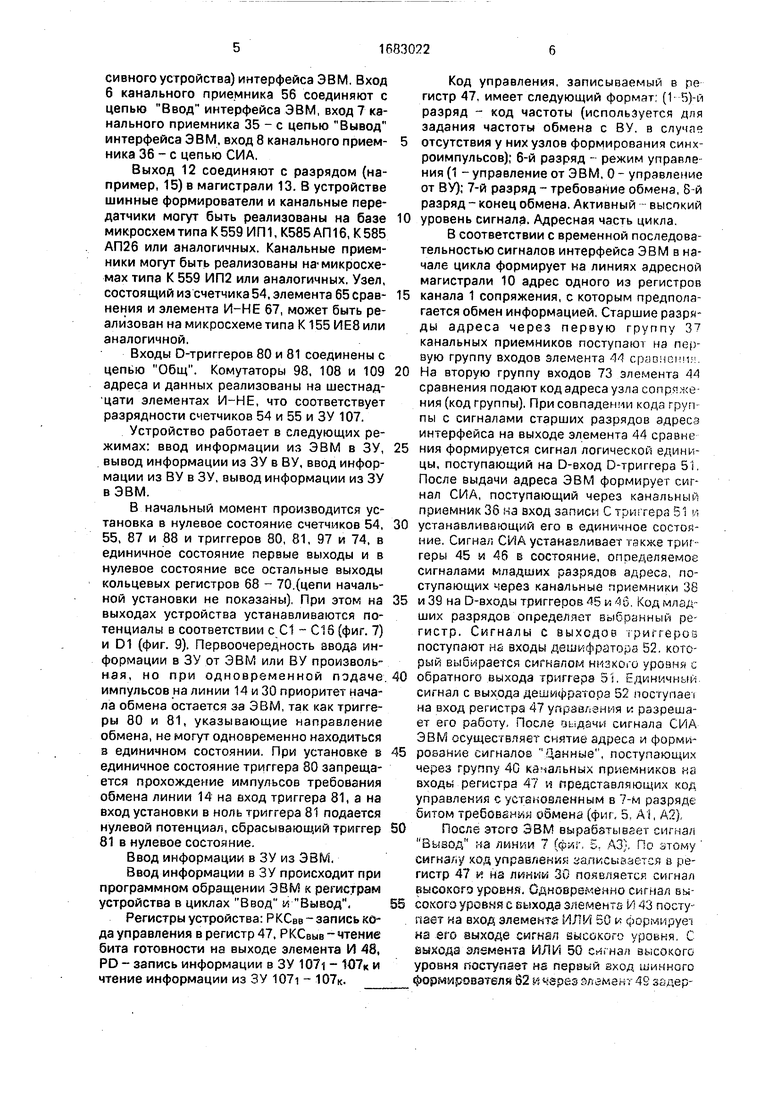

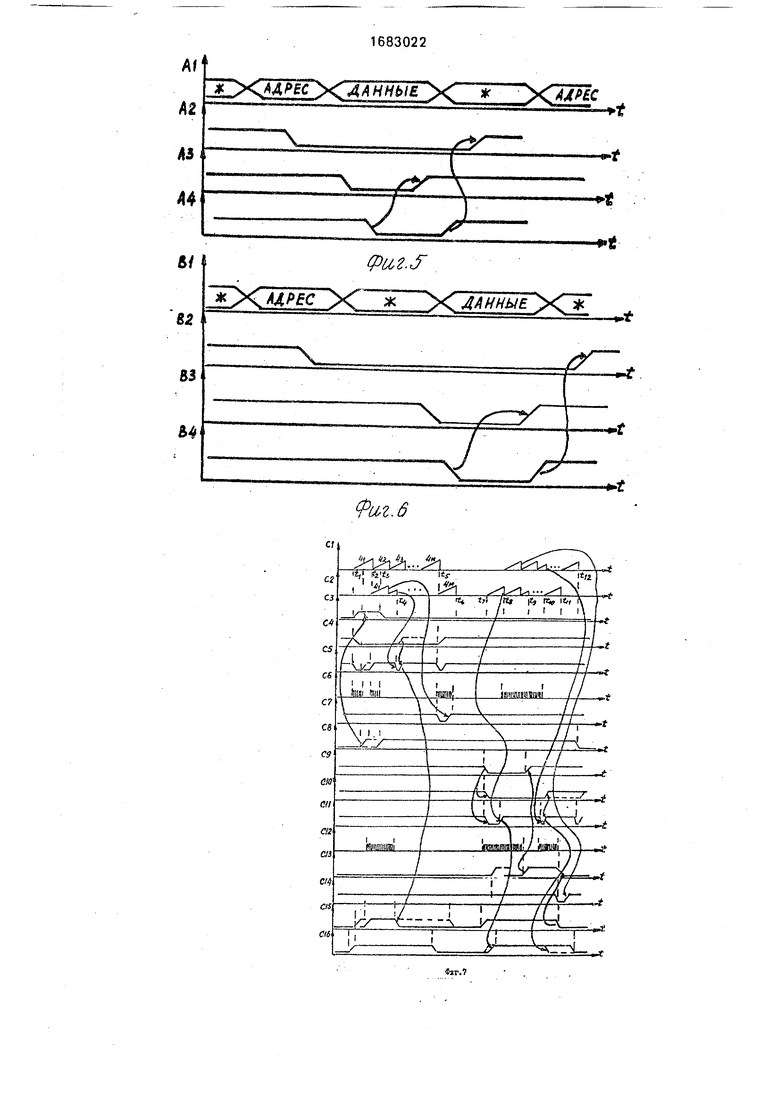

100,первый и второй элементы НЕ 101 и 102, первый и второй элементы И 103 и 104, группа элементов ИЛИ 105, элемент ИЛИ- НЕ 106, запоминающее устройство 107, вторая и первая группы 108 и 109 коммутаторов данных, второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 110. На фиг. 5 обозначены: А1 - временная диаграмма сигналов в цикле Вывод на линиях 10, 11 и 13 (10 - Адрес, 11 и 13 - Данные); А2 - временная диаграмма сигнала на линии 8 (СИА); A3 - на линии 7 (Вывод); А4 - на линии 9 (СИП).

На фиг. б обозначены: В1 - временная диаграмма сигналов в цикле Ввод на линиях 10, 11, 13 и 12 (10- Адрес, 11 и 13- Данные, 12 - Бит данные, например 15-й разряд); В2 - временная диаграмма сигнала на линии 8 (СИА); ВЗ - на линии 6 (Ввод); В4-на-линии 9 (СИП),

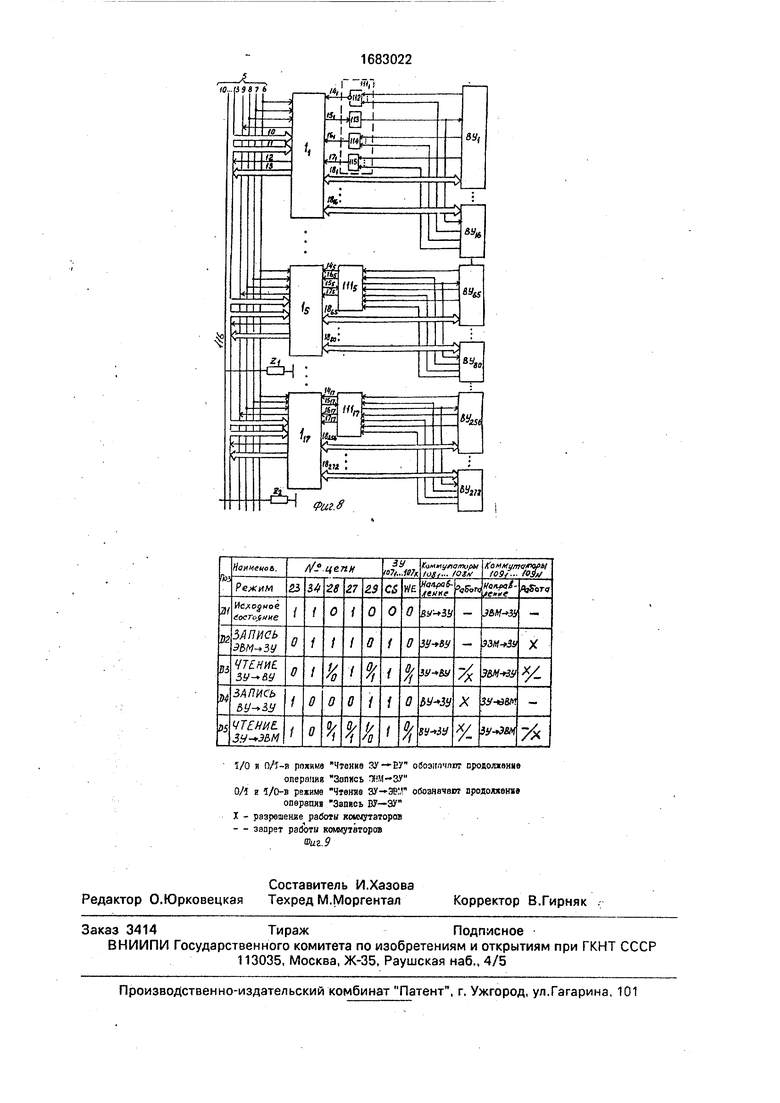

На фиг. 7 обозначены: С1 - временная диаграмма подсчета числа заполненных ЗУ блоков счетчиком 87; С2 - временная диаграмма подсчета числа заполненных ЗУ блоков 4 счетчиком 88; СЗ - временная диаграмма сигнала на линии 30; С4 - на линии 23; С5 - на линии 22; С6 - на линии 7; С7 - на линии 20; С8 - на линии 8 разряда регистра 47 (Конец обмена); С9 - на линии 14; СЮ - на линии 34; С11 - на линии 19;

С12-на линии 16; С13-на линии 17; С14- на линии 21; С15 - на линии 15; С16 - на линии 33;

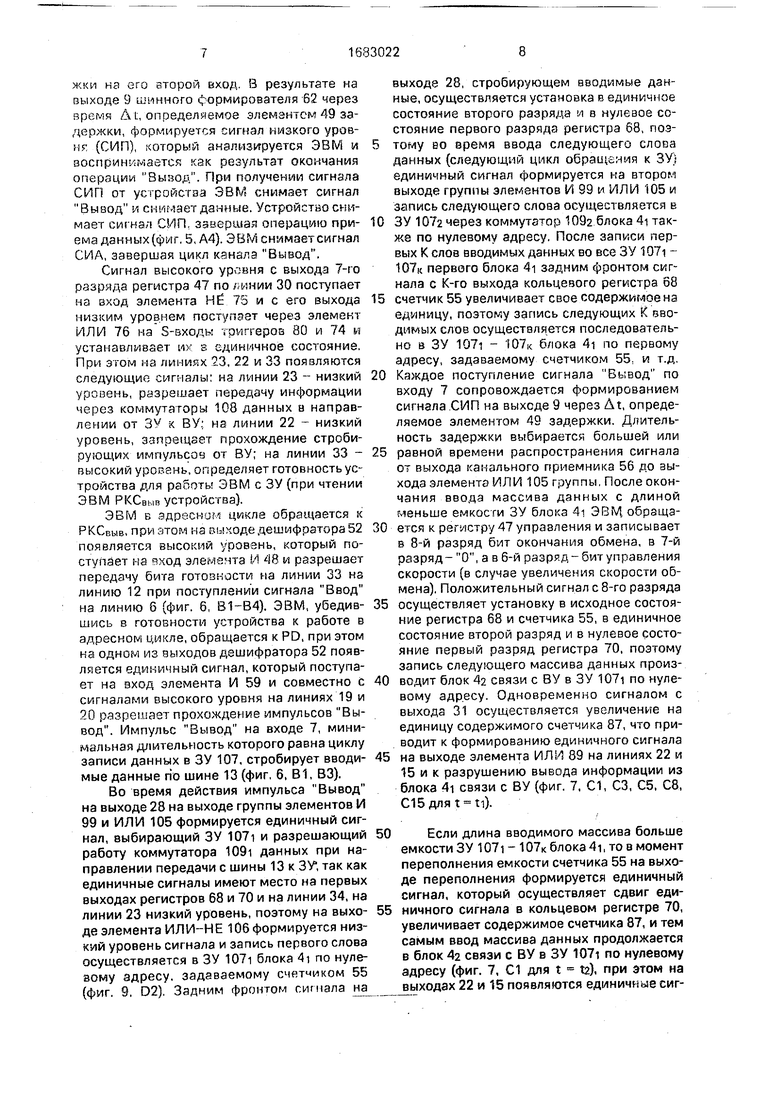

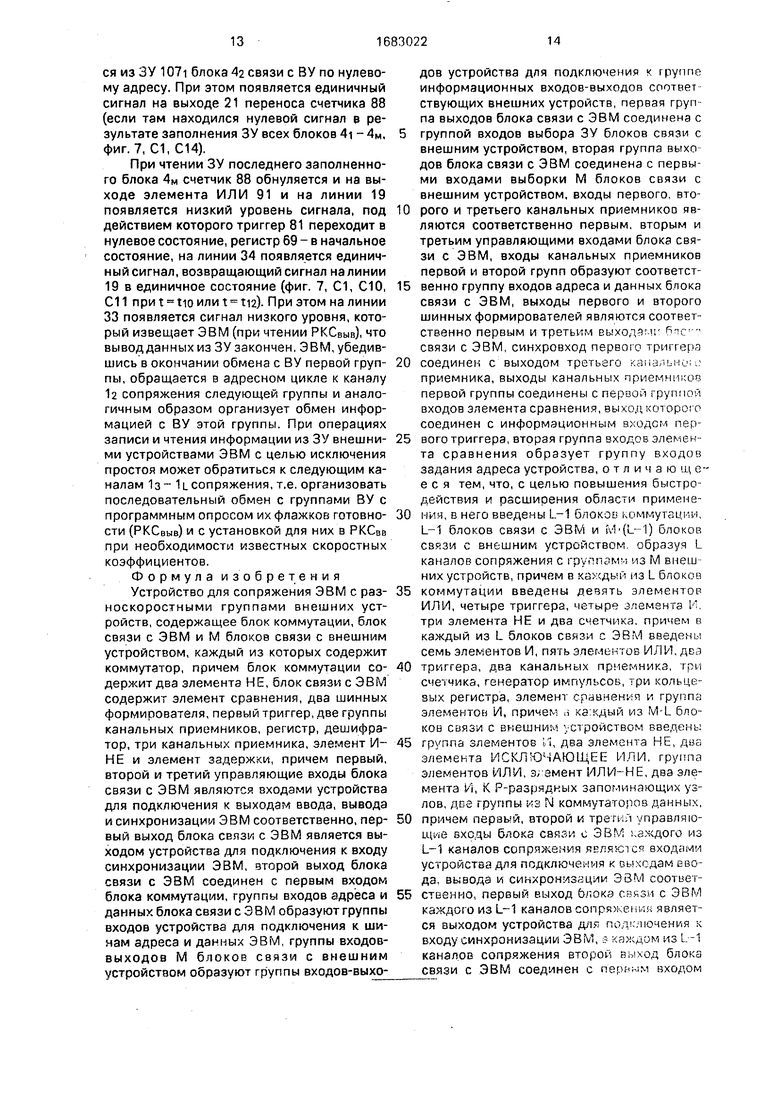

На фиг. 8 обозначены группа 111 логических элементов, элемент И-НЕ 112 , канальный передатчик 113, элементы И 114 и 115, шина Адрес/данные 116, Zi - набор согласующих резисторов (ZH 250 Ом), 2z - то же (ZH 120 Ом).

Работу устройства рассмотрим на примере использования его для сопряжения ЭВМ типа Электроника-бО с L группами из М внешних устройств.

Разрядность информационного слова

ЭВМ (шина 13) 16 бит. Максимальное количество групп (L) 17 (определяется нагрузочной способностью ЭВМ). Количество внешних устройств в группе (М) 16 (определяется разрядностью используемых кольцевых регистров сдвига и счетчиков).

Объем ЗУ 1024 слов х16 (4 микросхемы типа 541 РУ2). Количество ЗУ в блоке связи с ВУ (К) 16. Разрядность информационного слова ВУ (шина 18) 256 бит.

Управляющий сигнал по линии 14 от ВУ

формируется в результате сложения сигналов готовности от ВУ по И, т.е. обмен ведег- ся только когда все ВУ готовы к работе. Сигнал на линиях 16 и 17 формируется в

результате объединения сигналов стробов обмена от каждого ВУ по И (т.е. управляющими являются стробы от самого скоростного ВУ). Линия 15 сигнала соединяется со всеми ВУ.

На входы канальных приемников37-39

поступают соответственно тринадцать и два бита адреса, на входы канальных приемников 40-16 битов данных.

Выход 9 шинного формирователя 62 соединяют с цепью СИП (сигнал ответа пассивного устройства) интерфейса ЭВМ. Вход 6 канального приемника 56 соединяют с цепью Ввод интерфейса ЭВМ, вход 7 канального приемника 35 - с цепью Вывод интерфейса ЭВМ, вход 8 канального приемника 36 - с цепью СИЛ.

Выход 12 соединяют с разрядом (например, 15)в магистрали 13. В устройстве шинные формирователи и канальные передатчики могут быть реализованы на базе микросхем типа К 559 ИП1, К585 АП16, К 585 АП26 или аналогичных. Канальные приемники могут быть реализованы на-микросхемах типа К 559 ИП2 или аналогичных. Узел, состоящий из счетчика 54, элемента 65 сравнения и элемента И-НЕ 67, может быть реализован на микросхеме типа К 155 ИЕЗили аналогичной.

Входы D-триггеров 80 и 81 соединены с цепью Общ. Комутаторы 98, 108 и 109 адреса и данных реализованы на шестнад- цати элементах И-НЕ, что соответствует разрядности счетчиков 54 и 55 и ЗУ 107.

Устройство работает в следующих режимах: ввод информации из ЭВМ в ЗУ, вывод информации из ЗУ в ВУ, ввод информации из ВУ в ЗУ, вывод информации из ЗУ в ЭВМ.

В начальный момент производится установка в нулевое состояние счетчиков 54, 55, 87 и 88 и триггеров 80, 81, 97 и 74, в единичное состояние первые выходы и в нулевое состояние все остальные выходы кольцевых регистров 68 - 70.(цепи начальной установки не показаны). При этом на выходах устройства устанавливаются потенциалы в соответствии с С1 - С16 (фиг. 7) и D1 (фиг. 9). Первоочередность ввода информации в ЗУ от ЭВМ или ВУ произвольная, но при одновременной подаче импульсов на линии 14 и 30 приоритет начала обмена остается за ЭВМ, так как триггеры 80 и 81, указывающие направление обмена, не могут одновременно находиться з единичном состоянии. При установке в единичное состояние триггера 80 запрещается прохождение импульсов требования обмена линии 14 на вход триггера 81, а на вход установки в ноль триггера 81 подается нулевой потенциал, сбрасывающий триггер 81 в нулевое состояние.

Ввод информации в ЗУ из ЭВМ.

Ввод информации в ЗУ происходит при программном обращении ЭВМ к регистрам устройства в циклах Ввод и Вывод,

Регистры устройства: РКСвв запись кода управления в регистр 47. РКСвыв-чтение бита готовности на выходе элемента И 48, PD - запись информации в ЗУ 107i - 107 и чтение информации из ЗУ 107i - 107К.

Код управления, записываемый в ре гистр 47. имеет следующий формат. (1 5)-й разряд - код частоты (используется для задания частоты обмена с ВУ. в случае

отсутствия у них узлов формирования синхроимпульсов); 6-й разряд - режим управления (1 - управление от ЭВМ, 0 - управление от ВУ); 7-й разряд - требование обмена, 8-й разряд-конец обмена. Активный высокий

0 уровень сигнала. Адресная часть цикла.

В соответствии с временной последовательностью сигналов интерфейса ЭВМ в начале цикла формирует на линиях адресной магистрали 10 адрес одного из регистров

5 канала 1 сопряжения, с которым предполагается обмен информацией. Старшие разряды адреса через первую группу З7 канальных приемников поступают на первую группу входов элемента 44 сраонсичг

0 На вторую группу входов 73 элемента 44 сравнения подают код адреса узла ния (код группы). При совпадении кода труп пы с сигналами старших разрядов адреса интерфейса на выходе элемента 44 сравне

5 ния формируется сигнал логической единицы, поступающий на D-вход D-триггера 51. После выдачи адреса ЭВМ формирует сигнал СИА, поступающий через канальный приемник 36 на вход записи С трш гера 51

0 устанавливающий его в единичное состояние. Сигнал СИА устанавливает также триггеры 45 и 46 в состояние, определяемое сигналами младших разрядов адреса, поступающих через канальные приемники 38

5 и 39 на D-входы триггеров 45 м 46. Код младших разрядов определяет выбранный регистр. Сигналы с выходов ipnrrepos поступают на входы дешифратора 52. который выбирается сигналом низкого уровня с

0 обратного выхода триггера 51. Единичный сигнал с выхода дешифратора 52 поступав на вход регистра 47 управления и разрешает его работу, После задачи сигнала СИА ЭВМ осуществляет снятие адреса и форми5 рование сигналов Данные, поступающих через группу 40 кабальных приемников на входы регистра 47 и представляющих код управлений с установленным в 7-м разряде битом требований обмена (фиг, 5. Ai, А2),

0 После этого ЭВМ вырабатывает сигнал Вывод на линии 7 фиг. о. A3}, По отому сигналу ход управлений запксыазет-я в регистр 47 и на линии 30 появляется сигнал высокого уровня. Одновременно сигнал вы5 сокого уровня с выхода элемента И 43 поступает на вход элемент© ИЛИ 50 и формирует на его выходе сигнал высокого уровня. С выхода элемента ИЛИ 50 ей, нал высокого уровня поступает из первый зход шинного формирователя 62 и ерез зпгмеп-, 49 зйдержки на его второй вход. В результате на выходе 9 шинного формирователя 62 через время Доопределяемое элементом 49 задержки, формируется сигнал низкого уров- яг (СИП), который анализируется ЭВМ и воспринимается как результат окончания операции Вывод. При получении сигнала СИП от устройства ЭВМ снимает сигнал Вывод -л снимает данные. Устройство снимает сигнал СИП, завершая операцию приема данных (фиг, 5, А4). ЭВМ снимает сигнал СИЛ, завершая цикл канала Вывод,

Сигнал высокого уровня с выхода 7-го разряда регистра 47 по мжии 30 поступает на вход элемента НЕ 75 и с его выхода низким уровнем поступает через элемент ИЛИ 76 на S-входк риггеров 80 и 74 и устанавливает MV в единичное состояние. При згом на линиях 23, 22 и 33 появляются следующие сигналы: на линии 23 - низкий уровень, разрешает передачу информации через коммутаторы 108 данных в направлении от 3V к ВУ; на линии 22 - низкий уровень, запрещает прохождение строби- рующих импульсов от ВУ; на линии 33 - высокий уровень, определяет готовность устройства для работы ЭВМ с ЗУ (при чтении ЭВМ РКСвыв устройства).

ЭВМ в эдрненш1 цикле обращается к РКСвыв, при этом на выходе дешифратора 52 появляется высокий уровень, который поступает на ячод элемента И 48 и разрешает передачу бита готовности на линии 33 на линию 12 при поступлении сигнала Ввод на линию б (фиг. 6, В1-В4). ЭВМ, убедившись в готовности устройства к работе в адресном цикле, обращается к PD, при этом на одном из выходов дешифратора 52 появляется единичный сигнал, который поступает на вход элемента И 59 и совместно с сигналами высокого уровня на линиях 19 и 20 разрешает прохождение импульсов Вывод. Импульс Вывод на входе 7, минимальная длительность которого равна циклу записи данных в ЗУ 107, стробирует вводимые данные по шине 13 (фиг, 6, В1, ВЗ).

Во время действия импульса Вывод на выходе 28 на выходе группы элементов И 99 и ИЛИ 105 формируется единичный сигнал, выбирающий ЗУ 107i и разрешающий работу коммутатора 109i данных при направлении передачи с шины 13 к ЗУ, так как единичные сигналы имеют место на первых выходах регистров 68 и 70 и на линии 34, на линии 23 низкий уровень, поэтому на выходе элемента ИЛИ-НЕ 106 формируется низкий уровень сигнала и запись первого слова осуществляется в ЗУ 107i блока 4i по нулевому адресу, задаваемому счетчиком 55 (фиг. 9. D2). Задним фронтом сигнала на

выходе 28, стробирующем вводимые данные, осуществляется установка в единичное состояние второго разряда и в нулевое состояние первого разряда регистра 68, поэтому во время ввода следующего слова данных (следующий цикл обращения к ЗУ) единичный сигнал формируется на втором выходе группы элементов И 99 и ИЛИ 105 и запись следующего слова осуществляется в

ЗУ 1072 через коммутатор 1092 блока 4i также по нулевому адресу. После записи первых К слов вводимых данных во все ЗУ 107i - 107К первого блока 4i задним фронтом сигнала с К-го выхода кольцевого регистра 68

счетчик 55 увеличивает свое содержимое на единицу, поэтому запись следующих К вводимых слов осуществляется последовательно в ЗУ 107i - 107к блока 4i по первому адресу, задаваемому счетчиком 55. и т.д.

Каждое поступление сигнала Вывод по входу 7 сопровождается формированием сигнала СИП на выходе 9 через At, определяемое элементом 49 задержки. Длительность задержки выбирается большей или

равной времени распространения сигнала от выхода канального приемника 56 до выхода элементе ИЛИ 105 группы, После окончания ввода массива данных с длиной меньше емкости ЗУ блока 4i ЭВМ, обращается к регистру 47 управления и записывает в 8-й разряд бит окончания обмена, в 7-й разряд- О, а в 6-й разряд- бит управления скорости (в случае увеличения скорости обмена), Положительный сигнал с 8-го разряда

осуществляет установку в исходное состояние регистра 68 и счетчика 55, в единичное состояние второй разряд и в нулевое состояние первый разряд регистра 70, поэтому запись следующего массива данных производит блок 42 связи с ВУ в ЗУ 107i по нулевому адресу. Одновременно сигналом с выхода 31 осуществляется увеличение на единицу содержимого счетчика 87, что приводит к формированию единичного сигнала

на выходе элемента ИЛИ 89 на линиях 22 и 15 и к разрушению вывода информации из блока 41 связи с ВУ (фиг. 7, С1, СЗ, С5, С8, С15 для t ti).

Если длина вводимого массива больше емкости ЗУ 1071 - 107К блока 4i, то в момент переполнения емкости счетчика 55 на выходе переполнения формируется единичный сигнал, который осуществляет сдвиг единичного сигнала в кольцевом регистре 70, увеличивает содержимое счетчика 87, и тем самым ввод массива данных продолжается в блок 42 связи с ВУ в ЗУ 107i по нулевому адресу (фиг. 7, С1 для t 12), при этом на выходах 22 и 15 появляются единичные сигналы, разрешающие ВУ обмен информацией с устройством (фиг. 7, С5, С15).

Для исключения двойного срабатывания кольцевого регистра 70 и счетчика 87 при вводе массивов длиной, равной емкости ЗУ одного блока 4 связи с ВУ, введена блокировка второго входа элемента И 57 нулевым сигналом с выхода элемента ИЛИ 60. Если все ЗУ 107i - 107 блоков 4i - 4М связи с ВУ заполнены информацией, то на выходе 20 переполнения счетчика 87 формируется нулевой сигнал, который закрывает элемент И 59 и запрещает дальнейший ввод информации до тех пор, пока не освободится ЗУ 107 блока 4i - 4М связи с ВУ (фиг. 7, С1, С7 при t ts).

При поступлении единичного сигнала с выхода 6 разряда регистра 47 на вход элемента И-НЕ 67 на выходе этого элемента появляются импульсы с частотой, задаваемой ЭВМ, которые используются в случае отсутствия синхроимпульсов от ВУ или при работе ВУ на частотах, больших частоты цикла обмена управляющей ЭВМ.

Вывод информации из ЗУ в ВУ.

Вывод информации из ЗУ 107 устройства на линии 18i - 18М ВУ возможен только после заполнения массивом данных ЗУ 107t - 107К хотя бы одного блока 4 связи с ВУ. При этом на выходе переполнения счетчика 55 формируется единичный сигнал, который осуществляет сдвиг единичного сигнала в кольцевом регистре 70, увеличивает содержимое счетчика 87, и на выходе элемента ИЛИ 89 и на линиях 22 и 15 появляются единичные сигналы, разрешающие обмен между ВУ и ЗУ (фиг. 7, С1, С15 при t t2).

Вывод информации из ЗУ 107 осуществляется Р-разрядными словами, причем Р R К, где R - разрядность вводимого в ЗУ слова; К- количество ЗУ 107,

ВУ, получив по линии 15 единичный сигнал разрешения работы, формирует на линии 16 сигналы, стробирующие вводимые данные с минимальной длительностью, равной циклу чтения из ЗУ 107. Во время действия единичного сигнала на одном из входов элемента И 63 на выходе элемента И 63 также появляется единичный сигнал, так как на входах 21 и 22 имеются сигналы высокого уровня. Во время действия единичного сигнала на выходе элемента И 63 на первом выходе группы элементов И 72 появляется единичный сигнал, так как на первом выходе кольцевого регистра находился единичный сигнал после начальной установки.

Единичный сигнал на выходе 29i приводит к формированию единичных сигналов

на всех выходах группы элементов ИЛИ 105 блока 4i связи с ВУ, на выходах еь борки кристалла коммутаторов 108i - 108м данных и на входах задания режима всех ЗУ 107i 107к(на выходе элемента ИЛИ-НЕ 106), по этому данные, выводимые из ЗУ 107i - 107К по нулевому адресу, задаваемому счетчиком 66, через коммутаторы 108i - 108ы поступают на шину 18. Задним фронтом единичного

0 сигнала с выхода элемента И 63 счетчик 66 адреса вывода увеличивает свое содержимое на единицу, поэтому во время действия следующего единичного сигнала на входе 16 устройства вывод данных производится од5 новременно из ЗУ 107i - 107 блока 4i по следующему адресу, задаваемому счетчиком 66 (фиг. 7, С2, С12 t t2 и фиг, 9, D3).

При выводе массива информации длиной, большей емкости ЗУ блока 4i, на выхо

0 де переполнения счетчика 66 и на линии 292 формируется сигнал высокого уровня, разрешающий вывод информации из ЗУ блока 42 (при сдвиге кольцевого регистра 69). Для исключения ложного срабатывания

5 введена блокировка входа элемента И 58 нулевым сигналом с выхода элемента ИЛИ 71. Если после чтения массива информации Отсутствуют в блоках 4 заполненные ЗУ 107, т.е. счетчик 87 устанавливается в нулевое

0 состояние и на выходе элемента ИЛИ 89 появляется кулевой сигнал, под действием которого триггер 80 переходит в нулевое состояние (фиг. 7, С2, С4, С15 для t - 14). на выходе 15 появляется сигнал низкого уров5 ня и дальнейший вывод информации из ЗУ будет остановлен. При этом передний фронт сигнала низкого уровни на линии 22 устанавливает регистр 70 в начальное состояние, т.е. подготавливает его к выводу

0 информации из ЗУ.

Ввод информации Р ЗУ из ВУ. Ввод информации из ЗУ в ЗУ происходит после вывода ю ЗУ ранее записанной информации, т.е. при обнулении счетчикэ 87

5 и при наличии на линии 15 отрицательного потенциала. ВУ выставляет на линии 14 отрицательный уро&ень сигнала. При этом триггер 81 переходит в единичное состояние и на линиях 34 и 19 появляется нулевой

0 сигнал (фиг. 7, С9, СЮ. С11 для t -1, фиг. 9, D4), Эти сигналы устанавливают режим записи s ЗУ блока 4 и запрещают прохождение импульсов на выход 28. Триггер 97 устанавливается в единичное состояние, и

5 на выходе 15 появляется единичный сигнал, определяющий работу ВУ.

ВУ, проанализировав сигнап на линии 15, выставляет на шину 18 информацию и на линию 16 стробирующие импульсы (так4 как стробирующие импульсы складываются по

И, то результирующая частота определяется скоростью наиболее быстродействующего ВУ, при отсутствии импульсов синхронизации от ВУ на линию 16 помещается положительный потенциал и стробирование производится импульсами от управляемого делителя частоты).

Во время действия единичного сигнала на входе элемента И 63 на его выходе появляется также единичный сигнал, который приводит к формированию единичного сигнала на выходе 29ч. Единичный сигнал выходе 29i приводит к формированию единичных сигналов на вс , выходах группы элементов ИЛИ 105 связи с ВУ и на входах выборки кгштгаллз коммутаторов 108i - 108ы данных, На выходе элемента ИЛИ-НЕ 106 почвяяется сигнал низкого уровня, коюрьж определяет режим записи з ЗУ (фиг. 9. D4), поэтому данные, находящиеся на шине J8 оступают через коммутаторы 108 нз входы ЗУ .л записываются по нулевому адресу, задаваемому счетчиком 66. Задним фропгогл единичного сигнала с выхода элемента И 63 счетчик 66 увеличивает свое содержимое на единицу, поэтому во время действия следующего единичного сигнала на входе 16 уст ройства звод данных производится одновременно во see ЗУ 1071 - 107к блока 4i по следующему адресу, задаваемому счетчиком 66 (фиг. 7, С2, С12 при t - п, ts). В момент окончания зводз массива информации единичный сигнал поступает на вход 17 устройства (фиг. 7, С13 для t tg), при этом в кольцевом регистре 69 происходит сдвиг информации, а на цепи 32 появляется импульс, под действием которого счетчик 88 увеличивает свое содержимое на единицу.

При вводе массива данных длиной больше емкости ЗУ 107i - 107К блока 4i на выходе переполнения счетчика.66 появляется единичный сигнал, под действием которого в регистре 69 происходит сдвиг информации, и на выходах 29г, 19 и 33 появляется сигнал высокого уровня, разрешающий ввод информации в ЗУ блока 42 и чтение ее (фиг. 7, С11,С16)изЭВМ.

При заполнении всех ЗУ 107i - 107к блоков 4i - 4М информацией на выходе переполнения счетчика 88 и на линии 21 появляется сигнал низкого уровня (фиг. 7, С2, С14 для t no), под действием которого на линии 15 появляется сигнал низкого уровня, запрещающий работу ВУ.

Вывод информации из ЗУ в ЭВМ.

Вывод информации из ЗУ 107 устройства на шину 13 ЭВМ возможен только после заполнения массивом данных ЗУ 107i-107K хотя бы одного блока 4 связи с ВУ. При этом

на выходе переполнение счетчика 66 формируется единичный сигнал, который осуществляет сдвиг единичного сигнала в кольцевом регистре 69, увеличивает по цепи

32 содержимое (ноль) счетчика 88, и на выходе элемента ИЛИ 91 и на линиях 19 и 33 появляются единичные сигналы, разрешающие обмен между ВУ и ЭВМ (фмг. 7, С2, С11. С16 для| 1з).

0 Единичный сигнал по линии 33 поступает на вход элемента И 48, сообщая о готов- косги устройства для обмена с ЭВМ,

ЭВМ в адресном цикле обращается к РКС вывода и в цикле Ввод читает биг

5 готовности в 15-м разряде данных. Затем ЭВМ в адресном цикле обращается к PD и в цикле Ввод читает данные на шине 13. При этом строб чтения (сигнал Ввод) поступает по линии 7 через элементы И 43 и ИЛИ 50

0 на вход элемента И 59.

Во время действия импульса Ввод на выходе 8 на выходе группы элементов И 99 и ИЛИ 105 формируется единичный сигнал, выбирающий ЗУ 107i и разрешающий рабо5 ту коммутатора 109i данных при направлении передачи от ЗУ к -пине 13, так как единичные сигналы имеют место на первых выходах регистров 68 и 70 и на линии 23, а на линии 34 низкий уровень сигнала, поэто0 мунэ выходе элемента ИЛ И-НЕ 106 формируется высокий уровень сигнала и чтение первого слова осуществляется из ЗУ 107т блока 4i связи с ВУ по нулевому адресу, задаваемому счетчиком 55 (фиг. 7, С1, фиг.

5 9, D5). Задним фронтом сигнала Ввод на линии 28 осуществляется установка в единичное состояние второго разряда и в нулевое состояние первого разряда регистра 68, поэтому при следующем обращении к PD

0 единичный сигнал формируется на втором выходе группы элементов И 99 и ИЛИ 105 и чтение следующего слова осуществляется из ЗУ 1072 через коммутатор 1092 блока 4i также по нулевому адресу.

5 После чтения первых К слов из всех ЗУ 107i - 107К блока 4i задним фронтом сигнала с К-го выхода кольцевого регистра 68 счетчик 55 увеличивает свое содержимое на единицу, поэтому чтение следующих К слов

0 осуществляется последовательно из ЗУ 107i - 107к блока 4 по первому адресу, задаваемому счетчиком 55, и т.д.

Если длина читаемого массива больше емкости ЗУ 107i - 107К блока 4i, то в момент

5 переполнения счетчика 55 на его выходе переполнения формируется единичный сигнал, который осуществляет сдвиг единичного сигнала в кольцевом регистре 70, уменьшает содержимое счетчика 88 и тем самым чтение массива данных продолжается из ЗУ 107i блока 42 связи с ВУ по нулевому адресу. При этом появляется единичный сигнал на выходе 21 переноса счетчика 88 (если там находился нулевой сигнал в результате заполнения ЗУ всех блоков 4i - 4М, фиг. 7,С1,С14).

При чтении ЗУ последнего заполненного блока 4М счетчик 88 обнуляется и на выходе элемента ИЛИ 91 и на линии 19 появляется низкий уровень сигнала, под действием которого триггер 81 переходит в нулевое состояние, регистр 69 - в начальное состояние, на линии 34 появляется единичный сигнал, возвращающий сигнал налинии 19 в единичное состояние (фиг. 7, С1, СЮ, С11 при t tio или t tia). При этом на линии 33 появляется сигнал низкого уровня, который извещает ЭВМ (при чтении РКСвыа), что вывод данных из ЗУ закончен. ЭВМ, убедившись в окончании обмена с ВУ первой группы, обращается в адресном цикле к каналу 12 сопряжения следующей группы и аналогичным образом организует обмен информацией с ВУ этой группы. При операциях записи и чтения информации из ЗУ внешними устройствами ЭВМ с целью исключения простоя может обратиться к следующим каналам 1з 1| сопряжения, т.е. организовать последовательный обмен с группами ВУ с программным опросом их флажков готовности (РКСвыв) и с установкой для них в РКСва при необходимости известных скоростных коэффициентов.

Формула изобретения Устройство для сопряжения ЭВМ с раз- носкоростными группами внешних устройств, содержащее блок коммутации, блок связи с ЭВМ и М блоков связи с внешним устройством, каждый из которых содержит коммутатор, причем блок коммутации содержит два элемента НЕ, блок связи с ЭВМ содержит элемент сравнения, два шинных формирователя, первый триггер, две группы канальных приемников, регистр, дешифратор, три канальных приемника, элемент И- НЕ и элемент задержки, причем первый, второй и третий управляющие входы блока связи с ЭВМ являются входами устройства для подключения к выходам ввода, вывода и синхронизации ЭВМ соответственно, первый выход блока связи с ЭВМ является выходом устройства для подключения к входу синхронизации ЭВМ, второй выход блока связи с ЭВМ соединен с первым входом блока коммутации, группы входов адреса и данных блока связи с ЭВМ образуют группы входов устройства для подключения к шинам адреса и данных ЭВМ, группы входов- выходов М блоков связи с внешним устройством образуют группы входов-выходов устройства для подключения к группе информационных входов-выходов соотеет ствующих внешних устройств, первая труп па выходов блока связи с ЭВМ соединена с

группой входов выбора ЗУ блоков связи с внешним устройством, вторая группа выхо дов блока связи с ЭВМ соединена с первыми входами выборки М блоков связи с внешним устройством, входы первого, вто0 рого и третьего канальных приемников являются соответственно первым, вторым и третьим управляющими входами блока связи с ЭВМ, входы канальных приемников первой и второй групп образуют соответст5 венно группу входов адреса и данных блока связи с ЭВМ, выходы первого и второго шинных формирователей являются соответственно первым и третьим выходзмг РИс1 связи с ЭВМ, синхровход первого триггера

0 соединен с выходом третьего j приемника, выходы канальных приемников первой группы соединены с первой группой входов элемента сравнения, выход которого соединен с информационным входом пер5 вого триггера, вторая группа входов элемента сравнения образует группу входов задания адреса устройства, отличают, е- е с я тем, что, с целью повышения быстродействия и расширения области примеие0 ния, в него введены L-1 блоков коммутации, L-1 блоков связи с ЭВМ и M (L-1) блоков связи с внешним устройством, образуя L каналов сопряжения с группзмм из М внешних устройств, причем в каждый из L блоков

5 коммутации введены девять элементов ИЛИ, четыре триггера, четыре элемента К, три элемента НЕ и два счетчика, причем в каждый из L блоков связи с ЭВМ введены семь элементов И, пять элементов ИЛИ. два

0 триггера, два канальных приемника, три счетчика, генератор импульсов, три кольцевых регистра, элемент сравнения и группа элементов И, причем -л каждый из M-L блоков связи с внешним -устройством введены

5 группа элементов 11, два элемента НЕ, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, группа элементов ИЛИ, з; змент ИЛИ-НЕ, два элемента И, К Р-разрядных запоминающих узлов, две группы MS N коммутаторов данных,

0 причем первый, второй и третий управляющее входы блока связи о ЭВМ каждого из L-1 каналов сопряжения являются входами устройства для подключения к оыхсдам ввода, вывода и синхронизации ЭВМ соответ5 ственно, первый выход блока связи с ЭВМ каждого из L-1 каналов сопряжения является выходом устройства для подключения к входу синхронизации ЭВМ, . каждом из L-1 каналов сопряжения второй выход блока связи с ЭВМ соединен с первым входом

блока коммутации, группы входов адреса и данных блока связи с ЭВМ каждого из L-1 каналов сопряжения образуют группы входов устройства для подключения к шинам адреса и данных ЭВМ в каждом из L-1 каналов сопряжения, группы входов-выходов М блоков связи с внешним устройством образуют группы входов-выходов для подключения к входам-выходам соответствующего внешнего устройства, первая группа выходов блока связи с ЭВМ соединена с группой входов выбора ЗУ блоков связи с внешним устройством, вторая группа выходов блока связи с ЭВМ соединена первыми входами выборки М блоков связи с внешним устройством, причем в блоке сзлзи с ЭВМ каждого из L-1 каналов сопряжения входы первого, второго и третьего кянальных приемников являются соот&етсгвенно первым, вторым и третьим управляющими входами блока связи с ЭВМ, ахоць канальных приемников первой и второй групп образуют соответственно группу входов адреса и данных блока связи с ЭВМ, выходы первого и второго шинных формирователей являются соответственно первым и третьим выходами блока связи с ЭВМ, синхровход первого триггера соединен с выходом третьего канального приемника, выходы канальных приемников первой группы соединены с первой группой входов элемента сравнения, выход которого соединен с информационным входом первого триггера, вторая группа входов элемента сравнения образует группу входов задания адреса и канала сопряжения, причем в каждом канале сопряжения второй вход блока коммутации является входом требований обмена устройства, первый выход блока коммутации является соответствующим выходом режима устройства, четвертый управляющий вход блока связи с ЭВМ является соответствующим входом Строб обмена устройства, выход готовности блокэ связи с ЭВМ является соответствующим выходом готовности устройства, пятый управляющий вход блока связи с ЭВМ является соответствующим входом готовности устройства, выход Заполнение от ЗУ блока связи с ЭВМ соединен с третьим входом блока коммутации, второй выход которого соединен с управляющим входом блока связи с ЭВМ, седьмой управляющий вход которого соединен с третьим выходом блока коммутаций, четвертый выход которого соединен с восьмым управляющим входом блока связи с ЭВМ, девятый управляющий вход которого соединен с пятым выходом блока коммутации, шестой выход которого соединен с десятым управляющим входом блока связи с ЭВМ, седьмой выход

блока коммутации соединен с входами разрешения передачи М блоков связи с внешним устройством, выход требований обмена блока связи с ЭВМ соединен с четвертым

входом блока коммутации, третья группа выходов блока связи с ЭВМ соединена с первыми группами адресных входов блоков связи с внешним устройством, вторые группы адресных входов которых соединены с

0 четвертой группой выходов блока связи с ЭВМ, четвертый выход которого соединен с входами строба обмена блоков связи с внешним устройством, вторые входы выборки которых соединены с выходами пятой

5 группы блока связи с ЭВМ, вторые группы входов-выходов данных блоков связи с внешним устройством являются группой входов-выходов устройства для подключения к шине данных ЭВМ, причем в блоке

0 связи с ЭВМ каждого из L каналов сопряжения зыход первого элемента ИЛИ соединен с первым входом первого шинного Формирователя, с первым входом первого элемента И и с входом элемента задержки, выход

5 которого соединен с вторым входом первого шинного формирователя, выходы первого и второго канальных приемников соединены соответственно с первыми входами второго и третьего элементов И, вторые входы кото0 рых соединены с прямым выходом первого триггера, инверсный выход которого соединен с входом выборки дешифратора, первый и второй входы которого соединены с выходами второго и третьего триггеров, вхо5 ды синхронизации которых соединены с выходом третьего канального приемника, информационные входы второго и третьего триггеров соединены соответственно с выходами четвертого и пятого канальных при0 емников, входы которых соединены с первой группой адресных входов блока связи с ЭВМ, выход второго элемента И соединен с первым входом первого элемента ИЛ И и с первым входом четвертого элемента И,

5 выход которого соединен с входом второго шинного формироватетя, выход третьего элемента И соединен с вторым входом первого элемента ИЛИ и с входом синхронизации регистра управления, информационные

0 входы которого соединены с выходами канальных приемников второй группы, вход выборки регистра управления соединен с первым выходом дешифратора, второй выход которого соединен с вторым входом чет5 вертого элемента И, третий вход которого является десятым управляющим входом блока связи с ЭВМ, первый выход регистра управления соединен с входами начальной установки первого кольцевого регистра сдвига и первого счетчика и с первым входом пятого элемента И, второй вход которого соединен с выходом второго элемента ИЛИ, входы которого соединены с выходами первого счетчика и являются третьей группой выходов блока связи с ЭВМ, третий выход дешифратора соединен с вторым входом первого элемента И, третий и четвертый входы которого являются соответственно шестым и седьмым управляющими входами блока связи с ЭВМ, четвертый выход которого соединен с выходом первого элемента И и соединен с входом сдвига первого кольцевого регистра, выходы которого являются первой группой выходов блока связи с ЭВМ, выход старшего разряда первого кольцевого регистра соединен со счетным входом первого счетчика, выход переноса которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, выход третьего элемента ИЛИ является вторым выходом блока связи с ЭВМ и соединен с входом сдвига второго кольцевого регистра, вход начальной установки которого соединен с первым входом шестого элемента И, выходы второго кольцевого регистра являются второй группой выходов блока связи с ЭВМ, четвертый управляющий вход которого соединен с вторым входом шестого элемента И, третий вход которого соединен с выходом элемента И-НЕ, первый вход которого соединен с вторым выходом регистра управления, третий выход которого является пятым выходом блока связи с ЭВМ, группа выходов регистра управления соединена с первой группой входов второго элемента сравнения, вторая группа входов которого соединена с группой выходов второго счетчика, счетный вход которого соединен с выходом генератора импульсов, вход сброса второго счетчика соединен с выходом второго элемента сравнения и с вторым входом элемента И-НЕ, четвертый и первый входы шестого элемента И являются соответственно восьмым и девятым управляющими входами блока связи с ЭВМ, выход шестого элемента И соединен с первыми входами элементов И группы и со счетным входом третьего счетчика, вход сброса которого является пятым управляющим входом блока связи с ЭВМ и соединен с первым входом седьмого элемента И, второй вход которого соединен с выходом четвертого элемента ИЛИ, входы которого соединены с выходами третьего счетчика и являются четвертой группой выходов блока связи с ЭВМ, выход переноса третьего счетчика соединен с первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом седьмого элемента И, выход пятого элемента ИЛИ

является шестым выходом блока связи с ЭВМ и соединен с входом сдвига кольцевого регистра, вход начальной установки которого соединен с шестым упрарпч

ющим входом блока связи с ЭВМ, выходы третьего кольцевого регистра соединены с вторыми входами элементов И группы, выходы которых являются пятой группой выходов блока связи с ЭВМ, причем в каждом

блоке коммутации первый вход соединен с первыми входами первого и второго элементов И, выход которого соединен с вычи- тзющим входом первого счетчика, суммирующий вход которого соединен с выходом третьего элемента И, первый вход которого является третьим входом блока коммутации и соединен с первым входом четвертого элемента И, второй вход которого соединен с вторым входом первого элемента И, с первыми входами первого и второго элементов ИЛ Ии-с прямым выходом первого триггера, инверсный выход которого является седьмым выходом блока коммутации, соединен с первым входом третьего

элемента ИЛИ и с входом сброса второго триггера, прямой выход которого соединен с вторым входом второго элемента И, первым входом третьего элемента И и с первым входом четвертого элемента ИЛИ, второй

вход которого соединен с выходом первого элемента НЕ, выход четвертого элемента ИЛИ соединен с входом установки первого триггера, вход синхронизации которого соединен с выходом второго элемента НЕ,

вход которого соединен с третьим входом четвертого элемента ИЛИ. с выходом пятого элемента ИЛИ и с вторым входом третьего элемента ИЛИ, выход которого является пятым выходом блока коммутации, четвертый

выход которого соединен с выходом перено-; са второго счетчика, выходы которого соединены с входами шестого элемента ИЛИ, вычитающий и суммирующий входы второго счетчика соединены с выходами соответственно четвертого и первого элементов И, второй вход блока коммутации соединен с вторым входом второго элемента ИЛИ, выход которого соединен с входом установки второго триггера, инверсный выход которого соединен с вторым входом первого эле- менга ИЛИ, выход которого является восьмым выходом блока коммутации и соединен с первым входом седьмого элемента ИЛИ, второй вход которого соединен с выходом шестого элемента ИЛИ, с третьим входом второго элемента ИЛИ и с входом третьего элемента НЕ, выход которого соединен с входом синхронизации второго триггера, входы пятого элемента ИЛИ соединены с выходами второго счетчика, выход переноса которого является третьим выходом блока коммутации, первый и второй выходы которого соединены с выходами соответственно 5 третьего триггера и седьмого элемента ИЛИ, вход первого элемента НЕ является четвертым входом блока коммутации, инверсный выход третьего триггера соединен со своим информационным входом, вход 10 синхронизации третьего триггера соединен с выходом восьмого элемента ИЛИ, первый вход которого соединен с выходом третьего элемента ИЛИ, второй вход восьмого элемента ИЛИ соединен с выходом четвертого 15 элемента НЕ, вход которого соединен с выходом переноса первого счетчика, вход установки третьего триггера соединен с выходом второго элемента ИЛИ, прямой выход четвертого триггера является шестым 20 выходом блока коммутации, выход переноса второго счетчика соединен с входом пятого элемента НЕ, выход которого соединен с первым входом девятого элемента ИЛИ, выход которого соединен с входом синхро- 25 низации четвертого триггера, информационный вход которого соединен с его инверсным выходом, вход установки четвертого триггера соединен с выходом четвертого элемента ИЛИ, второй вход 30 девятого элемента ИЛИ соединен с выходом седьмого элемента ИЛИ, причем в каждом блоке связи с внешним устройством первый вход выборки соединен с первым управляющим входом коммутатора адреса и 35 соединен с первыми входами элементов И группы, первый вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является первым входом разрешения передачи блока свя-зм с внешним устройством и соединен с первы- 40 ми входами коммутаторов данных первой группы, вторые входы которых соединены с первыми входами элементов ИЛИ группы и с выходами элементов И группы, втррые входы которых являются группой входов вы- 45 бора ЗУ блока связи с внешним устройством, вторая группа адресных входов

которого соединена с первой группой входов коммутатора адреса, вторая группа входов которого является первой группой адресных входов блока связи с внешним устройством, второй вход выборки которого соединен с первым входом первого элемента И, выход которого соединен с вторым управляющим входом коммутатора адреса и соединен с вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с первыми входами коммутаторов данных второй группы и с вторыми входами элементов ИЛИ группы, выходы которых соединены с входами выборки запоминающих устройств, входы режима которых соединены с выходом элемента ИЛИ-НЕ, входы которого соединены с выходами первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является вторым входом разрешения передачи блока связи с внешним устройством и соединен с вторыми входами коммутаторов данных второй группы, первая группа входов-выходов которой соединена с первой группой входов-выходов коммутаторов данных первой группы и с входами-выходами данных запоминающих устройств, входы адреса которых соединены с выходами коммутатора адреса, первая и вторая группы входов-выходов блока связи с внешним устройством соединены с второйгруппойвходов-выходовсоответственно первой и второй групп коммутаторов данных, вход Строб обмена блока связи с внешним устройством соединен с первым входом второго элемента И, выход которого соединен с третьими входами элементов И группы, второй вход второго элемента И соединен с выходом первого элемента НЕ, вход которого соединен с первым входом первого элемента И, второй вход которого соединен с выходом второго элемента НЕ, вход которого соединен с пес - вым входом второго элемента И, выход которого соединен с вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

г-i г

IЭВМ j з

%l1

L-J

б,.

7t

, вы П

|±й

t

8Уми1 II

0. /

CV CM О

f

oo id

г:

11

гз

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1990 |

|

SU1837302A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Устройство для сопряжения ЭВМ с М внешними устройствами | 1986 |

|

SU1374232A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Устройство для сопряжения эвм с внешним устройством | 1988 |

|

SU1513462A1 |

| Устройство для сопряжения ЭВМ с датчиками | 1987 |

|

SU1427375A1 |

| Устройство индикации состояния ЭВМ | 1989 |

|

SU1667067A1 |

| Устройство для временного контроля сигналов интерфейса | 1986 |

|

SU1324028A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1377864A1 |

Изобретение относится к устройствам вычислительной техники и автоматики и может быть использовано при создании различных систем автоматизированного контроля и автоматического управления. Целью изобретения является повышение быстродействия за счет исключения зависимости скорости работы устройства от типа управляющей ЭВМ и расширение области применения устройства за счет появления возможности сопряжения ЭВМ с разноско- ростными внешними устройствами. Устройство содержит блоки коммутации, блоки связи с ЭВМ, блоки связи с внешним устройством, 9 ил.

L,

-J

-I

| Устройство для обмена информацией | 1982 |

|

SU1091151A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения ЭВМ с М внешними устройствами | 1986 |

|

SU1374232A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-10-07—Публикация

1989-10-23—Подача