7/ /г

/J W

// /г

оо 00

ел ND

4

/J /«

Изобретение относится к цифровой вычислительной технике и может быть использовано в цифровых системах, в частности в устройствах обмена информацией.

Целью изобретения является coKpaiueFfHO времени опроса приоритетных источников дискретных сообщений.

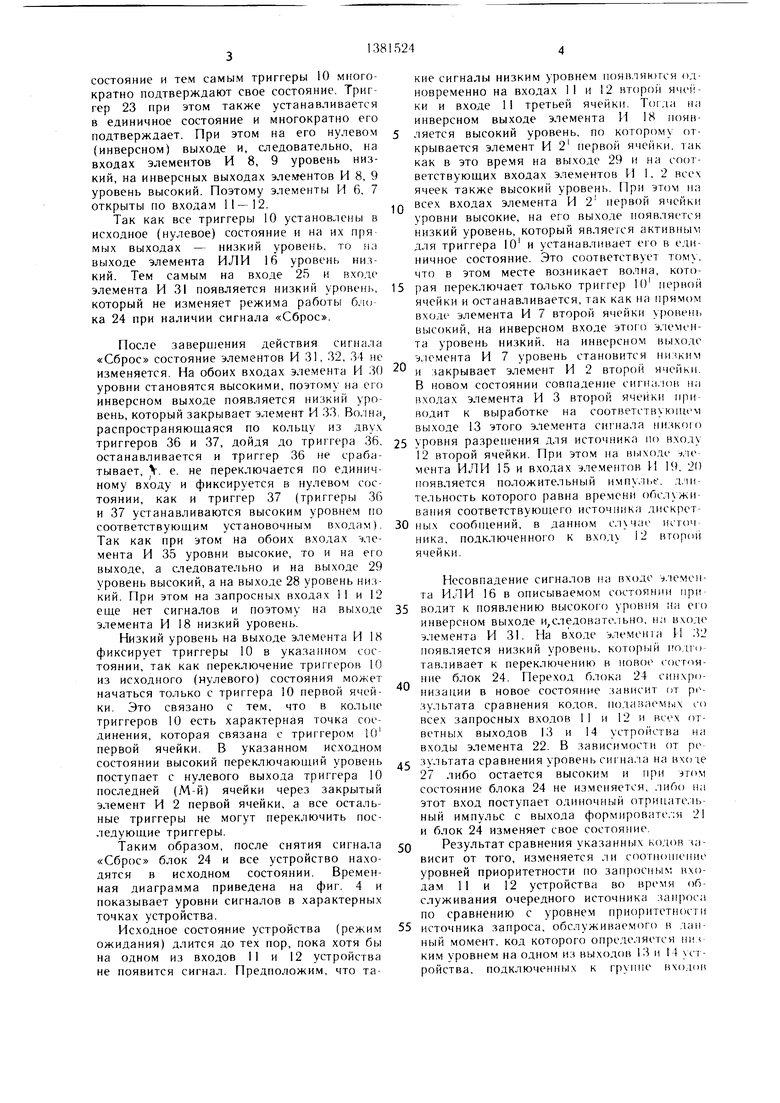

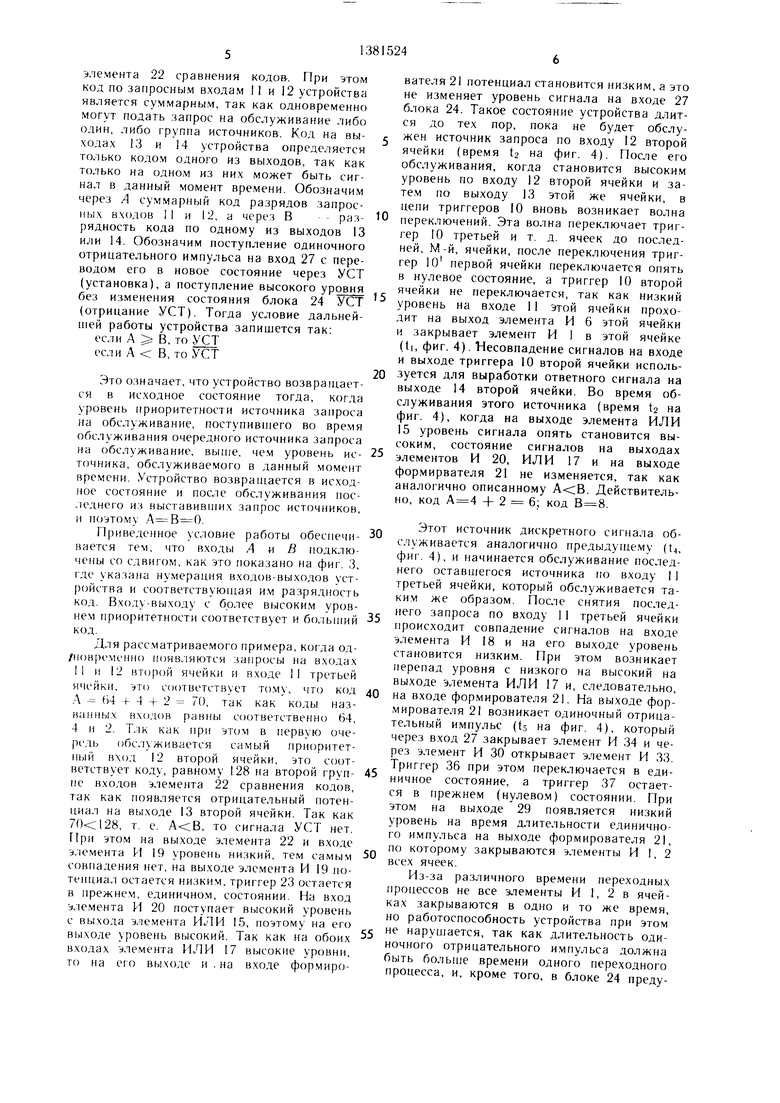

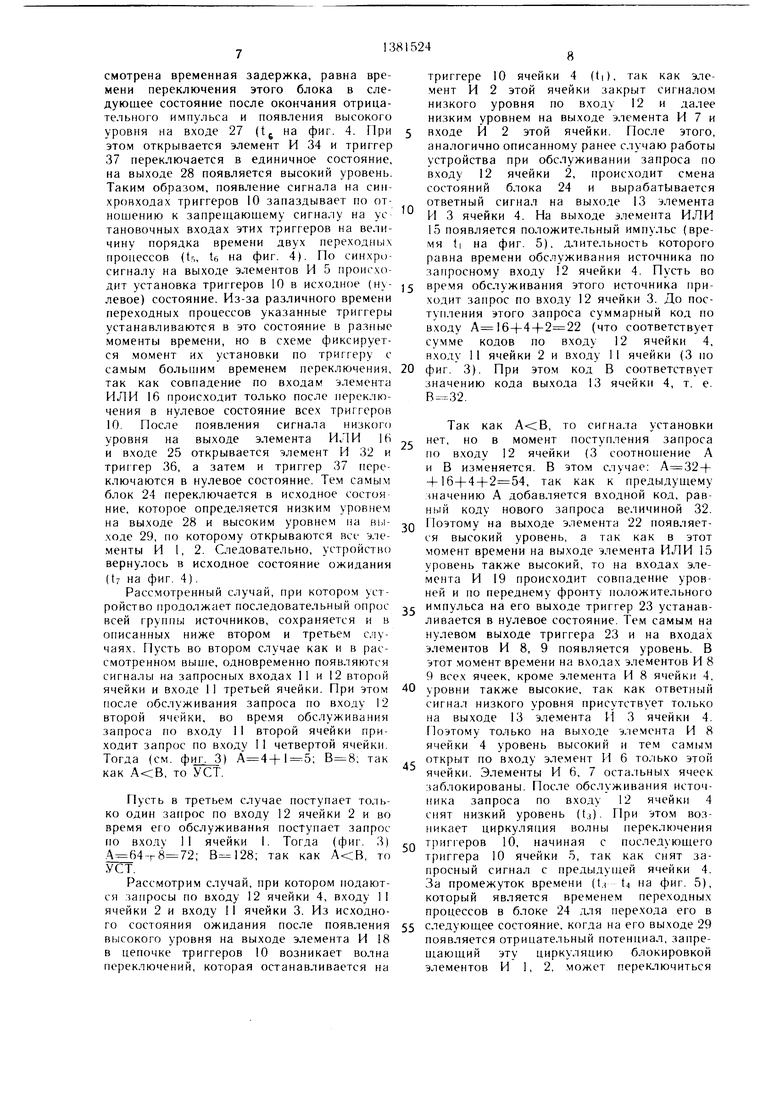

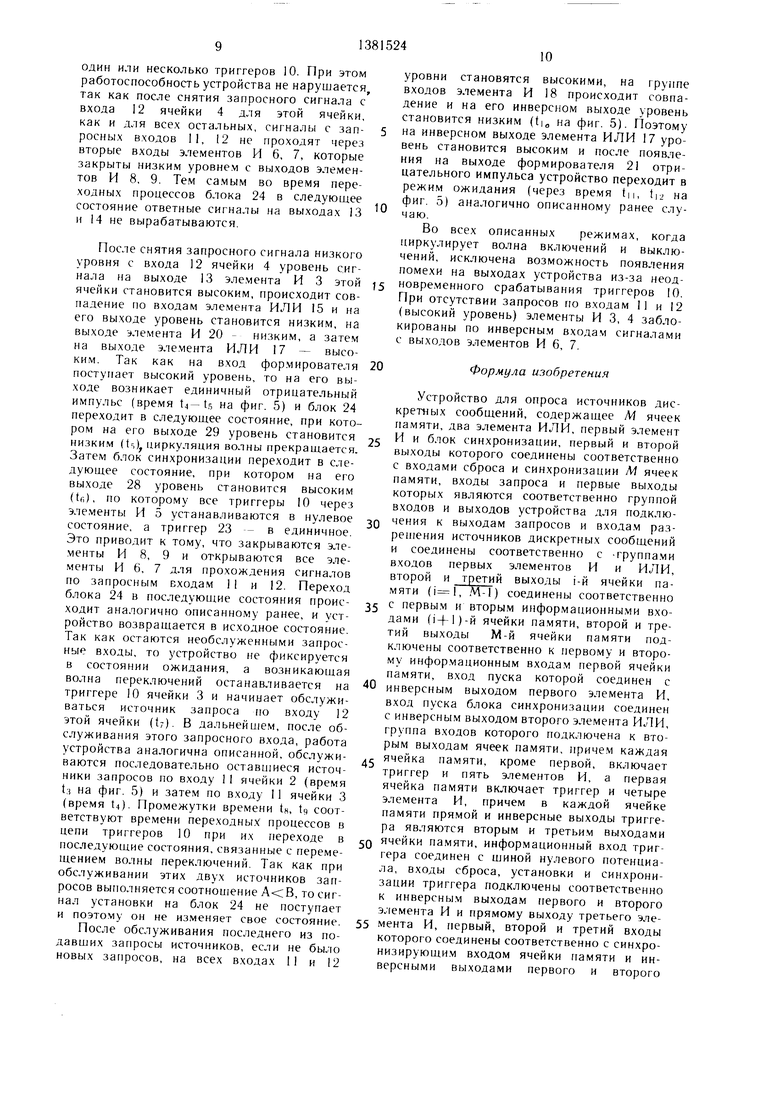

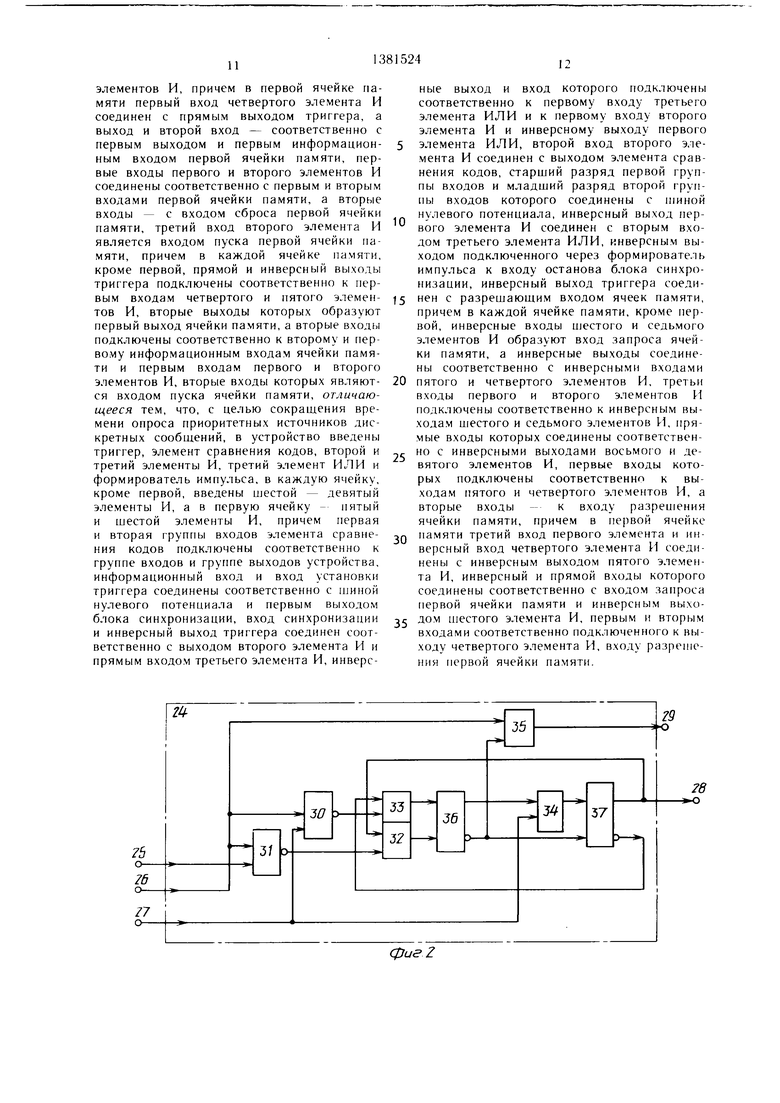

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - функциональная схема блока синхронизации; на фиг. 3 - схема подключения входов элемента сравнения кодов; на фиг. 4 и 5 - временные диаграммы работы устройства.

Устройство содержит М каскадно соединенных ячеек памяти, в каждую из которых, кроме первой, входит первый, второй, пятый, четвертый, третий, шестой - девятый элементы И 1-9 и триггер 10. В первую ячейку памяти входят первый и второй элементы И 1, 2, четвертый элемент И 4, третий элемент И 5, пятый элемент И 6, шестой элемент И 8 и триггер 10. Устройство имеет пару входов 11 и 12 запроса в каждой ячейке памяти, кроме первой, которая содержит один запросный вход 11. Выходы 13 и 14 каждой ячейки, кроме первой, образуют пару выходов устройства для подключения входов paspeuie- ния источников дискретных сообщений. Первая ячейка имеет один выход 14. Устройство содержит также с первого по третий элементы ИЛИ 15, 16, 17, с первого по третий элементы И 18, 19, 20, формирователь 21 импульса, элемент 22 сравнения кодов и триггер 23. Кроме того, в устройство входит блок 24 синхронизации с входами 25, 26, 27 пуска, сброса и останова и с первы.м и вторым выхода.ми 28 и 29.

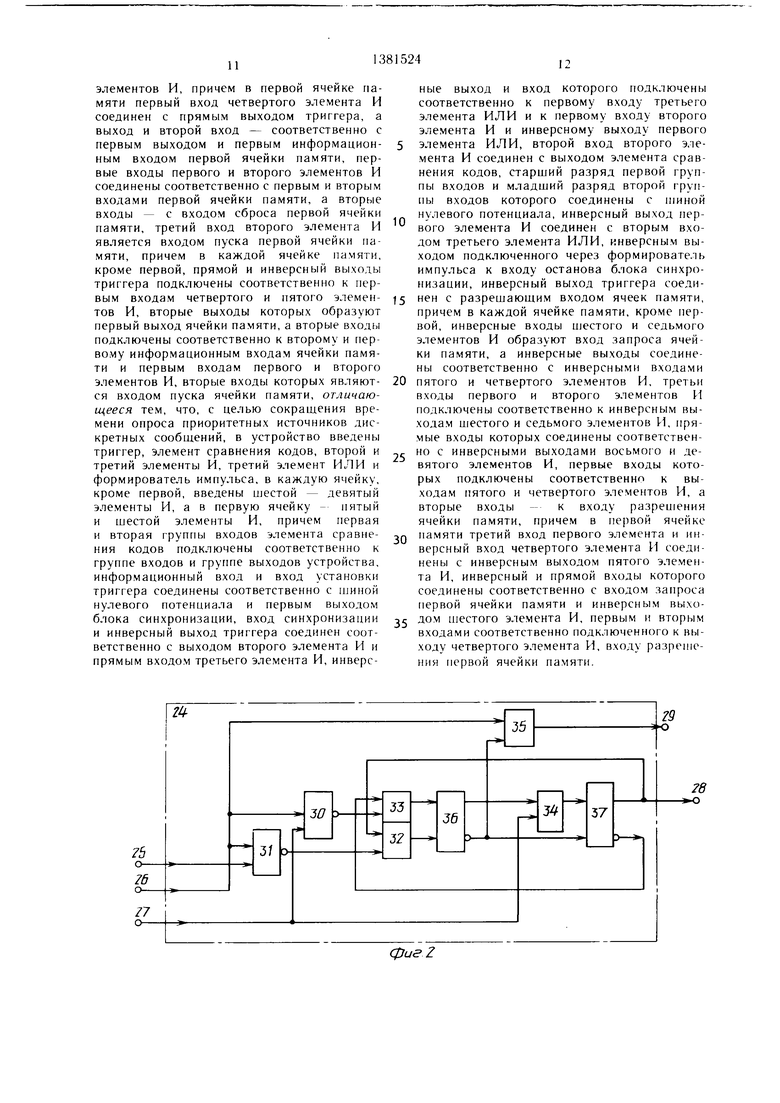

В состав блока 24 синхронизации (фиг. 2) входят шесть элементов И 30- 35 и два триггера 36 и 37.

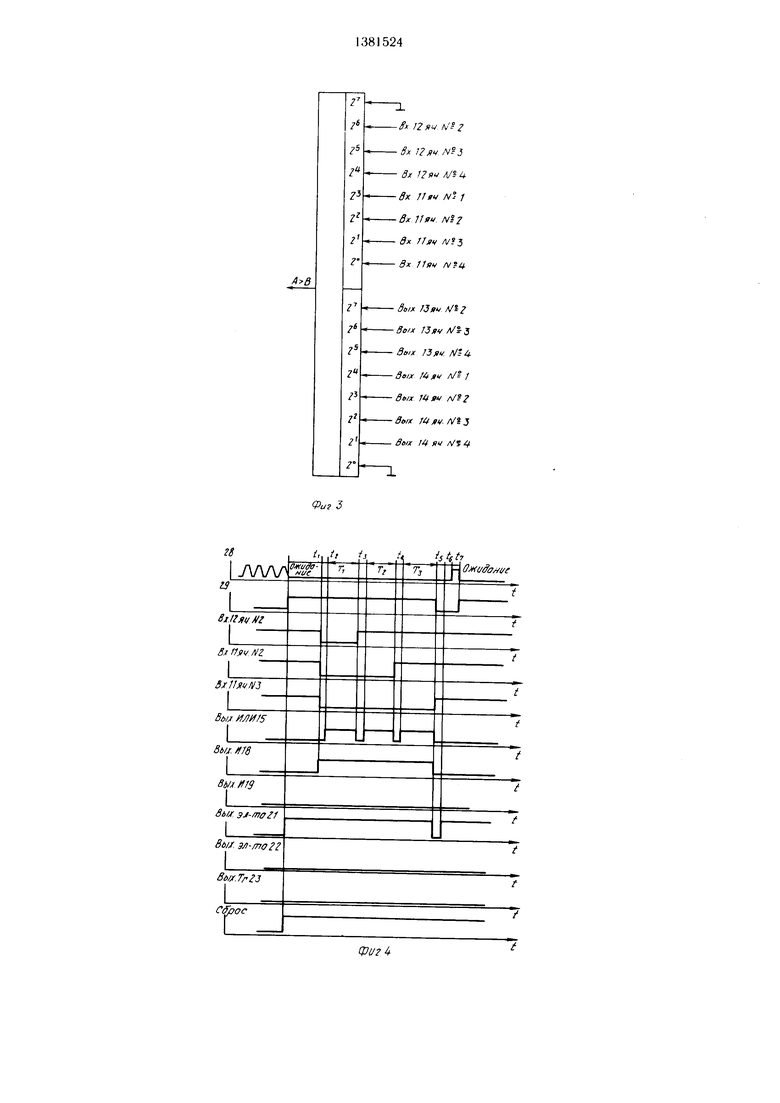

В элементе 22 сравнения кодов (фиг. 3) самый стар1пий по разряду вход первой группы и самый младщий вход второй группы входов соединены с щиной нулевого потенциала. Все последующие входы первой и второй групп входов соединены соответственно с запросными выходами и входами устройства в порядке уменьшения их приоритетности. Самый высокий приоритет в устройстве имеет вход 12 второй ячейки, затем вход 12 третьей ячейки и т. д. до последней (М-й) ячейки, и далее но уровню приоритета следуют вход 11 первой ячейки, вход I1 второй ячейки, затем вход 1 1 третьей ячейки и т. д. до последней (М-й) ячейки. Указанное подключение входов элемента 22 сравнения кодов соответствует то.му, что для устройства, содержащего, например, семь запросных входов (четыре входа II и три входа 12), используется элемент сравнения кодов на восемь двоичных разрядов. При этом пусть код входа 12 второй ячейки имеет двоичную разрядность, равную 64, следующий по

приоритетности код входа 12 третьей ячейки равен и все последующие соответственно 16, 8, 4, 2, 1.

Выходам 13 и 14 устройства для подключения входа разрешения каждого источника дискретных сообщений присваивается приоритетность и двоичная разрядность соответственно входам 11, 12, но со сдвигом на один разряд, т. е. самая высокая приоритетность и двоичный код, равный 128, имеет выход 13 второй ячейки, затем выход 13 третьей ячейки с кодом 64 и т. д. Устройство работает следующим образом. С приходом сигнала «Сброс низкого уровня на вход 26 и первые входы элементов И 30, 31 на их инверсных выходах появляются высокие уровни, которые открывают элементы И 32, 33 (фиг. 2). Так как при этом еще отсутствуют сигналы запроса на входах II и 12 устройства, то на инверсном выходе элемента И 18 уро0 вень низкий, на инверсном выходе элемента ИЛИ 17 и, следовательно, на входе формирователя 21 уровень высокий. Высокий уровень на входе формирователя 21 приводит к формированию им одиночного отрицатель5 ного импульса. При этом на его выходе и, следовательно, на входе 27 уровень высокий. Длительность сигнала «Сброс превышает длительность одиночного импульса формирователя 21 и поэтому на входе 27 уровень становится высоким при одновременно

0 низком уровне на входе 26. Элементы И 32- 34 открыты по своим первы.м входам, т. е. на выходе этих элементов появляется сигнал такого же уровня, что и на вторых входах. По кольцу из триггеров 36 и 37 циркулирует волна включений и выключе5 НИИ до тех пор, пока действует сигнал «Сброс. Во время действия этого сигнала на выходе элемента И 35 и на выходе 29 также низкий уровень, который закрывает все элементы И 1 и 2.

Во время действия сигнала «Сброс на

выходах триггеров 36 и 37 циркуляция волны проявляется в том, что на их выходах генерируется сигнал высокой частоты (порядка 10 мГц) по форме близкий к прямоугольному. В этот момент времени исс пользуется такой сигнал с единичного выхода триггера 37.

Так как на выходе 29 во время действия сигнала «Сброс уровень сигнала низкий, то на инверсных выходах элементов И 1, 2 он высокий, т. е. пассив0 ный для установочных единичных и нулевых входов триггеров 10. Таким образом, сигнал высокой частоты с выхода 28 через элементы И 5 проходит на синхроводы триггеров 10 и устанавливает их в исходное (нулевое) состояние, так как их инфор5 мационные входы подключены к шине нулевого потенциала. Во время действия сигнала «Сброс указанные потенциалы и сигнал на выходе 28 сохраняют описанное

состояние и тем самым триггеры 10 многократно подтверждают свое состояние. Триггер 23 при этом также устанавливается в единичное состояние и многократно его подтверждает. При этом на его нулевом (инверсном) выходе и, следовательно, на входах элементов И 8, 9 уровень низкий, на инверсных выходах элементов И 8, 9 уровень высокий. Поэтому элементы И 6, 7 открыты по входам 11-12.

Так как все триггеры 10 установлены в исходное (нулевое) состояние и на их пря мых выходах - низкий уровень, то на выходе элемента ИЛИ 16 уровень низкий. Тем самым на входе 25 и входе элемента И 31 появляется низкий уровень, который не изменяет режима работы блока 24 при наличии сигнала «Сброс.

После завершения действия сигнала «Сброс состояние элементов И 31, 32, 34 не изменяется. На обоих входах элемента И i5() уровни становятся высокими, поэтому на его инверсном выходе появляется низкий уровень, который закрывает элемент И 33. Волна распространяющаяся по кольцу из двух триггеров 36 и 37, дойдя до триггера 36. останавливается и триггер 36 не срабатывает, V. е. не переключается по единичному входу и фиксируется в нулевом состоянии, как и триггер 37 (триггеры 36 и 37 устанавливаются высоким уровнем по соответствующим установочны.м входам). Так как при этом на обоих входах элемента И 35 уровни высокие, то и на его выходе, а следовательно и на выходе 29 уровень высокий, а на выходе 28 уровень низкий. При этом на запросных входах 11 и 12 еще нет сигналов и поэтому на выходе элемента И 18 низкий уровень.

Низкий уровень на выходе элемента И 18 фиксирует триггеры 10 в указанном состоянии, так как переключение триггеров 10 из исходного (нулевого) состояния может начаться только с триггера 10 первой ячейки. Это связано с тем, что в кольпе триггеров 10 есть характерная точка соединения, которая связана с триггером 10 первой ячейки. В указанном исходном состоянии высокий переключающий уровень поступает с нулевого выхода триггера 10 последней (М-й) ячейки через закрытый элемент И 2 первой ячейки, а все остальные триггеры не могут переключить последующие триггеры.

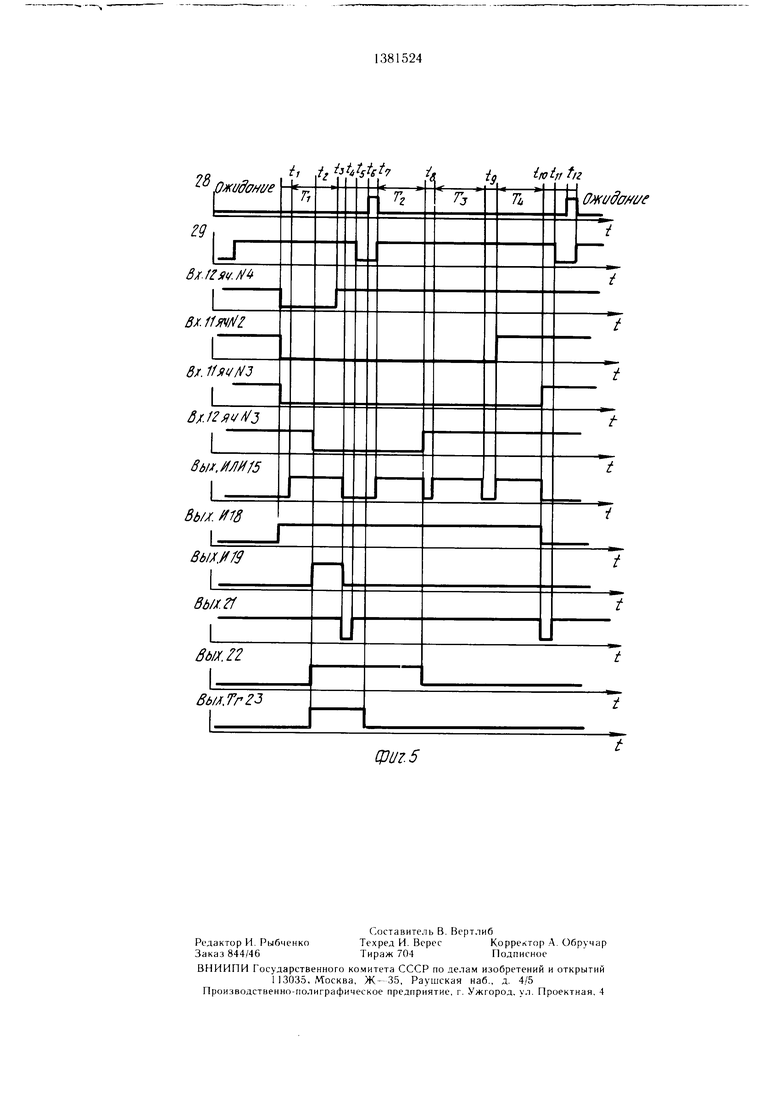

Таким образом, после снятия сигнала «Сброс блок 24 и все устройство находятся в исходном состоянии. Временная диаграмма приведена на фиг. 4 и показывает уровни сигналов в характерных точках устройства.

Исходное состояние устройства (режим ожидания) длится до тех пор, пока хотя бы на одном из входов 11 и 12 устройства не появится сигнал. Предположим, что такие сигналы низким уровнем появляются одновременно на входах 11 и 12 второй ки и входе 11 третьей ячейки. Тогда на инверсном выходе элемента И 18 поянляется высокий уровень, по которому открывается элемент И 2 первой ячейки, так как в это время на выходе 29 и на соответствующих входах элементов И 1,2 всех ячеек также высокий уровень. При этом на

Q всех входах элемента И 2 первой ячейки уровни высокие, на его выходе иояв.пяется низкий уровень, который является активным для триггера 10 и устанавливает ei o в единичное состояние. Это соответствует том. что в этом месте возникает волна, кото5 рая переключает только триггер И) первой ячейки и останавливается, так как на прямом входе элемента И 7 второй ячейки уровень высокий, на инверсном входе этог о элемента уровень низкий, на инверсном выходе элемента И 7 уровень становится низким

и закрывает элемент И 2 второй ячейки. В новом состоянии совпадение сигна.чов на входах элемента И 3 второй ячейки приводит к выработке на соответствующем выходе 13 этого элемента сигнала низко()

5 уровня разреп1ения для источника по входу 12 второй ячейки. При этом на выходе .че мента ИЛИ 15 и входах элементов И 19. 20 появляется положительный импульс, д.пи- тельность которого равна времени обслуживания соответствуюпгего источника дискрет0 ных сообп1ений, в данном с, источ ника, подключенного к входу 12 второй ячейки.

Несовпадение сигналов на входе э.чемсн- та ИЛИ 16 в описываемом состоянии нри5 водит к появлению высокого уровня на его инверсном выходе последовательно, на входе элемента И 31. На входе элемен1а И 32 появляется низкий уровень, который тавливает к переключению в новое состояние блок 24. Переход блока 24 синхронизации в новое состояние зависит от результата сравнения кодов, подаваемых со всех запросных входов 11 и 12 и всех ответных выходов 13 и 14 устройства на входы элемента 22. В зависимости от ре5 зультата сравнения уровень сигна.ма на нхо le 27 либо остается высоким и при этом состояние блока 24 не изменяется, либо на этот вход поступает одиночный отрицательный импульс с выхода формирователя 21 и блок 24 изменяет свое состояние.

0 Результат сравнения указанных кодов зависит от того, изменяется ли с(Х1тнон1Снио уровней приоритетности по запросным входам 11 и 12 устройства во время обслуживания очередного источника запроса по сравнению с уровнем приоритетности

5 источника запроса, обслуживаемого и данный момент, код которого определяется низ КИМ уровнем на одном из выходов 13 и 14 ci- ройства, подключенных к группе входов

0

элемента 22 сравнения кодо&. При этом код по запросным входам 11 и 12 устройства является суммарным, так как одновременно могут подать запрос на обслуживание либо один, либо группа источников. Код на вы- ходах 13 и 14 устройства определяется только кодом одного из выходов, так как только на одном из них может быть сигнал в данный момент времени. Обозначим через А суммарный код разрядов запросных входов 11 н 12, а через В - раз- рядность кода по одному из выходов 13 или 14. Обозначим поступление одиночного отрицательного импульса на вход 27 с переводом его в новое состояние через УСТ (установка), а поступ,ление высокого уровня без изменения состояния блока 24 УСТ (отрицание УСТ). Тогда условие дальней- И1ей работы устройства запишется так:

если А В, то УСТ

если А В, то УСТ

Это означает, что устройство возвращается в исходное состояние тогда, когда уровень приоритетности источника запроса на обслуживание, поступившего во время обслуживания очередного источника запроса на обслуживание, , чем уровень ис- точника, обслуживаемого в данный .мо.мент времени. Устройство возвращается в исходное состояние и после обслуживания последнего из выставивших запрос источников, и поэтому ..

Приведенное условие работы обеспечи- Бается тем, что входы А и В подключены со сдвигом, как это показано на фиг. 3, г де указана нумерация входов-выходов устройства и соответствующая им разрядность код. Входу-выходу с более высоким уровнем приоритетности соответствует и больший код.

Для рассматриваемого примера, когда од- /новре.мешю появ. тются запросы на входах 11 и 12 второй ячейки и входе 11 третьей ячейки, это соответствует то.му, что код А Н4 f 4 + 2 70, так как коды названных входов равны соответственно 64, 4 и 2. Тлк как при этом в первую очередь обс.чуживается самый прие)ритет- ный вход 12 второй ячейки, это соответствует коду, равному 128 на второй груп- пе входов элемента 22 сравнения кодов, так как появляется отрицательный потенциал на выходе 13 второй ячейки. Так как , т. е. , то сигнала УСТ нет. При этом на выходе элемента 22 и входе элемента И 19 уровень низкий, тем самы.м совпадения нет, на выходе элемента И 19 потенциал остается низким, триггер 23 остается в прежнем, единичном, состоянии. На вход элемента И 20 поступает высокий уровень с выхода элемента ИЛИ 15, поэтому на его выходе уровень высокий. Так как на обоих входах элемента ИЛИ 17 высокие уровни, то на его выходе и . на входе формирователя 21 потенциал становится низким, а это не изменяет уровень сигнала на входе 27 блока 24. Такое состояние устройства длится до тех пор, пока не будет обслужен источник запроса по входу 12 второй ячейки (время t2 на фиг. 4). Посте его обслуживания, когда становится высоким уровень по входу 12 второй ячейки и затем по выходу 13 этой же ячейки, в цепи триггеров 10 вновь возникает волна переключений. Эта волна переключает триггер 10 третьей и т. д. ячеек до последней, М-й, ячейки, после переключения триггер 10 первой ячейки переключается опять в пулевое состояние, а триггер 10 второй ячейки не переключается, так как низкий уровень на входе 11 этой ячейки проходит на выход элемента И 6 этой ячейки и закрывает элемент И 1 в этой ячейке (t|, фиг. 4). Несовпадение сигналов на входе и выходе триггера 10 второй ячейки используется для выработки ответного сигнала на выходе 14 второй ячейки. Во время обслуживания этого источника (время 12 на фиг. 4), когда на выходе элемента ИЛИ 15 уровень сигнала опять становится высоким, состояние сигналов на выходах элементов И 20, ИЛИ 17 и на выходе формирвателя 21 не изменяется, так как аналогично описанному . Действительно, код + 2 6; код .

Этот источник дискретного сигнала обслуживается аналогично предыдуц1ему (t4, фиг. 4), и начинается обслуживание последнего оставшегося источника но входу 1 третьей ячейки, который обслуживается таким же образом. После снятия последнего запроса по входу 1 1 третьей ячейки происходит совпадение сигналов на входе элемента И 18 и на его выходе уровень становится низким. При этом возникает перепад уровня с низкого на высокий на выходе элемента ИЛИ 17 и, следовательно, на входе формирователя 21. На выходе формирователя 21 возникает одиночный отрицательный импульс (ts на фиг. 4), который через вход 27 закрывает элемент И 34 и через эле.мент И 30 открывает эле.мент И 33. Триггер 36 при этом переключается в единичное состояние, а триггер 37 остается в прежнем (нулевом) состоянии. При этом на выходе 29 появляется низкий уровень на время длительности единичного импульса на выходе формирователя 21, по которому закрываются элементы И 1, 2 всех ячеек.

Из-за различного времени переходных процессов не все элементы И 1, 2 в ячейках закрываются в одно и то же время, но работоспособность устройства при этом не нарушается, так как длительность одиночного отрицательного импульса должна быть больп е времени одного переходного процесса, и, кроме того, в блоке 24 предусмотрена временная задержка, равна времени перек;1ючения этого блока в следующее состояние после окончания отрицательного импульса и появления высокого уровня на входе 27 (tj на фиг. 4. При этом открывается элемент И 34 и триггер 37 переключается в единичное состояние, на выходе 28 появляется высокий уровень. Таким образом, появление сигнала на сим- хровходах триггеров 10 запаздывает по отношению к запрещающему сигналу на ус тановочных входах этих триггеров на величину порядка времени двух переходных процессов (t-,, te на фиг. 4). По синхросигналу на выходе элементов И 5 происходит установка триггеров 10 в исходное (нулевое) состояние. Из-за различного времени переходных процессов указанные триггеры устанавливаются в это состояние в разные моменты времени, но в схеме фиксируется .момент их установки по триггеру с самым большим временем переключения, так как совпадение по входам элемента ИЛИ 16 происходит только после переключения в нулевое состояние всех триггеров 10. После появления сигнала низкого уровня на выходе элемента ИЛИ 16 и входе 25 открывается элемент И 32 и триггер 36, а затем и триггер 37 переключаются в нулевое состояние. Тем самым блок 24 переключается в исходное состоя ние, которое определяется низким уровнем на выходе 28 и высоким уровнем на выходе 29, по которому открываются все элементы И 1, 2. Следовательно, устройство вернулось в исходное состояние ожидания (t на фиг. 4).

Рассмотренный случай, при котором устройство продолжает последовательный опрос всей группы источников, сохраняется и в описанных ниже втором и третьем случаях. Пусть во втором случае как и в рассмотренном Bbinie, одновременно появляются сигналы на запросных входах 11 и 12 второй ячейки и входе 11 третьей ячейки. При этом после обслуживания запроса по входу 12 второй ячейки, во время обслуживания запроса по входу 11 второй ячейки приходит запрос по входу II четвертой ячейки. Тогда (см. фиг, 3) так как , то УСТ.

Пусть в третьем случае поступает только один запрос по входу 12 ячейки 2 и во время его обслуживания поступает запрос по входу 11 ячейки 1. Тогда (фиг. 3) .Л 64-г8 72; так как , то УСТ.

Рассмотрим случай, при котором подаются запросы по входу 12 ячейки 4, входу 1 1 ячейки 2 и входу 11 ячейки 3. Из исходного состояния ожидания после появления высокого уровня на выходе э.темента И 18 в цепочке триггеров 10 возникает волна переключений, которая останавливается на

8

триггере 10 ячейки 4 (ti), так мент И 2 этой ячейки закрыт низкого уровня низким уровнем на входе И 2 этой

как эле- сигналом и далее

по входу 12 выходе элемента И 7 и ячейки. После этого,

0

5

0

5

0

5

0

5

0

5

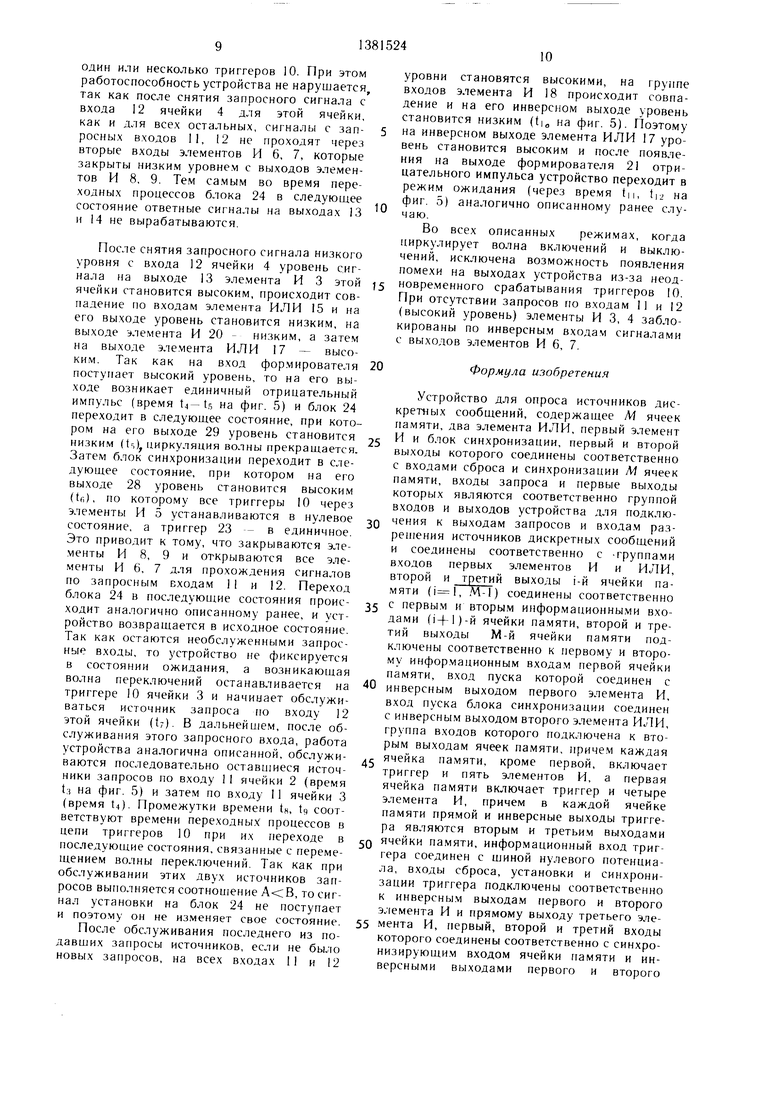

аналогично описанному ранее случаю работы устройства при обслуживании запроса по входу 12 ячейки 2, происходит смена состояний блока 24 и вырабатывается ответный сигнал на выходе 13 эле.мента И 3 ячейки 4. На выходе элемента ИЛИ 15 появляется положительный импульс (время ti на фиг. 5). длительность которого равна времени обслуживания источника по запросному входу 12 ячейки 4. Пусть во время обслуживания этого источника приходит запрос по входу 12 ячейки 3. До поступления этого запроса суммарный код по входу А: 16-)--4 + (что соответствует су.мме кодов по входу 12 ячейки 4, входу 11 ячейки 2 и входу 1I ячейки (3 по фиг. 3). При этом код В соответствует значению кода выхода 13 ячейки 4, т. е.

8 32.

Так как , то сигнала установки нет, но в момент поступления запроса по входу 12 ячейки (3 соотношение А и В изменяется. В этом случае: + -(-16+4 + , так как к предыдущему значению А добавляется входной код, равный коду нового запроса величиной 32. Поэтому на выходе элемента 22 появляется высокий уровень, а так как в этот момент времени на выходе эле.мента ИЛИ 15 уровень также высокий, то на входах элемента И 19 происходит совпадение уровней и по переднему фронту положительного импульса на его выходе триггер 23 устанавливается в нулевое состояние. Тем самым на нулевом выходе триггера 23 и на входах элементов И 8, 9 появляется уровень. В этот момент времени на входах элементов И 8

9всех ячеек, кроме элемента И 8 ячейки 4, уровни также высокие, так как ответный сигнал низкого уровня присутствует только на выходе 13 элемента И 3 ячейки 4. Поэтому только на выходе элемента И 8 ячейки 4 уровень высокий и тем самым открыт по входу элемент И 6 только этой ячейки. Элементы И 6, 7 остальных ячеек заблокированы. После обслуживания источника запроса по входу 12 ячейки 4 снят низкий уровень (tj). При этом возникает циркуляция волны переключения трип еров 10, начиная с последующего триггера 10 ячейки 5, так как снят запросный сигнал с предыдущей ячейки 4. За промежуток времени (t,i t на фиг. 5), который является временем переходных процессов в блоке 24 для перехода его в следующее состояние, когда на его выходе 29 появляется отрицательный потенциал, запрещающий эту циркуляцию блокировкой элементов И 1, 2, может переключиться

один или несколько триггеров 10. При этом работоспособность устройства не нарушается, так как после снятия запросного сигнала с входа 12 ячейки 4 для этой ячейки, как и для всех остальных, сигналы с зап- росных входов 11, 12 не проходят через вторые входы элементов И 6, 7, которые закрыты низким уровнем с выходов элементов И 8, 9. Тем самым во время переходных процессов блока 24 в следующее состояние ответные сигналы на выходах 13 и 14 не вырабатываются.

После снятия запросного сигнала низкого уровня с входа 12 ячейки 4 уровень сигнала на выходе 13 элемента И 3 этой ячейки становится высоким, происходит совпадение по входам элемента ИЛИ 15 и на его выходе уровень становится низким, на выходе элемента И 20 - низким, а зате.м на выходе элемента ИЛИ 17 - высоким. Так как на вход формирователя поступает высокий уровень, то на его выходе возникает единичный отрицательный импульс (время на фиг. 5) и блок 24 переходит в следующее состояние, при котором на его выходе 29 уровень становится низким (ts)., циркуляция волны прекращается. Затем блок синхронизации переходит в следующее состояние, при котором на его выходе 28 уровень становится высоким (tfi), по которому все триггеры 10 через элементы И 5 устанавливаются в нулевое состояние, а триггер 23 - в единичное. Это приводит к тому, что закрываются эле- .менты И 8, 9 и открываются все элементы И 6, 7 для прохождения сигналов по запросным входам 11 и 12. Переход блока 24 в последующие состояния проис- ходит аналогично описанному ранее, и устройство возвращается в исходное состояние. Так как остаются необслуженными запросные входы, то устройство не фиксируется в состоянии ожидания, а возникающая

волна переключении останавливается на

триггере 10 ячейки 3 и начинает обслуживаться источник запроса по входу 12 этой ячейки (t;). В дальнейшем, после обслуживания этого запросного входа, работа устройства аналогична описанной, обслужи- ваются последовательно оставшиеся источники запросов по входу 11 ячейки 2 (время t:i на фиг. 5) и затем по входу 11 ячейки 3 (время t4). Промежутки времени t«, ts соответствуют времени переходных процессов в цепи триггеров 10 при их переходе в последующие состояния, связанные с перемещением волны переключений. Так как при обслуживании этих двух источников запросов выполняется соотношение , то сигнал установки на блок 24 не поступает и поэтому он не изменяет свое состояние.

После обслуживания последнего из подавших запросы источников, если не было новых запросов, на всех входах 11 и 12

5

0

5 0 5 o r

0

.г Q 5

уровни становятся высокими, на группе входов элемента И 18 происходит совпадение и на его инверсном выходе уровень становится низким (ti на фиг. 5). Поэтому на инверсном выходе элемента ИЛИ 17 уровень становится высоким и после появления на выходе формирователя 21 отрицательного импульса устройство переходит в режим ожидания (через время tn, t|2 на фиг. 5) аналогично описанному ранее случаю.

Во всех описанных режи.мах, когда циркулирует волна включений и выключений, исключена возможность появления помехи на выходах устройства из-за неодновременного срабатывания триггеров 10. При отсутствии запросов по входам II и 12 (высокий уровень) элементы И 3, 4 заблокированы по инверсным входам сигналами с выходов элементов И 6, 7.

Формула изобретения

Устройство для опроса источников дискретных сообщений, содержащее М ячеек памяти, два элемента ИЛИ, первый элемент И и блок синхронизации, первый и второй выходы которого соединены соответственно с входами сброса и синхронизации М ячеек памяти, входы запроса и первые выходы которых являются соответственно группой входов и выходов устройства для подключения к выходам запросов и входам разрешения источников дискретных сообщений и соединены соответственно с -группа.ми входов первых элементов И и ИЛИ, второй и третий выходы i-й ячейки памяти (, М-1) соединены соответственно с первым и вторым информационными входами (- )-н ячейки па.мяти, второй и третий выходы М-й ячейки памяти подключены соответственно к первому и второму инфор.мационньш входам первой ячейки памяти, вход пуска которой соединен с инверсным выходом первого элемента И, вход пуска блока синхронизации соединен с инверсным выходом второго элемента ИЛИ, группа входов которого подключена к вторым выходам ячеек памяти, причем каждая ячейка памяти, кроме первой, включает триггер и пять элементов И, а первая ячейка памяти включает триггер и четыре элемента И, причем в каждой ячейке памяти прямой и инверсные выходы триггера являются вторым и третьи.м выходами ячейки памяти, информационный вход триггера соединен с шиной нулевого потенциала, входы сброса, установки и синхронизации триггера подключены соответственно к инверсным выходам первого и второго элемента И и прямому выходу третьего элемента И, первый, второй и третий входы которого соединены соответственно с синхронизирующим входом ячейки памяти и инверсными выходами первого и второго

элементов И, причем в первой ячейке памяти первый вход четвертого элемента И соединен с прямым выходом триггера, а выход и второй вход - соответственно с первым выходом и первым информационным входом первой ячейки памяти, первые входы первого и второго элементов И соединены соответственно с первым и вторым входами первой ячейки памяти, а вторые входы - с входом сброса первой ячейки памяти, третий вход второго элемента И является входом пуска первой ячейки памяти, причем в каждой ячейке памяти, кроме первой, прямой и инверсный выходы триггера подключены соответственно к первым входам четвертого и пятого элементов И, вторые выходы которых образуют первый выход ячейки памяти, а вторые входы подключены соответственно к второму и первому информационным входам ячейки памяти и первым входам первого и второго элементов И, вторые входы которых являются входом пуска ячейки памяти, отличающееся тем, что, с целью сокращения времени опроса приоритетных источников дискретных сообщений, в устройство введены триггер, элемент сравнения кодов, второй и третий элементы И, третий элемент ИЛИ и формирователь импульса, в каждую ячейку, кроме первой, введены шестой - девятый элементы И, а в первую ячейку - пятый и щестой элементы И, причем первая и вторая группы входов элемента сравнения кодов подключены соответственно к группе входов и группе выходов устройства, информационный вход и вход установки триггера соединены соответственно с тиной нулевого потенциала и первым выходом блока синхронизации, вход синхронизации и инверсный выход триггера соединен соответственно с выходом второго элемента И и прямым входом третьего элемента И, инверсные выход и вход которого подключены соответственно к первому входу третьего элемента ИЛИ и к первому входу второго элемента И и инверсному выходу первого элемента ИЛИ, второй вход второго элемента И соединен с выходом элемента сравнения кодов, старщий разряд первой группы входов и младщий разряд второй группы входов которого соединены с щиной нулевого потенциала, инверсный выход первого элемента И соединен с вторым входом третьего элемента ИЛИ, инверсным выходом подключенного через формирователь импульса к входу останова блока синхронизации, инверсный выход триггера соеди5 нен с разрещающим входом ячеек памяти, причем в каждой ячейке памяти, кроме первой, инверсные входы niecToro и седьмого элементов И образуют вход запроса ячейки памяти, а инверсные выходы соединены соответственно с инверсными входами

0 пятого и четвертого элементов И, третьи входы первого и второго элементов И подключены соответственно к инверсным выходам шестого и седьмого элементов И, прямые входы которых соединены соответственс но с инверсными выходами восьмого и девятого элементов И, первые входы которых подключены соответственно к выходам пятого и четвертого элементов И, а вторые входы - к входу разрешения ячейки памяти, причем в первой ячейке

0 памяти третий вход первого элемента и инверсный вход четвертого элемента И соединены с инверсным выходом пятого элемента И, инверсный и прямой входы которого соединены соответственно с входом запроса первой ячейки памяти и инверсным выхо5 дом шестого элемента И, первым и вторым входами соответственно подключенного к выходу четвертого элемента И, входу разрешения первой ячейки памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приоритета | 1988 |

|

SU1531097A1 |

| Отказоустойчивая вычислительная система | 1990 |

|

SU1798800A1 |

| Устройство для обслуживания запросов | 1990 |

|

SU1728863A1 |

| Устройство для опроса источников дискретных сообщений | 1986 |

|

SU1406597A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 1992 |

|

RU2108618C1 |

| Устройство приоритета | 1986 |

|

SU1365084A1 |

| Устройство для обслуживания запросов | 1988 |

|

SU1550517A1 |

| Устройство для опроса источников дискретных сообщений | 1985 |

|

SU1278860A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Устройство динамического приоритета | 1990 |

|

SU1756888A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в цифровых системах, в частности в устройствах обмена информацией. Цель изо бретения - сокращение времени опроса приоритетных источников дискретных сообщений. Устройство содержит М каскадно соединенных ячеек памяти, два элемента ИЛИ 15 и 16, элемент И 18 и блок 24 синхронизации. Каждая из ячеек, кроме первой, содержит триггер 10 и пять элементов И 1-5. В устройство введены триггер 23, второй, третий элементы И 19 и 20, третий элемент ИЛИ 17, формирователь 21 импульса, элемент 22 сравнения кодов, а в каждую ячейку, кроме первой, введены четыре элемента И 6-9. Принцип работы состоит в том, что каждый раз во время опроса и обслуживания очередного источника дискретных сообщений производится сравнение приоритетности вновь поступивших запросов по отнощению к обслуживаемому. В зависимости от результата этого сравнения устройство продолжает опрашивать последуюшие источники или возврашается в исходное состояние. 5 ил. (Л

фиг 2

(Put 5

| Устройство для опроса инсточников дискретных сообщений | 1978 |

|

SU694857A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для опроса источников дискретных сообщений | 1985 |

|

SU1278860A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-15—Публикация

1986-06-17—Подача