Изобретение относится к вычислительной технике и может быть использовано при построении цифровых вычислительных систем повышенной надежности и производительности.

Целью изобретения является повышение надежности системы в режиме обслуживания внешних абонентов за счет подключения внешнего абонента к исправ- .ному процессору.

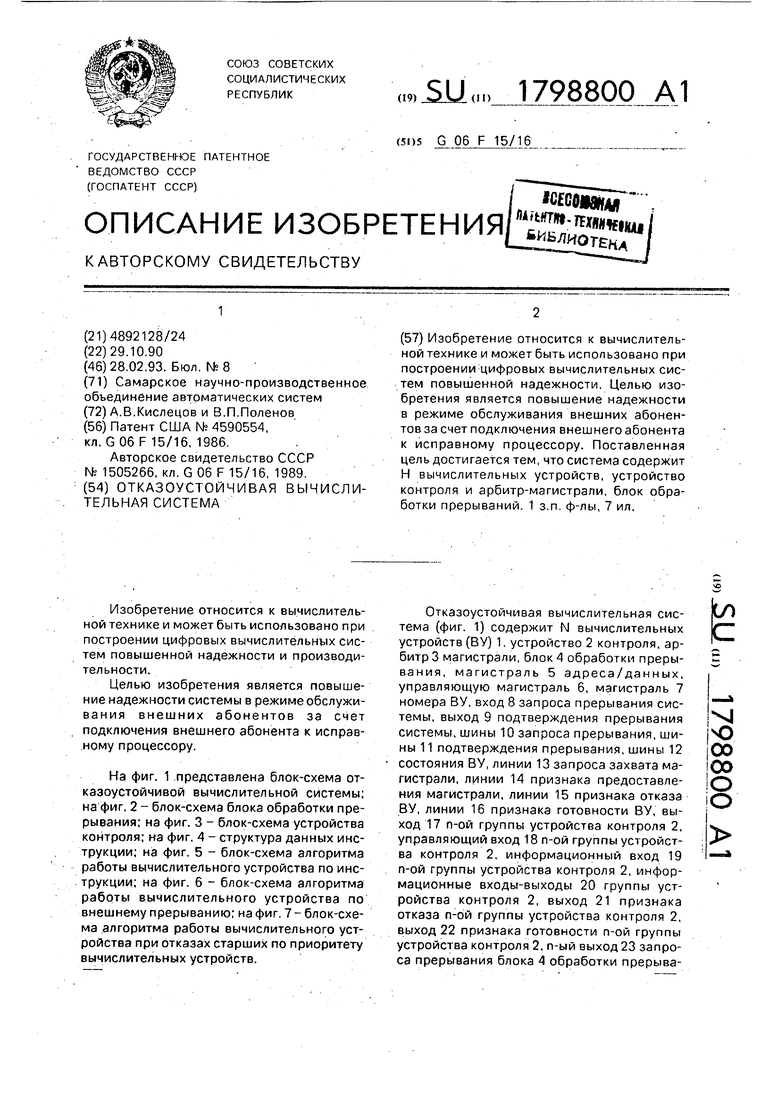

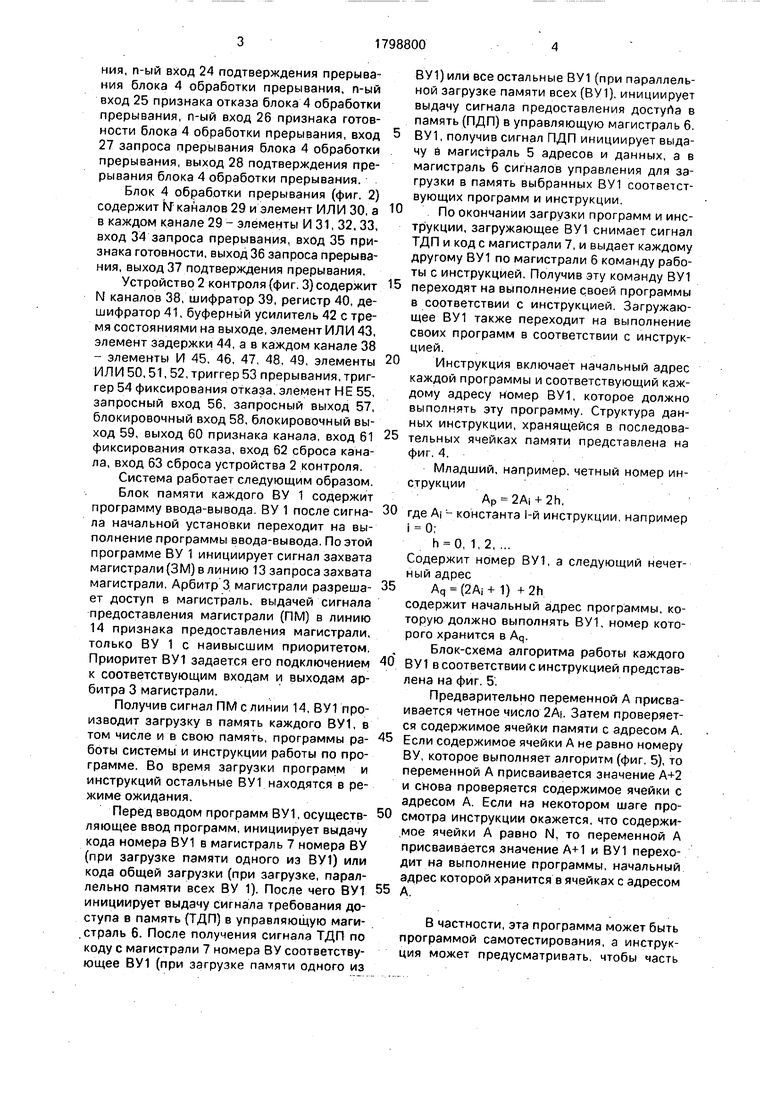

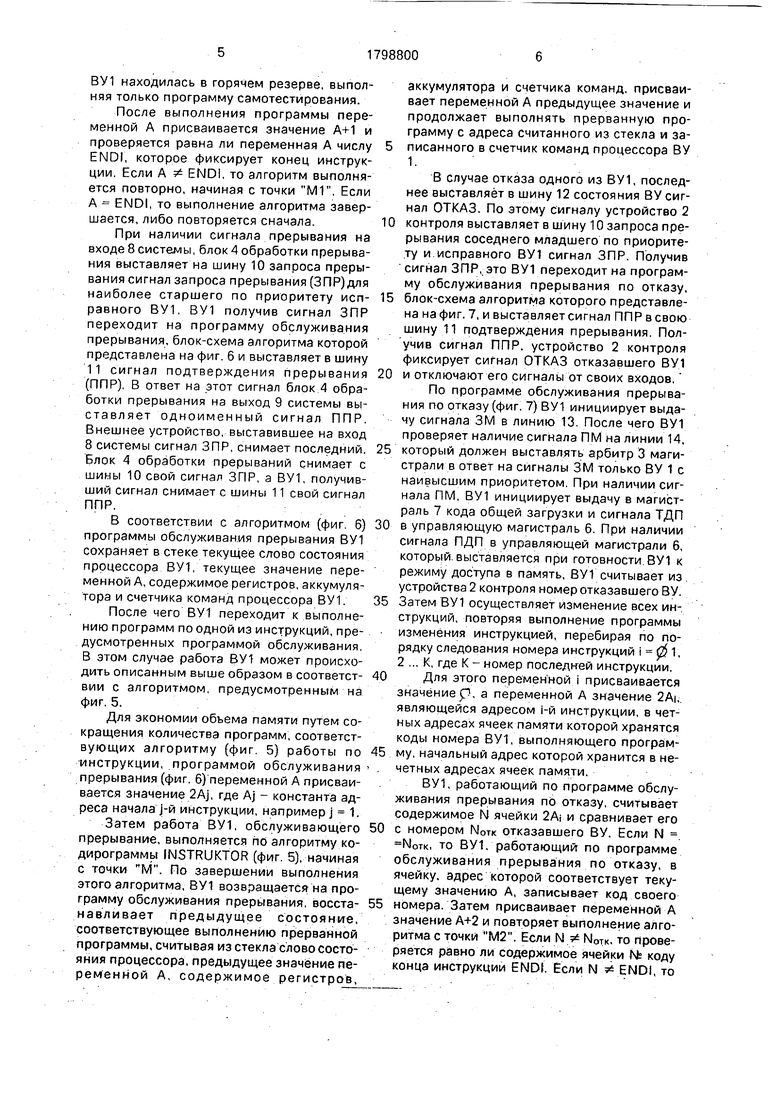

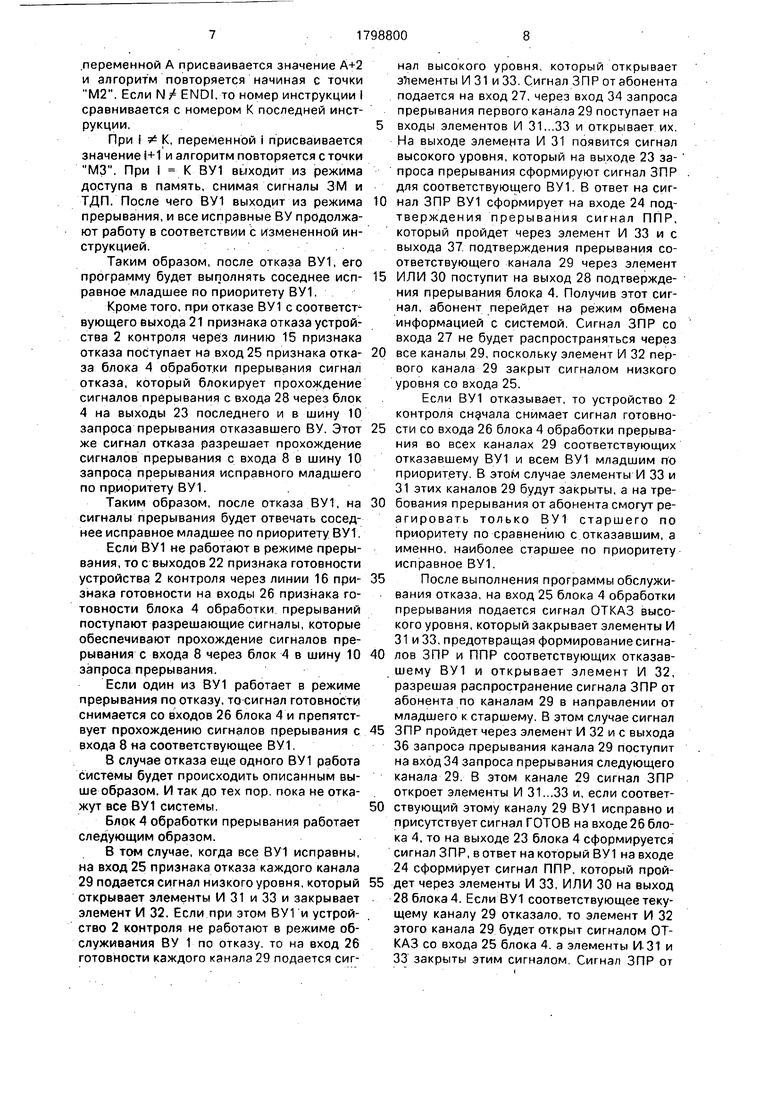

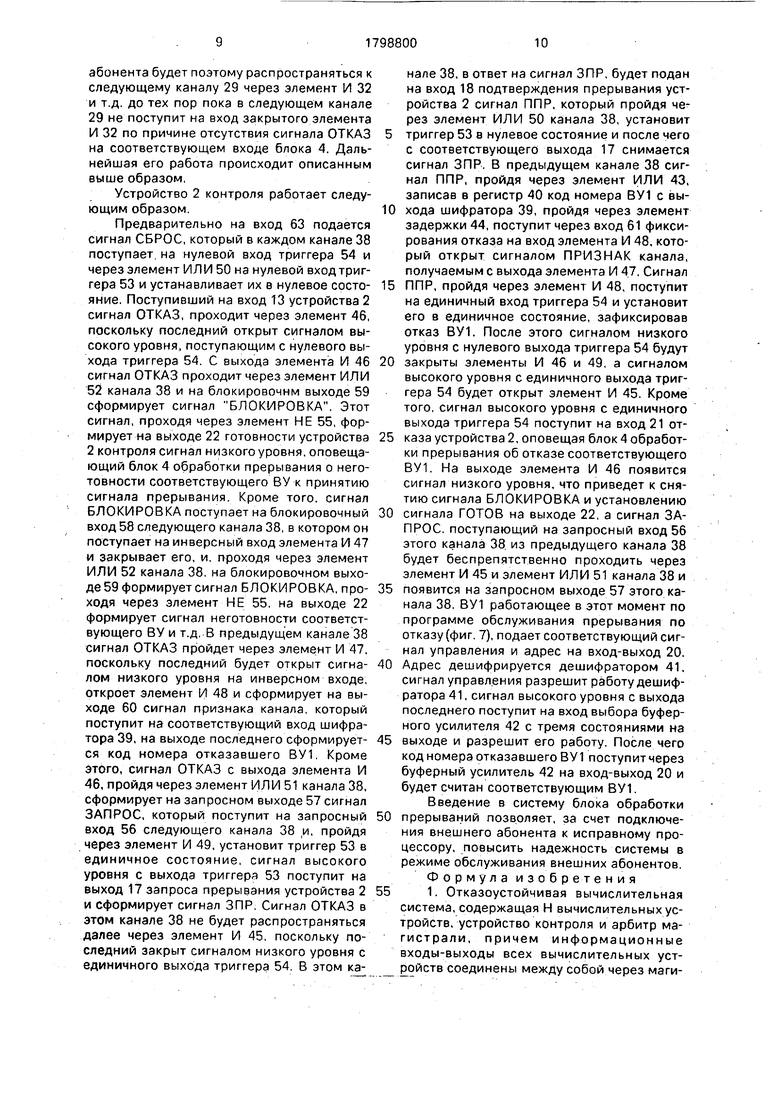

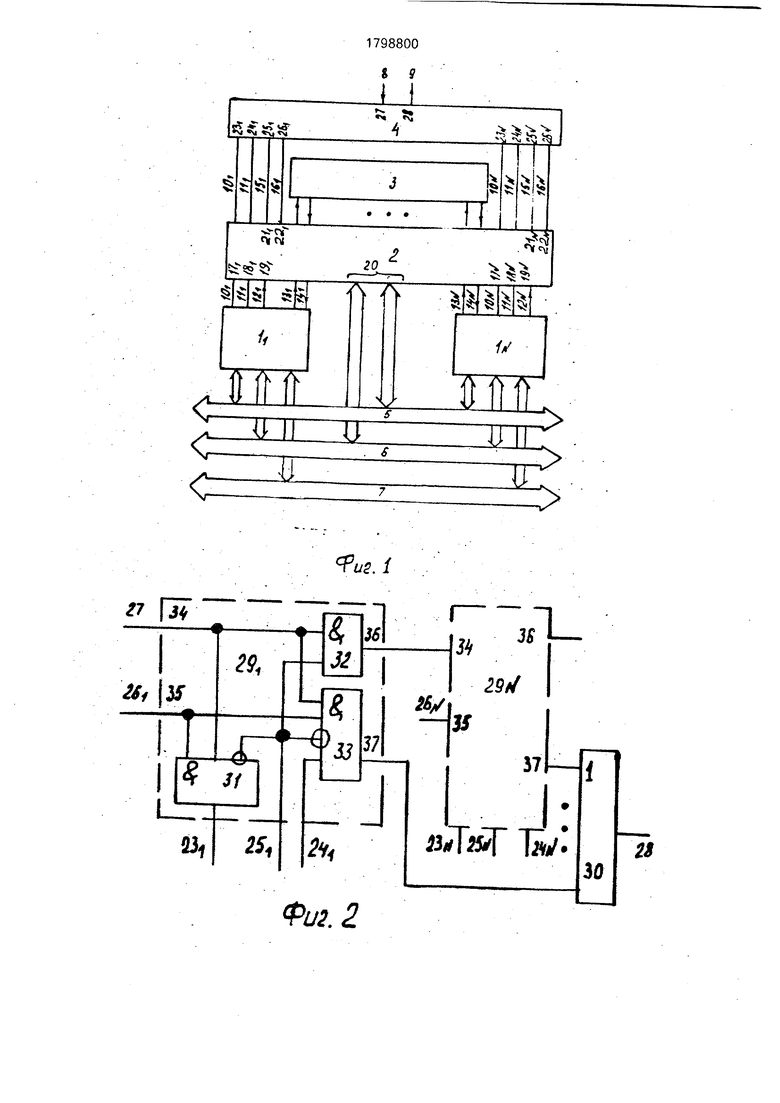

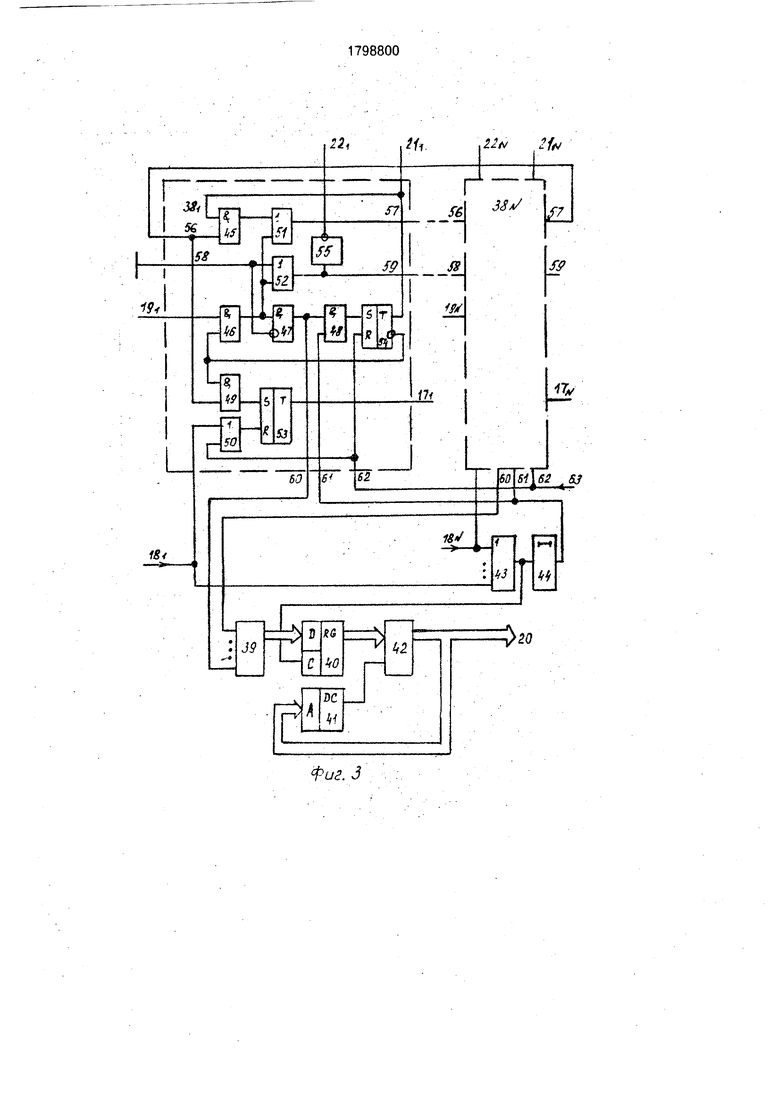

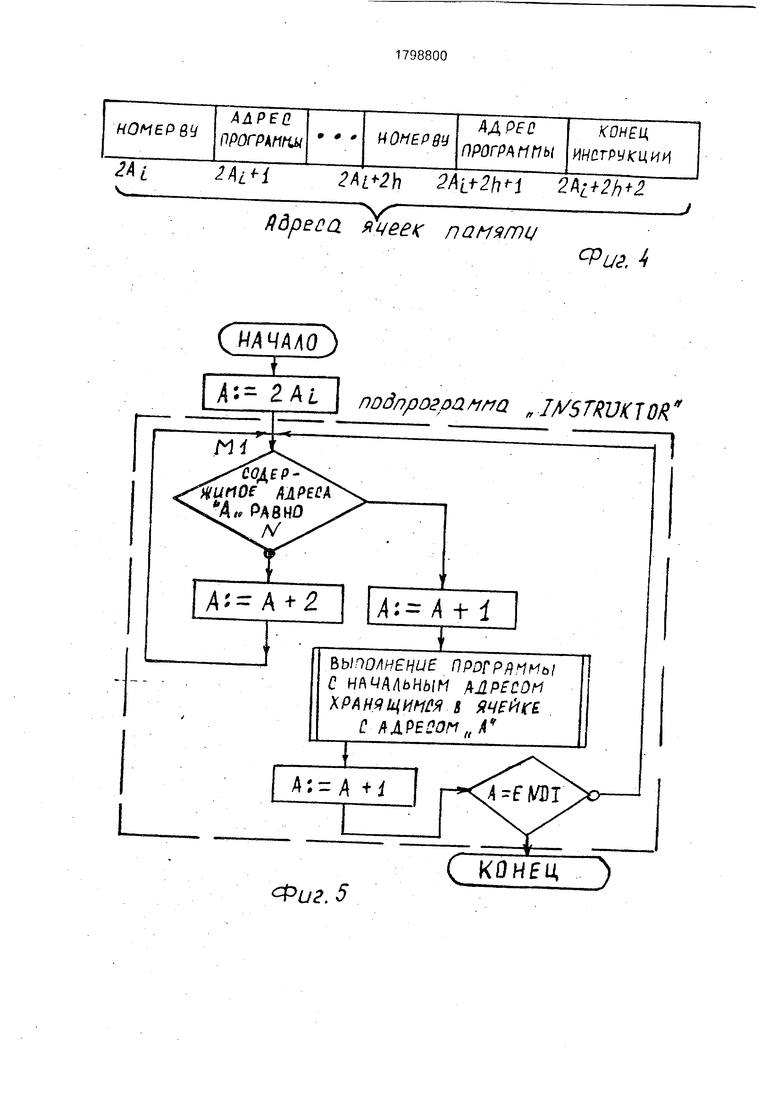

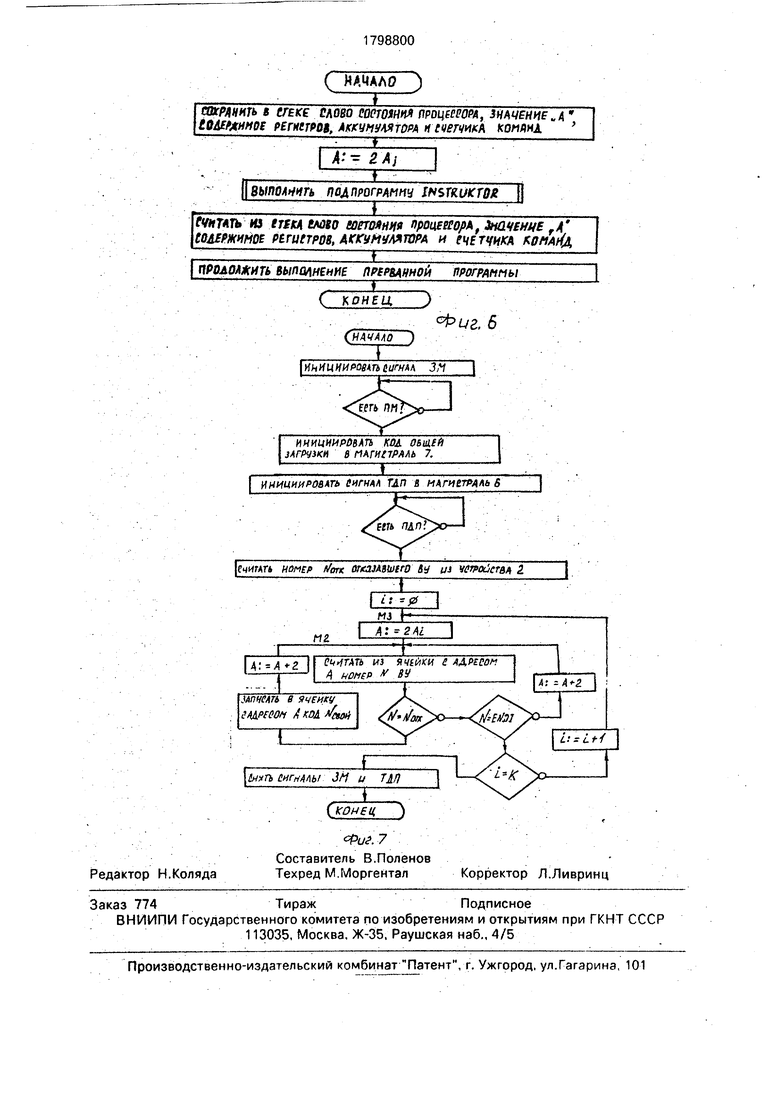

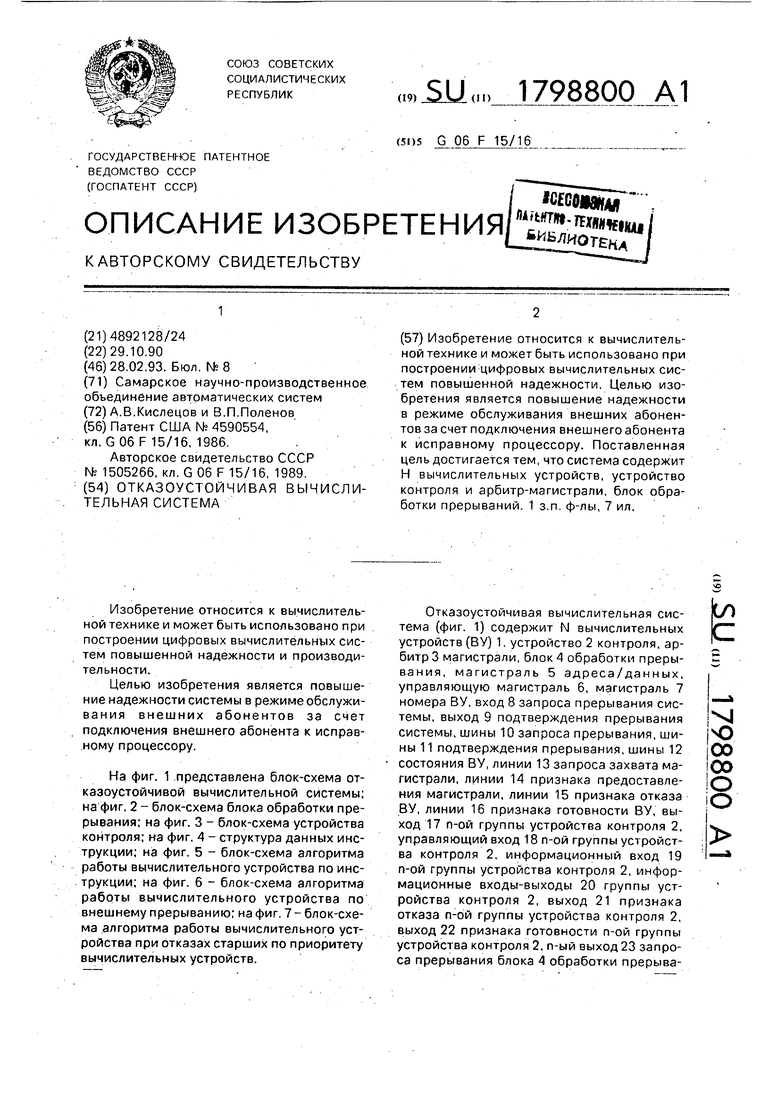

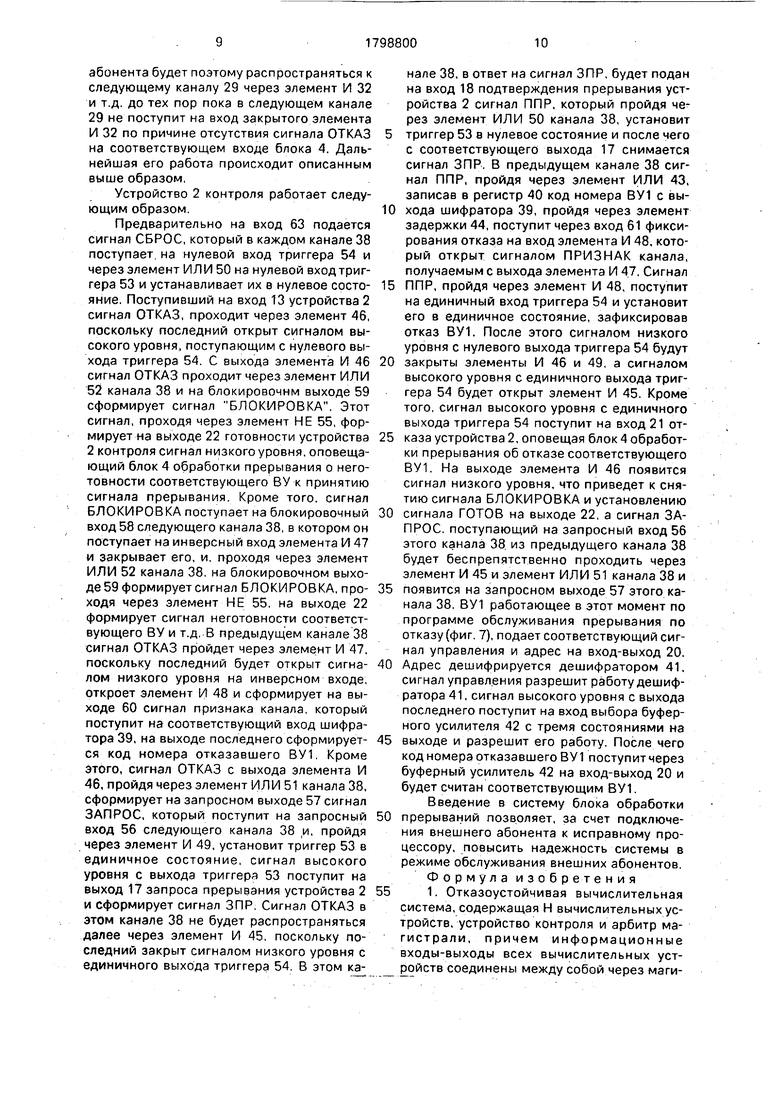

На фиг. 1 .представлена блок-схема отказоустойчивой вычислительной системы; на фиг. 2 - блок-схема блока обработки прерывания; на фиг. 3 - блок-схема устройства контроля; на фиг. 4 - структура данных инструкции; на фиг. 5 - блок-схема алгоритма работы вычислительного устройства по инструкции; на фиг. 6 - блок-схема алгоритма работы вычислительного устройства по внешнему прерыванию; на фиг. 7- блок-схема алгоритма работы вычислительного устройства при отказах старших по приоритету вычислительных устройств.

Отказоустойчивая вычислительная система (фиг. 1) содержит N вычислительных устройств(ВУ) 1,устройство 2 контроля, арбитр 3 магистрали, блок 4 обработки преры- вания, магистраль 5 адреса/данных, управляющую магистраль 6, магистраль 7 номера ВУ, вход 8 запроса прерывания системы, выход 9 подтверждения прерывания системы, шины 10 запроса прерывания, шины 11 подтверждения прерывания, шины 12 состояния ВУ, линии 13 запроса захвата магистрали, линии 14 признака предоставления магистрали, линии 15 признака отказа ВУ, линии 16 признака готовности ВУ, выход 17 n-ой группы устройства контроля 2, управляющий вход 18 n-ой группы устройства контроля 2, информационный вход 19 n-ой группы устройства контроля 2, информационные входы-выходы 20 группы устройства контроля 2, выход 21 признака отказа n-ой группы устройства контроля 2, выход 22 признака готовности n-ой группы устройства контроля 2, n-ый выход 23 запроса прерывания блока 4 обработки прерыва Ч чО 00 00

0 (О

ния, n-ый вход 24 подтверждения прерывания блока 4 обработки прерывания, п-ый вход 25 признака отказа блока 4 обработки прерывания, n-ый вход 26 признака готовности блока 4 обработки прерывания, вход 27 запроса прерывания блока 4 обработки прерывания, выход 28 подтверждения прерывания блока 4 обработки прерывания.

Блок 4 обработки прерывания (фиг. 2) содержит Кг каналов 29 и элемент ИЛИ 30, а в каждом канале 29 - элементы И 31, 32, 33, вход 34 запроса прерывания, вход 35 признака готовности, выход 36 запроса прерывания, выход 37 подтверждения прерывания.

Устройство 2 контроля (фиг. 3) содержит N каналов 38, шифратор 39, регистр 40, дешифратор 41, буферный усилитель 42 с тремя состояниями на выходе, элемент ИЛИ 43, элемент задержки 44, а в каждом канале 38 - элементы И 45, 46, 47, 48, 49, элементы ИЛИ 50,51, 52, триггер 53 прерывания, триггер 54 фиксирования отказа, элемент НЕ 55, запросный вход 56, запросный выход 57, блокировочный вход 58, блокировочный выход 59, выход 60 признака канала, вход 61 фиксирования отказа, вход 62 сброса канала, вход 63 сброса устройства 2 контроля.

Система работает следующим образом.

Блок памяти каждого ВУ 1 содержит программу ввода-вывода. ВУ 1 после сигна- ла начальной установки переходит на выполнение программы ввода-вывода. По этой программе ВУ 1 инициирует сигнал захвата магистрали (ЗМ) в линию 13 запроса захвата магистрали, Арбитр 3. магистрали разреша- ет доступ в магистраль, выдачей сигнала предоставления магистрали (ПМ) в линию 14 признака предоставления магистрали, только ВУ 1 с наивысшим приоритетом, Приоритет ВУ1 задается его подключением к соответствующим входам и выходам арбитра 3 магистрали.

Получив сигнал ПМ с линии 14, ВУ1 производит загрузку в память каждого ВУ1, в том числе ив свою память, программы ра- боты системы и инструкции работы по программе. Во время загрузки программ и инструкций остальные ВУ1 находятся в режиме ожидания.

Перед вводом программ ВУ 1, осуществ- ляющее ввод программ, инициирует выдачу кода номера ВУ1 в магистраль 7 номера ВУ (при загрузке памяти одного из ВУ1) или кода общей загрузки (при загрузке, параллельно памяти всех ВУ 1). После чего ВУ1 инициирует выдачу сигнала требования доступа в память (ТДП) в управляющую маги- .страль 6. После получения сигнала ТДП по коду с магистрали 7 номера ВУ соответствующее ВУ1 (при загрузке памяти одного из

ВУ1) или все остальные ВУ1 (при параллельной загрузке памяти всех (ВУ1), инициирует выдачу сигнала предоставления доступа в память (ПДП) в управляющую магистраль б. ВУ 1, получив сигнал ПДП инициирует выдачу в магистраль 5 адресов и данных, а в магистраль 6 сигналов управления для загрузки в память выбранных ВУ1 соответствующих программ и инструкции.

По окончании загрузки программ и инструкции, загружающее ВУ1 снимает сигнал ТДП и код с магистрали 7, и выдает каждому другому ВУ1 по магистрали 6 команду работы с инструкцией. Получив эту команду ВУ1 переходят на выполнение своей программы в соответствии с инструкцией. Загружающее ВУ1 также переходит на выполнение своих программ в соответствии с инструкцией.

Инструкция включает начальный адрес каждой программы и соответствующий каждому адресу номер ВУ1, которое должно выполнять эту программу. Структура данных инструкции, хранящейся в последовательных ячейках памяти представлена на фиг. 4.

Младший, например, четный номер инструкции

Ap 2Ai + 2h,

где AJ - константа 1-й инструкции, например 1 0;

h 0, 1,2, ...

Содержит номер ВУ1, а следующий нечетный адрес

Aq (2Aj + 1) +2h

содержит начальный адрес программы, которую должно выполнять ВУ1, номер которого хранится в Aq.

Блок-схема алгоритма работы каждого ВУ 1 в соответствии с инструкцией представлена на фиг. 5.

Предварительно переменной А присваивается четное число 2А|. Затем проверяется содержимое ячейки памяти с адресом А. Если содержимое ячейки А не равно номеру ВУ, которое выполняет алгоритм (фиг. 5), то переменной А присваивается значение А+2 и снова проверяется содержимое ячейки с адресом А. Если на некотором шаге просмотра инструкции окажется, что содержи- ,мое ячейки А равно N, то переменной А присваивается значение А+1 и ВУ1 переходит на выполнение программы, начальный адрес которой хранится в ячейках с адресом А.

В частности, эта программа может быть программой самотестирования, а инструкция может предусматривать, чтобы часть

ВУ1 находилась в горячем резерве, выполняя только программу самотестирования.

После выполнения программы переменной А присваивается значение А+1 и проверяется равна ли переменная А числу ENDI, которое фиксирует конец инструкции. Если А ENDI, то алгоритм выполняется повторно, начиная с точки Ml. Если А ENDI, то выполнение алгоритма завершается, либо повторяется сначала.

При наличии сигнала прерывания на входе 8 системы, блок 4 обработки прерывания выставляет на шину 10 запроса прерывания сигнал запроса прерывания (ЗПР) для наиболее старшего по приоритету исп- равного ВУ1. ВУ1 получив сигнал ЗПР переходит на программу обслуживания прерывания, блок-схема алгоритма которой представлена на фиг. 6 и выставляет в шину 11 сигнал подтверждения прерывания (ППР). В ответ на этот сигнал блок 4 обработки прерывания на выход 9 системы выставляет одноименный сигнал ППР. Внешнее устройство, выставившее на вход 8 системы сигнал ЗПР, снимает последний. Блок 4 обработки прерываний снимает с шины 10 свой сигнал ЗПР, а ВУ1, получивший сигнал снимает с шины 11 свой сигнал

ППР.;

В соответствии с алгоритмом (фиг. 6) программы обслуживания прерывания ВУ1 сохраняет в стеке текущее слово состояния процессора ВУ1, текущее значение переменной А, содержимое регистров, аккумулятора и счетчика команд процессора ВУ1.

После чего ВУ1 переходит к выполнению программ по одной из инструкций, предусмотренных программой обслуживания. В этом случае работа ВУ1 может происходить описанным выше образом в соответст- вии с алгоритмом, предусмотренным на фиг. 5.

Для экономии обьема памяти путем сокращения количества программ, соответствующих алгоритму (фиг. 5) работы по инструкции, программой обслуживания прерывания (фиг. 6) переменной А присваивается значение 2Aj, где Aj - константа адреса начала j-й инструкции, например 1.

Затем работа ВУ1, обслуживающего прерывание, выполняется по алгоритму ко- дирограммы INSTRUKTOR (фиг. 5), начиная с точки М. По завершении выполнения этого алгоритма, ВУ1 возвращается на программу обслуживания прерывания, восста- навливает предыдущее состояние, соответствующее выполнению прерванной программы, считывая из стекла слово состояния процессора, предыдущее значение переменной А, содержимое регистров,

аккумулятора и счетчика команд, присваивает переменной А предыдущее значение и продолжает выполнять прерванную программу с адреса считанного из стекла и записанного в счетчик команд процессора ВУ 1.

В случае отказа одного из ВУ1, последнее выставляет в шину 12 состояния ВУ сигнал ОТКАЗ. По этому сигналу устройство 2 контроля выставляет в шину 10 запроса прерывания соседнего младшего по приоритету и исправного ВУ1 сигнал ЗПР. Получив сигнал ЗПР, это ВУ1 переходит на программу обслуживания прерывания по отказу, блок-схема алгоритма которого представлена на фиг. 7, и выставляет сигнал ПП Р в свою шину 11 подтверждения прерывания. Получив сигнал ППР. устройство 2 контроля фиксирует сигнал ОТКАЗ отказавшего ВУ.1 и отключают его сигналы от своих входов.

По программе обслуживания прерывания по отказу (фиг. 7) ВУ1 инициирует выдачу сигнала ЗМ в линию 13. После чего ВУ1 проверяет наличие сигнала ПМ на линии 14, который должен выставлять арбитр 3 магистрали в ответ на сигналы ЗМ только ВУ 1 с наивысшим приоритетом. При наличии сигнала ПМ, ВУ1 инициирует выдачу в магистраль 7 кода общей загрузки и сигнала ТДП в управляющую магистраль 6. При наличии сигнала ПДП в управляющей магистрали 6, который, выставляется при готовности. ВУ1 к режиму доступа в память, ВУ1 считывает из. устройства 2 контроля номер отказавшего ВУ. Затем ВУ1 осуществляет изменение всех инструкций, повторяя выполнение программы изменения инструкцией, перебирая по порядку следования номера инструкций 1 01, 2 ... К, где К - номер последней инструкции.

Для этого переменной i присваивается значение р. а переменной А значение 2А|,. являющейся адресом i-й инструкции, в четных адресах ячеек памяти которой хранятся коды номера ВУ1, выполняющего программу, начальный адрес которой хранится в нечетных адресах ячеек памяти.

ВУ1, работающий по программе обслуживания прерывания по отказу, считывает содержимое N ячейки 2Aj и сравнивает его с номером NOT отказавшего ВУ. Если N . N0TK, то ВУ1. работающий по программе обслуживания прерывания по отказу, в ячейку, адрес которой соответствует текущему значению А, записывает код своего номера. Затем присваивает переменной А значение А+2 и повторяет выполнение алгоритма с точки М2. Если N. М0тк. то проверяется равно ли содержимое ячейки fsfe коду конца инструкции ENDf. Если N ENDI, то

.переменной А присваивается значение А+2 и алгоритм повторяется начиная с точки М2. Если N ENDI, то номер инструкции i сравнивается с номером К последней инструкции.

При i з К, переменной i присваивается значение 1+1 и алгоритм повторяется с точки МЗ, При i К ВУ1 выходит из режима доступа в память, снимая сигналы ЗМ и ТДП. После чего ВУ1 выходит из режима прерывания, и все исправные ВУ продолжают работу в соответствии с измененной инструкцией.

Таким образом, после отказа ВУ1, его программу будет выполнять соседнее исправное младшее по приоритету ВУ1.

Кроме того, при отказе ВУ1 с соответствующего выхода 21 признака отказа устройства 2 контроля через линию 15 признака отказа поступает на вход 25 признака отказа блока 4 обработки прерывания сигнал отказа, который блокирует прохождение сигналов прерывания с входа 28 через блок 4 на выходы 23 последнего и в шину 10 запроса прерывания отказавшего ВУ. Этот же сигнал отказа разрешает прохождение сигналов прерывания с входа 8 в шину 10 запроса прерывания исправного младшего по приоритету ВУ1.

Таким образом, после отказа ВУ1, на сигналы прерывания будет отвечать соседнее исправное младшее по приоритету ВУ1.

Если ВУ1 не работают в режиме прерывания, то с выходов 22 признака готовности устройства 2 контроля через линии 16 признака готовности на входы 26 признака готовности блока 4 обработки прерываний поступают разрешающие сигналы, которые обеспечивают прохождение сигналов прерывания с входа 8 через блок 4 в шину 10 запроса прерывания.

Если один из ВУ1 работает в режиме прерывания по отказу, то сигнал готовности снимается со входов 26 блока 4 и препятствует прохождению сигналов прерывания с входа 8 на соответствующее ВУ1.

В случае отказа еще одного ВУ1 работа системы будет происходить описанным выше образом. И так до тех пор, пока не откажут все ВУ1 системы.

Блок 4 обработки прерывания работает следующим образом.

В том случае, когда все ВУ1 исправны, на вход 25 признака отказа каждого канала 29 подается сигнал низкого уровня, который открывает элементы 1/131 и 33 и закрывает элемент И 32. Если при этом ВУ1 и устройство 2 контроля не работают в режиме обслуживания ВУ 1 по отказу, то на вход 26 готовности каждого канала 29 подается сигнал высокого уровня, который открывает элементы И 31 и 33. Сигнал ЗПР от абонента подается на вход 27, через вход 34 запроса прерывания первого канала 29 поступает на

входы элементов И 31...33 и открывает их. На выходе элемента И 31 появится сигнал высокого уровня, который на выходе 23 запроса прерывания сформируют сигнал ЗПР для соответствующего ВУ1. В ответ на сиг0 нал ЗПР ВУ1 сформирует на входе 24 подтверждения прерывания сигнал ППР, который пройдет через элемент И 33 и с выхода 37. подтверждения прерывания соответствующего канала 29 через элемент

5 ИЛИ 30 поступит на выход 28 подтверждения прерывания блока 4. Получив этот сигнал, абонент перейдет на режим обмена информацией с системой. Сигнал ЗПР со входа 27 не будет распространяться через

0 все каналы 29, поскольку элемент И 32 первого канала 29 закрыт сигналом низкого уровня со входа 25.

Если ВУ1 отказывает, то устройство 2 контроля сначала снимает сигнал готовно5 сти со входа 26 блока 4 обработки прерывания во всех каналах 29 соответствующих отказавшему ВУ1 и всем ВУ1 младшим по приоритету. В этом случае элементы И 33 и 31 этих каналов 29 будут закрыты, а на тре0 бования прерывания от абонента смогут реагировать только ВУТ старшего по приоритету по сравнению с отказавшим, а именно, наиболее старшее по приоритету исправное ВУ1.

5 После выполнения программы обслуживания отказа, на вход 25 блока 4 обработки прерывания подается сигнал ОТКАЗ высокого уровня, который закрывает элементы И 31 и 33, предотвращая формированиесигна0 лов ЗПР и ППР соответствующих отказавшему ВУ1 и открывает элемент И 32, разрешая распространение сигнала ЗПР от абонента по каналам 29 в направлении от младшего к старшему. В этом случае сигнал

5 ЗПР пройдет через элемент И 32 и с выхода 36 запроса прерывания канала 29 поступит на вход 34 запроса прерывания следующего канала 29. В этом канале 29 сигнал ЗПР откроет элементы И 31...33 и, если соответ0 ствующий этому каналу 29 ВУ1 исправно и присутствует сигнал ГОТОВ на входе 26 блока 4, то на выходе 23 блока 4 сформируется сигнал ЗПР, в ответ на который ВУ1 на входе 24 сформирует сигнал ППР, который прой5 дет через элементы И 33, ИЛИ 30 на выход 28 блока 4. Если ВУ1 соответствующее текущему каналу 29 отказало, то элемент И 32 этого канала 29 будет открыт сигналом ОТКАЗ со входа 25 блока 4. а элементы И-31 и 33 закрыты этим сигналом. Сигнал ЗПР от

абонента будет поэтому распространяться к следующему каналу 29 через элемент И 32 и т.д. до тех пор пока в следующем канале 29 не поступит на вход закрытого элемента И 32 по причине отсутствия сигнала ОТКАЗ на соответствующем входе блока 4. Дальнейшая его работа происходит описанным выше образом,

Устройство 2 контроля работает следующим образом.

Предварительно на вход 63 подается сигнал СБРОС, который в каждом канале 38 поступает, на нулевой вход триггера 54 и через элемент ИЛИ 50 на нулевой вход триггера 53 и устанавливает их в нулевое состояние. Поступивший на вход 13 устройства 2 сигнал ОТКАЗ, проходит через элемент 46, поскольку последний открыт сигналом высокого уровня, поступающим с нулевого выхода триггера 54. С выхода элемента И 46 сигнал ОТКАЗ проходит через элемент ИЛИ 52 канала 38 и на блокировочнм выходе 59 сформирует сигнал БЛОКИРОВКА. Этот сигнал, проходя через элемент НЕ 55, формирует на выходе 22 готовности устройства 2 контроля сигнал низкого уровня, оповещающий блок 4 обработки прерывания о неготовности соответствующего ВУ к принятию сигнала прерывания. Кроме того, сигнал БЛОКИРОВКА поступает на блокировочный вход 58 следующего канала 38, в котором он поступает на инверсный вход элемента И 47 и закрывает его, и, проходя через элемент ИЛИ 52 канала 38. на блокировочном выходе 59 формирует сигнал БЛОКИРОВКА, проходя через элемент НЕ 55. на выходе 22 формирует сигнал неготовности соответствующего ВУ и т.д. В предыдущем канале 38 сигнал ОТКАЗ пройдет через элемент И 47, поскольку последний будет открыт сигналом низкого уровня на инверсном входе, откроет элемент И 48 и сформирует на выходе 60 сигнал признака канала, который поступит на соответствующий вход шифратора 39, на выходе последнего сформируется код номера отказавшего ВУ1. Кроме этого, сигнал ОТКАЗ с выхода элемента И 46, пройдя через элемент ИЛИ 51 канала 38, сформирует на запросном выходе 57 сигнал ЗАПРОС, который поступит на запросный вход 56 следующего канала 38 и, пройдя через элемент И 49, установит триггер 53 в единичное состояние, сигнал высокого уровня с выхода триггера 53 поступит на выход 17 запроса прерывания устройства 2 и сформирует сигнал ЗПР. Сигнал ОТКАЗ в этом канале 38 не будет распространяться далее через элемент И 45, поскольку последний закрыт сигналом низкого уровня с единичного выхода триггера 54. В этом канале 38, в ответ на сигнал ЗПР, будет подан на вход 18 подтверждения прерывания устройства 2 сигнал ППР, который пройдя через элемент ИЛИ 50 канала 38, установит

триггер 53 в нулевое состояние и после чего с соответствующего выхода 17 снимается сигнал ЗПР. В предыдущем канале 38 сигнал ППР, пройдя через элемент ИЛИ 43, записав в регистр 40 код номера ВУ1 с вы0 хода шифратора 39, пройдя через элемент задержки 44, поступит через вход 61 фиксирования отказа на вход элемента И 48, который открыт сигналом ПРИЗНАК канала, получаемым с выхода элемента И 47. Сигнал

5 ППР, пройдя через элемент И 48, поступит на единичный вход триггера 54 и установит его в единичное состояние, зафиксировав отказ ВУ1. После этого сигналом низкого уровня с нулевого выхода триггера 54 будут

0 закрыты элементы И 46 и 49. а сигналом высокого уровня с единичного выхода триггера 54 будет открыт элемент И 45. Кроме того, сигнал высокого уровня с единичного выхода триггера 54 поступит на вход 21 от5 каза устройства 2, оповещая блок 4 обработки прерывания об отказе соответствующего ВУ1. На выходе элемента И 46 появится сигнал низкого уровня, что приведет к снятию сигнала БЛОКИРОВКА и установлению

0 сигнала ГОТОВ на выходе 22, а сигнал ЗАПРОС, поступающий на запросный вход 56 этого канала 38. из предыдущего канала 38 будет беспрепятственно проходить через элемент И 45 и элемент ИЛИ 51 канала 38 и

5 появится на запросном выходе 57 этого канала 38. ВУ1 работающее в этот момент по программе обслуживания прерывания по отказу (фиг. 7), подает соответствующий сигнал управления и адрес на вход-выход 20.

0 Адрес дешифрируется дешифратором 41, сигнал управления разрешит работу дешифратора 41, сигнал высокого уровня с выхода последнего поступит на вход выбора буферного усилителя 42 с тремя состояниями на

5 выходе и разрешит его работу. После чего код номера отказавшего ВУ1 поступит через буферный усилитель 42 на вход-выход 20 и будет считан соответствующим ВУ1.

Введение в систему блока обработки

0 прерываний позволяет, за счет подключения внешнего абонента к исправному процессору, повысить надежность системы в режиме обслуживания внешних абонентов. Формула изобретения

5 1. Отказоустойчивая вычислительная система, содержащая Н вычислительных устройств, устройство контроля и арбитр ма- гистрали, причем информационные входы-выходы всех вычислительных устройств соединены между собой через магистраль адреса/данных и подключены к информационным входам группы устройства контроля, управляющие входы-выходы всех вычислительных устройств соединены между собой через управляющую магистраль, входы-выходы номера вычислительного устройства всех вычислительных устройств соединены между собой через магистраль номера вычислительного устройства, выходы запроса прерывания и запроса захвата магистрали а-ro вычислительного устройства (а 1, .... Н) подключены соответственно к первому и второму управляющему входам а-й группы устройства контроля, первый и второй выходы а-й группы которого подклю- чены соответственно к входам подтверждения прерывания и признака предоставления магистрали а-го вычислительного устройства, третий выход а-й группы устройства контроля подключен к а-му входу запроса магистрали арбитра магистрали, а-й выход разрешения захвата магистрали которо го подключен к третьему управляющему входу а-й группы устройства контроля, отличающаяся тем, что, с целью повышения надежности в режиме обслуживания внешних абонентов за счет подключения внешнего абонента к исправному процессору, она содержит блок обработки прерываний, причем выход состояния а-го вычислительного устройства подключен к информационному входу а-й группы устройства контроля, а-й выход запроса прерывания, а-й вход подтверждения прерывания, а-й вход признака отказа и а-й вход призна- ка готовности блока обработки прерываний подключены соответственно к третьему управляющему входу, четвертому, пятому и

шестому выходам а-й группы устройства контроля, вход запроса прерывания системы подключен к входу запроса прерывания блока обработки прерывания, выход подтверждения прерывания которого подключен к выходу подтверждения прерывания системы.

2. Система поп, 1,отличающаяся тем, что блок обработки прерываний содержит первую, вторую и третью группы элементов И и элемент ИЛИ, причем а-й вход подтверждения прерывания блока подключен к первому входу а-го элемента Н первой группы, а-й вход признака отказа блока подключен к второму входу а-го элемента Н первой группы, к первому входу а-го элемента И второй группы и к первому входу а-го элемента И третьей группы, а-й вход признака готовности блока подключен к третьему входу а-го элемента И первой группы и к второму входу а-го элемента И второй группы, вход запроса прерывания блока подключен к третьему входу первого элемента И второй группы, к четвертому входу первого элемента И первой группы и к второму входу первого элемента И третьей группы, выход а-го элемента И первой группы подключен к а:му входу элемента ИЛИ, выход которого подключен к выходу подтверждения прерывания блока, а-й выход запроса прерывания которого подключен к выходу а-го элемента И второй группы, выход К-го элемента И третьей группы (К - 1, ..,, Н-1) подключен к четвертому входу (К+1)- го элемента И первой группы, к второму входу (К+1)-го элемента И третьей группы и к третьему входу (К-Н)-го элемента И второй группы.

. 2

Риг. 3

Фиг.-4

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство для сопряжения абонентов с каналом связи | 1987 |

|

SU1432537A1 |

| Устройство для связи микропроцессора с внешними устройствами | 1986 |

|

SU1372330A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Система сбора и обработки информации | 1987 |

|

SU1424024A1 |

| Устройство для контроля и перезапуска ЭВМ | 1987 |

|

SU1464162A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1725223A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство для сопряжения микропроцессорной системы с внешними устройствами с контролем | 1984 |

|

SU1242956A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении:цифровых вычислительных систем повышенной надежности. Целью изобретения является повышение надежности в режиме обслуживания внешних абонентов за счет подключения внешнего абонента к исправному процессору. Поставленная цель достигается тем, что система содержит Н вычислительных устройств, устройство контроля и арбитр-магистрали, блок обработки прерываний. 1 з.п. ф-лы, 7 ил.

С НАЧАЛО)

Л: 2AL

ВЫПОЛНЕНЫ ПРОГРАММЫ С НАЧАЛЬНЫМ

ХРАНЯ ц имея s ячейге

С-ЛАРЕМ

Фиг. 5

подпрограмма „JA/STRVKJ OR

С КОНЕЦ

( НАЧАЛО) X

СОХРАНИТЬ в стеке слово СОРТОМ процеееорл, ЗНАЧЕНИЕ „А lOAEMHMOf РЕГИСТРЫ, АККУМУЛЯТОРА HtoerwxA коиднд

Г

I А: г Л;

|| выполнить пал ПРОГРАММ JNS m t/r ток Ц

I

I

fwrwb из шд елмо ейетояння процеееорл Значение .к одержчноЕ PtruiTpos, АгеамаляторА и (ЧЕТЧИКА КОМАНД

--- f . / . ; ; -

ПРОДОЛЖИТЬ выполнение пгнщнной ПРОГРАММЫ

С КОНЕЦ J

(ЙМАЛО 1

Г

.

HbHUtfHPQgATi ji/W4A З М

ИНИЦИИРОВАТЬ Ш OBuiffl ЗЛГРУЗКН В ПЬГИПРААЬ 7.

I ИНИЦИИРОВАТЬ СИГНАЛ тлп в МАГИСТРАЛЬ s

I--------------.-----i--.----г----i------------:-------

|СцигАГ4 номер f/огк oraJABttiiro № us чотробстм 2.

--- ----- t --------

I

(JCOUEH J

Редактор Н.Коляда

. 7

Составитель В.Поленов Техред М.Моргентал

., 6

Корректор Л.Ливринц

| Патент США № 4590554, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР М; 1505266, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-02-28—Публикация

1990-10-29—Подача