Изобретение относится к вычисли- тельной технике, в частности к устройствам управления обменом информации устройством приоритетного обслу- живания.и может быть использовано при разработке вычислительных устройств.

: Целью изобретения является расширение области применения устройства за счет возможности работы как в режиме относительного, так и абсолютно - го приоритетом и циклического обслуживания запросов,

.

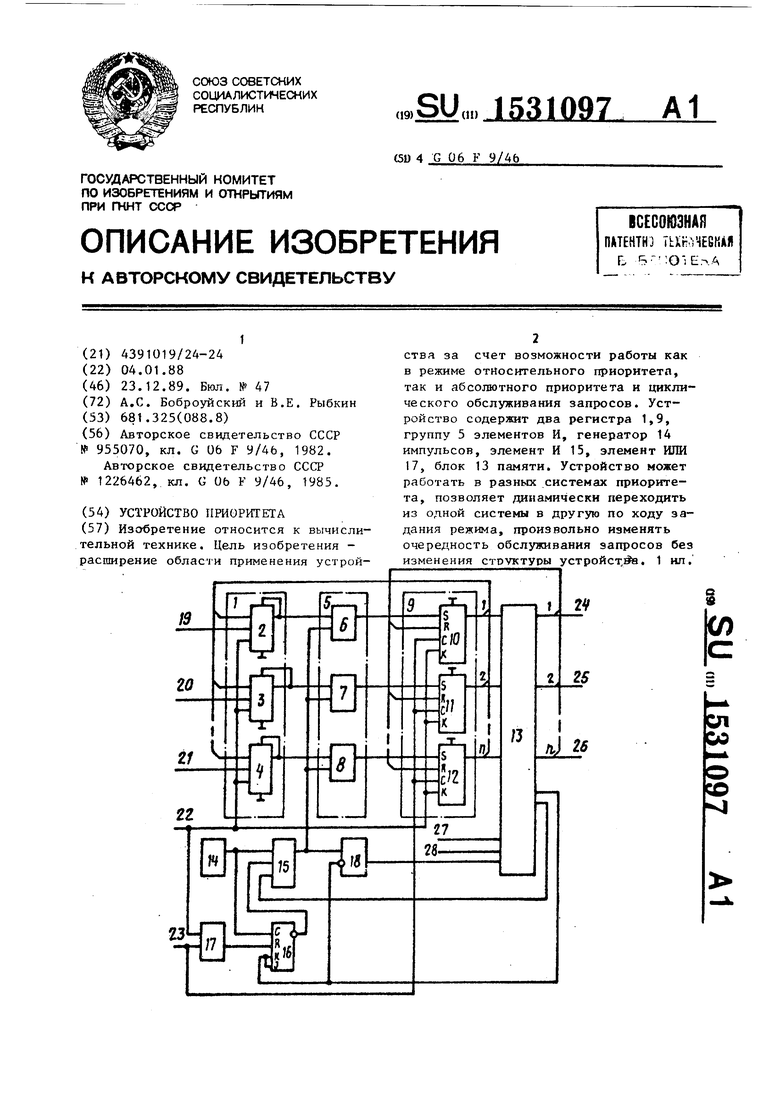

На чертеже приведена структурная схема устройства приоритета.

Устройство содержит регистр 1, триггеры 2-4 регистра 1, группу элементов И 5, элементы И 6-8 группы 5, регистр 9, триггеры 10-12 регистра 9, блок 13 памяти, генератор 14 импульсов, элемент И 15, триггер 16, элемент ИЛИ 17, элемент И 18, запросные входы 19-21 устройства, вход 22 на- чальной установки устройства, вход 23 конца обслуживания устройства, выходы 24-26 устройства, входы 27 и 28 режима устройства.

Устройство может работать в дис- 1ц плине обслуживания с относительными приоритетами, абсолютными приоритетами, а также в режиме циклической обработки запросов.

Рассмотрим работу устройства в режиме обслуживания запросов с абсолютным приоритетом.

После прихода на вход 22 устройства импульса начальной установки он попадает на регистры 1 и 9, а также че- рез элемент ИЛИ 17 на триггер 16, после чего регистры 1 и 9 и триггер 16 обнуляются, и устройство готово к pq,- боте.

Допустим, что наивысший приоритет имеет вход триггера 2, самый низкий - вход триггера 4, При поступлении запросов по входам 19-21 они запоминаются в регистре 1, т.е. триггеры 2-4 этого регистра переходят в единичное состояние.Очередным тактовым импульсом от генератора 14 запросы, поступившие в регистр 1, переписываются через группу 5 элементов И в регистр 9. По этому коду, находящемуся в регистре 9, и коду, определяющему режим абсолютного приоритета на входах 27- 28, из блока 13 памяти выбирается ячейка, содержащая единицу в том раз

0

5

5

5

ряде, который соответствует яапросу с наиболее высоким приоритетом из данной комбинации запросов, после чего на соответствующем выходе устройства появляется потенциал высокого уровня. Например, если поступил запрос по ВХОДУ 20, то в блоке 13 памяти выбирается ячейка, содержащая единицу во втором разряде, и на выходе 25 устройства появится потенциал единичного уровня. Триггер 16 всегда находится в нулевом состоянии, так как на его информационный вход с первого управляющего выхода блока 13 памяти поступает сигнал единичного уровня, и каждый тактовый импульс с генератора 14, поступающий на синхронизирующий вход триггера 16, подтверждает его нулевое состояние, в.-которое и переведен после начальной устаногки. Таким образом, каждьй импульс с генератора 14 проходит через элемент И 15 на группу 5 элементов И, так как на третий вход элемента И 15 поступает сигнал единичного уровня с второго управляющего выхода блока 13 памяти. Тем СШ-1ЫМ каж,чый тактовый импульс с генератора 14 переписьюает вновь поступившие запросы из регистра 1 в регистр 9. Допустим ,1 что после начала обработки запроса, поступившего по входу 20, приходит запрос по входу 19, тогда с приходом тактового импульса с генератора 14 он переписывается в регистр 9. В блоке 13 памяти выбирается ячейка, содержащая единицу только в первом разряде, поэтому на выходус 25 устройства устанавливается потенциал нулевого уровня, а на выходе 24 - единичного уровня. Тем самым прервет- ря обслуживание запроса по второму каналу и начнется обслуживание по первому каналу. После прихода импульса конца обслуживания обнуляется только тот триггер регистра 9 (триггер 10), который соответствует каналу запроса, по которому происходило и закончено обслуживание. После обнуления одного из (триггеров -10-12 регистра 9 происходит обнудение соответствующего триггера регистра 1 (триггер 2), В блоке 13 памяти опять выбирается ячейка с единицей во втором разряде . Сигнал на выходе 24 становится нулевым, а на выходе 25 - единичным, тем самым устройство возвращается к прерванному обслуживанию запроса.

В случае работы устройства в дисциплине относительного приоритета раница закдючается только в том, что после поступления первого импульса опроса от генератора 14 триггер 16 устанавливается в единичное состояние Для этого на его информационный вход соединенньш с первым управляющим выходом блока памяти, поступает нуль. Таким образом, элемент И 15 закрыт до тех пор, пока не придет импульс конца обслуживания на вход 23 устройства, а триггер 16 не встанет в нулевое состояние. Следовательно, обспу- живание запроса, которое в настоящий момент производится, не прервется, и если придет более приоритетньм запрос, его обслуживание начнется только после конца обслуживания первого по времени запроса. Причем на время,равное длительности импульса опроса с генератора 14, блок 13 памяти через элемент И 18 переводится в область адресов, по которым на труппе выходов блока памяти формируются сигналы нулевого уровня не зависимо от состояния группы адресных входов, что дает возможность избежать переходных процессов на выходах устройства приоритета во время переписи запросов из регистра 1 в регистр 9.

В случае работы в режиме циклического о бслуживания запросов любая единица на выходе регистра 9 переводит блок памяти в состояние, когда на втором управляющем выходе нуль, который закрывает элемент И 15, т.е. импульсы записи не попадают на регистр 9 до тех пор, пока все заявки, записанные в регис1ре 9 ранее, не будут обслужены на группе входов памяти, не появятся нулевые сигналы, вследствие чего в блоке памяти выберется соот- ветствующая. ячейка и на втором управляющем выходе блока памяти установится единичный сигнал.

После этого цикл обслуживания может повториться.

Формула изобретения

Устройство приоритета, содержащее два регистра, группу элементов И, первый элемент И, генератор импульсов, элемент ИЛИ, причем запросные входы устройства соединены с вхо

6

1 1 It

10

15

20

25

дами установки в 1 nepBOJ o регистра, выходы элементов И группы соединены с входами установки в 1 второго регистра, выход каждого разряда второго регистра соединен с тактовым входом одноименного разряда первого регистра, вход нача.пьной установки и вход конца обслуживания устройства соединены с входами элемента ИЛИ, вход начальной установки устройства соединен с входами сброса первого и второго регистров, вход конца обслуживания устройства соединен с тактовым входом второго регистра, о т л и чающееся тем, что, с целью расширения области применения за счет возможности работы как в режиме относительного, так и абсолютьюго приоритета и циклического обслуживагшя запросов, устройст1;о содержит второй элемент И, триггер и блок памя1 И, группа вьгг.идов которого являеч ся группой выходов устройства и соедянена с первой группой информациониь:х входом второго регистра, вторая группа инфор-- мационных входов которого соединена с потенциалом логического нуля устройства, пероый и второй входы режима устройства соединены соответсч венно с первым и вторым ад1) входами блока памяти, третий адресный вход и группа адресных входов коч орого сое- / 1нены соответстве но с выходом первого элемента И и с выходами B i oporo регистра, первая группа информационных входов первого регистра соединена с входом логического нуля устройства, вход сброса триггера соединен с ььгхо- дом элемента ИЛИ, первый и второй информационные входы триггера соединены соответственно с инверсным входом первого элемента И и с первым выходом блока памяти, второй выход которого

дп соединен с первым входом второго элемента И, второй .и третий входы которого соединены соответственно с инверс- ньи выходом триггера и с выходом генератора импульсов и с тактовым дом триггера, выход второго элемента И соединен с прямым входом первого элемента И и с первыми входами элементов И группы, второй вход каждого из которых соединен с выходом одноименного разряда первого регистра и с вторым информационным входом этого разряда.

30

35

40

55

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования сигнала прерывания | 1987 |

|

SU1432522A1 |

| Устройство для приоритетного обслуживания запросов абонентов | 1987 |

|

SU1495792A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Мультимикропрограммное устройство управления | 1982 |

|

SU1043651A1 |

| Приоритетное устройство (его варианты) | 1984 |

|

SU1211729A1 |

| Устройство для сопряжения ЭВМ с синхронным каналом передачи данных | 1986 |

|

SU1424023A1 |

| Устройство приоритета | 1986 |

|

SU1365084A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для формирования сигнала прерывания | 1984 |

|

SU1241242A1 |

| Устройство для управления обменом информацией | 1990 |

|

SU1783525A1 |

Изобретение относится к вычислительной технике. Цель изобретения - расширение области применения устройства за счет возможности работы как в режиме относительного приоритета, так и абсолютного приоритета и циклического обслуживания запросов. Устройство содержит два регистра 1,9, группу 5 элементов И, генератор импульсов 14, элемент И 15, элемент ИЛИ 17, блок 13 памяти. Устройство может работать в разных системах приоритета, позволяет динамически переходить из одной системы в другую по ходу задания режима, произвольно изменять очередность обслуживания запросов без изменения структуры устройства. 1 ил.

| Устройство приоритета | 1981 |

|

SU955070A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство приоритета | 1984 |

|

SU1226462A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1989-12-23—Публикация

1988-01-04—Подача