Изобретение относится к вычислительной технике и может быть использовано в устройствах ввода информации от различных дискретных датчиков в устройство обработки данных.

Цель изобретения - повышение надежности устройства за счет уменьшения вероятности переполнения блока памяти.

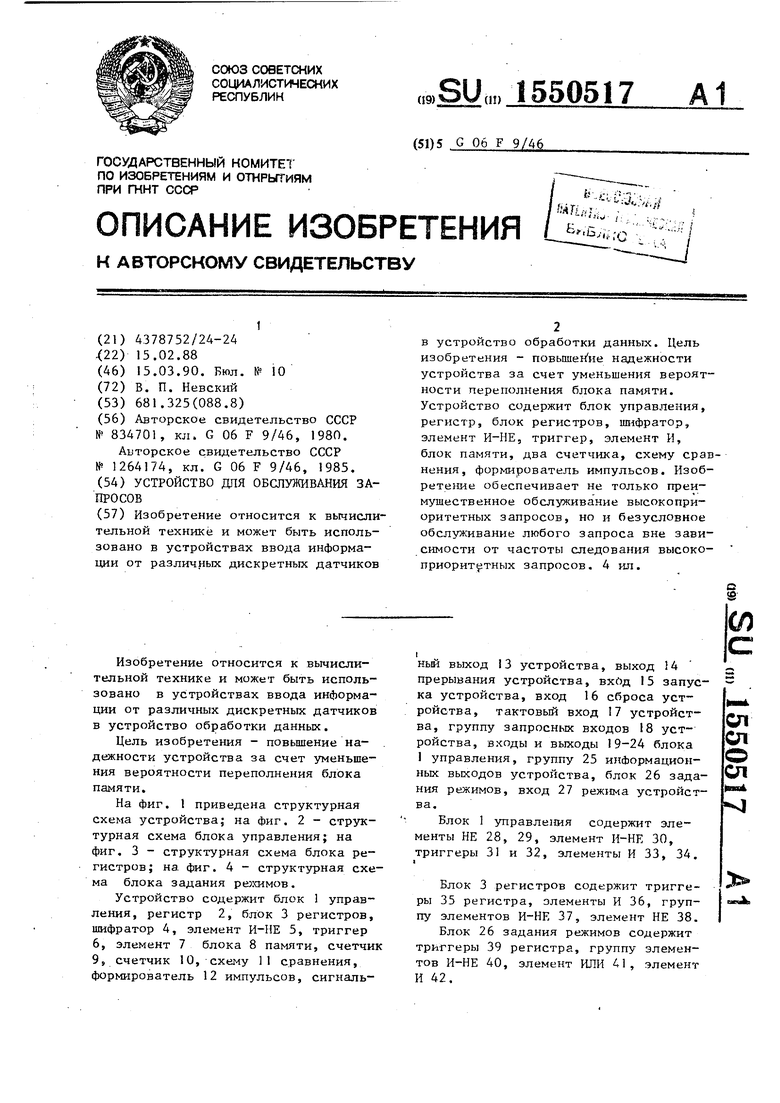

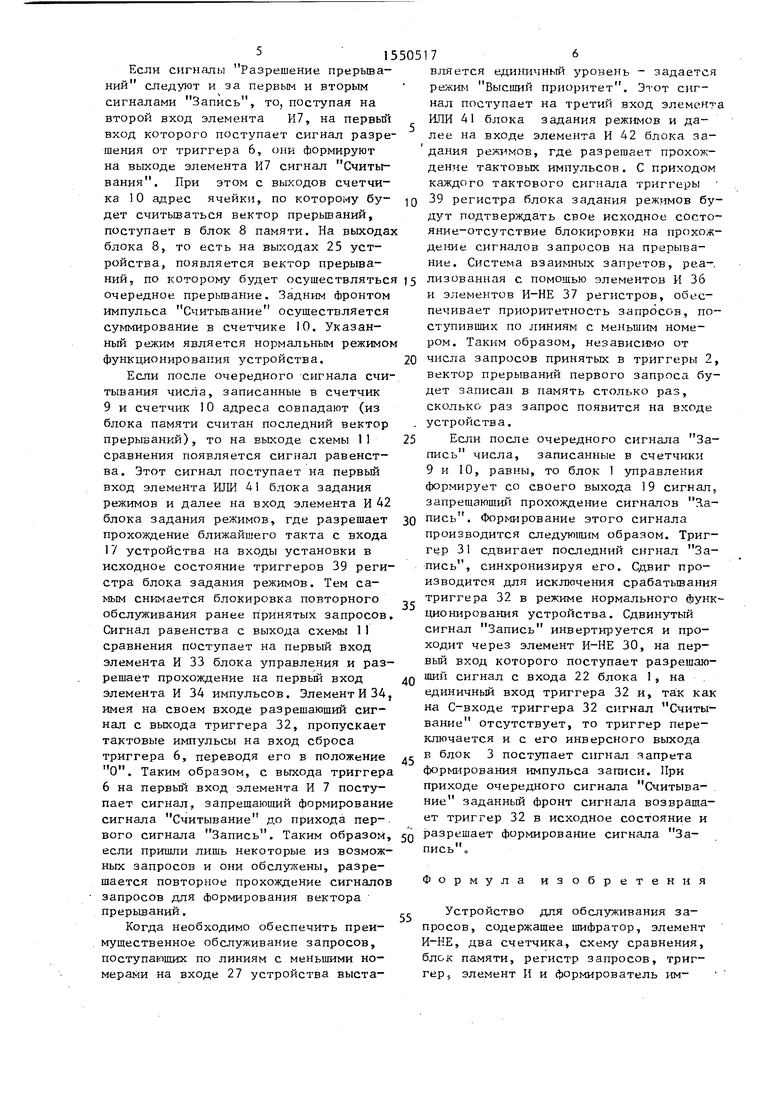

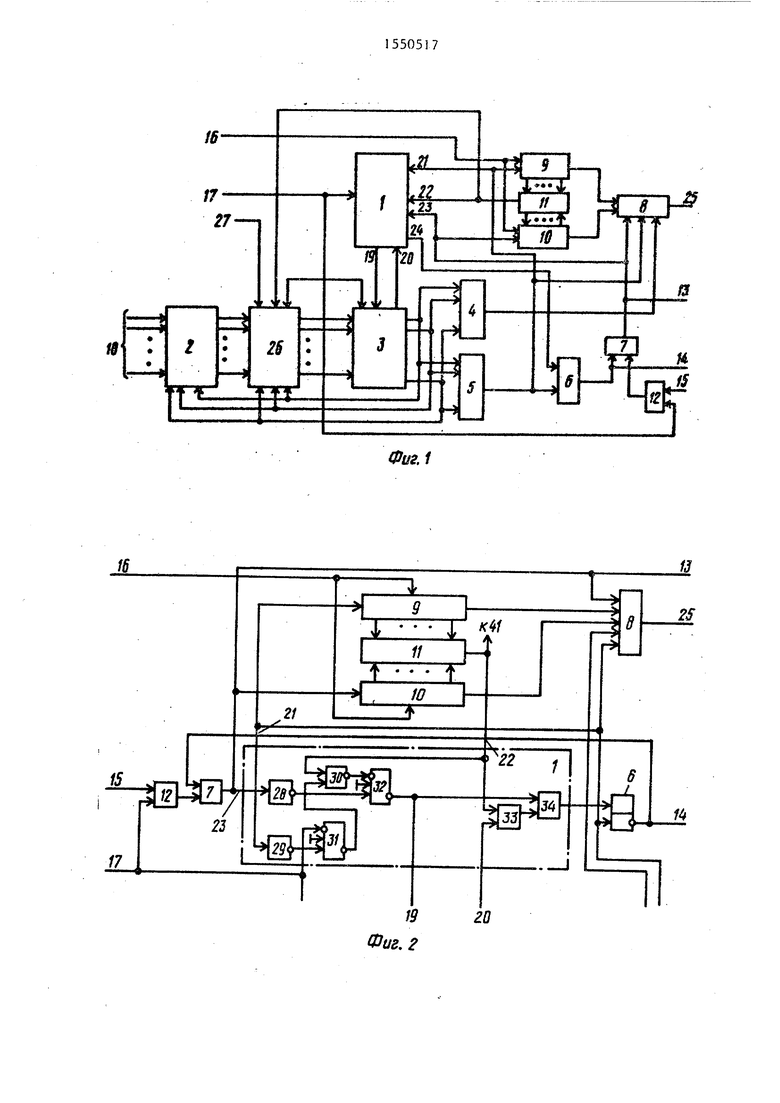

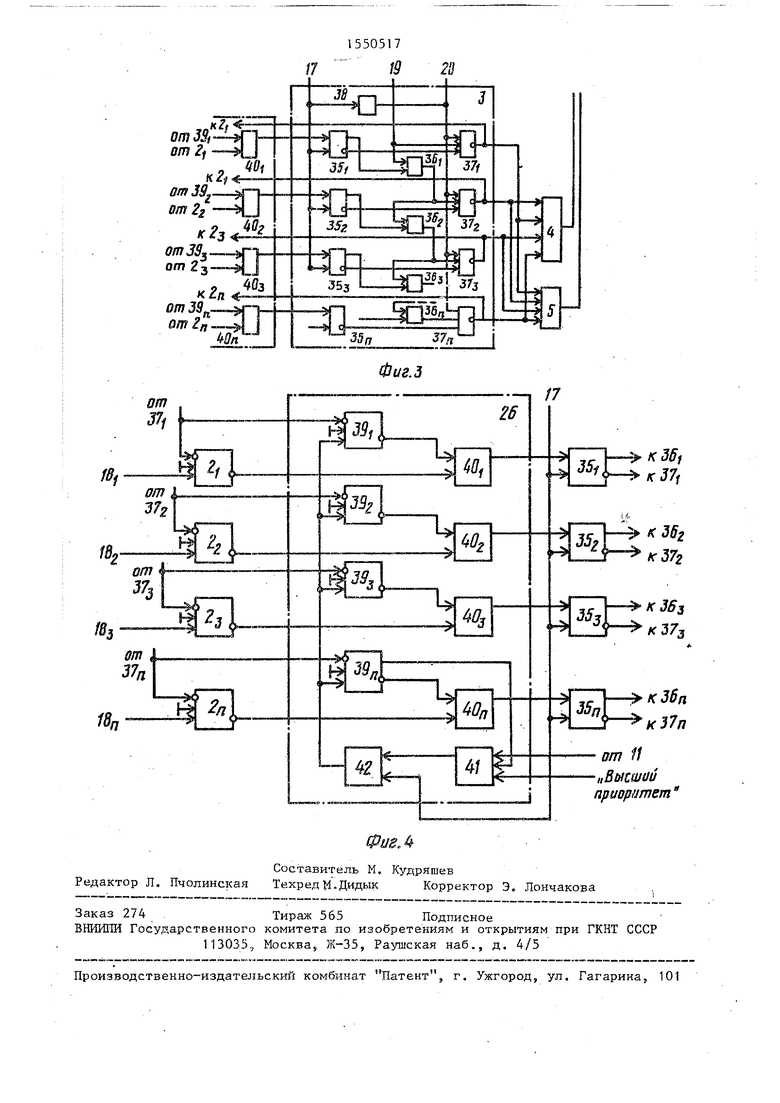

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - структурная схема блока управления; на фиг. 3 - структурная схема блока регистров; на фиг. 4 - структурная схема блока задания режимов.

Устройство содержит блок 1 управления, регистр 2, блок 3 регистров, шифратор 4, элемент И-НЕ 5, триггер 6, элемент 7 блока 8 памяти, счетчик 9, счетчик 10, схему 11 сравнения, формирователь 12 импульсов, сигнальный выход 13 устройства, выход J4 прерывания устройства, вход 15 запуска устройства, вход 16 сброса устройства, тактовый вход 17 устройства, группу запросных входов 18 устройства, входы и выходы 19-24 блока 1 управления, группу 25 информационных выходов устройства, блок 26 задания режимов, вход 27 режима устройства.

Блок 1 управления содержит элементы НЕ 28, 29, элемент И-НЕ 30,

триггеры 31 и 32, элементы И 33, 34.

i

Блок 3 регистров содержит триггеры 35 регистра, элементы И 36, группу элементов И-НЕ 37, элемент НЕ 38.

Блок 26 задания режимов содержит триггеры 39 регистра, группу элементов И-НЕ 40, элемент ИЛИ 41, элемент И 42,

ел

СП

о

СП

ГааА,

31550

Устройство работает следующим образом

В случае одновременного поступления сигналов от внешних устройств на входы 18 триггеры 2 переходят в состояние О. Сигналы единичного уровня с инверсных выходов триггеров 2 поступают на первые входы соответствующих элементов И-НЕ 40 блока задания режимов, на вторые входы которых поступают сигналы единичного уровня с выходов соответствующих триггеров

39регистра блока задания режимов (исходное состояние регистра О)„ Уровень О с выходов элементов И-НЕ

40поступает на соответствующие триггеры 35 блока регистров. Ближайшим тактом, поступающим с входа 17 уст- ройств, триггеры 35 переводятся в состояние О. Ближайшим тактом с выхода элемента НЕ 38 формируется импульс отрицательной полярности. Этот импульс поступает на элемент И-НЕ

37-1s с выхода которого на вход тркг- гера 2-1 поступает сигнал, переводящий его в состояние 1, с выхода элемента И-НЕ 37-2 в этот момент импульс не формируется, так как на его третий вход с прямого выхода триггера 35- через элемент И 36-1 поступает сигнал запрета, который через элемент И 36-2 присутствует на всех последующих элементах И-НЕ 37. Этим обеспечивается приоритетность запросов.

Импульс с выхода элемента И-НЕ 37- 1 поступает на вход шифратора 4, в котором осуществляется кодирование первого вектора прерываний в виде двоичного кода, поступающего на информационные входы блока 8 памяти. Через элемент 5 импульс с выхода элемента И-НЕ 37-1 осуществляет запись в блок 8 памяти по адресу, формируемому счетчиком 9, информации кода вектора прерываний с выходов шифратора 4.

В исходное состояние счетчики 9 и 10 устанавливаются счгналом5 поступающим с входа 16 устройства. Поэтому первьй вектор запроса прерываний записывается в блек памяти по нулевому адресу. При поеттедуюдих опросах этот - вектор может быть записан по любому адресу. Текущий адрес записи с выхода счетчика 9 поступает на входы адреса записи блока 8 памяти. Задним фронтом импульса сигнала, поступающего с выхода элемента 5Э триггер 6 уста

o

5

0

5 Q

5

40

45

50

55

навливается в состояние 1 и подготавливает элемент И 7 к прохождению сигнала,, Одновременно осуществляется суммирование в счетчике 10. Следующим тактом триггер 35-1 переводится в исходное состояние, чем снимается запрет с входа элемента И 36-1 и он формирует на третьем входе элемента И-НЕ 37-2 сигнал разрешения, позволяющий сформировать отрицательный импульс, поступающий на вторые входы шифратора 4 и элемента И-НЕ 5 для формирования кода второго вектора прерываний и второго сигнала записи. По сигналу Запись в очередную ячейку блока 8 памяти по адресу, сформированному счетчиком 9, записывается новый вектор прерываний. Далее по аналогичной схеме в блок 8 памяти записывается очередной вектор прерываний. Возможность повторного формирования вектора прерываний по уже обслуженному запросу блокирована следующим образом. Как только первый запрос будет принят для формирования вектора прерываний, сигнал с выхода элемента И-НЕ 37-1 поступает на вход установки в 1 триггера 39-1 регистра блока задания режимов. Триггер 39-1 переходит в состояние 1 и сигнал нулевого уровня с его инверсного выхода блокирует прохождение сигнала запроса на прерывание через элемент И-НЕ 40-1. С принятием очередного запроса для формирования вектора прерываний по аналогичной схеме блокируется повторное прохождение и других запросов. Блокировки снимаются только тогда, когда в блок 8 памяти записан вектор прерываний по последнему запросу. Сигнал единичного уровня с прямого выхода последнего триггера 39 регистра блока задания режимов поступает на второй вход элемента ИЛИ 41 блока задания режимов и далее на вход элемента И 42,где разрешает прохождение ближайшего тактового импульса с входа 17 устройства. Ближайший тактовый импульс переводит триггеры 39 регистра блока задания режимов в исходное состояние О. Сигналы единичного уровня с инверсных выходов триггеров 39 поступают на вторые входы элементов И-НЕ 40, где разрешают прохождение поступивших запросов на входы триггеров 35 регистра блока регистров. Далее процесс повторяется в указанном порядке.

515

Если сигналы Разрешение прерываний следуют и за первым и вторым сигналами Запись, то, поступая на второй вход элемента И7, на первый вход которого поступает сигнал разрешения от триггера 6, они формируют на выходе элемента И7 сигнал Считывания. При этом с выходов счетчи- кз 10 адрес ячейки, по которому бу- дет считываться вектор прерываний, поступает в блок 8 памяти. На выходах блока 8, то есть на выходах 25 устройства, появляется вектор прерываний, по которому будет осуществляться очередное прерывание. Задним фронтом импульса Считывание осуществляется суммирование в счетчике 10. Указанный режим является нормальным режимом функционирования устройства,

Если после очередного сигнала считывания числа, записанные в счетчик 9 и счетчик 10 адреса совпадают (из блока памяти считан последний вектор прерываний), то на выходе схемы 1 1 сравнения появляется сигнал равенства. Этот сигнал поступает на первый вход элемента ИЛИ 41 блока задания режимов и далее на вход элемента И 42 блока задания режимов, где разрешает прохождение ближайшего такта с входа 17 устройства на входы установки в исходное состояние триггеров 39 регистра блока задания режимов. Тем самым снимается блокировка повторного обслуживания ранее принятых запросов. Сигнал равенства с выхода схемы 11 сравнения поступает на первый вход элемента И 33 блока управления и разрешает прохождение на первьй вход элемента И 34 импульсов. Элемент И 34, имея на своем входе разрешающий сигнал с выхода триггера 32, пропускает тактовые импульсы на вход сброса триггера 6, переводя его в положение О. Таким образом, с выхода триггера 6 на первьй вход элемента И 7 поступает сигнал запрещающий формирование сигнала Считывание до прихода первого сигнала Запись. Таким образом, если пришли лишь некоторые из возможных запросов и они обслужены, разрешается повторное прохождение сигналов запросов для формирования вектора прерываний.

Когда необходимо обеспечить преимущественное обслуживание запросов, поступающих по линиям с меньшими номерами на входе 27 устройства выста176

ваяется единичный уровень - задается режим Высший приоритет. сигнал поступает на третий вход элемента ИЛИ 41 блока задания режимов и далее на входе элемента И 42 блока задания режимов, где разрешает прохождение тактовых импульсов. С приходом каждого тактового сигнала триггеры 39 регистра блока задания режимов будут подтверждать свое исходное состояние-отсутствие блокировки на прохождение сигналов запросов на прерывание. Система взаимных запретов, реализованная с помощью элементов И 36 и элементов 37 регистров, обеспечивает приоритетность запросов, поступивших по линиям с меньшим номером. Таким образом, независимо от числа запросов принятых в триггеры 2, вектор прерываний первого запроса будет записан в память столько раз, сколько раз запрос появится на входе устройства.

Если после очередного сигнала Запись числа, записанные в счетчики 9 и 10, равны, то блок 1 управления формирует со своего выхода 19 сигнал, запрещающий прохождение сигналов Яа- пись. Формирование этого сигнала производится следующим образом. Триггер 31 сдвигает последний сигнал Запись, синхронизируя его. Сдвиг производится для исключения срабатывания триггера 32 в режиме нормального функционирования устройства. Сдвинутый сигнал Запись инвертируется и проходит через элемент И-НЕ 30, на первьй вход которого поступает разрешающий сигнал с входа 22 блока 1, на единичный вход триггера 32 и, так как на С-входе триггера 32 сигнал Считывание отсутствует, то триггер переключается и с его инверсного выхода в блок 3 поступает сигнал запрета формирования импульса записи. При приходе очередного сигнала Считывание заданньй фронт сигнала возвращает триггер 32 в исходное состояние и разрешает формирование сигнала Запись

Формула изобретения

Устройство для обслуживания запросов, содержащее шифратор, элемент И-НЕ, два счетчика, схему сравнения, блок памяти, регистр запросов, триггер s элемент И и формирователь импульсов, первая и вторая группы входов схемы сравнения соединены с первыми группами выходов первого и второго счетчиков, вторые группы выходов которых соединены соответственно с группой входов адреса записи и группой входов адреса считывания блока памяти, группа выходов шифратора соединена с группой информационных вхо- дОв блока памяти, тактовый вход блока регистров соединен с тактовым входом устройства, выходы блока регистров соединены с входами установки в 1 одноименных разрядов регистра запросив, с входами шифратора и с входами э4емента И-НЕ, информационные входы регистра запросов соединены с входом логического нуля устройства, тактовые - с одноименными запросными вводами устройства} первый вход блока управления соединен с выходом блока регистров, второй вход - с выходом схемы сравнения, третий вход - с вы- ходом элемента И-НЕ, со счетным вхо- дОм первого счетчика, с входом управ- записью блока памяти и с нулевым входом триггера, четвертый вход - с выходом элемента И, с входом считывания блока памяти, со счетным входом второго счетчика и с сигнальным выходом устройства, вход сброса которого соединен с входами сброса первого и второго счетчиков, пятый вход 6jtoKa управления соединен с тактовым входом устройства и с первым входом Формирователя импульсов, второй вход которого соединен с входом запуска устройства, единичный вход триггера соединен с первым выходом блока управления , выход триггера - с первым входом элемента И и с выходом прерывания устройства, второй вход элемента И соединен с выходом формирователя импульсов, выходы блока памяти являются информационными выходами устройства, второй выход блока управления соединен с управляющим входом блока регистров, отличающееся тем, что, с целью повышения надежности за. счет уменьшения вероятности переполнения блока памя-

ти, оно содержит блок задания режимов, который содержит регистр, группу элементов И-НЕ, элемент И, элемент ИЛИ, причем выходы элементов И-НЕ группу блока задания режимов соецине5 ны с информационными входами блока.- регистров, первые входы элементов И- НЕ группы блока задания режимов соединены с соответствующими выходами регистра запросов, вторые входы элеQ ментов И-НЕ группы блока задания режимов соединены с инверсными выходами соответствующих разрядов регистра блока задания режимов, входы установки в 1 которых подключены к

5 выходам блока регистров, информационные входы разрядов регистра блока задания режимов соединены с входом логического нуля устройства, тактовые входы разрядов регистра блока задания

0 режимов соединены с выходом элемента И блока задания режимов, первый вход которого соединен с тактовым входом устройства, второй вход элемента И блока задания режимов соединен с выходом элемента ИЛИ блока задания режимов , первый вход которого соединен с выходом схемы сравнения, второй вход элемента ИЛИ блока задания режимов t соединен с прямым выходом последнего

Q разряда регистра блока задания режимов, третий вход элемента ИЛИ блока задания режимов соединен с входом режима устройства.

5

Фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обслуживания запросов | 1985 |

|

SU1264174A1 |

| Устройство для сопряжения ЭВМ с синхронными каналами передачи данных | 1986 |

|

SU1347083A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Система для отладки программ | 1987 |

|

SU1481774A1 |

| Устройство для сопряжения вычислительного модуля с магистралью | 1985 |

|

SU1325495A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Микропрограммное устройство для обработки прерываний | 1983 |

|

SU1126956A1 |

| Устройство для обслуживания запросов | 1985 |

|

SU1283768A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах ввода информации от различных дискретных датчиков в устройство обработки данных. Цель изобретения - повышение надежности устройства за счет уменьшения вероятности переполнения блока памяти. Устройство содержит блок управления, регистр, блок регистров, шифратор, элемент И-НЕ, триггер, элемент И, блок памяти, два счетчика, схему сравнения, формирователь импульсов. Изобретение обеспечивает не только преимущественное обслуживание высокоприоритетных запросов, но и безусловное обслуживание любого запроса вне зависимости от частоты следования высокоприоритетных запросов. 4 ил.

19 Фиг. 2

20

17

1550517

19 2$

| Устройство для организации очереди | 1979 |

|

SU834701A1 |

| Устройство для обслуживания запросов | 1985 |

|

SU1264174A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-03-15—Публикация

1988-02-15—Подача