Изобретение относится к вычислительной технике и может быть исполь эовано при построении многоканальных систем умножения с одним общим входным частотным сигналом.

Цель изобретения - повьппение точности умножения за счет исключения выходного сигнала при нулевом состоянии двоичного счетчика.

На чертеже представлена функциональная схема устройства.

Устройство для умножения содержит двоичный счетчик I, дешифратор 2, блок 3 приоритетного прерывания, элемент И-НЕ 4, входы 5 множителей, N мультиплексоров 6, N делителей 7 частоты, выходы которых являются выходами устройства. Входы N делителей 7 частоты соединены соответственно с выходами N мультиплексоров 6, информационные входы которых соединены с входами 5 множителей устройства, входы с нулевого по седьмой запроса прерывания блока 3 приоритетного прерывания соединены соответственно с третьего по десятый разрядными выходами двоичного счетчика 1 , счетньш вход которого соедине с входом множимого устройства и.с первым входом дешифратора 2, первый и второй разрядные выходы двоичного счетчика 1 соединены соответственно с вторым и третьим входами дешифратора 2, первый и второй выходы которого соединены соответственно с входом синхронизации и входом разрешения записи блока 3 приоритетного прерывания, третий выход дешифратор 2 соединен с первым входом элемента И-НЕ 4, второй вход которого соединен с выходом разрешения прерыва- 1ШЯ блока 3 приоритетного прерывания, а выход элемента И-НЕ 4 соединен со стробирующими входами N мультиплексоров 6, адресные входы которых соединены соответственно с выходами кода прерывания блока 3 приоритетного прерывания. 1

Устройство, работает следующим образом.

Тактовые импульсы представляют собой частоту множимого, поступают на вход С десятиразрядного двоичного счетчика 1, Выходы первых двух разрядов счетчика 1 соединены с входами дешифратора 2, на один из его входов также поступает тактовый импульс. В результате на выводе деши

фратора 2 формируются три импульса в следующей последовательности: импульс синхронизации, который проходит на вход синхронизации С блока 3

приоритетного прерывания; импульс разрешения записи Р.З., который также поступает на вход Р.3. блока 3 приоритетного прерывания; импульс стробирования, который поступает на

второй вход элемента И-НЕ 4. Так как в начальный момент на всех выходах с второго по десятый разряд имеется нулевой сигнал, то в это время на выходе РП1 разрешения группы прерывания блока 3 приоритетного прерывания имеется сигнал запрета, который поступает на первый вход элемента И-НЕ 4, что исключает прохождение стробирующего импульса на вход стробирования мультиплексора 6. Как только будет записан импульс в третьем разряде Q счетчика 1, на вход 3II7 блока 3 приоритетного прерывания поступает сигнал прерывания. По этому сигналу на выходе блока 3 КПО-КТ12 Код прерывания будет сформирован код вектора прерывания, соответствующий высшему приоритету ЗП7.

Это соответствует двоичному коду 001. После поступления на вход адреса Х10-Х12 мультиплексора 6 этого кода и одновременного поступления на его стробирзгющий вход XI импульса разрешения прохождения сигнала, а

также если на его информационном входе Х2-Х9, соответствующем старшему разряду входа множителя 5, имеется сигнал, на выходе мультиплексора 6 появляется сигнал.

После того, как на вход устройства П1 оходит следующая .серия четырех импульсов, на выходе Qg десятиразрядного двоич його счетчика 1 формируется сигнал О, а на выходе Q . Этот код поступает на входы ЗП7 и ЗПб запроса прерываний блока 3 приоритета прерывания. При этом на его выходе кода прерывания появляется код 010. Таким образом, кажДое нечетное число на .выходе Q - счетчика I дает разрешение на прохождение импульсов с мультиплексора 6. За полный цикл счета счетчика 1 (256 импульсов) сформируется

28 импульсов на выходе селектора- мультиплексора при нечетных числах.

Ка:кдое четное число на выходах счетчика Qj - Q, дает соответственно 64 импульса.

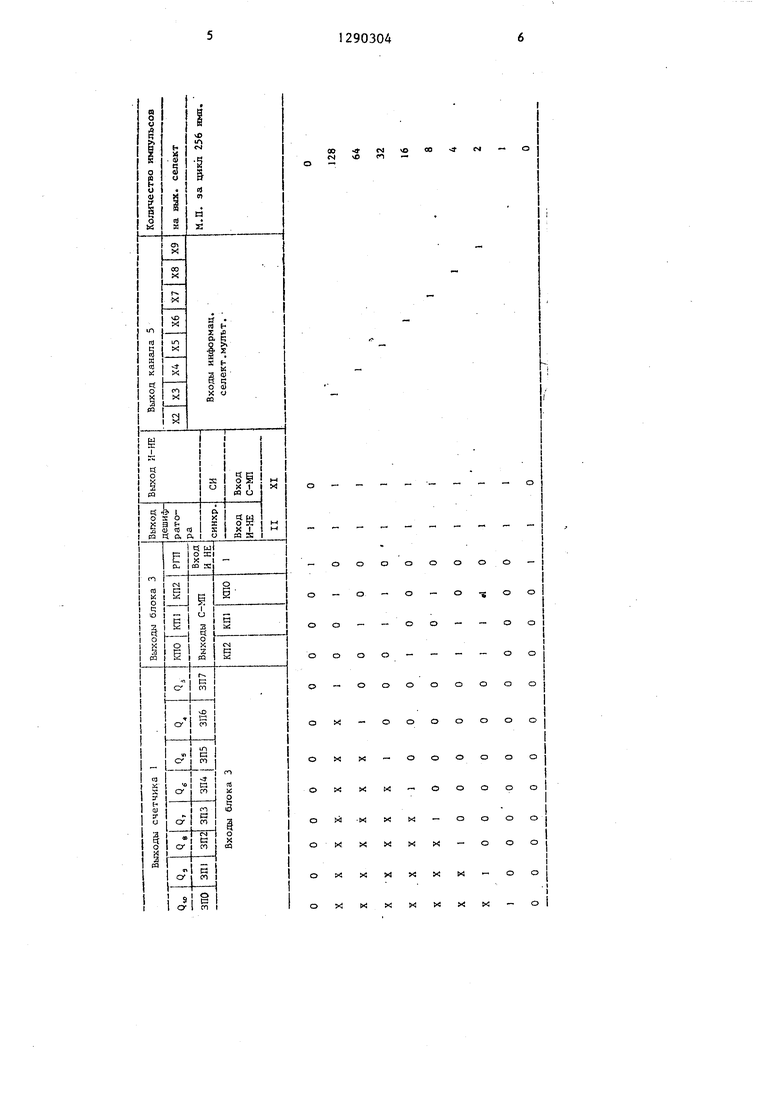

Б таблице показан алгоритм работы устройства, где X - сигналы, которые не влияют на выходные сигналы блока 3 приоритетного прерывания; XI - стробирзтощий импульс, который проходит на стробирующий вход XI мультиплексора 6.

Как видно из таблицы, каждому коду, сформированному за один цикл 256 импульсов, пришедших через разряды ХЗ-Х10 счетчика 1, соответствует определенное количество импульсов на выходе мультиплексора 6. В зависимости от кода на входе 5 множителя можно сформировать любое число импульсов от О до 255.

Если обозначить входную частоту устройства F, входной код числом К, коэффициент деления D выходного делителя 7 частоты число разрядов в двоичном счетчике 1 восемь, то выходная частота на выходе одного из каналов устройства (на выходе делителя 7 частоты) будет

бых

F К 5

Так как все величины в знаменателе формулы - постоянные, а значения числителя (Р - частота, К - код числа на выходе канала) - переменные, то устройство выполняет функции умножения в каждом канале.

Формула изобр„етения 35

-Устройство для умножения, содержащее двоичный счетчик, элемент И - НЕ,

5

0

5

5

дешифратор N мультиплексоров и N делителей частоты, выходы которых являются выходами устройства, входы N делителей частоты соединены соответственно с выходами N мультиплексоров, информационные входы которых являются входами множителей устройства, счетный вход двоичного счетчика является входом множимого устройства, отличающееся тем, что, с целью повьшгения точности умножения за счет исключения выходного сигнала при нулевом состоянии двоичного счетчнка, в него введен блок приоритетного прерывания, входы с нулевого по седьмой запроса прерывания которого соединены соответственно с третьего по десятый разрядными выходами двоичного счетчика, счетный вход которого соединен с первым входом дешифратора, первый и второй разрядные выходы двоичного счетчика соединены соответственно с вторым и третьим входами дешифратора, первый и второй выходы которого соединены соответственно с входом синхронизации и входом разрешения записи блока приоритетного прерывания, третий выход дешифратора соединен с первым входом элемента И - НЕ, второй вход которого соединен с выходом разрешения прерывания блока приоритетного прерывания, а выход элемента И - НЕ соединен со стробирующим входами N мультиплексоров, адресные входы которых соединены соответственно с выходами кода прерывания блока приоритетного прерывания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное программное задающее устройство | 1986 |

|

SU1383297A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Вычислительное устройство | 1986 |

|

SU1327118A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2006936C1 |

| Кодек для передачи информации с помощью имитостойких последовательностей сигналов сложной формы | 1987 |

|

SU1451719A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| Число-импульсное арифметическое устройство | 1980 |

|

SU951303A1 |

Изобретение относится к области вычислительной техники, может быть использовано при построении многоканальных систем умножения с одним об1дим входным частотньм сигналом и позволяет повысить точность и упрощает многоканальные устройства умножения, когда имеется один общий частотный сигнал, который необходимо умножить на несколько кодовых сигналов, на выходе которых получается частота. Цель изобретения - повышение точности умножения за счет исключения выходного сигнала. Положительный эффект изобретения достигается за счет того, что в него введен дешифратор 2 и блок 3 приоритетного прерывания, причем благодаря исключению одного ложного импульса при нулевом состоянии входного счетчика 1 снижается погрешность при умножении на малые величины. Кроме того, вся логическая часть устройства выполнена проще, так как решается она на одной микросхеме блоке приоритетного прерывания. 1 ил., 1 табл. i (Л 1C ;о о со

| Двоичный умножитель | 1979 |

|

SU855657A1 |

| Устройство для умножения | 1983 |

|

SU1160401A1 |

Авторы

Даты

1987-02-15—Публикация

1985-08-07—Подача