Изобретение относится к технике измерения параметров движения и может быть использовано для измерения ускорений вращающихся валов.

Известно устройство для измерения ускорения вала, содержащее импульсный датчик частоты вращения, генератор эталонного времени, реверсивный счетчик, вентили, схему инкремента, RS-триггер, D- триггер, дешифратор, блок отсчета. Это устройство обладает низкой динамической точностью, так как не позволяет идентифицировать режимы смени скоростного режима.

Наиболее близким по технической сущности к предложенному устройству является устройство, содержащее импульсный датчик, расположенный на валу и подсоединенный выходом к входам двух элементов И, к второму входу первого элемента И подключен прямой выход генератора эталонного времени, а к второму входу второго элемента И - его инверсный выход, выход

первого элемента И соединен с суммирующим входом реверсивного счетчика, а выход второго элемента И - с его вычитающим входом, кроме того, устройство содержит схему инкремента, соединённую с инверсными выходами реверсивного счетчика и блока отсчёта;.

Недостатком этого устройства является низкая динамическая точность, так как и в нем не учтена возможность смены скоростного режима вала. :

Целью изобретения является повышение динамической точности измерения ускорения.. .

Цель достигается тем, что в известное устройство, содержащее импульсный датчик, расположенный на валу и подсоединен ный выходом к входам двух элементов И, к второму входу яервого элемента И подключен прямой выход генератора эталонного времени, а к второму входу второго элемента И - его инверсный выход, выход первого элемента И соединен с суммирующим вхо-Ч

ю

vj 00

дом реверсивного счетчика, а выход второго элемента И с его вычитающим входом; кроме того, устройство содержит схему инкремента, соединенную с инверсными выходами реверсивного счетчика, и блок отсчета, дополнительно введены формирователь коротких импульсов, элемент задержки, RS-триггер, мультиплексор, третий элемент И и идентификатор смены скоростного режима, причем п рямой выход гене- ратора Эталонного времени через формироваУель Хоротких импуЖсов соединен с элементом задержки, стробирующим входом схемы инкремента и тактовым входом идентификатора смены скоростного ре- жима, выход элемента задержки соединен с R-входом реверсивного счётчика, с R-вхо- дом RS-триггера и первым входом третьего элемента И, выход дешифратора соединен с S-входом RS-триггера, прямой выход кото- рого соединен с управляющим входом мультиплексора, к информационным входам которого подключены выходы схемы инкремента и прямые выходы реверсивного счетчика, выходы мультиплексора соединены с блоком .отсчета, прямые выходы реверсивного счетчика связаны с информационными входами идентификатора смены скоростного режима, выход которого соединен с вторым входом третьего элемента. И, выход которого связан с разрешающим вхо дом мультиплексора. Кроме того, идентификатор смены скоростного режима содержит стробируемый дешифратор, счетный триггер, два элемента И, два D-триггера и стро- бируем ый сумматор по модулю два, причем информационные входы идентификатора соединены с информационными входами стробируемого дешифратора, тактовый вход идентификатора соединен со строби- рующим входом дешифратора, входом счетного триггера и стробирующим входом сумматора по модулю два, выход дешифратора соединен с первыми входами элементов И, к вторым их входам соответственно подключены прямой и инверсный выходы счетного триггера, а выходы соединены с С-входами D-тригг еров, к D-входам которых подключен выходдешифратора, прямые выходы D-триггеров соединены с информаци- онными входами сумматора по модулю два, выход которого является выходом идентификатора.

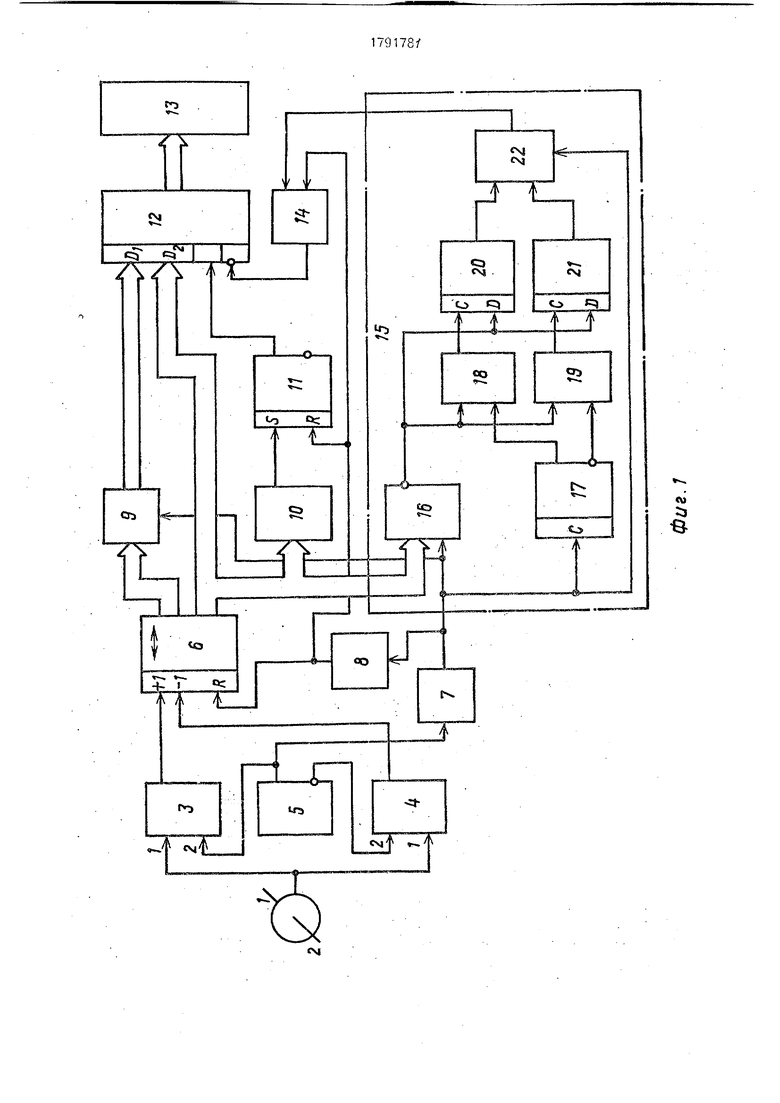

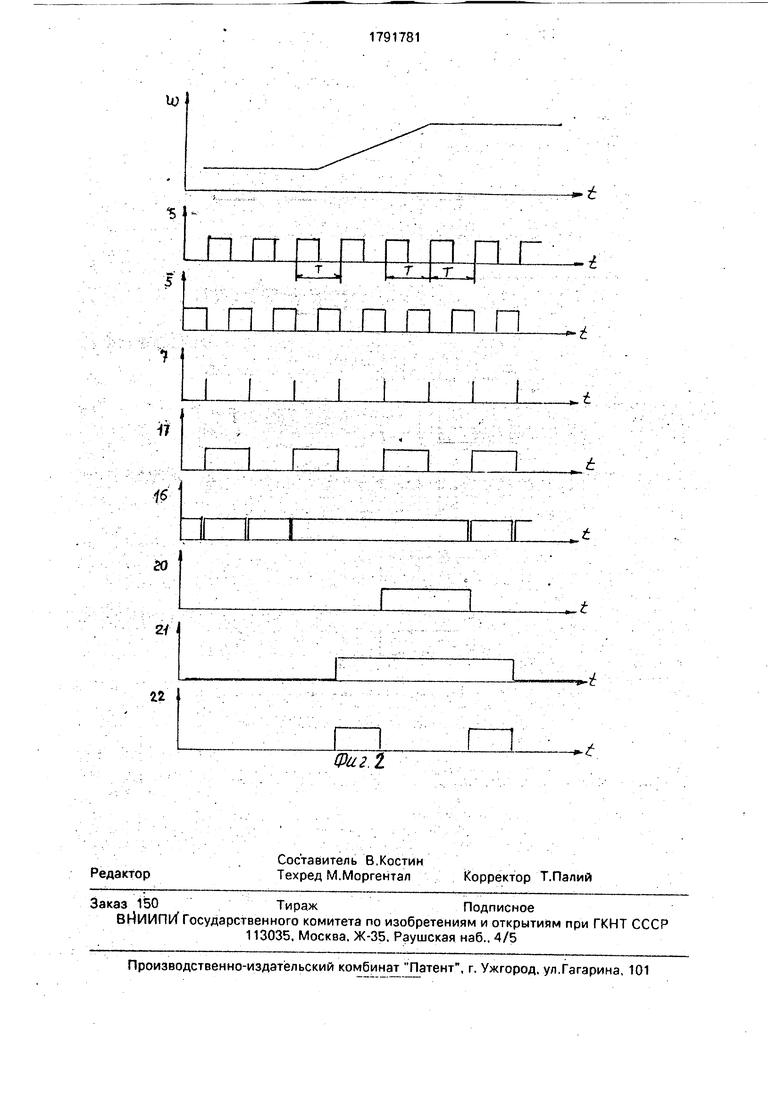

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - временные диаграммы его работы.

На схеме показаны:

1 - импульсный датчик,

2 - объект измерения - вал, 3,4- элементы И,

5 - генератор эталонного времени,

6 - реверсивный счетчик,

7 - формирователь коротких импульсов, 8- элемент задержки, .

9 - схема инкремента,

10 - дешифратор,

11 - RS-триггер,

12 - мультиплексор,

13 - блок отсчета, 14-элемент И,

15 - идентификатор, который в свою очередь содержит:

16 - дешифратор,

17 - счетный триггер,

18, 19 - э лементы И,

20,21 - D-триггеры,

22 - сумматор по модулю два.

Структурная схема построена следующим образом..

Импульсный датчик 1, расположенный на валу 2 и подключенный к элементам И 3 и 4. К другим входам этих элементов подключены соответственно прямой и инверсный выходы генератора 5 эталонного времени. Выходные сигналы генератора 5 (фиг. 2) представляют собой меандры, сдвинутые по фазе на 180°. Выходные сигналы элементов 3 и 4 поступают соответственно на суммирующий и вычитающий входы реверсивного счетчика 6. Прямой выход генератора 5 подключен к формирователю 7 коротких импульсов, выходной сигнал которого формируется по фронту сигнала прямого выхода генератора 5 (фиг. 2) и поступает непосредственно на стробирукжилй вход идентификатора 15 (стробмрующий вход дешифратора. 16) и на стробирующий вход смены инкремента 9, а через элемент задержки 8 - на R-вхо д реверсивного счет1 чика 6, R-вход RS-триггера 11 и вход элемента И 14. Кодовые выходы реверсивного счетчика объединены в две группы - прямые и инверсные. Инверсные выходы через схему инкремента 9 подключены к первой группеинформационных входов мультиплексора 12, а прямые выходы - непосредственно к второй группе входов мультиплексора 12, к входам дешифратора 10 и к информационным входам идентификатора 15 (информационные входы стробируемого дешифратора 16). Выход дешифратора 10 соединен с S-входом RS- трйггера 11, прямой выход которого связан с. управляющим входом мультиплексора 12 (определяет, с какого направления осуществляется передача информации на блок отсчета). К разрешающему входу мультиплексора 12 (определяет включение в работу или отключение мультиплексора 12) подключен выход элемента И 14, к второму

входу которого подключен выход идентификатора 15 (выход сумматора 22 по модулю два). Собственно идентификатор 15 смены скоростного режима содержит стробируе- мый дешифратор 16, счетный триггер 17, элементы И 18, 19, D-триггеры 20, 21 и сумматор 22 по модулю два.

Сущность функционирования устройства сводится к следующему.

Импульсный датчик 1 вырабатывает сигналы, частота которых пропорциональна частоте вращения валэ: fi К ft. Импульсы генератора 5 поочередно открывают элементы И 3 и 4. Тем самым обеспечивается поочередная подача сигнала датчика 1 на суммирующий и вычитающий входы реверсивного счетчика 6. В последнем к концу каждого цикла измерений (продолжительностью в период Т импульсов гене ра тора 5) формируется код

N. Ifl/0 t T/2 - fl/T/2 t T, npoпорциональный разности частот вращения на постоянном временном интервале. В конце каждого интервала с задержкой, определяемой элементом 8 и выбираемой по величине меньшей, чём минимальный период импульсов датчика 1, реверсивный счет- чик сбрасывается в нулевое состояние и тем самым подготавливается к новому циклу измерений, Если ускорение положительно, то в цикле измерения реверсивный счетчик переходит через состояние все нули. Это обстоятельство фиксируется дешифратором 10, выходной сигнал которого устанавливает в единичное состояние RS-триггер 11. Выходной потенциал прямого выхода этого триггера определяет передачу в блок отсчета 13 через мультиплексор 12 дополнительного кода С (добавление единицы к обратному коду осуществляется в схеме 9 инкремента). В противном случае (ускорение отрицательно) дешифратор 10 в цикле не срабатывает, триггер 11 остается в нулевом состоянии (сбрасывается в него в конце каждого цикла выходным сигналом элемента задержки 8) и мультиплексор 12 передает в блок отсчета 13 прямой код реверсивного счетчика 6.

Описанная часть структуры фактически реализует функции прототипа и позволяет точно измерять ускорение лишь тогда, когда измерительный интервал Т полностью укладывается на линейно изменяющемся участке графика частоты вращения во времени (на фиг. 2 этому соответствует измерительный интервал Т, оканчивающийся в момент времени t2). В противном случае (интервалы Т на фиг. 2, оканчивающиеся в моменты

времени ti и 1з) имеет место динамическая ошибка измерения ускорения. .

В таких режимах вступает в работу идентификатор 15 смены скоростного режима. Его функционирование сводится к следующему. Выходной сигнал формирователя 7 в конце каждого интервала Т стробирует дешифратор 16 и, если в реверсивном счетчике 6 зафиксировано нулевое ускорение, то

дешифратор 16 формирует Отрицательный импульс (фиг. 2). В противном Случае (нулевое ускорение) на выходе дешифратора 16 в момент стробирования остается потенциал высокого уровня (фиг. 2). Одновременно выходной сигнал формирователя 7 пёреключа- етсчетный триггер 17 и тем самым выходной сигнал дешифратора поочередно через элементы И 18, 19 передается на С-входы D- триггеров 20, 21. Соответствующий

D-триггер, будучи в нулевом (единичном) состоянии, переключается, если с дешифратора 16, поступает единичный (нулевой) потенциал, и остается в прежнем состоянии, если с дешифратора 16 поступает нулевой (единичный) потенциал. Таким образом, в моменты окончания интервалов Т (на фиг. 2 - это ti и ta). непосредственно следующие за моментами смены скоростного режима, потенциалы U20, IJ21 прямых выходов Ьтриггеров 20, 21 оказываются различными. При этом выходной сигнал сумматора 22 по модулю два, реализующего функцию tfeo A U21 ч U20 А 1)21. оказывается равным единице и в момент появления сигнала на

выходе элемента задержки 8 на выходе элемента И 14 будет единичный уровень. Такой уровень является запрещающим два мультиплексора 12, он не коммутирует на блок отсчета 13 ни одной из двух групп входов, т.

е. происходит пропуск Отсчёта. Если же два примыкающих во времени интервал Т полностью расположены либо на участке стаби- лизации скорости, либо на участке ее линейного изменения, то D-триггеры 20, 21

принимают одинаковое состояние (либо нули, либо единицы) и выходной сигнал сумматора 22 по модулю два равен нулю и разрешается работа мультиплексора 12. Таким образом, предложенное устройство позволяет исключить отсчеты с Динамическими погрешностями, обусловленными сменой скоростного режима,

Формула изобретения

1. Цифровой измеритель ускорения вала, содержащий импульсный датчик, расположенный на валу, два элемента И, первые выходы которых подключены к выходу импульсного датчика, генератор.эталонного

времени, прямой выход которого соединен С вторым входом первого элемента И, а инверсный - с вторым входом второго элемента И, реверсивный счётчик, Суммирующий и вычитающий входы которого соединены с выходами собтвёгственнО rtifpBdfo и второго; элементов И, схема инкремента; которой соединены с инверсными выходами реверсивного счётчика, дешифратор, входы которого соединены с прямыми выходами реверсивного счетчика, и блок отсчета, О У /l и ч а ю щ и И с я тем, что, с цейьй) повышения динамической точности измерения, в него введены формирователь корот-; кйх импульсов, элемент задержки, RS-tpMrrep, мультиплексор, третий элемент И и идентификатор смень скоростного ре- жима. причём прямой выход генератора эта- лонногб времени пбд ключе н к входу формирователя коротких импульсов, выход которого соединен со стробирующим входов схемы инкремента, с тактовым входом идентификатора смейы скоростного режима и через элемент задержки - с R-вхбдами рёверсивног.о смётчйка-й RS-трйггёра, а так- же5с первым входом третьего элемейта И, второй вход которого соединён с выходом идентификатора смены скоростного режима, а вйход-с разрешающим входом муль- twiriAekcopa, к информационны.м входам которого Яодключены выходь( смены инкремента и прямые вйходы реверсивного счётчика, а к управляющему его входу - прямой

выход RS-триггера, выходы мультиплексора соединены с входами блока отсчета, S-вход RS-tpHrrepa соединен с выходом дешифратора, а информационные входы идентифи- кагора смены скоростного режима подключены k прямым выходам реве реи вного счётчика . V; , :,

2. Измеритель по п. 1, от л и ч а ю щ и й- С я тем, что идентификатор смены скоро- стного режима содержит стробируемый де- шифратор, счетный триггер, два элемента И, Два tD-трйггёра и стробируемый сумматор по модулю два причем стробируемого Дешифратора соединен с первыми входами элементов И, вторые входы которых под- ключены соответственно к прямому и инверсному выходам счетноготриггера, выходы элементов И соединены соответст- венное С-входами D-трйггёров, D-входы ко- то рых соединены с выходом дешифратора, прямые выходы D-fриггеров соединены с информационными входами сумматора по модулю два, выход которого является выходом идентификатора смены скоростного ре- жима, Нри этом информационные входы стробируемого дешифратора являются информационными входами идентификатора смены скоростного режима, а стробирую- щйе входы дешифратора, сумматора по мо- дулю два и вход счетного триггера объединены и являются тактовым входом идентификатора смены скоростного режи- ма.. -;V::: .. ..: ....: :. . . : - - :

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой регистрации электрических сигналов | 1987 |

|

SU1472920A1 |

| Устройство для предварительной фильтрации входных сигналов узкополосных цифровых фильтров | 1990 |

|

SU1739481A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Прецизионный датчик перемещений | 1983 |

|

SU1158856A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство для определения момента разладки случайных процессов | 1985 |

|

SU1260973A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК ДИСКРЕТНОГО КАНАЛА СВЯЗИ | 1995 |

|

RU2138910C1 |

| Формирователь импульсов | 1990 |

|

SU1711325A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

Изобретение относится к измерительной технике и может быть использовано для измерения ускорений вращающегося вала. Сущность изобретения: цифровой измеритель ускорения вала содержит импульсный датчик, элементы И, генератор эталонной частоты, реверсивный счетчик, формирователь коротких импульсов, элементГзэд ерж- ки, схему инкремента, два дешифратора, RS-триггер, мультиплексор, блок отсчета, счетный триггер, два D-триггера, сумматор по модулю два. 2 ил,

Фиг.2.

.Ј

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой измеритель ускоренияВАлА | 1979 |

|

SU824061A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой измеритель ускорения вала | 1978 |

|

SU685987A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1993-01-30—Публикация

1991-06-24—Подача