02

ас

со

со 05

Изобретение относится к автоматике, вычислительной технике и связи.

Цель изобретения - повь1шение достоверности контроля и быстродействия.

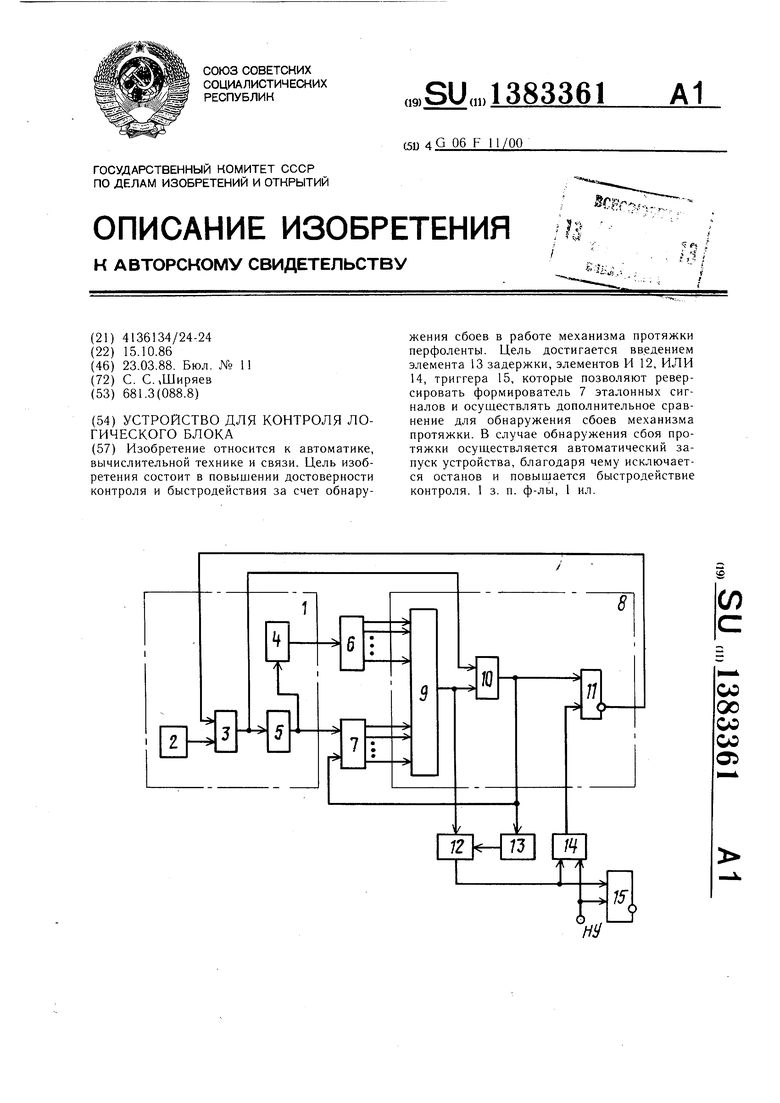

На чертеже представлена схема устройства.

Устройство содержит блок 1 управления, генератор 2 импульсов, элемент И 3, формирователь 4 импульса, элемент 5 задержки, , контролируемый блок 6, формирователь 7 эталонных сигналов, блок 8 регистрации ошибок, схему 9 сравнения, элемент 10 запрета, триггер 11 отсутствия ошибки, элемент И 12, элемент 13 задержки, элемент ИЛИ 14, триггер 15 ошибки.

Устройство работает следуюш,им образом.

К входам и выходам устройства подключается контролируемый блок (трансмиттер) 6, в который заправлена перфолента с перфорацией, информация которой идентична информации, выдаваемой формирователем 7 эталонных сигналов.

Импульсы с генератора 2 через открытый элемент И 3 поступают на вход элемента 10 запрета, в котором осуществляется опрос результатов сравнения сигналов с блока 6 и формирователя 7 эталонных сигналов. После окончания опроса через элемент 5 задержки запускаются формирователь 4 импульса, обеспечивающий переход блока 6 на чтение следующей строки перфоленты, и формирователь 7 эталонных сигналов, переходящий в следующее состояние.

Если блок б исправен, результат сравнения в схеме 9 положительный. При этом элемент 10 запрета закрыт, триггер 11 в исходном состоянии, сигнал с его выхода поддерживает открытое состояние элемента И 3, разрешая прохождение очередных импульсов запуска.

Если сигналы с блока 6 отличаются от сигналов с формирователя 7, результат сравнения в схеме 9 отрицательный, элемент 10 запрета открывается и пропускает импульс опроса, который запускает триггер 11, после чего происходит обнаружение сбоя механизма протяжки.

Сбой механизма протяжки приводит к тому, что в узле считывания блока 6 остается предыдущая строка перфоленты, в то время как формирователь 7 переходит в следующее состояние. Поэтому для обнаружения сбоя протяжки необходимо вернуть формирователь 7 в предыдущее состояние и произвести дополнительное сравнение сигналов с контролируемого блока 6 и формирователя эталонных сигналов, которое в случае сбоя протяжки должно дать положительный результат.

Сигнал ошибки с выхода элемента 10 запрета поступает на реверсирующий вход формирователя 7, который при этом возвращается в предыдущее состояние (формирователь 7 может быть выполнен, например.

на основе счетчика, работающего в режиме сложения и вычитания).

Кроме того, сигнал ошибки через элемент 13 задержки (на время реверса формирователя 7) поступает на вход элемента И 12, в котором осуществляется опрос результата дополнительного сравнения с предыдущим состоянием формирователя 7. Если результат дополнительного сравнения положительный (имеет место сбой протяжки), импульс опроса с выхода элемента 13 задержки через открытый элемент И 12 запускает триггер 15, регистрирующий сбой протяжки, и через элемент ИЛИ 14 сбрасывает триггер 11, который открывает элемент И 3, разрещая дальнейший контроль трансмиттера - блока 6.

Если результат дополнительного сравнения отрицательный, импульс опроса через закрытый элемент И 12 не проходит, триггер 15 остается в исходном состоянии, триг гер 11 не сбрасывается, удерживая в закрытом состоянии элемент И 3, запрещая проверку трансмиттера до устранения причин ошибки считыва ния.

5Формула изобретения

1. Устройство для контроля логического блока, содержащее блок управления, формирователь эталонных сигналов и блок регистрации ошибок, причем первый выход блока управления является выходом устрой0 ства для подключения к синхровходу контролируемого блока, а второй и третий выходы подключены соответственно к входу формирователя эталонных сигналов и разрешающему входу блока регистрации ощибок, первая группа информационных входов ко5 торого является группой входов устройства для подключения к выходам контролируемого блока, а вторая группа информационных входов соединена с группой входов фор.ми- рователя эталонных сигналов, выход отсутQ ствия ошибки блока регистрации ощибок соединен с разрешающим входом блока управления, отличающееся тем, что, с целью повышения достоверности контроля и быстродействия, оно содержит элемент И, элемент ИЛИ, элемент задержки и триггер

5 ошибки, а блок регистрации ошибок содержит схему сравнения, элемент запрета и триггер отсутствия ошибки, причем первая и вторая группы входов схемы сравнения образуют первую и вторую группы информационных входов блока регистрации оши0 бок, разрешающий вход и выход отсутствия ошибки которого подключены соответственно к первому входу элемента запрета и нулевому выходу триггера отсутствия ошибки, выход схемы сравнения соединен с вторым

е входом элемента запрета и первым входом элемента И, второй вход которого соединен с выходом элемента задержки, а выход соединен с первым входом элемента ИЛИ и единичным входом триггера ошибки, нулевой

3 13833614

вход которого и второй вход элемента ИЛИимпульсов, элемент И, элемент задержки

объединены и являются входом сброса уст-и формирователь импульса, причем выход

ройства, выход элемента запрета соединенгенератора импульсов соединен с первым

с единичным входом триггера отсутствиявходом элемента И, второй вход которого

ошибки, входом элемента задержки и входом5 является разрешающим входом блока, а вывозврата формирователя эталонных сигна-ход - третьим выходом блока, и через элелов, выход элемента ИЛИ соедннен с входоммент задержки соединен с входом формиросброса триггера отсутствия ошибки.вателя импульса, выход которого и выход

2. Устройство по п. 1, отличающееся тем,элемента задержки являются соответственно

что блок управления содержнт генераторпервым и вторым выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации сигналов неисправности | 1979 |

|

SU864290A1 |

| Устройство для контроля работы трансмиттера | 1980 |

|

SU926660A1 |

| Устройство для регистрации сигналов неисправности | 1987 |

|

SU1495802A1 |

| Устройство для контроля знаний оператора | 1985 |

|

SU1256077A2 |

| Трансмиттер | 1980 |

|

SU944141A1 |

| Устройство для контроля клавиатуры | 1986 |

|

SU1432525A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1304027A1 |

| Устройство для контроля логических блоков | 1980 |

|

SU902018A1 |

| Устройство для передачи дискретной информации | 1982 |

|

SU1078660A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

Изобретение относится к автоматике, вычислительной технике и связи. Цель изобретения состоит в повышении достоверности контроля и быстродействия за счет обнаружения сбоев в работе механизма протяжки перфоленты. Цель достигается введением элемента 13 задержки, элементов И 12, ИЛИ 14, триггера 15, которые позволяют реверсировать формирователь 7 эталонных сигналов и осуществлять дополнительное сравнение для обнаружения сбоев механизма протяжки. В случае обнаружения сбоя протяжки осуществляется автоматический запуск устройства, благодаря чему исключается останов и повыщается быстродействие контроля. 1 3. п. ф-лы, 1 ил.

Авторы

Даты

1988-03-23—Публикация

1986-10-15—Подача