I

Изобретение относится к вычислительной технике, в частности к устройствам для обнаружения ошибок и контроля логических блоков.

Известно устройство для обнаружения ошибок в выходной последовательности цифровых узлов, содержащее регистр сдвига и сумматор по модулю два в цепи обратной связи, вход сумматора подключен к выходу контролируемого узла, выходы регистра через де- шифратор подключены к индикатору эталонных сигнатур 1 .

Недостатком данного устройства является то, что оно обеспечивает возможность контроля информации только одного из каналов контролируемого цифрового блока.

Наиболее близким к предлагаемому устройству является устройство для контроля цифровых блоков, содержащее генератор тестов, выходы которого подключены ко входу блока управления Ик входам эталонного и контролируемого блоков, выходы которых через блок сравнения подключены к блоку регистрации и индикации, шйходы эталон ного блока через блок пирамидальной свертки по модулю два подключены к одному из входов сумматора, который включен в цепь обратной связи регистра сдвига, выхо/ регистра через дешифратор подключены к индикатору исправности эталонного блока, а выходы

10 блока управления соединены с управляющим входом генератора тестов и регистра сдвига f 2.

Недостатком известного устройства является невозможность обнаружения

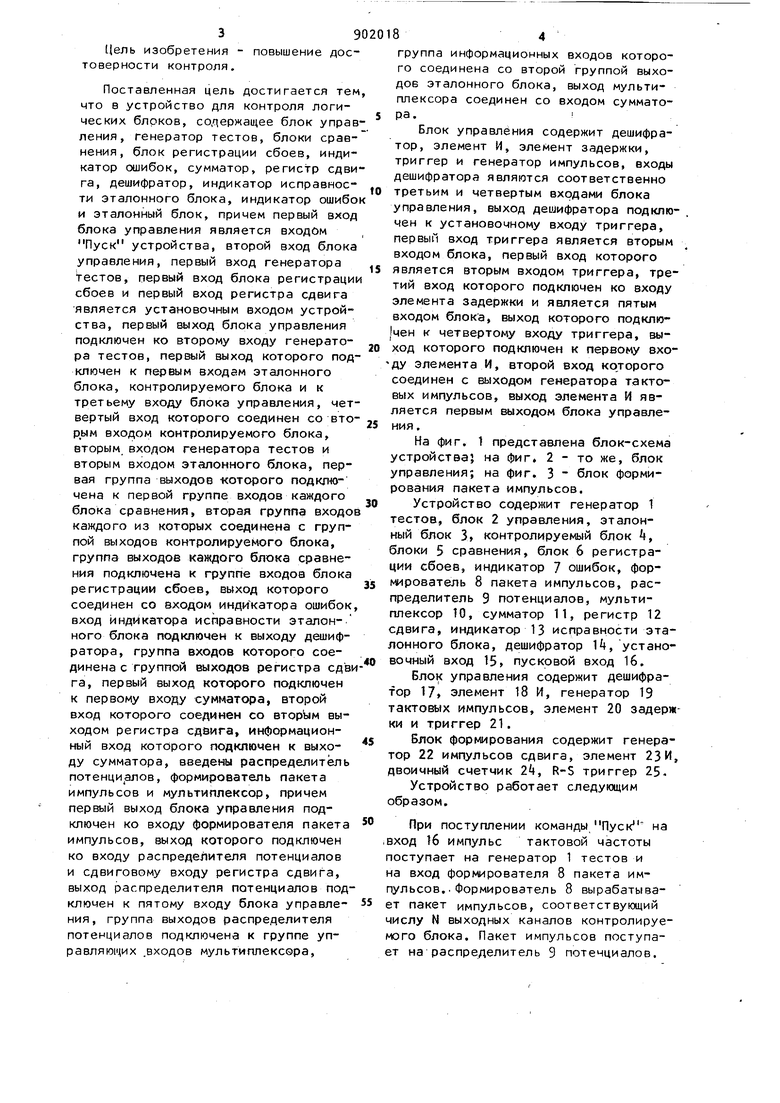

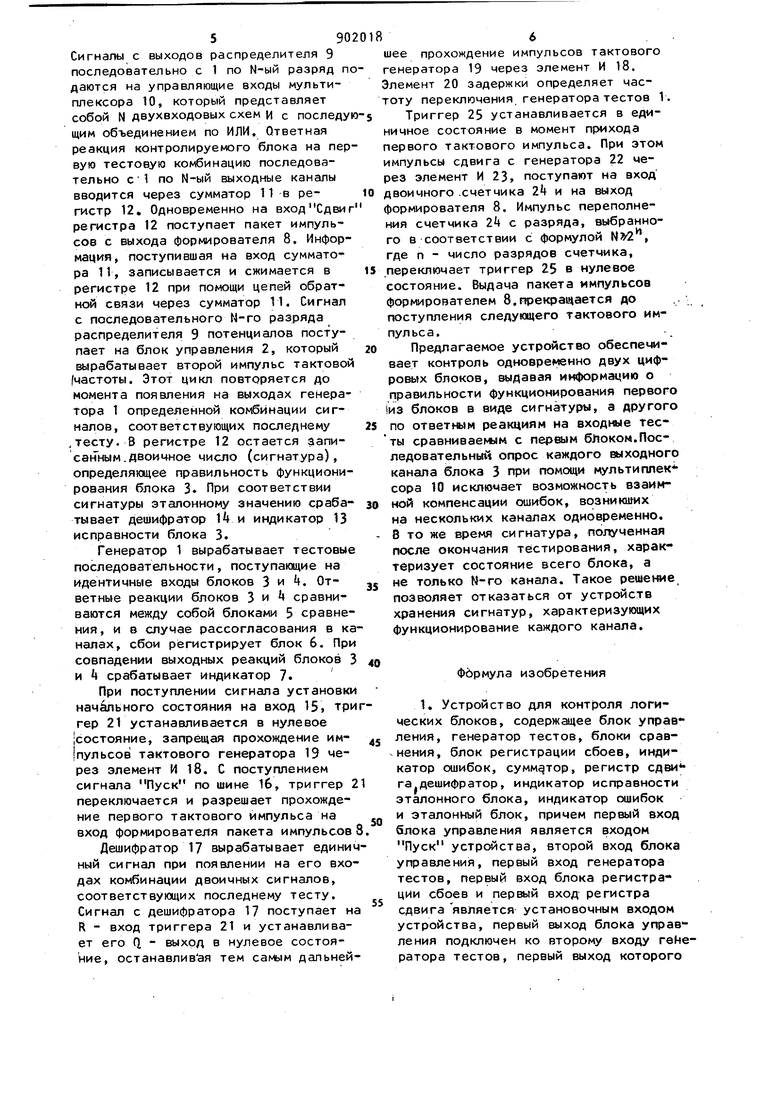

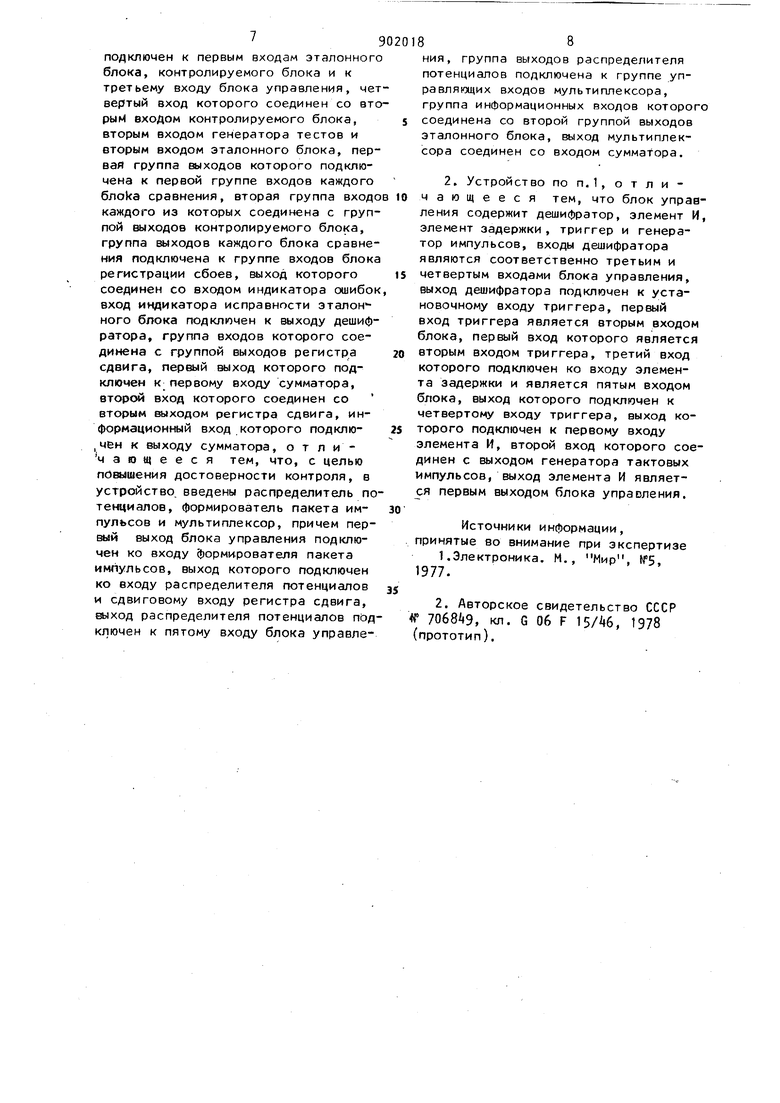

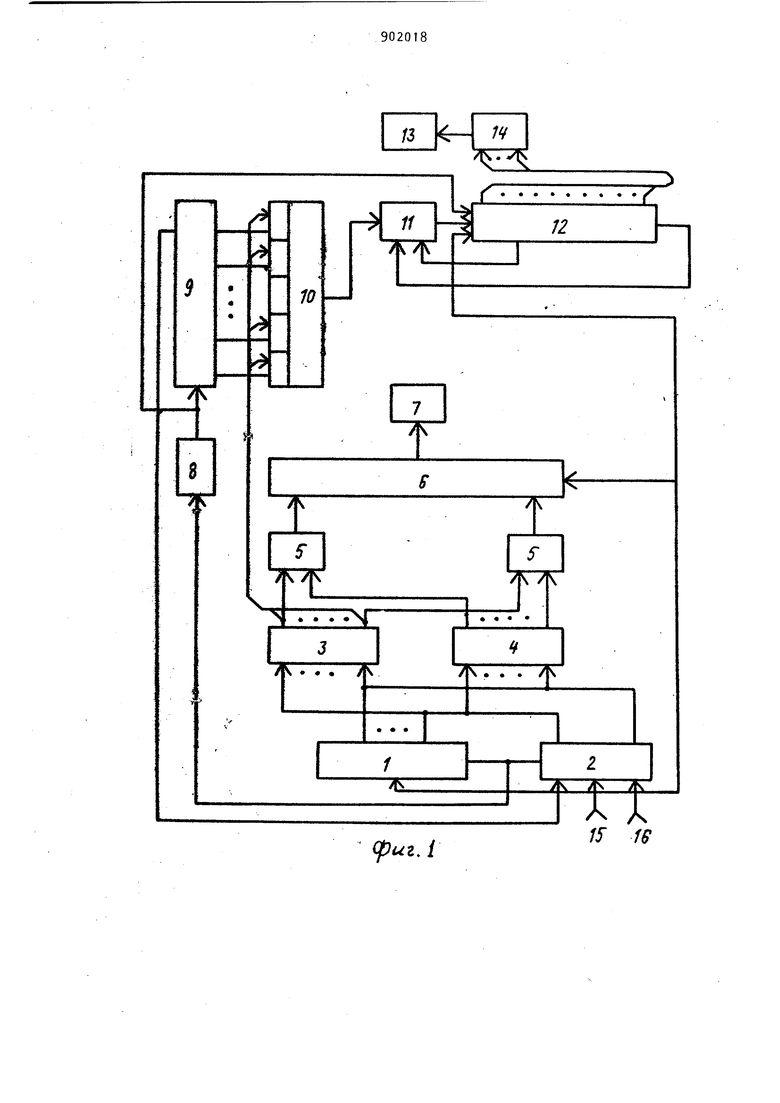

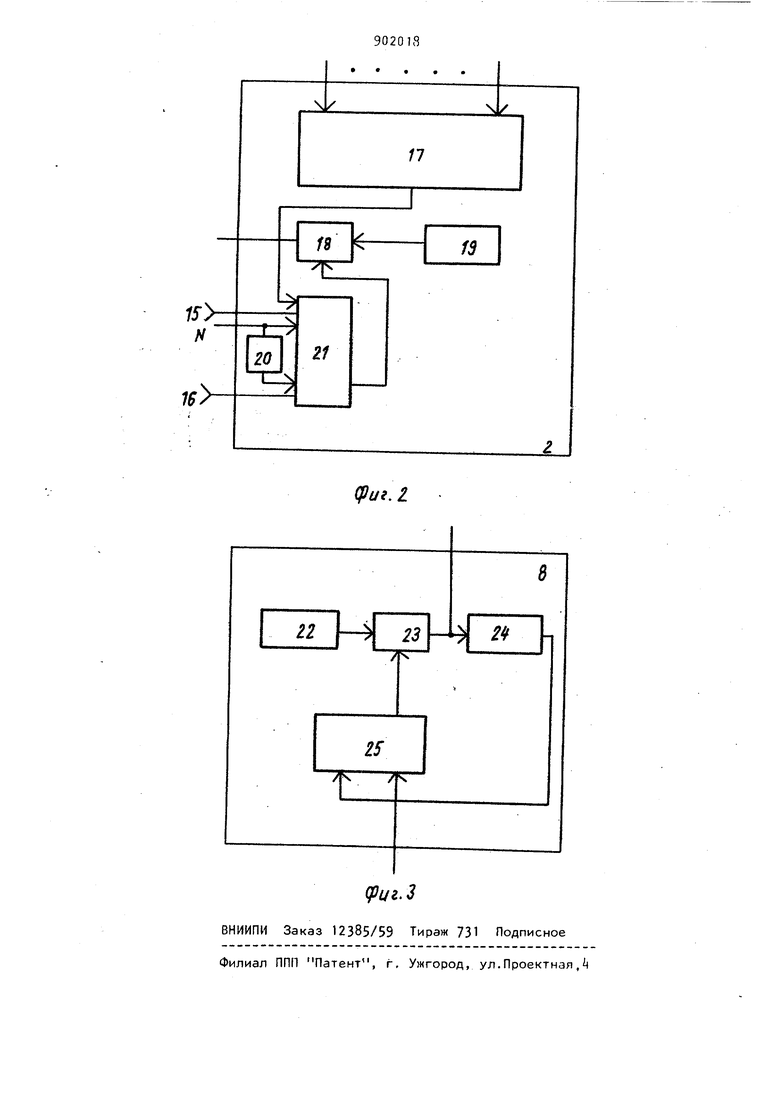

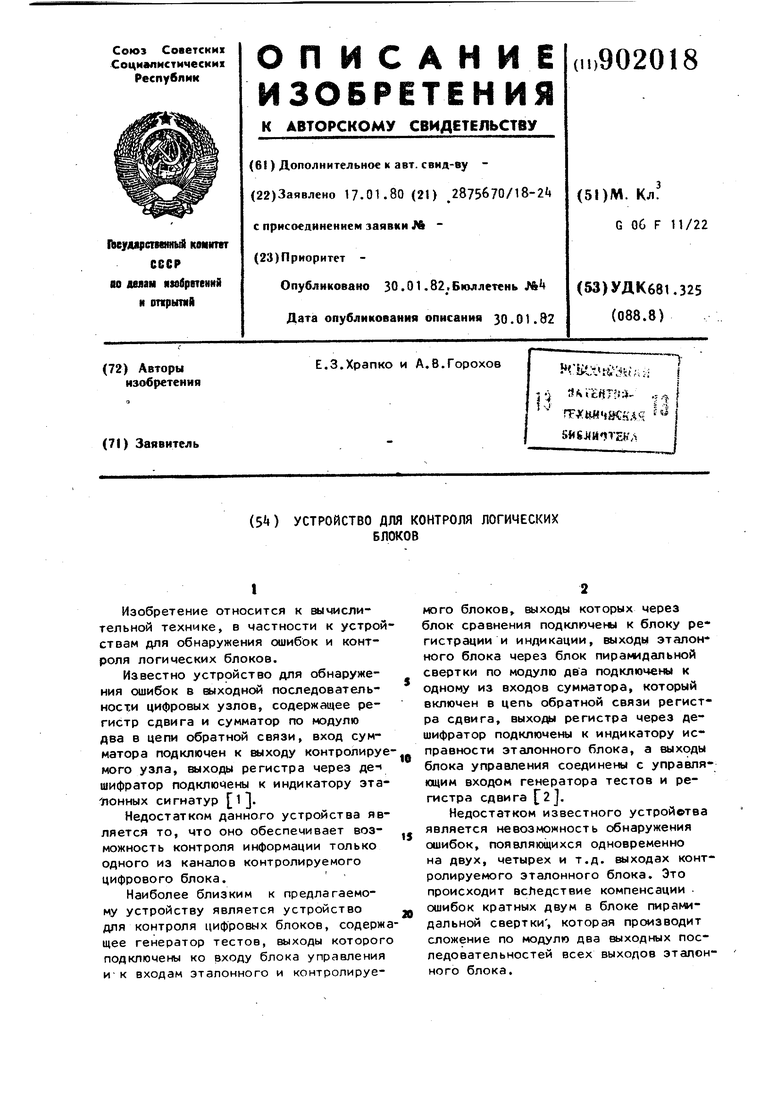

IS ошибок, появляющихся одновременно на двух, четырех и т.д. выходах контролируемого эталонного блока. Это происходит вследствие компенсации ошибок кратных двум в блоке пирамидальной свертки , которая производит сложение по модулю два выходных последовательностей всех выходов эталонного блока. 3 Цель изобретения - повышение дос товерности контроля. Поставленная цель достигается тем что 8 устройство для контроля логических блоков, содержащее блок управ ления, генератор тестов, блоки сравнения, блок регистрации сбоев, индикатор ошибок, сумматор, регистр сдви га, дешифратор, индикатор исправноети эталонного блока, индикатор ошибо и эталонный блок, причем первый вход блока управления является входом Пуск устройства, второй вход блока управления, первый вход генератора tecTOB, первый вход блока регистраци сбоев и первый вход регистра сдвига является установочным входом устройства, первый выход блока управления подключен ко второму входу генератора тестов, первый выход которого под ключен к первым входам эталонного блока, контролируемого блока и к третьему входу блока управления, чет вертый вход которого соединен со вто рым входом контролируемого блока, вторым входом генератора тестов и вторым входом эталонного блока, первая группа выходов которого подктшмена к первой группе входов каждого блока сравнения, вторая группа входо каждого из которых соединена с группой выходов контролируемого блока, группа выходов каждого блока сравнения подключена к группе входов блока регистрации сбоев, выход которого соединен со входом индикатора ошибок вход индикатора исправности эталонного блока подключен к выходу дешифратора, группа входов которого соединена с группой выходов регистра сдв га, первый выход которого подключен к первому входу сумматора, второй вход которого соединен со втором выходом регистра сдвига, информационный вход которого подключен к выходу сумматора, введены распределитель потенци алов, формирователь пакета импульсов и мультиплексор, причем первый выход блока управления подключен ко входу формирователя пакета импульсов, выход которого подключен ко входу распределителя потенциалов и сдвиговому входу регистра сдвига, выход распределителя потенциалов под ключен к пятому входу блока управления, группа выходов распределителя потенциалов подключена к группе управляющих .входов мультиплексера. 84 группа информационных входов которого соединена со второй группой выходов эталонного блока, выход мультиплексора соединен со входом сумматора. Блок управления содержит дешифратор, элемент И, элемент задержки, триггер и генератор импульсов, входы дешифратора являются соответственно третьим и четвертым входами блока управления, выход дешифратора подключен к установочному входу триггера, первый вход триггера является вторым входом блока, первый вход которого является вторым входом триггера, третий вход которого подключен ко входу элемента задержки и является пятым входом блока, выход которого подклю1чен к четвертому входу триггера, выход которого подключен к первому вхоДУ элемента И, второй вход ко.торого соединен с выходом генератора тактовых импульсов, выход элемента И является первым выходом блока управления. На фиг. 1 представлена блок-схема устройства; на фиг, 2 - то же, блок управления; на фиг. 3 - блок формирования пакета импульсов. Устройство содержит генератор тестов, блок 2 управления, эталонный блок 3, контролируемый блок Ц, блоки 5 сравнения, блок 6 регистрации сбоев, индикатор 7 ошибок, формирователь 8 пакета импульсов, распределитель 9 потенциалов, мультиплексор 10, сумматор 11, регистр 12 сдвига, индикатор 13 исправности эталонного блока, дешифратор 14, установочный вход 15, пусковой вход 16. Блок управления содержит дешифраfop 17 элемент 18 И, генератор 19 тактовь1Х импульсов, элемент 20 задержки и триггер 21. Блок формирования содержит генератор 22 импульсов сдвига, элемент 23 И, двоичный счетчик 2, R-S триггер 25. Устройство работает следующим образом. При поступлении команды на вход 16 импульс тактовой частоты поступает на генератор 1 тестов и на вход формирователя 8 пакета импульсов.. Формирователь 8 вырабатывает пакет импульсов, соответствующий числу N выходных каналов контролируемого блока. Пакет импульсов поступает на распределитель 9 потенциалов. Сигналы с выходов распределителя 9 последовательно с 1 по N-ый разряд п даются на управляющие входы мультиплексора 10, который представляет собой N двухвходовых схем и с последу щим объединением по ИЛИ. Ответная реакция контролируемого блока на пер вую тестовую комбинацию последовательно с1 по N-ый выходные каналы вводится через сумматор 11 в регкстр 12, Одновременно на вход Сдви регистра 12 поступает пакет импульсов с выхода формирователя 8, Инфор мация, поступившая на вход сумматора IV, записывается и сжимается в регистре 12 при помощи цепей обратной связи через сумматор 11. Сигнал с последовательного М-го разряда распределителя 9 потенциалов поступает на блок управления 2, который вырабатывает второй импульс тактово (частоты. Этот цикл повторяется до момента появления на выходах генератора 1 определенной кo бйнaции сигналов, соответствующих последнему ,тесту. В регистре 12 остается записанным, двоичное число (сигнатура), определяющее правильность функциони рования блока 3. При соответствии сигнатуры эталонному значению срабатывает дешифратор И и индикатор 13 исправности блока 3. Генератор 1 вырабатывает тестовы последовательности, поступающие на идентичные входы блоков 3 и . Ответные реакции блоков 3 и сравниваются между собой блоками 5 сравне ния, и в случае рассогласования в к налах, сбои регистрирует блок 6. Пр совпадении выходных реакций блоков и k срабатывает индикатор 7. При поступлении сигнала установк начального состояния на вход 15, тр гер 21 устанавливается в нулевое 1состояние, запрадая прохождение им пульсов тактового генератора 19 через элемент И 18. С поступлением сигнала Пуск по шине 16, триггер переключается и разрешает прохождение первого тактового импульса на вход формирователя пакета импульсов Дешифратор 17 вырабатывает едини ный сигнал при появлении на его вхо дах комбинации двоичных сигналов, соответствующих последнему тесту. Сигнал с дешифратора 17 поступает н R - вход триггера 21 и устанавливает его Q - выход в нулевое состояние, останавливая тем самым дальней шее прохождение импульсов тактового енератора 19 через элемент И 18. лемент 20 задержки определяет часоту переключения генератора тестов 1. Триггер 25 устанавливается в едиичное состояние в момент прихода ервого тактового импульса. При этом мпульсы сдвига с генератора 22 чеез элемент И 23, поступают на вход воичного .счетчика 2 и на выход ормирователя 8. Импульс переполнения счетчика 2 с разряда, выбранного в соответствии с; формулой , где п - число разрядов счетчика, переключает триггер 25 в нулевое состояние. Выдача пакета импульсов формирователем 8,пре1фаи1ается до поступления следующего тактового импульса. Предлагаемое устройство o6ecnei iвает контроль одновременно двух цифpoBbtx блоков, выдавая информацию о гравильности функционирования первого из блоков в виде сигнатуры, а другого по ответным реакциям на входные тесты сравниваемым с первым блоком.Последовательный опрос каждого выходного канала блока 3 при помощи мультиппек сора 10 исключает возможность взаим ной компенсации ошибок, возникших на нескольких каналах одновременно. 8 то же время сигнатура, полученная после окончания тестирования, характеризует состояние всего блока, а не только М-го канала. Такое решение позволяет отказаться от устройств хранения сигнатур, характеризующих функционирование каждого канала. ФЬрмула изобретения 1, Устройство для контроля логических блоков, содержащее блок управления, генератор тестов, блоки срав нения, блок регистрации сбоев, индикатор ошибок, сумматор, регистр дешифратор, индикатор исправности эталонного блока, индикатор ошибок и эталонный блок, причем первый вход блока управления является входом Пуск устройства, второй вход блока управлени)я, первый вход генератора тестов, первый вход блока регистрации сбоев и первый вход регистра сдвига является установочным входом устройства, первый выход блока управления подключен ко второму входу геМератора тестов, первый выход которого 9 подключен к первым входам эталонного блока, контролируемого блока и к третьему входу блока управления, чет вертый вход которого соединен со вто рыИ входом контролируемого блока, вторым входом генератора тестов и вторым входом эталонного блока, первая группа выходов которого подключена к первой группе входов каждого блоКа сравнения, вторая группа входо каждого из которых соединена с группой выходов контролируемого блока, группа выходов каждого блока сравнения подключена к группе входов блока регистрации сбоев, выход которого соединен со входом индикатора ошибок вход индикатора исправности эталонного блока подключен к выходу дешифратора, группа входов которого соединена с группой выходов регистра сдвига, первый выход которого подключен к первому входу сумматора, второй вход которого соединен со вторым выходом регистра сдвига, информационный вход которого подклю,чен к выходу сумматора, о т л и чающееся тем, что, с целью повышения достоверности контроля, в устройство введены распределитель по тенциалов, формирователь пакета импульсов и мультиплексор, причем пери й выход блока управления подключен ко входу формирователя пакета импульсов, выход которого подключен ко входу распределителя потенциалов и сдвиговому входу регистра сдвига, выход распределителя потенциалов под ключен к пятому входу блока управле88ния, группа выходов распределителя потенциалов подключена к группе управляющих входов мультиплексора, группа информационных входов которого соединена со второй группой выходов эталонного блока, выход мультиплексора соединен со входом сумматора. 2. Устройство по п.1, о т л и чающееся тем, что блок управления содержит дешифратор, элемент И, элемент задержки , триггер и генератор импульсов, входы дешифратора являются соответственно третьим и четвертым входами блока управления, выход дешифратора подключен к установочному входу триггера, первый вход триггера является вторым входом блока, первый вход которого является вторым входом триггера, третий вход которого подключен ко входу элемента задержки и является пятым входом блока, выход которого подключен к четвертому входу триггера, выход которого подключен к первому входу элемента И, второй вход которого соединен с выходом генератора тактовых импульсов, выход элемента И является первым выходом блока управления. Источники информации, принятые во внимание при экспертизе 1.Электроника. М., Мир, №5, 1977. 2. Авторское свидетельство СССР , кл. G 06 F 15/46, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для функционально-параметрического контроля логических элементов | 1983 |

|

SU1157544A1 |

| Устройство для контроля логических узлов | 1980 |

|

SU890398A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1160417A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля цифровых блоков | 1978 |

|

SU706849A1 |

| Устройство для диагностики неисправностей логических блоков | 1987 |

|

SU1520548A1 |

| Устройство для локализации ошибок в двоичной последовательности | 1988 |

|

SU1566354A1 |

| Устройство для контроля лоических блоков | 1986 |

|

SU1453409A1 |

15 1В

(puz.i

П

(ui,2.

2

23

74 Ч

Авторы

Даты

1982-01-30—Публикация

1980-01-17—Подача