Изобретение относится к .вычислительной технике и может быть использовано для контроля цифровых узлов.

Цель изобретения - повышение достоверности контроля, а также рас- птрение функциональных возможностей за счет обеспечения 1 ;онтроля после- довательностных узлов.

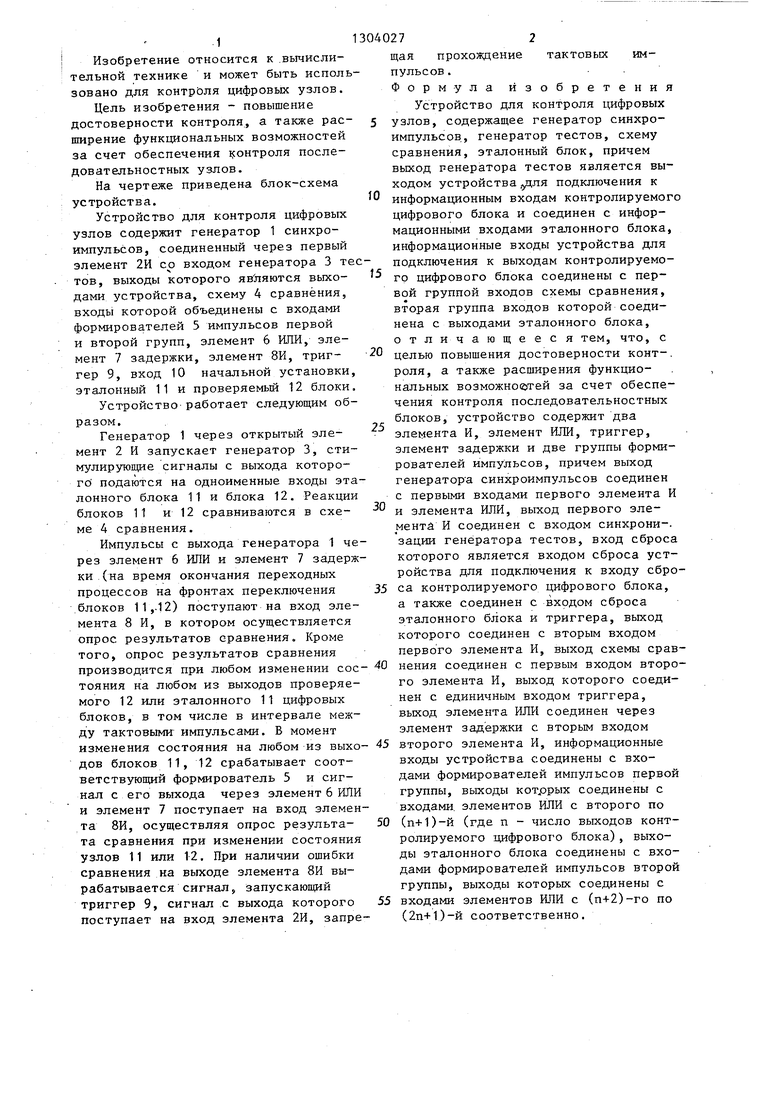

На чертеже приведена блок-схема устройства.

Устройство для контроля цифровых узлов содержит генератор 1 синхроимпульсов, соединенный через первый элемент 2И со входом генератора 3 тестов, выходы которого яв ляются выходами устройства, схему 4 сравнения, входь которой объединены с входами формирователей 5 импульсов первой и второй групп, элемент 6 ИЛИ, элемент 7 задержки, элемент 8И, триггер 9, вход 10 начальной установки, эталонный 11 и проверяемый 12 блоки.

Устройство работает следующим образом.

Генератор 1 через открытый элемент 2 И запускает генератор 3, стимулирующие сигналы с выхода которо- гб подаются на одноименные входы эталонного блока 11 и блока 12. Реакции блоков 11 и 12 сравниваются в схеме 4 сравнения.

Импульсы с выхода генератора 1 через элемент 6 ИЛИ и элемент 7 задержки (на время окончания переходных процессов на фронтах переключения блоков 11,.12) поступают на вход элемента 8 И, в котором осуществляется опрос результатов сравнения. Кроме того, опрос результатов сравнения

10

J5

щая прохо5вдение тактовых импульсов .. . Формула изобретения

Устройство для контроля цифровых узлов, содержащее генератор синхроимпульсов, генератор тестов, схему сравнения, эталонный блок, причем выход генератора тестов является выходом устройства уЧля подключения к информационным входам контролируемого цифрового блока и соединен с информационными входами эталонного блока, информационные входы устройства для подключения к выходам контролируемого цифрового блока соединены с первой группой входов схемы сравнения, вторая группа входов которой соединена с выходами эталонного блока, отличающееся тем, что, с целью повыщения достоверности конт-. роля, а также расширения функциональных возможностей за счет обеспечения контроля последовательностных блоков, устройство содержит два элемента И, элемент ИЛИ, триггер, элемент задержки и две группы формирователей импульсов, причем выход генератор а синхроимпульсов соединен с первыми входами первого элемента И и элемента ИЛИ, выход первого элемента И соединен с входом синхрони-. зации генератора тестов, вход сброса которого является входом сброса устройства для подключения к входу сбро- 35 са контролируемого цифрового блока, а также соединен с входом сброса эталонного блока и триггера, выход которого соединен с вторым входом первого элемента И, выход схемы срав20

25

30

го элемента И, выход которого соединен с единичным входом триггера, выход элемента ИЛИ соединен через элемент задержки с вторым входом

производится при любом изменении сое- нения соединен с первым входом второ- тояния на любом из выходов проверяемого 12 или эталонного 11 цифровых блоков, в том числе в интервале между тактовыми импульсами. В момент

изменения состояния на любом из выхо- 45 второго элемента И, информационные дов блоков 11, 12 срабатывает соот- входы устройства соединены с входами формирователей импульсов первой группы, выходы котррых соединены с входами, элементов ИЛИ с второго по 50

ветствутощий формирователь 5 и сигнал с его выхода через элемент 6 ИЛИ и элемент 7 поступает на вход элемента 8И, осуществляя опрос результата сравнения при изменении состояния узлов 11 или 12. При наличии ошибки сравнения на выходе элемента 8И вырабатывается сигнал, запускающий триггер 9, сигнал с выхода которого поступает на вход элемента 2И, запре(п+1)-й (где п - число выходов контролируемого :вдфрового блока), выходы эталонного блока соединены с входами формирователей импульсов второй группы, выходы которых соединены с 55 входами элементов ИЛИ с (п+2)-го по (2п+1)-й соответственно.

5

щая прохо5вдение тактовых импульсов .. . Формула изобретения

Устройство для контроля цифровых узлов, содержащее генератор синхроимпульсов, генератор тестов, схему сравнения, эталонный блок, причем выход генератора тестов является выходом устройства уЧля подключения к информационным входам контролируемого цифрового блока и соединен с информационными входами эталонного блока, информационные входы устройства для подключения к выходам контролируемого цифрового блока соединены с первой группой входов схемы сравнения, вторая группа входов которой соединена с выходами эталонного блока, отличающееся тем, что, с целью повыщения достоверности конт-. роля, а также расширения функциональных возможностей за счет обеспечения контроля последовательностных блоков, устройство содержит два элемента И, элемент ИЛИ, триггер, элемент задержки и две группы формирователей импульсов, причем выход генератор а синхроимпульсов соединен с первыми входами первого элемента И и элемента ИЛИ, выход первого элемента И соединен с входом синхрони-. зации генератора тестов, вход сброса которого является входом сброса устройства для подключения к входу сбро- 5 са контролируемого цифрового блока, а также соединен с входом сброса эталонного блока и триггера, выход которого соединен с вторым входом первого элемента И, выход схемы срав0

5

0

го элемента И, выход которого соединен с единичным входом триггера, выход элемента ИЛИ соединен через элемент задержки с вторым входом

нения соединен с первым входом второ-

второго элемента И, информационные входы устройства соединены с входами формирователей импульсов первой группы, выходы котррых соединены с входами, элементов ИЛИ с второго по

(п+1)-й (где п - число выходов контролируемого :вдфрового блока), выходы эталонного блока соединены с входами формирователей импульсов второй группы, выходы которых соединены с входами элементов ИЛИ с (п+2)-го по (2п+1)-й соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1988 |

|

SU1603385A2 |

| Устройство для контроля цифровых узлов | 1987 |

|

SU1603390A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Устройство для контроля логических схем | 1986 |

|

SU1381517A1 |

| Устройство для контроля логического блока | 1986 |

|

SU1383361A1 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

| Устройство для локализации неисправностей | 1988 |

|

SU1674128A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1290333A1 |

| Устройство для локализации неисправностей | 1980 |

|

SU903888A1 |

| Формирователь тестов | 1985 |

|

SU1259271A1 |

Изобретение относится к области вычислительной техники и может быть использовано для поиска неисправностей цифровых схем. Цель изобретения повышение достоверности контроля, (Л также расширение функциональных возможностей за счет обеспечения контроля последовательностньк узлов путем осуществления дополнительного опроса результатов сравнения на всех выходах проверяемого и эталонного узлов, что позволяет предотвратить ошибочное срабатьшание элементов памяти в промежутках между тактовыми импульсами. Для достижения этой цели устройство содержит генератор синхроимпульсов-, генератор тестов, схему сравнения, группу формирователей импульсов, элемент ИЛИ, элемент задержки, элемент И и триггер. 1 ил. сл с со о о IS5

Редактор В.Ковтун

Составитель А.Сиротская

Техред М.Ходанич Корректор С.Черни

Заказ 1312/49 Тираж 673Под:шсное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для контроля цифровых блоков | 1975 |

|

SU607218A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля и диагностики цифровых блоков | 1976 |

|

SU605216A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-15—Публикация

1985-07-08—Подача