синхронизации. Кодовые посылки начала строки с этого блока через шифратор 16 и блок коммутации 4 поступают на выход устройства. С блока 2 аналого-цифрового преобразования семиразрядный параллельный код поступает на суммирующий регистр памяти (СРП) 7 непосредственно и через элемент задержки 6 (на строку), а четыре старших разряда кода нечетных отсчетов записываются в регистр памяти (РП), 10, Информация с СРП 7 переписывается последовательно в РП 8 и 9. Работа устройства зависит от результатов сравнения кодов в блоках сравнения (БС) 11-14. В БС 12 сравниваются четыре старших разряда кодов СРП 7 и РП 9 (элементы j-й строки). Если есть изменения хотя бы в одном из разрядов, то информация об истинном состоянии пяти разрядов записывается, в блок памяти 18 и поступает с РП 9 через блок коммутации 4 в канал связи. БС 13 сравнивает четыре старших разряда кодов с РП 8 и 9. (элементы соседних строк) Если БС 13 не выявляет изменений, то информация о

Изобретение относится к технике электрической связи, в частности к передаче телевизионных изображений в эвмкнутых телевизионных системах, может быть использовано для телеграфной связи в устройствах с преобразованием кода внутри передатчика, и является дополнительным к авт.св. 1146831.

Целью изобретения является умень шение искажений телевизионных сигналов.

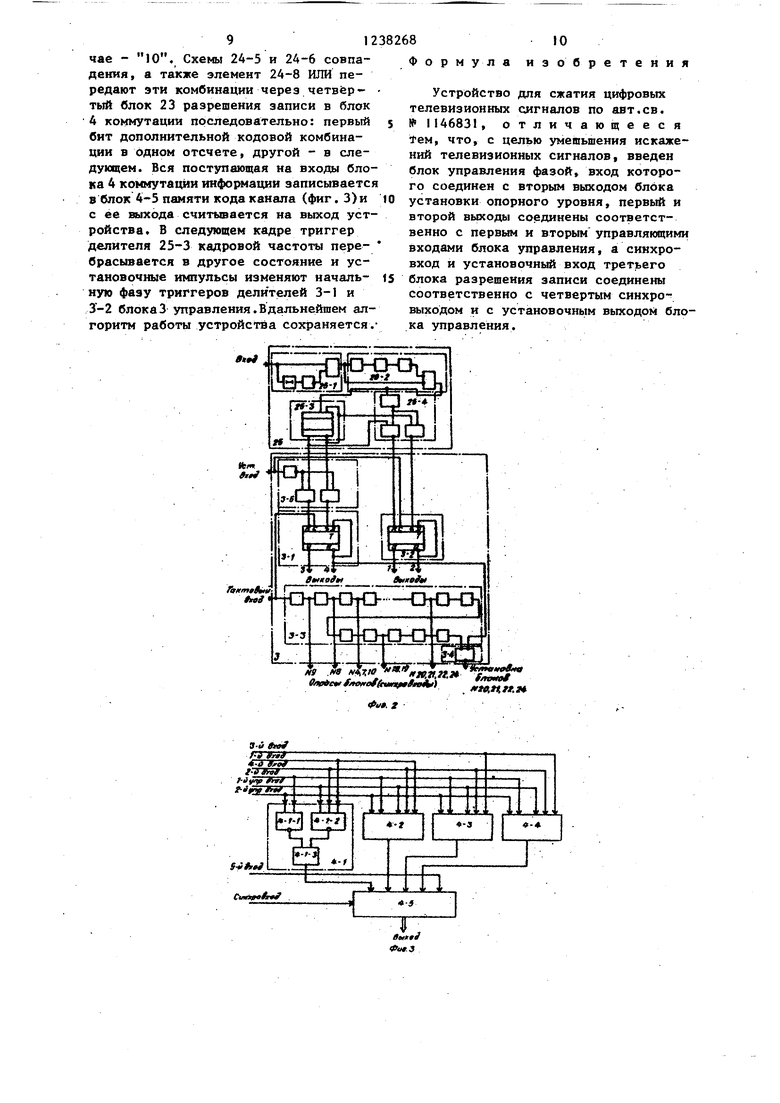

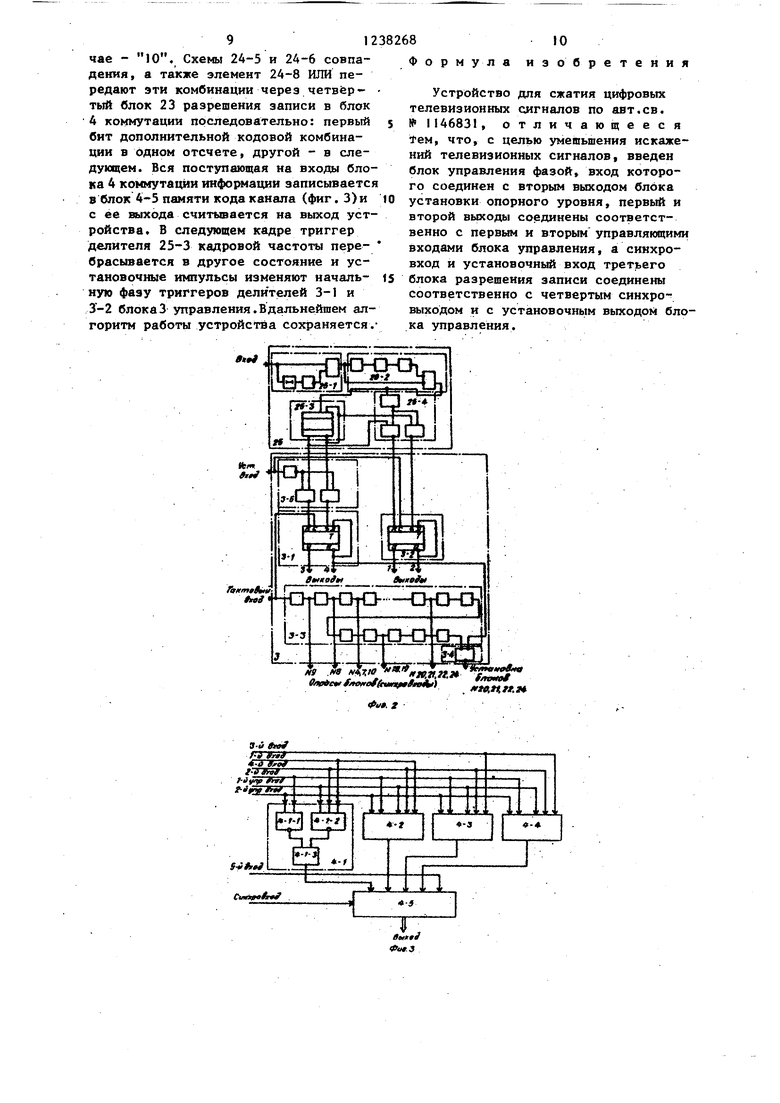

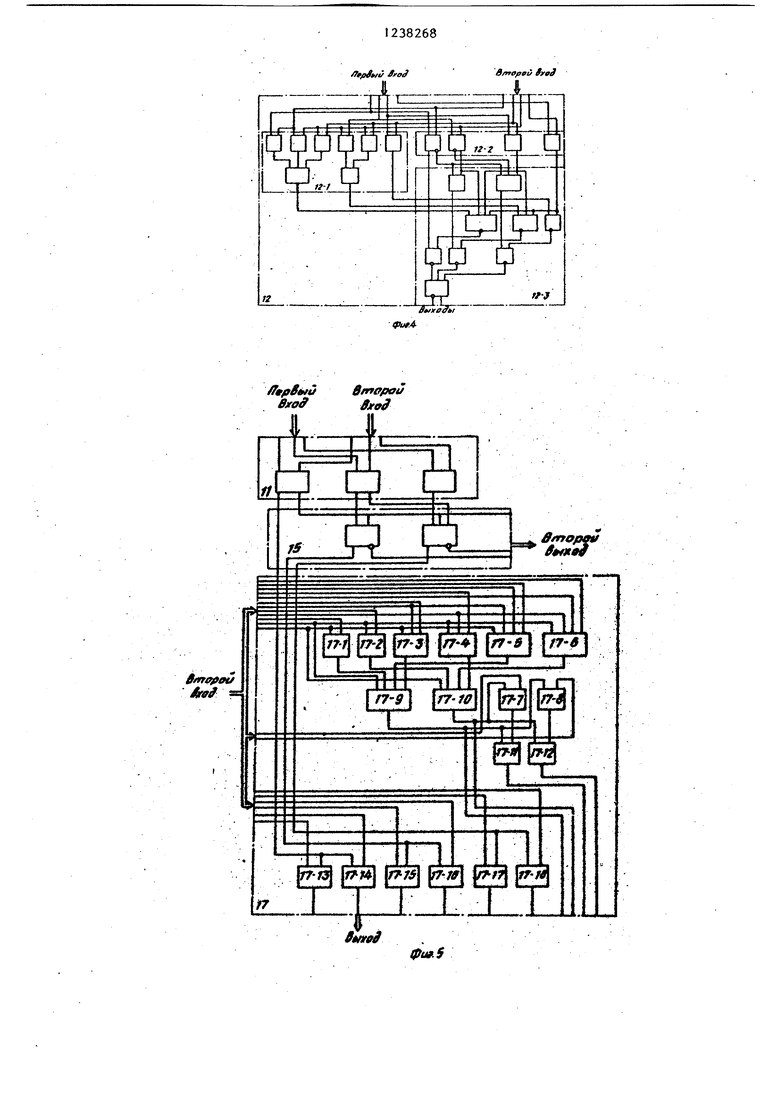

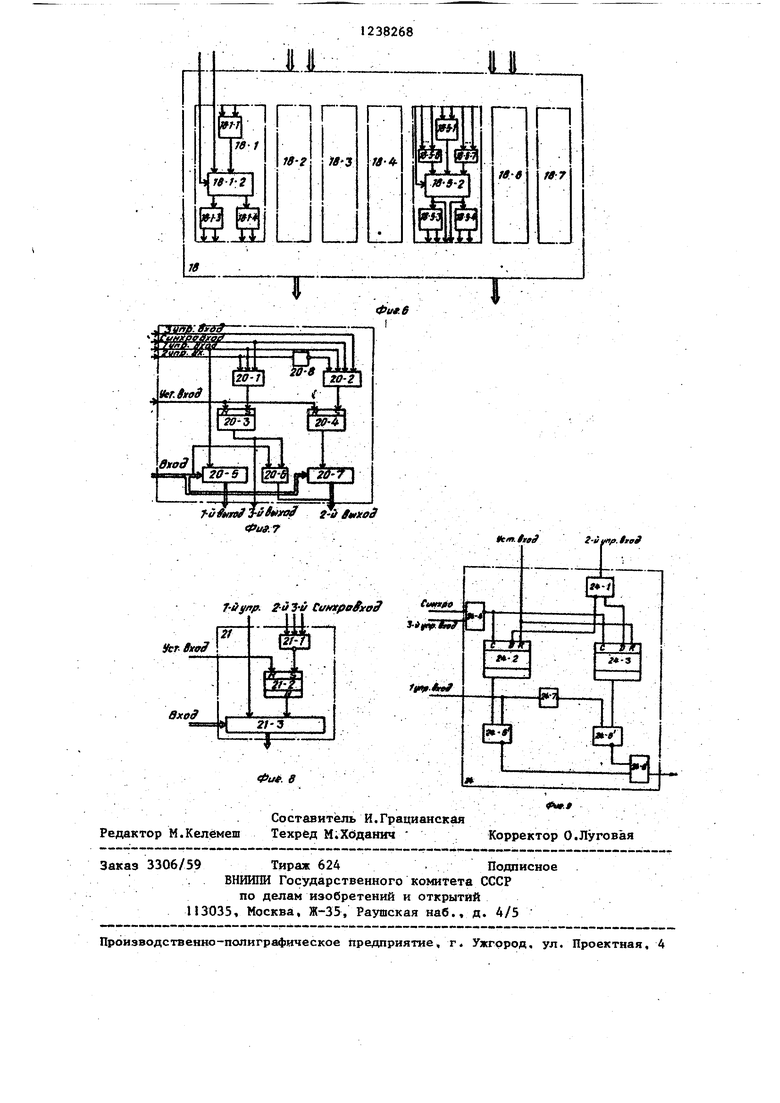

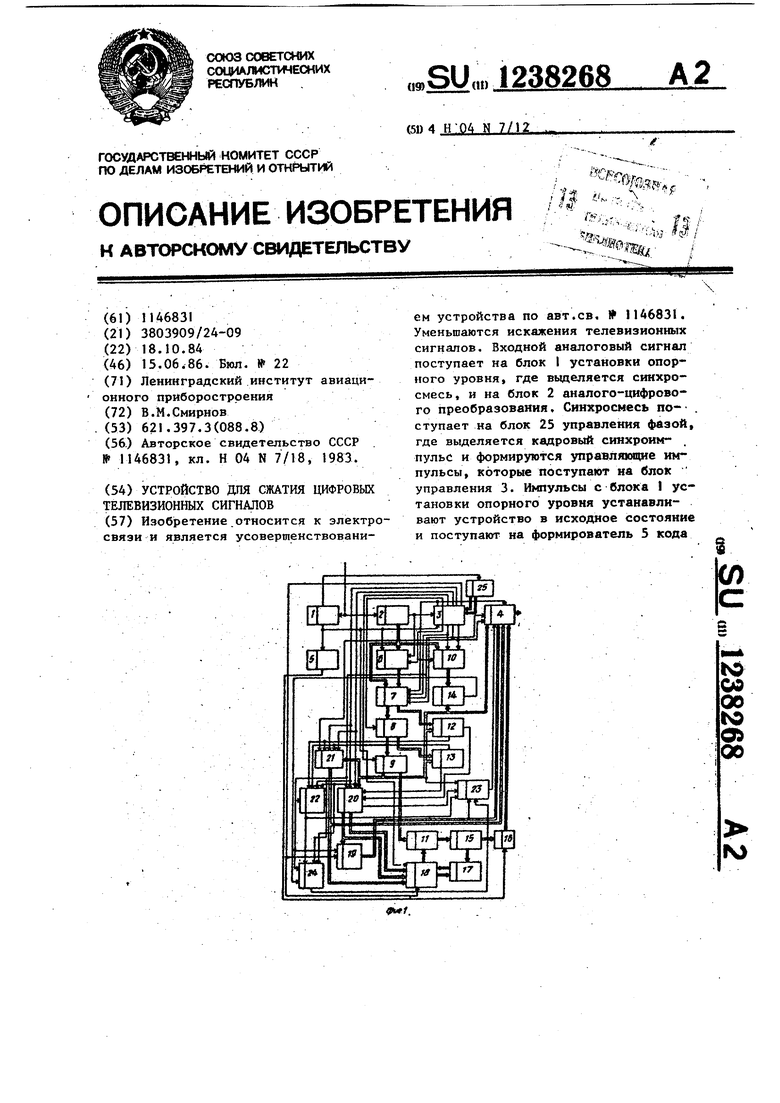

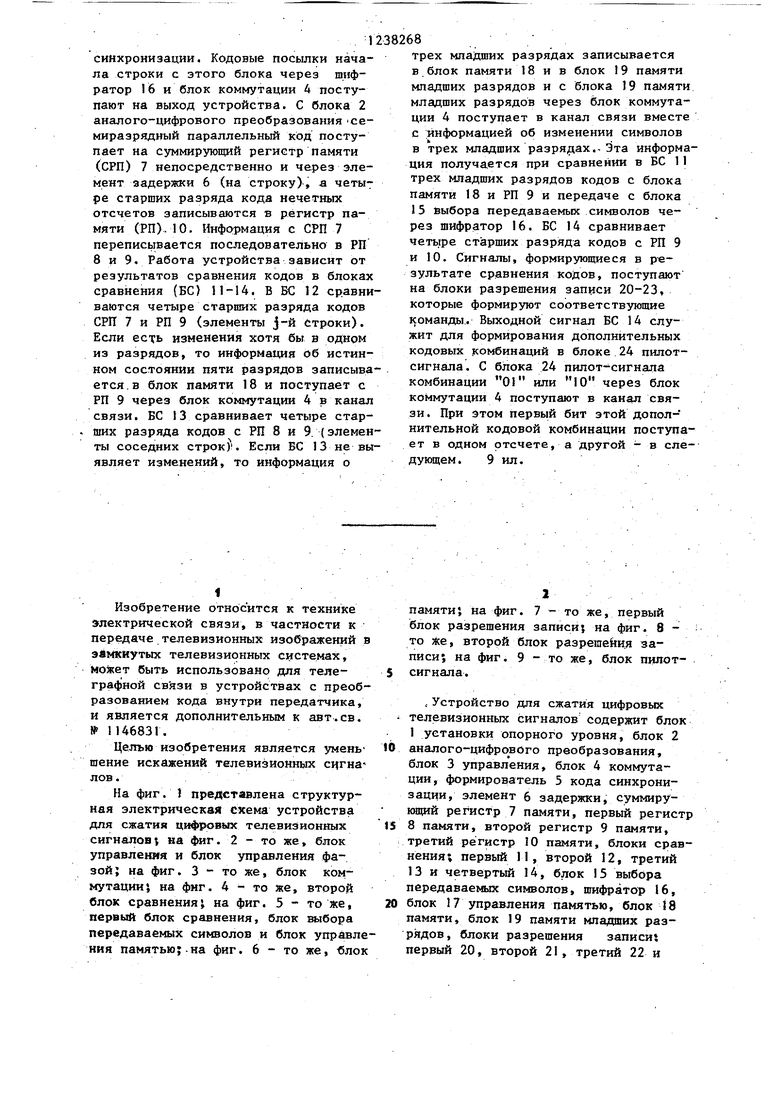

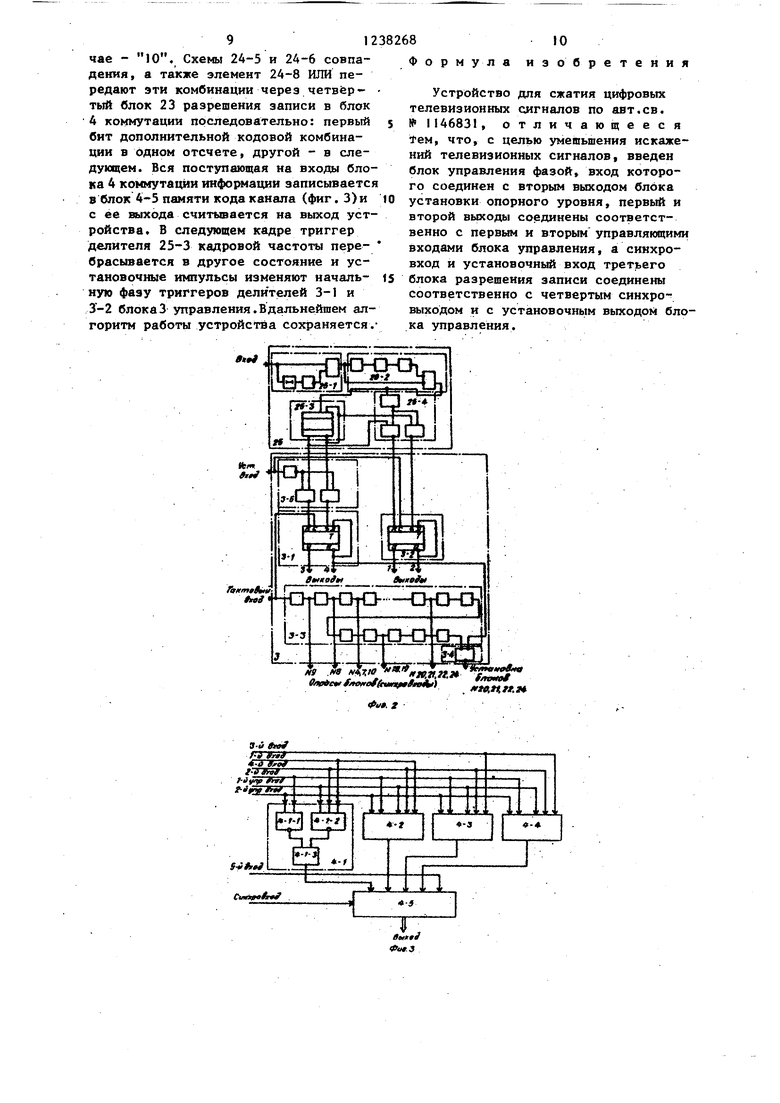

На фиг. 1 представлена структурная электрическая ехема устройства для сжатия цифровых телевизионных сигналов t на г .2 - то же, блок управления и блок управления фазой; на фиг. 3 - то же, блок коммутации} на фиг, 4 - то же, второй блок сравнения i на фиг. 5 - то же, первый блок сравнения, блок выбора передаваемых символов и блок управления памятью;-на фиг. 6 - то же, «лок

трех младших разрядах записывается в блок памяти 18 и в блок 19 памяти младших разрядов и с блока 19 памяти младших разрядов через блок коммутации 4 поступает в канал связи вместе с информацией об изменении символов в трех младших разрядах,-Эта информация получается при сравнении в БС 11 трех младших разрядов кодов с блока памяти 18 и РП 9 и передаче с блока 15 Выбора передаваемых символов через шифратор 16. БС 14 сравнивает четьфе старших разряда кодов с РП 9 и 10. Сигналы, формирующиеся в результате сравнения кодов, поступают на блоки разрешения записи 20-23, которые формируют соответствующие команды. Выходной сигнал БС 14 служит для формирования дополнительных кодовых комбинаций в блоке 24 пилот- сигнала. С блока 24 пилот-сигнала комбинации 01 или 10 через блок коммутации 4 поступают в канал связи. При этом первый бит этой допол- нительной кодовой комбинации поступает в одном отсчете, а другой - в сле- дуницем. 9 ил.

памяти; на фиг. 7 - то же, первый блок разрешения записи; на фиг. 8 - : то же, второй блок разрегаейия записи; на фиг. 9 - то же, блок пилот- сигнала.

, Устройство для сжатия цифровых

телевизионных сигналов содержит блок

1 установки опорного уровня, блок 2

аналого-цифрового преобразования, блок 3 управления, блок 4 коммутации, формирователь 5 кода синхронизации, элемент 6 задержки, суммирующий регистр 7 памяти, первый регистр

8 памяти, второй регистр 9 памяти, третий регистр 10 памяти, блоки сравнения; первый 11, второй 12, третий 13 и четвертый 14, блок 15 выбора передаваемых символов, шифратор 16,

блок 17 управления памятью, блок 18 памяти, блок 19 памяти младших разрядов, блоки разрешения записи первый 20, второй 21, третий 22 и

четвертый 23; блок 24 пилот-сигнала, блок 25 управления фазой.

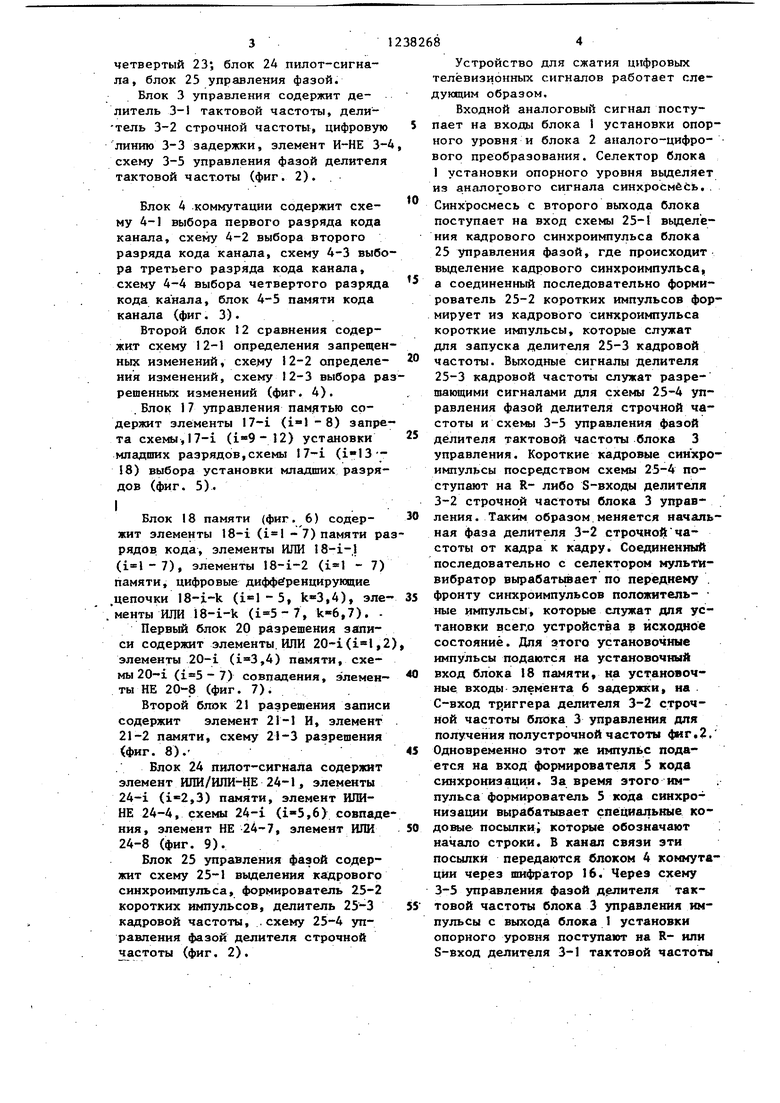

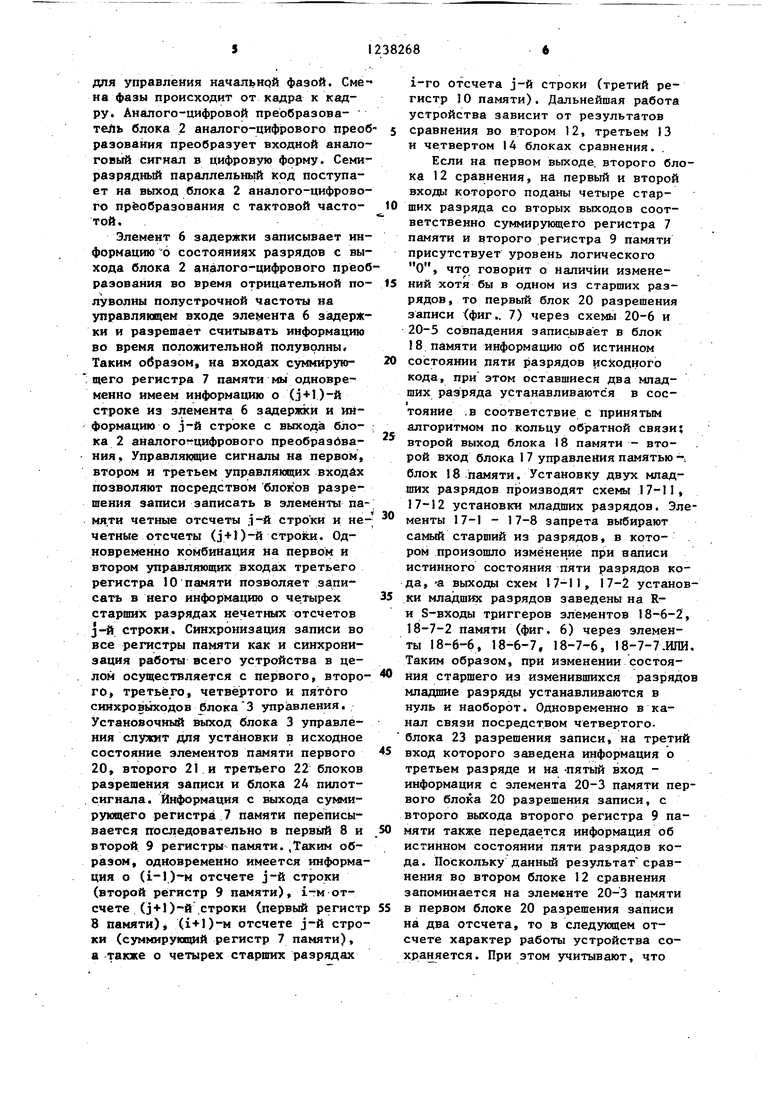

Блок 3 управления содержит делитель 3-1 тактовой частоты, дели- тель 3-2 строчной частоты, цифровую линию 3-3 задержки, элемент И-НЕ 3-4, схему 3-5 управления фазой делителя тактовой частоты (фиг. 2). .

.

Блок 4 коммутации содержит схему 4-1 выбора первого разряда кода канала, схему 4-2 выбора второго разряда кода канала, схему 4-3 выбора третьего разряда кода канала, схему 4-4 выбора четвертого разряда кода канала, блок 4-5 памяти кода канала (фиг. 3).

Второй блок 12 сравнения содер- жнт схему 12-1 определения запрещенных изменений, схему 12-2 определения изменений, схему 12-3 выбора рарешенных изменений (фиг. 4).

.Блок 17 управления памятью содержит элементы 17-i ( -8) запрета схемы,17-i () установки младших разрядов,схемы ( 18) выбора установки младших разрядов (Фиг. 5).

I

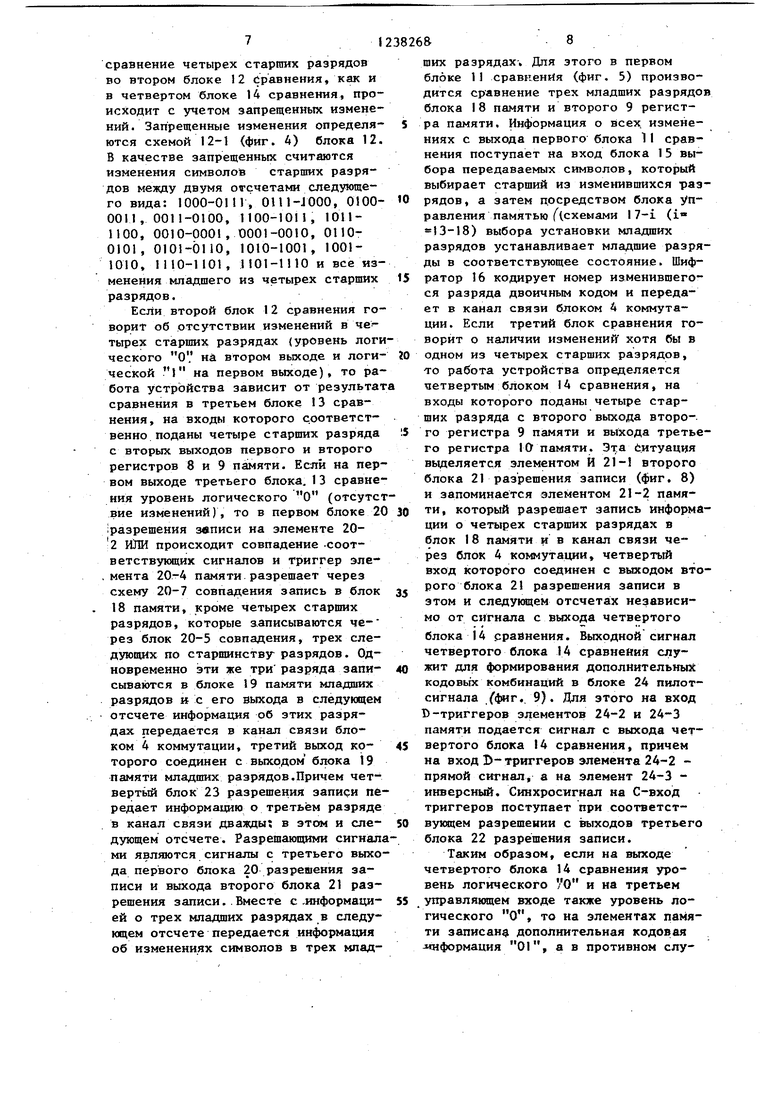

Блок 18 памяти (фиг. 6) содер

40

жит элементы 18-i ( - 7) памяти разрядов кода, элементы ИЛИ 18-1-1 (), элементы 18-1-2 ( - 7) памяти, цифровые диффе ренцирующие цепочки 18-i-k ( - 5, ,4), эле- 35 менты ИЛИ 18-i-k (, k-6,7), Первый блок 20 разрешения записи содержит элементы. ИЛИ 20-1(,2), элементы 20-1 (,4) памяти, схемы 20-1 () совпадения, элементы НЕ 20-8 (фиг. 7).

Второй блок 21 разрешения записи содержит элемент 21-1 И, элемент . 21-2 памяти, схему 21-3 разрешения (фиг. 8).

Блок 24 пилот-сигнала содержит элемент ИЛИ/ШШ-НЕ 24-1, элементы 24-1 (1«2,3) памяти, элемент ШШ- НЕ 24-4, схемы 24-1 (1-5,6) совпаде ния, элемент НЕ 24-7, элемент ИЛИ 24-8 (фиг. 9).

Блок 25 управления фазой содержит схему 25-1 выделения кадрового синхроимпульса, формирователь 25-2 коротких импульсов, делитель 25-3 кадровой частоты, .схему 25-4 управления фазой делителя строчной частоты (фиг. 2).

45

50

55

,

to

t5

25

20

40

35

,

.

2382684

Устройство для сжатия цифровых телевизионных сигналов работает сле- дующим образом.

Входной аналоговый сигнал поступает на входы блока I установки опорного уровня и блока 2 аналого-цифрового преобразования. Селектор блока 1 установки опорного уровня выделяет из аналогового сигнала синхросмёсь,,

Синхросмесь с второго выхода блока поступает на вход схемы 25-1 вьщеле- ния кадрового синхроимпульса блока 25 управления фазой, где происходит выделение кадрового синхроимпульса, а соединенный последовательно формирователь 25-2 коротких импульсов формирует из кадрового синхроимпульса короткие импульсы, которые служат для запуска делителя 25-3 кадровой частоты. Выходные сигналы делителя 25-3 кадровой частоты служат разрешающими сигналами для схемы 25-4 управления фазой делителя строчной частоты и 3-5 управления фазой делителя тактовой частоты блока 3 управления. Короткие кадровые синхроимпульсы посредством схемы 25-4 поступают на R- либо S-входы делителя 3-2 строчной частоты блока 3 управления. Таким образом.меняется начальная фаза делителя 3-2 строчной частоты от кадра к кадру. Соединенный последовательно с селектором мультивибратор вырабатьюает по переднему . фронту синхроимпульсов положитель- ные импульсы, которые служат дпя установки всего устройства в исходное состояние. Для этого установочные импульсы подаются на установочный вход блока 18 памяти, на установочные входы элемента 6 задержки, на С-вход тр,иггера делителя 3-2 строчной частоты блока 3 управления для получения полустрочной частоты фиг,2, Одновременно этот же импульс подается на вход формирователя 5 кода синхронизации. За время этого импульса формирователь 5 кода синхронизации вырабатывает спёциалыше кодовые посылки которые обозначают : начало строки. В канал связи эти посылки передаются блоком 4 коммутации через шифратор 16. Через схему 3-5 управления фазой Д1глителя тактовой частоты блока 3 управления импульсы с выхода блока 1 установки опорного уровня поступают на R- или S-вход делителя 3-1 тактовой частоты

30

45

50

55

для управления начальной фазой. Смена фазы происходит от кадра к кадру. Аналого-цифровой преобразователь блока 2 аналого-цифрового преоб разования преобразует входной аналоговый сигнал в цифровую форму. Семиразрядный параллельнь1й код поступает на выход блока 2 аналого-цифрового преобразования с тактовой часто- той,

Элемент 6 задержки записывает информацию 6 состояниях разрядов с выхода блока 2 аналого-цифрового преобразования во время отрицательной по- луволны полустрочной частоты на управляюцем входе 6 задержки и разрешает считывать информацию во время положительной полуволны. Таким образом, на входах суммирую-

: щего регистра 7 памяти мы одновременно имеем информацию о ()-й строке из злемента 6 задержки и информацию о j-й строке с выхода бло- ка 2 аналого гцифрового преобразбва- ния, Управлякздие сигналы на первом, втором и третьем управляющих входдх позволяют посредством блоков разрешения записи записать в элементы памя.ти четные отсчеты j-Й строки и нечетные отсчеты (j+1)-и строки. Одновременно комбинация на первом н втором управляющих входах третьего регистра 10 памяти позволяет за.пи- сать в него информацию о четырех старших разрядах нечетных отсчетов j-й строки. СинхронизаЦНя записи во все регистры памяти как и синхронизация работы всего устройства в целом осуществляется с первого, второ- го, третьего, четвёртого и пятого синхровыходов блока 3 управления. Установочный выход блока 3 управления служит для установки в исходное состояние элементов памяти первого 20, второго 21 и третьего 22 блоков разрешения записи и блока 24 пилот. сигнала. Информация с выхода суммирующего регистра 7 памяти переписывается последовательно в первый 8 и второй 9 регистры памяти..Таким образом, одновременно имеется информация о (i-l)-M отсчете j-й строки (второй регистр 9 памяти), i-м отсчете ()-й .строки (первый регистр 8 памяти) (i+l)-M отсчете j-й строки (суммирующий регистр 7 памяти), а также о четырех старших разрядах

i-ro отсчета j-й строки (третий регистр 10 памяти). Дальнейшая работа устройства зависит от результатов сравнения во втором 12, третьем 13 и четвертом 14 блоках сравнения.

Если на первом выходе, второго блока 12 сравнения, на первый и второй входы которого поданы четыре старших разряда со вторых выходов соответственно суммирующего регистра 7 памяти и второго регистра 9 памяти присутствует уровень логического О, что говорит о наличии изменений хотя бы в одном из старших разрядов, то первый блок 20 разрешения записи (фиг.. 7) через схемы 20-6 и 20-5 совпадения записывает в блок 8 памяти информацию об истинном состоянии пяти разрядов исходного кода, при этом оставшиеся два мпад- ших разряда устанавливаются в состояние .в соответствие с принятым алгоритмом по кольцу обратной связи; второй выход блока 18 памяти - второй вход блока 17 управления памятью -: блок 18 памяти. Установку двух мпад ших разрядов производят схемы 17-11, 17-12 установки младших разрядов. Элементы 17-1 - 17-8 запрета выбирают самый старший из разрядов, в котором произошло изменение ваписи истинного состояния пяти разрядов кода, & выходы схем 17-11, 17-2 установки младших разрядов заведены на R- и S-входы триггеров элементов 18-6-2, 18-7-2 памяти (фиг. 6) через элементы 18-6-6, 18-6-7, 18-7-6, 18-7-7.ИЛИ Таким образом, при изменении состояния старшего из изменившихся разрядо младшие разряды устанавливаются в нуль и наоборот. Одновременно в канал связи посредством четвертого- блока 23 разрешения записи, на третий вход которого заведена информация о третьем разряде и на -пятьШ вход - информация с элемента 20-3 памяти первого блока 20 разрешения записи, с второго выхода второго регистра 9 памяти также передается информация об истинном состоянии пяти разрядов кода. Поскольку данный результат сравнения во втором блоке 12 сравнения запоминается на элементе 20-3 памяти в первом блоке 20 разрешения записи на два отсчета, то в следующем отсчете характер работы устройства сохраняется. При этом учитывают, что

10

IS

:5

сравнение четырех старших разрядов во втором блоке 12 Сравнения, как и в четвертом блоке 14 сравнения, происходит с учетом запрещенных изменений. Запрещенные изменения определяются схемой 12-1 (фиг. 4) блока 12. В качестве запрещенных считаются изменения символов старших разрядов между двумя отсчетами следующего вида: 1000-01 И, 0111-1000, 0100- 0011, 0011-0100, 1100-1011, 1011- 1100, 0010-0001,0001-0010, 0110- 0101, 0101-0110, 1010-1001, 1001- 1010, 1110-1101, 1101-1110 и все изменения младшего из четырех старших разрядов.

Если второй блок 12 сравнения говорит об отсутствии изменений в тырех старших разрядах (уровень логического OV на втором выходе и логи- 10 ческой 1 на первом выходе), то работа устройства зависит от результата сравнения в третьем блоке 13 сравнения, на входы которого с.оответст- BeiHHo поданы четыре старших разряда с вторых выходов первого и второго регистров 8 и 9 . Если на первом выходе третьего блока, 13 сравнения уровень логического О (отсутствие изменений), то в первом блоке 20 30 ;разрешения звписи на элементе 20- 2 ИЛИ происходит совпадение -соответствующих сигналов и триггер элемента 20-4 памяти разрешает через схему 20-7 совпадения запись в блок 18 памяти, кроме четырех старших разрядов, которые записываются че- рез блок 20-5 совпадения, трех следующих по старшинству разрядов. Одновременно эти же три разряда записываются в блоке 19 памяти младших разрядов и с его выхода в следующем

отсчете информация об этих разрядах передается в канал связи блоком 4 коммутации, третий выход которого соединен с выходом блока 19 памяти младших разрядов.Причем чет- вертьй блок 23 разрешения записи передает информацию о третьем разряде в канал связи дважды в этом и следующем отсчете. Разрешающими сигналами являются сигналы с третьего выхода первого блока 20 разрешения записи и выхода второго блока 21 разрешения записи..Вместе с .информаци- 55 ей о трех младших разрядах в следующем отсчете передается информация об изменениях символов в трех млад35

40

45

50

10

IS

:5

10а30

55

3826&.8

ших разрядах. Для этого в первом блоке 11 сравнения (фиг. 5) производится сравнение трех младших разрядов блока 18 памяти и второго 9 регистра памяти. Информация о всех, изменениях с выхода первого блока 11 сравнения поступает на вход блока 15 выбора передаваемых символов, который выбирает старший из изменившихся разрядов , а затем посредством блока управления памятью ((.схемами I7-i (i 13-18) выбора установки младших разрядов устанавливает младшие разряды в соответствующее состояние. Шифратор 16 кодирует номер изменившегося разряда двоичным кодом и передает в канал связи блоком 4 коммутации. Если третий блок сравнения говорит о наличии изменений хотя бы в одном из четырех старших разрядов, то работа устройства определяется четвертым блоком 14 сравнения, на входы которого поданы четыре старших разряда с второго выхода второго регистра 9 памяти и выхода третьего регистра 10 памяти. Эта Ситуация выделяется элементом И 21- второго блока 21 разрешения записи (фиг, 8) и запоминается элементом 21-2 памяти, который разрешает запись информации о четырех старших разрядах в блок 18 памяти и в канал связи через блок 4 коммутации, четвертый вход которого соединен с выходом второго блока 21 разрешения записи в этом и следукнцем отсчетах независимо от сигнала с выхода четвертого блока 14 сравнения. Выходной сигнал четвертого блока 14 сравнения служит для формирования дополнительных кодовьтх комбинаций в блоке 24 пилот- сигнала .. 9). Для этого на вход Т -триггеров элементов 24-2 и 24-3 памяти подается сигнал с выхода четвертого блока 14 сравнения, причем на вход В-триггеров элемента 24-2 - прямой сигнал, а на элемент 24-3 - инверсный. Синхросигнал на С-вход триггеров поступает при соответст- вухщем разрешении с выходов третьего блока 22 разрешения записи.

Таким образом, если на выходе четвертого блока 14 сравнения уровень логического О и на третьем

35

40

45

50

управляющем входе также уровень логического О, то на элементах памяти записан дополнительная кодовая информация 01, а в противном случае - 10. Схемы 24-5 и 24-6 совпадения, а также элемент 24-8 ИЛИ передают эти комбинации череэчетвёр- тый блок 23 разрешения записи в блок 4 коммутации последовательно: первый бит дополнительной кодовой комбинации в одном отсчете, другой - в следующем. Вся поступающая на входы блока 4 коммутации информации записывается в блок 4-5 памяти кода канала (фнг.З)и с ее выхода считывается на выход устройства, В следующем кадре триггер делителя 25-3 кадровой частоты пере- брасывается в другое состояние и установочные импульсы изменяют иачаль- ную фазу триггеров дели телей 3-1 и 3-2 блока3 управления.Вдальнейшем алгоритм работы устройства сохраняется.Формула изобретения

Устройство для сжатия цифровых телевизионных сигналов по авт.св. № I146831, отличающееся Тем, что, с целью умешьшения искажений телевизионных сигналов, введен блок управления фазой, вход которого соединен с вторым выходом блока установки опорного уровня, первый и второй выходы соединены соответственно с первым и вторым управляющими входами блока управления, а синхро- вход и установочный вход третьего блока разрешения записи соединены соответственно с четвертым синхро- выходом и с установочным выходом блока управления.

««W

fatrinfitttu

9па

Us /JSr /tf ItK.v,M.

вавЛе г ((п11а в оЛЛMtAtttt

Фи. г

tfoA mf жм(

f

MtAtttt

tfoAai mf жм(.м

SfnopoiJ fyffS

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия цифровых телевизионных сигналов | 1984 |

|

SU1243159A2 |

| Устройство для сжатия цифровых телевизионных сигналов | 1982 |

|

SU1059702A1 |

| Устройство для кодирования телевизионных сигналов | 1986 |

|

SU1356259A1 |

| Устройство для сжатия цифрового телевизионного сигнала | 1985 |

|

SU1285626A1 |

| Устройство для сжатия цифровых телевизионных сигналов | 1980 |

|

SU944145A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Устройство для отображения информации на экране цветного видеоконтрольного блока | 1988 |

|

SU1529280A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ ЭВМ С ДИСПЛЕЕМ | 1992 |

|

RU2051410C1 |

| Устройство для отображения информации на экране электроннолучевой трубки | 1984 |

|

SU1257635A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1522272A1 |

Изобретение относится к электросвязи и является усовертенствованием устройства по авт.св. 1146831. Уменьшаются искажения телевизионных сигналов. Входной аналоговый сигнал поступает на блок I установки опорного уровня, где вьщеляется синхро- смесь, и на блок 2 аналого-цифрового преобразования. Синхросмесь по- ступает на блок 25 управления фазой, где выделяется кадровый синхроимпульс и формируются управляющие импульсы, которые поступают на блок управления 3. Импульсы с блока установки опорного уровня устанавливают устройство в исходаюе состояние и поступают на формирователь 5 кода % (Л с 1C 00 00 о 00 N

fff/fS /tf второй Bjfoffgiro3

11

о я

a

/TT p-51 |/7-V| j /7-i j

I I ii I 11Ц II liiu |ц1 I I I 1 I III

ffftopMt

/7$m ai/

Л0/ я

9м1го9

фм.9

..i.i,.

.ILL.

П Г

18-1

18-г

18 У

4 19-1:2

д

Н3( m f(

..JtU

Г

П

Гв-7

1в

Т

Фиг. б

Т

.A34ti / fre 2 fuMifffff,

g ftHtffS Фи9.7

ttia. ttef

Z-vuap. ttaf

УствчвЗ

7-itynp. 2-a-S-u Ci/MtpofxoS тш г

WjiJuBST С™

г/

вход

г/-з I

/«.AV

Составитель И.Грацианская Редактор М.Келемеш Техред М;Хдданич Корректор 0.Луговая

Заказ 3306/59 Тираж 624Подписное

. ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| ) Авторское свидетельство СССР 1146831, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-06-15—Публикация

1984-10-18—Подача