(5) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи сигналов | 1982 |

|

SU1119187A1 |

| Устройство для передачи сигналов | 1986 |

|

SU1385295A2 |

| Устройство для передачи двукратных биимпульсных сигналов | 1980 |

|

SU886284A1 |

| Устройство для приема дискретных сигналов | 1980 |

|

SU919136A1 |

| Система передачи дискретной информации | 1987 |

|

SU1533013A1 |

| Устройство приема дискретных сигналов | 1972 |

|

SU543178A1 |

| Устройство для приема биимпульсных сигналов | 1984 |

|

SU1256230A1 |

| Формирователь цифрового линейного сигнала | 1986 |

|

SU1392626A1 |

| Устройство для формирования биимпульсного сигнала | 1985 |

|

SU1282345A1 |

| Устройство для передачи и приема цифровых сигналов | 1988 |

|

SU1564735A1 |

1

Изобретение относится к электросвязи и может быть использовано в устройствах передачи дискретных сигналов по кабелям связи.

Известно устройство передачи сигналов, содержащее последовательно соединенные синхрогенератор и преобразователь бинарных сигналов, ,а также выходной согласующий блок 1 Однако известное устройство обладает низкой помехоустойчивостью из-за увеличения мощности флуктуационного шума.

Цель изобретения - повышение помехоустойчивости.

Для достижения указанной цели в устройство для передачи сигналов, содержащее последовательно соединенные синхрогенератор и преобразователь бинарных сигналов, а также выходной согласующий блок, введены последовательно соединенные блок согласования и фильтр, выход которого подключен к входу выходного согласующего блока, а выход преобразователя бинарных сигналов подключен к входу блока согласования. Кроме того, преобразователь бинарных сигналов содержит четыре элемента И, элемент ИЛИ, последовательно соединенные инвертор и первый делитель, а также второй делитель и последовательно соединенные блок задержки и де,шифратор, выход которого подключен

10 к первым входам элементов И, при этом прямой и инверсный выходы первого делителя подключены соответственно к вторым входам первого и второго элементов И, а прямой и инверс15ный выходы второго делителя подклю- . чены соответственно к вторым входам третьего и четвертого элементов И, причем выходы всех элементов И подключены к соответствующим входам элв

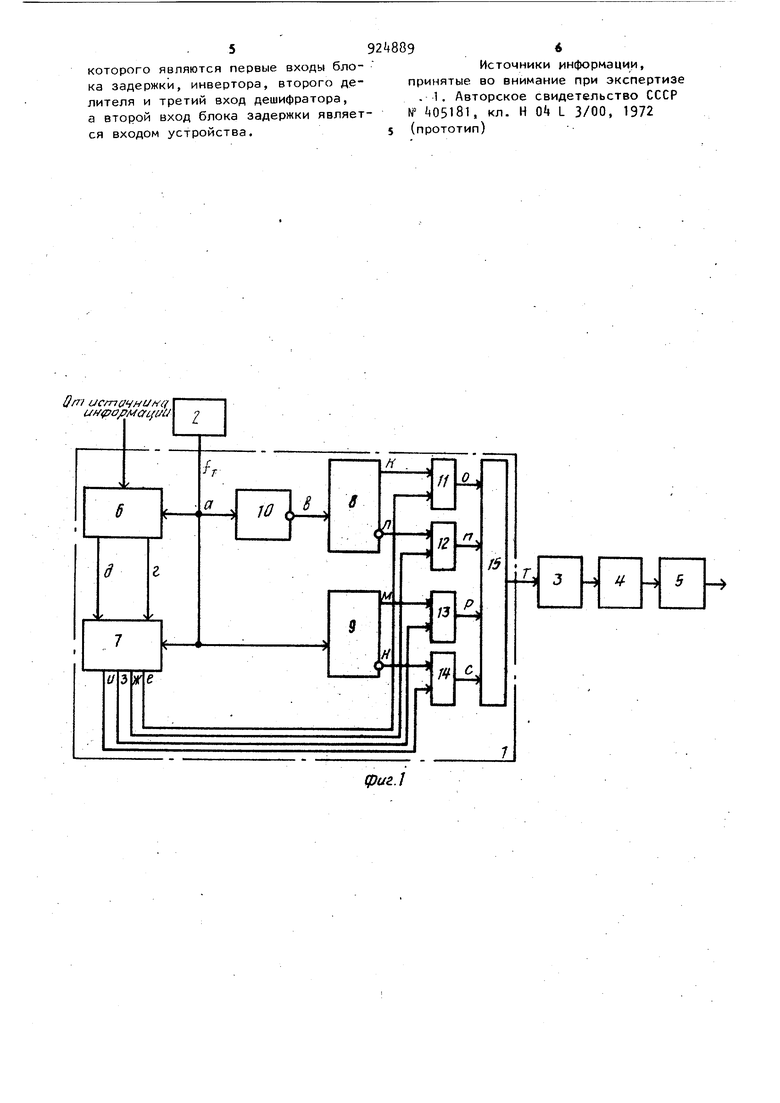

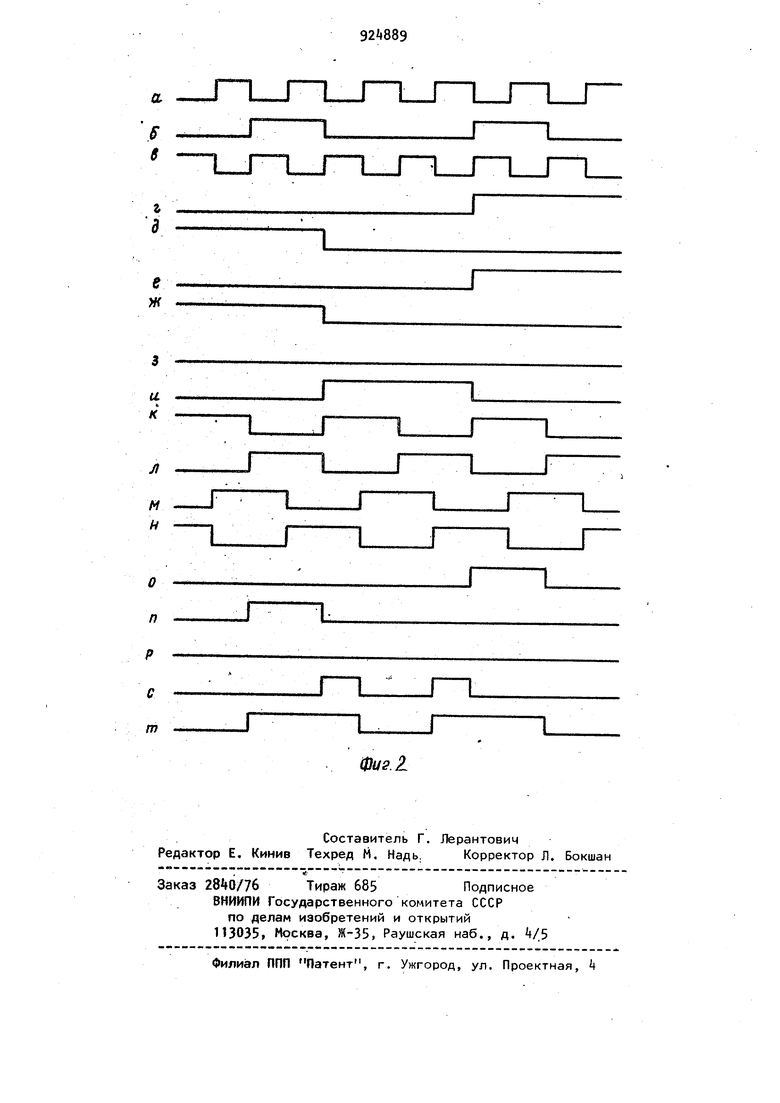

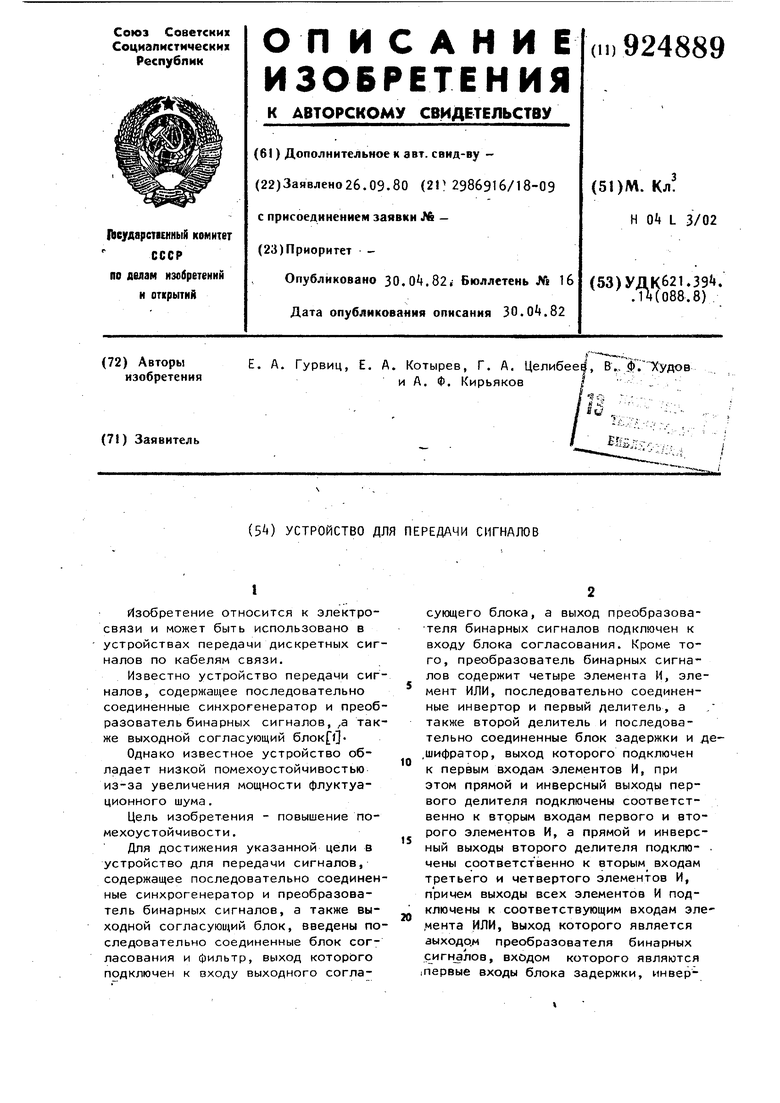

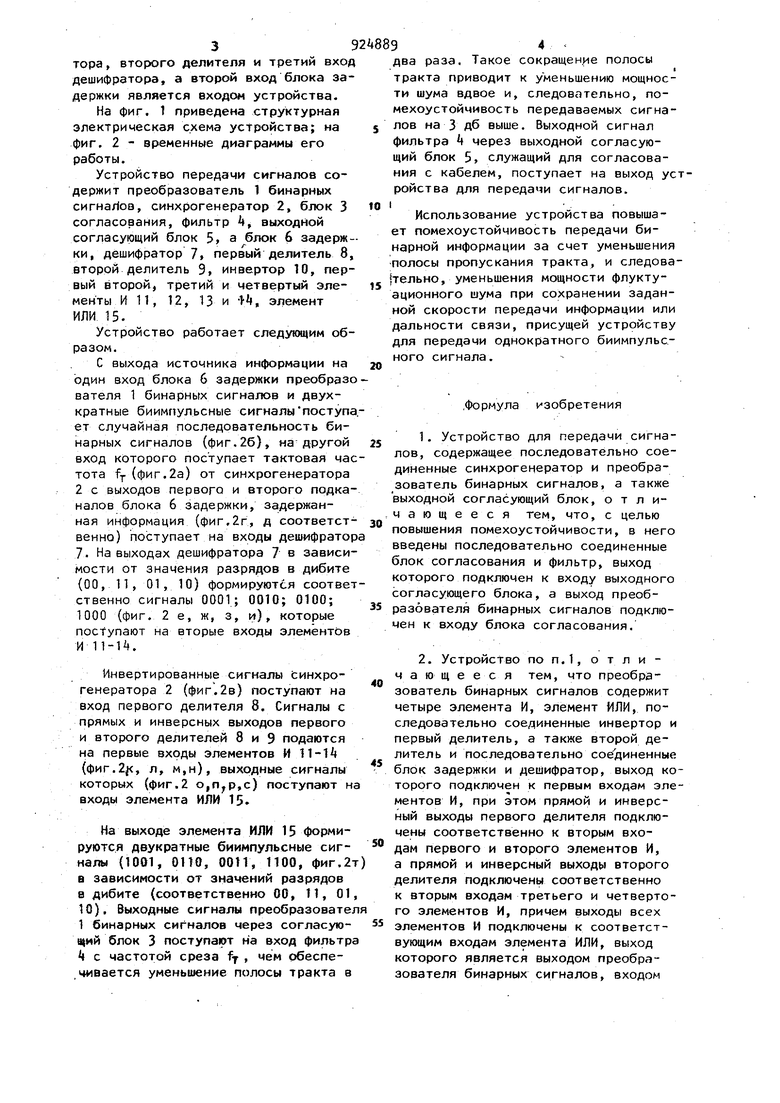

20 ,мента ИЛИ, йыход которого является аыходо.м преобразователя бинарных , входом которого являются Первые входы блока задержки, инвертора, вторюго делителя и третий вход дешифратора, а второй вход блока задержки является входом устройства. На фиг. 1 приведена структурная электрическая схема устройства; на фиг. 2 - временные диаграммы его работы. Устройство передачи сигнахюв содержит преобразователь 1 бинарных сигналов, синхрогенератор 2, блок 3 согласования, фильтр , выходной согласующий блок 5 а блок 6 задержки, дешифратор 7, первый делитель 8, второй делитель 9, инвертор 10, первый второй, третий и четвертый элементы И 11, 12, 13 и , элемент ИЛИ 15. Устройство работает следующим образом. С аыхода источника информации на один вход блока 6 задержки преобразо вателя 1 бинарных сигналов и двухкратные биимпульсные сигналыпоступа ет случайная последовательность бинарных сигналов (фиг.26), на другой вход которого поступает тактовая час тота f,(фиг.2a) от синхрогенератора 2 с выходов первого и второго подканалов блока 6 задержки, задержанная информация (фиг.2г, д соответственно) поступает на входы дешифратор 7. На выходах дешифратора 7 в зависимости от значения разрядов в дибите (00, 11, 01, 10) формируются соответ ственно сигналы 0001; 0010; 0100; 1000 {фиг. 2 е, ж, 3, и), которые поступают на вторые входы элементЬв И 11 -1 . Инвертированные сигналы синхрогенератора 2 (фмг.2в) поступают на вход первого делителя 8. Сигналы с прямых и инверсных выходов первого и второго делителей 8 и 9 подаются на первые входы элементов И 11-Н {фиг.2|, л, м,н), выходные сигналы которых (фиг.2 о,,с) поступают н входы элемента ИЛИ 15. На выходе элемента ИЛИ 15 формируются двукратные биимпульсные сигналы (1001, ОНО, ООП, 1100, фиг.2т в зависимости от значений разрядов в дибите (соответственно 00, 11, 01 10), Выходные сигналы преобразовател 1 бинарных сигналов через согласующий блок 3 поступают на вход фильтра k с частотой среза ff , чем обеспечивается уменьшение полосы тракта в два раза. Такое сокращен 1е полосы тракта приводит к уменьшению мощности шума вдвое и, следовательно, помехоустойчивость передаваемых сигналов на 3 дб выше. Выходной сигнал фильтра через выходной согласующий блок 5, служащий для согласования с кабелем, поступает на выход устройства для передачи сигналов. Использование устройства повышает помехоустойчивость передачи бинарной информации за счет уменьшения полосы пропускания тракта, и следовательно, уменьшения мощности флуктуационного шума при сохранении заданной скорюсти передачи информации или дальности связи, присущей устройству для передачи однократного биимпульсного сигнала. .формула изобретения 1. Устройство для передачи сигналов, содержащее последовательно соединенные синхрогенератор и преобразователь бинарных сигналов, а также выходной согласующий блок, отличающееся тем, что, с целью повышения помехоустойчивости, в него введены последовательно соединенные блок согласования и фильтр, выход которого подключен к входу выходного согласующего блока, а выход преобразователя бинарных сигналов подключен к входу блока согласования. 2. Устройство по п.1, о т л и чающееся тем, что преобразователь бинарных сигналов содержит четыре элемента И, элемент ИЛИ, последовательно соединенные инвертор и первый делитель, а также второй делитель и последовательно соединенные блок задержки и дешифратор, выход которого подключен к первым входам элементов И, при этом прямой и инверсный выходы первого делителя подключены соответственно к вторым входам первого и второго элементов И, а прямой и инверсный выходы второго делителя подключены соответственно к вторым входам третьего и четвертого элементов И, причем выходы всех элементов И подключены к соответствующим входам элемента ИЛИ, выход которого является выходом преобразователя бинарных сигналов, входом которого являются первые входы блока задержки, инвертора, второго делителя и третий вход дешифратора, а второй вход блока задержки является входом устройства.

Of7i ucmffi HtJf ii: uff ofMaLfi u 9248

фиг.1 89 Источники информации, принятые во внимание при экспертизе .1. Авторское свидетельство СССР № 05181. кл. Н О L 3/00, 1972 (прототип)

Авторы

Даты

1982-04-30—Публикация

1980-09-26—Подача