(21)4124453/24-21

(22)28.05.86

(46) 07.04.88. Бюл. № 13

(72) О. Н. Музыченко

(53) 621.374(088.8)

(56) Авторское свидетельство СССР

№ 1092727, кл. Н 03 К 19/23, 1982.

Авторское свидетельство СССР № 1083364, кл. Н 03 К 19/23, 1982.

(54) ПОРОГОВЫЙ ЭЛЕМЕНТ (57) Изобретение относится к области автоматики и вычислительной техники и может быть использовано для построения устройств обработки дискретной информации. Устройство содержит сканирующий мультиплексор 1, накопитель 3, триггер 5, блок 6 сброса и генератор 7 тактовых импульсов. Введение блока 2 формирования пачек импульсов, блока 4 формирования порога, элемента И 8 и образование новых функциональных связей повышают быстродействие порогового элемента. 10 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый элемент | 1984 |

|

SU1261100A1 |

| Пороговый элемент | 1985 |

|

SU1297220A1 |

| Пороговый элемент | 1985 |

|

SU1297219A1 |

| Пороговый элемент | 1982 |

|

SU1092727A1 |

| Пороговый элемент | 1987 |

|

SU1647871A1 |

| Пороговый элемент | 1987 |

|

SU1584098A1 |

| Пороговый элемент | 1983 |

|

SU1126924A1 |

| Пороговое устройство | 1986 |

|

SU1368979A1 |

| Пороговый элемент | 1982 |

|

SU1083364A1 |

| Пороговое устройство (его варианты) | 1984 |

|

SU1352449A1 |

со

00

со

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения различных устройств обработки дискретной информации.

Цель изобретения - повышение быстродействия порогового элемента.

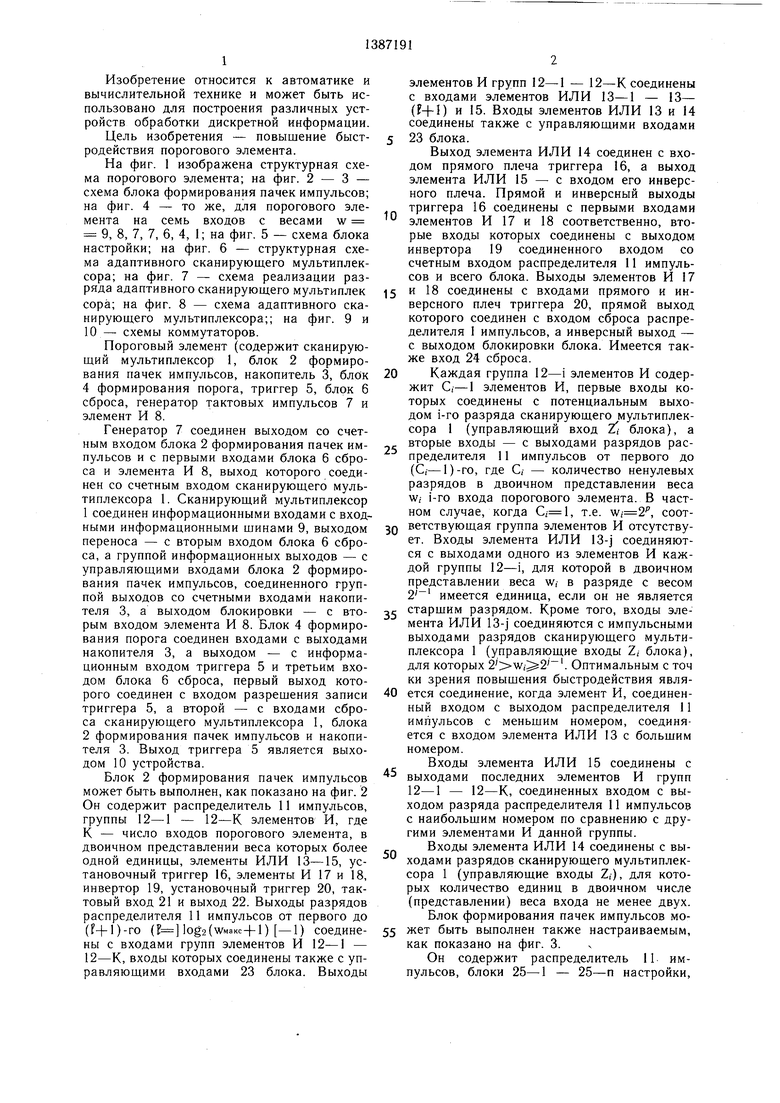

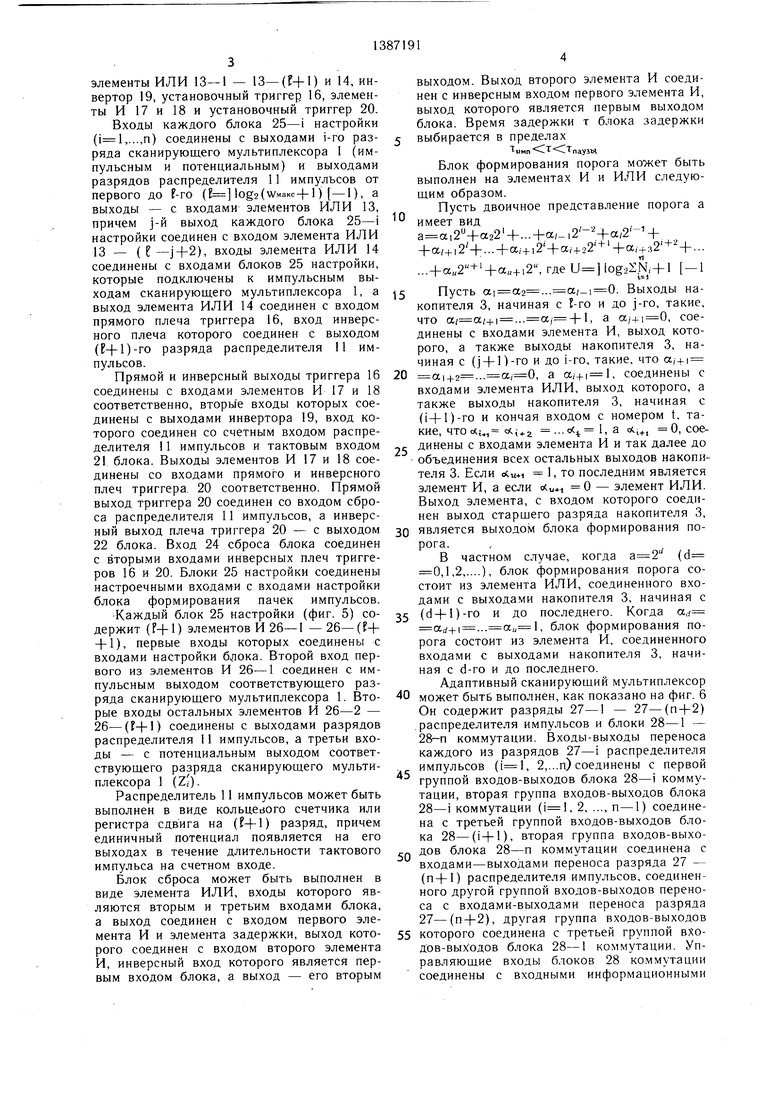

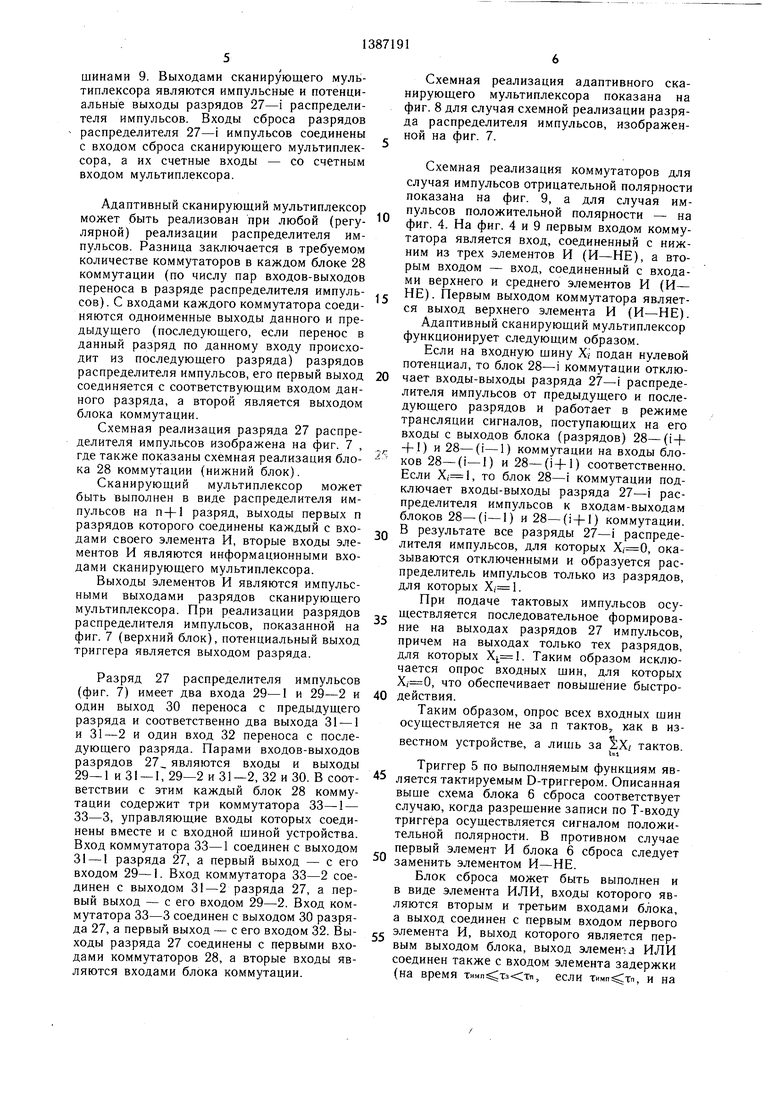

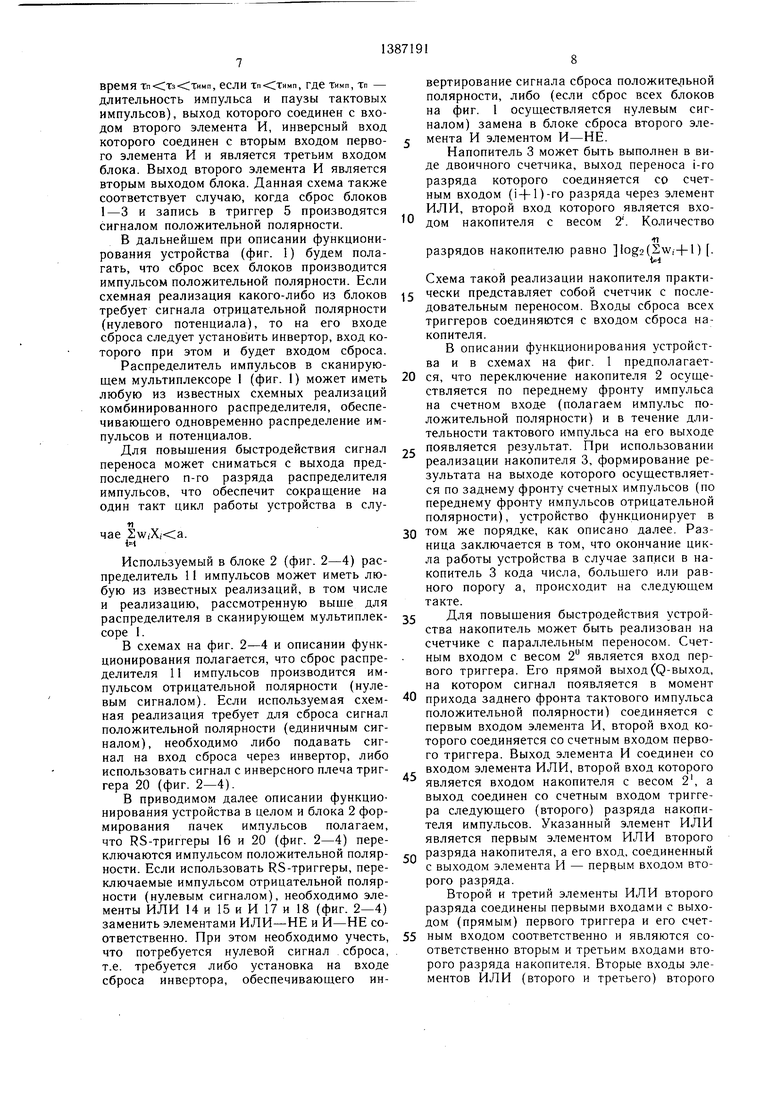

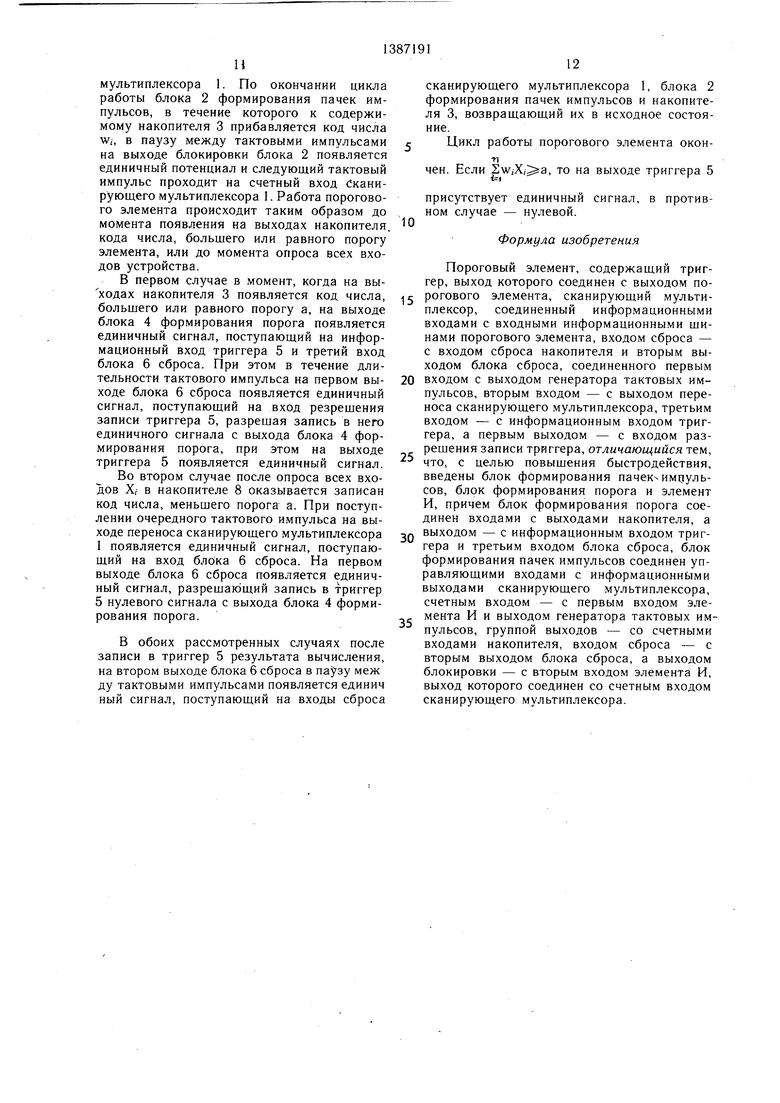

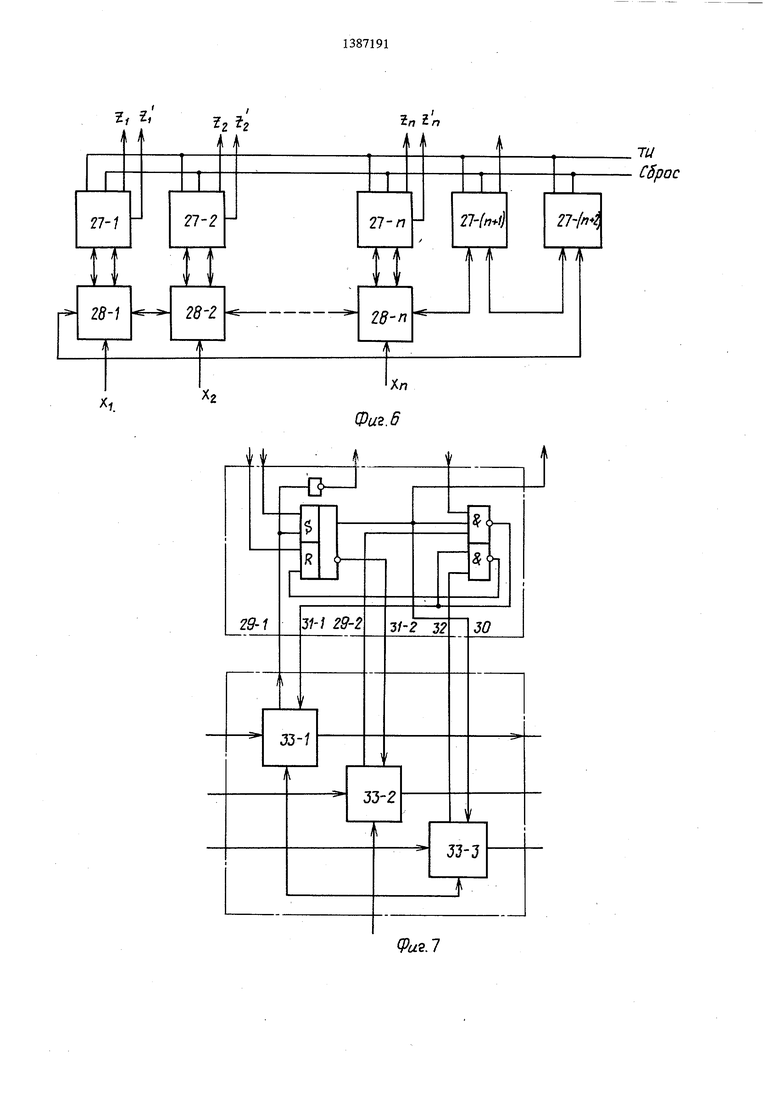

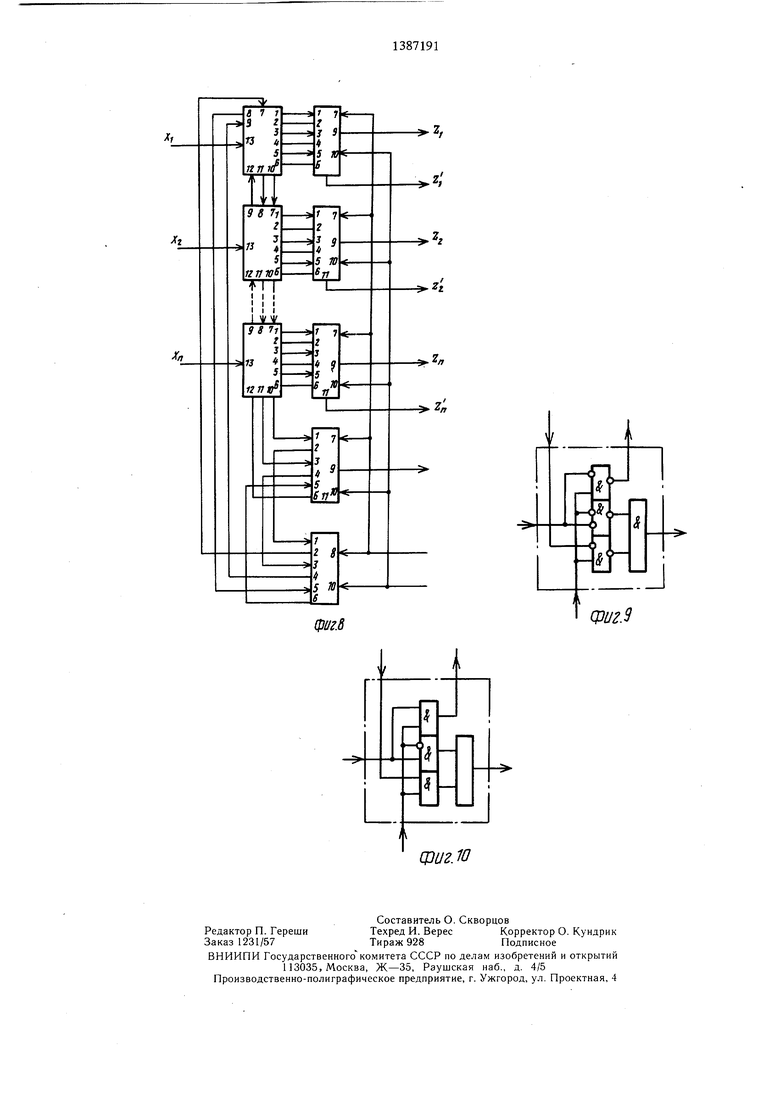

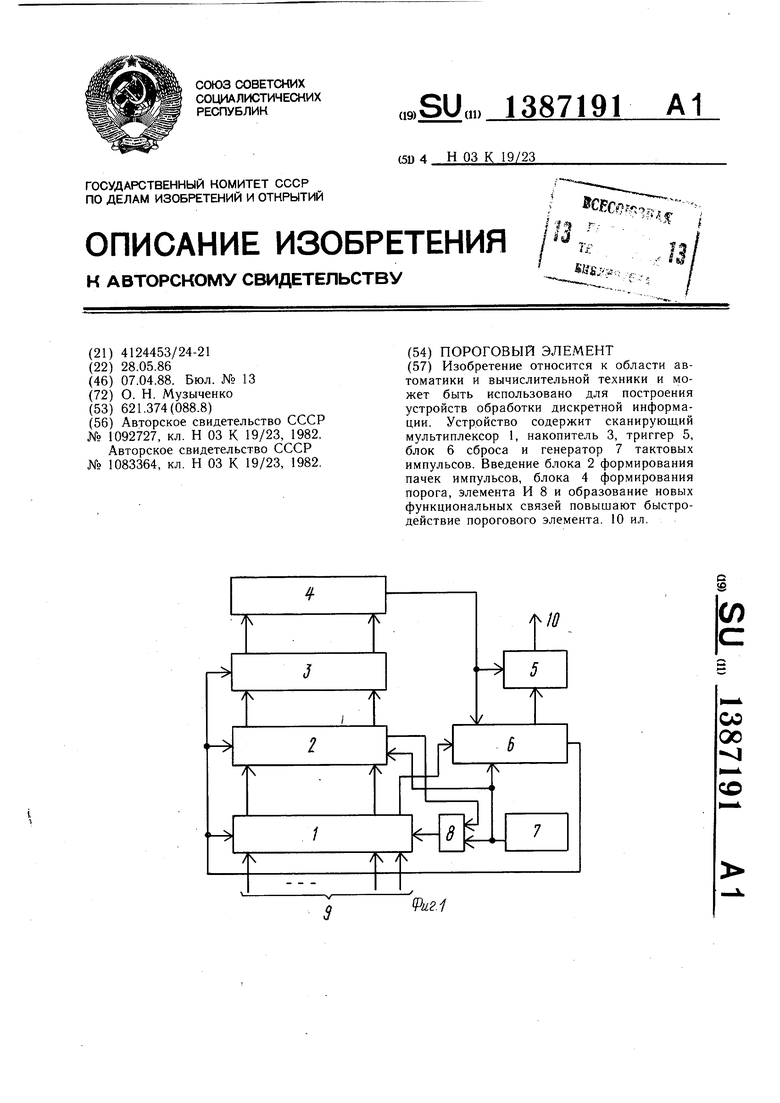

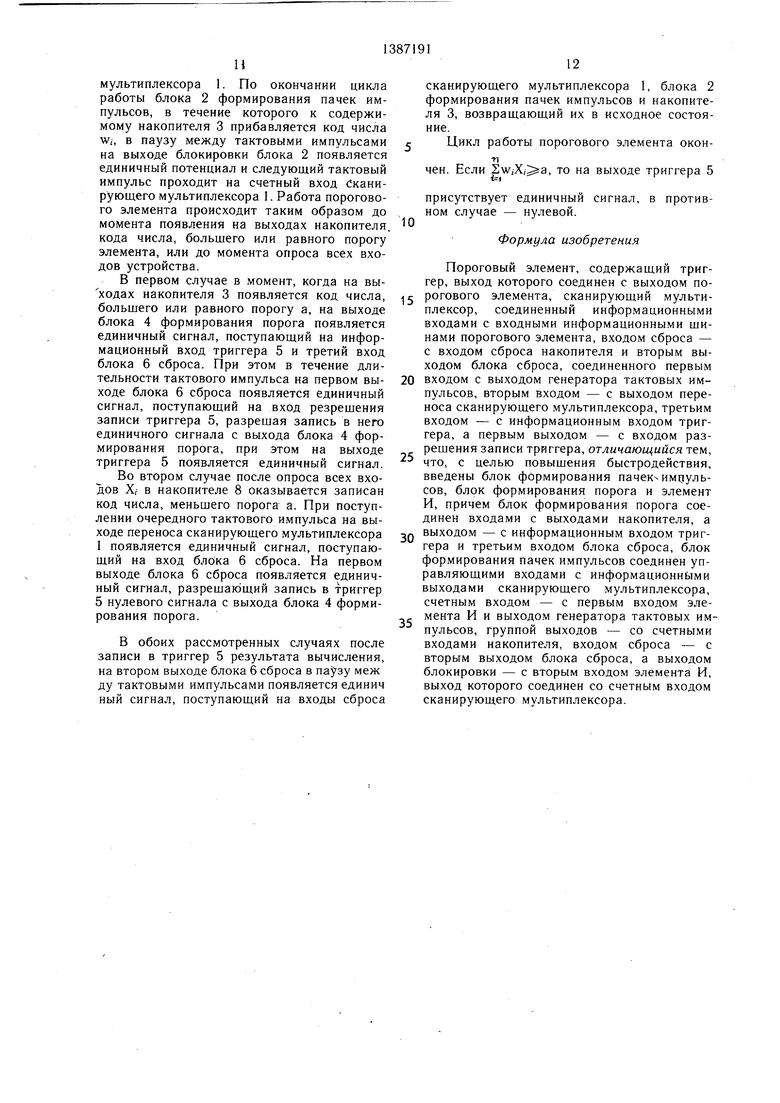

На фиг. 1 изображена структурная схема порогового элемента; на фиг. 2 - 3 - схема блока формирования пачек импульсов; на фиг. 4 - то же, для порогового элемента на семь входов с весами w 9, 8, 7, 7, 6, 4, 1; на фиг. 5 - схема блока настройки; на фиг. 6 - структурная схема адаптивного сканирующего мультиплексора; на фиг. 7 - схема реализации разряда адаптивного сканирующего мультиплек сора; на фиг. 8 - схема адаптивного сканирующего мультиплексора;; на фиг. 9 и 10 - схемы коммутаторов.

Пороговый элемент (содержит сканирующий мультиплексор 1, блок 2 формирования пачек импульсов, накопитель 3, блок 4 формирования порога, триггер 5, блок 6 сброса, генератор тактовых импульсов 7 и элемент И 8.

Генератор 7 соединен выходом со счетным входом блока 2 формирования пачек импульсов и с первыми входами блока 6 сброса и элемента И 8, выход которого соединен со счетным входом сканирующего мультиплексора 1. Сканирующий мультиплексор

1соединен информационными входами с входными информационными щинами 9, выходом переноса - с вторым входом блока 6 сброса, а группой информационных выходов - с управляющими входами блока 2 формирования пачек импульсов, соединенного группой выходов со счетными входами накопителя 3, а выходом блокировки - с вторым входом элемента И 8. Блок 4 формирования порога соединен входами с выходами накопителя 3, а выходом - с информационным входом триггера 5 и третьим входом блока 6 сброса, первый выход которого соединен с входом разрешения записи триггера 5, а второй - с входами сброса сканирующего мультиплексора 1, блока

2формирования пачек импульсов и накопителя 3. Выход триггера 5 является выходом 10 устройства.

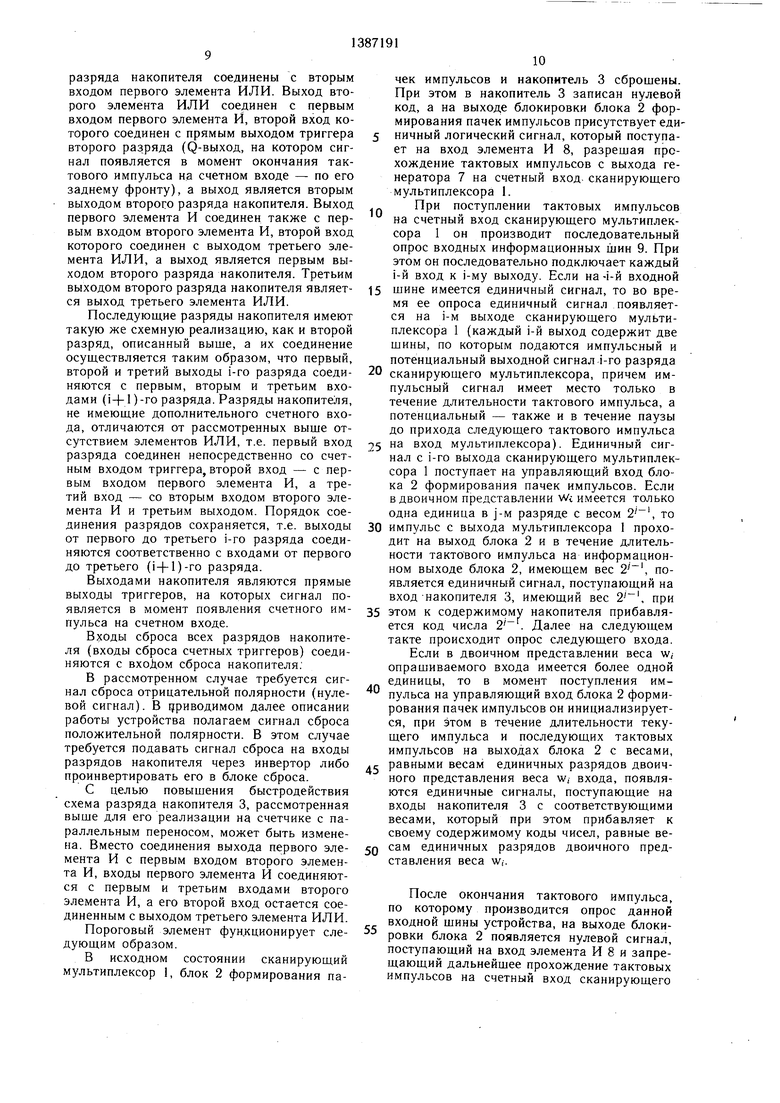

Блок 2 формирования пачек импульсов может быть выполнен, как показано на фиг. 2 Он содержит распределитель 11 импульсов, группы 12-1 - 12-К элементов И, где К - число входов порогового элемента, в двоичном представлении веса которых более одной единицы, элементы ИЛИ 13-15, установочный триггер 16, элементы И 17 и 18, инвертор 19, установочный триггер 20, тактовый вход 21 и выход 22. Выходы разрядов распределителя 11 импульсов от первого до (f-l-l)-ro (F log:2(wMaKc+l) -1) соедине- ны с входами групп элементов И 12-1 - 12-К, входы которых соединены также с управляющими входами 23 блока. Выходы

элементов И групп 12-1 - 12-К соединены с входами элементов ИЛИ 13-1 - 13- (P+l) и 15. Входы элементов ИЛИ 13 и 14 соединены также с управляющими входами

23 блока.

Выход элемента ИЛИ 14 соединен с входом прямого плеча триггера 16, а выход элемента ИЛИ 15 - с входом его инверсного плеча. Прямой и инверсный выходы триггера 16 соединены с первыми входами элементов И 17 и 18 соответственно, вторые входы которых соединены с выходом инвертора 19 соединенного входом со счетным входом распределителя 11 импульсов и всего блока. Выходы элементов И 17

и 18 соединены с входами прямого и инверсного плеч триггера 20, прямой выход которого соединен с входом сброса распределителя 1 импульсов, а инверсный выход - с выходом блокировки блока. Имеется также вход 24 сброса.

0 Каждая группа 12-i элементов И содержит С,-1 элементов И, первые входы которых соединены с потенциальным выходом i-ro разряда сканирующего мультиплексора 1 (управляющий вход Z блока), а вторые входы - с выходами разрядов распределителя 11 импульсов от первого до (С,--1)-го, где С,- - количество ненулевых разрядов в двоичном представлении веса W, i-ro входа порогового элемента. В частном случае, когда С, 1, т.е. w,, соотQ ветствующая группа элементов И отсутствует. Входы элемента ИЛИ 13-j соединяются с выходами одного из элементов И каждой группы 12-i, для которой в двоичном представлении веса w,- в разряде с весом имеется единица, если он не является

с старшим разрядом. Кроме того, входы элемента ИЛИ 13-j соединяются с импульсными выходами разрядов сканирующего мультиплексора 1 (управляющие входы Z, блока), для которых ,. Оптимальны.м с точ ки зрения повыщения быстродействия явля0 ется соединение, когда элемент И, соединенный входом с выходом распределителя 11 импульсов с меньшим номером, соединяется с входом элемента ИЛИ 13 с большим номером.

Входы элемента ИЛИ 15 соединены с

выходами последних элементов И групп 12-1 - 12-К, соединенных входом с выходом разряда распределителя 11 импульсов с наибольшим номером по сравнению с другими элементами И данной группы.

Входы элемента ИЛИ 14 соединены с вы- ходами разрядов сканируюшего мультиплексора 1 (управляющие входы Z,), для которых количество единиц в двоичном числе (представлении) веса входа не менее двух. Блок формирования пачек импульсов мо5 жет быть выполнен также настраиваемым, как показано на фиг. 3.

Он содержит распределитель 11 импульсов, блоки 25-1 - 25-п настройки.

элементы ИЛИ 13-1 - 13-(f+1) и 14, инвертор 19, установочный триггер 16, элементы И 17 и 18 и установочный триггер 20. Входы каждого блока 25-i настройки (,...,n) соединены с выходами i-ro разряда сканирующего мультиплексора 1 (импульсным и потенциальным) и выходами разрядов распределителя 11 импульсов от

первого до Р-ГО ( log2(WMaKC-|-l) (-1), а

выходы - с входами элементов ИЛИ 13, причем |-й выход каждого блока 25-i настройки соединен с входом элемента ИЛИ 13 - (f -J+2), входы элемента ИЛИ 14 соединены с входами блоков 25 настройки, которые подключены к импульсным выходам сканирующего мультиплексора 1, а выход элемента ИЛИ 14 соединен с входом прямого плеча триггера 16, вход инверсного плеча которого соединен с выходом (Е+1)-го разряда распределителя 11 импульсов.

Прямой и инверсный выходы триггера 16 соединены с входами элементов И 17 и 18 соответственно, вторы е входы которых соединены с выходами инвертора 19, вход которого соединен со счетным входом распределителя 11 импульсов и тактовым входом

21блока. Выходы элементов И 17 и 18 соединены со входами прямого и инверсного плеч триггера, 20 соответственно. Прямой выход триггера 20 соединен со входом сброса распределителя 11 импульсов, а инверсный выход плеча триггера 20 - с выходом

22блока. Вход 24 сброса блока соединен с вторыми входами инверсных плеч триггеров 16 и 20. Блоки 25 настройки соединены настроечными входами с входами настройки блока формирования пачек импульсов.

Каждый блок 25 настройки (фиг. 5) содержит (f+1) элементов И 26-1 - 26-(f+ +1), первые входы которых соединены с входами настройки . Второй вход первого из элементов И 26-1 соединен с импульсным выходом соответствующего разряда сканирующего мультиплексора 1. Вторые входы остальных элементов И 26-2 - 26-(+1) соединены с выходами разрядов распределителя 11 импульсов, а третьи входы - с потенциальным выходом соответствующего разряда сканирующего мультиплексора 1 (Z/).

Распределитель 11 импульсов может быть выполнен в виде кольцевого счетчика или регистра сдвига на (f+1) разряд, причем единичный потенциал появляется на его выходах в течение длительности тактового импульса на счетном входе.

Блок сброса может быть выполнен в виде элемента ИЛИ, входы которого являются вторым и третьим входами блока, а выход соединен с входом первого элемента И и элемента задержки, выход которого соединен с входом второго элемента И, инверсный вход которого является первым входом блока, а выход - его вторым

0

5

5

0

5

0

5

0

выходом. Выход второго элемента И соединен с инверсным входом первого элемента И, выход которого является первым выходом блока. Время задержки т блока задержки выбирается в пределах

,.

5

laysw

Блок формирования порога может быть выполнен на элементах И и ИЛИ следующим образом.

Пусть двоичное представление порога а имеет вид ,2 +а22 +.-+а/-|2 - +а,2- +

+ а,+ |2 +...+а,-+,2 +сс,-+22 + +а/+з2 +Ч... ...+а„2 + +а„+12, где U log.SN. + l -1

Пусть .... Выходы накопителя 3, начиная с Т-го и до j-ro, такие, что «(«;+:...а/ + 1, а , соединены с входами элемента И, выход которого, а также выходы накопителя 3, начиная с (j + l)-ro и до i-ro, такие, что a,+i ai+2...a,0, а a,, соединены с входами элемента ИЛИ, выход которого, а также выходы накопителя 3, начиная с (i+l)-ro и кончая входом с номером t. такие, что ,i 2 .., а о,1+, О, соединены с входами элемента И и так далее до объединения всех остальных выходов накопителя 3. Если ОС.Ц4, 1, то последним является элемент И, а если л. 0 - элемент ИЛИ. Выход элемента, с входом которого соединен выход старшего разряда накопителя 3, является выходом блока формирования порога.

В частном случае, когда (d 0,1,2,....), блок формирования порога состоит из элемента ИЛИ, соединенного входами с выходами накопителя 3, начиная с (d + l)-ro и до последнего. Когда а.а ad+i...a,j 1, блок формирования порога состоит из элемента И, соединенного входами с выходами накопителя 3, начиная с d-ro и до последнего.

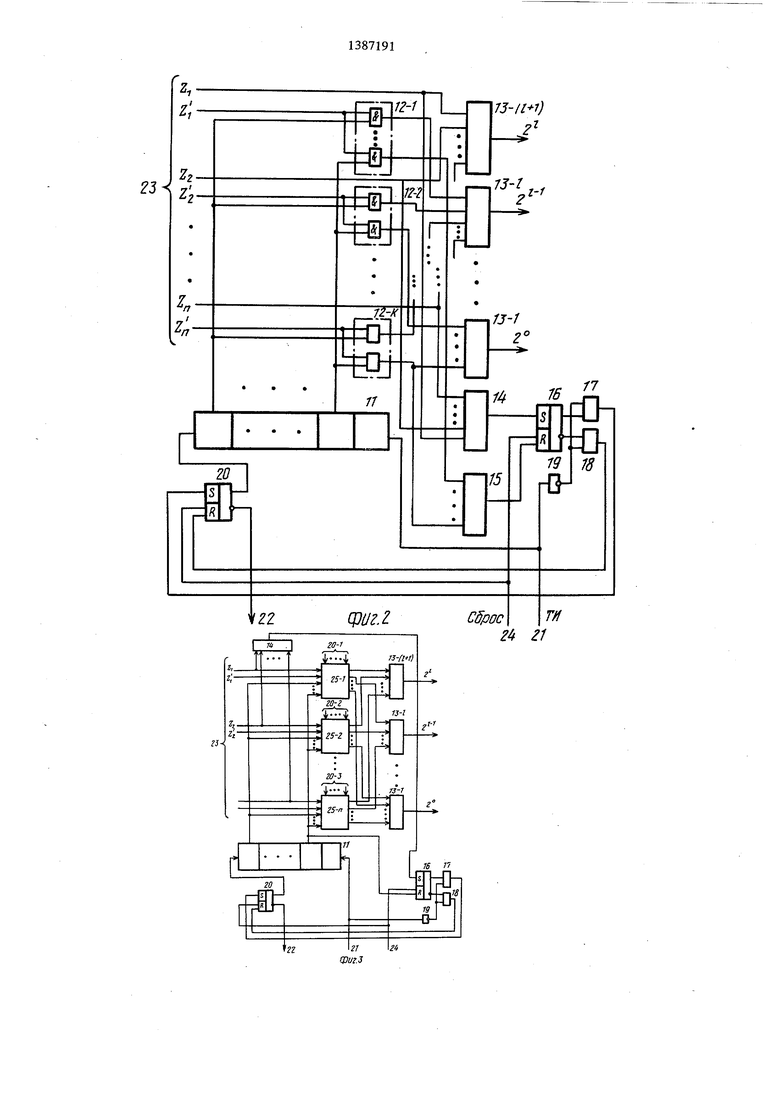

Адаптивный сканирующий мультиплексор может быт& выполнен, как показано на фиг. 6 Он содержит разряды 27-1 - 27-(п+2) .распределителя импульсов и блоки 28-1 - 28-п коммутации. Входы-выходы переноса каждого из разрядов 27-i распределителя импульсов (, 2,...п) соединены с первой группой входов-выходов блока 28-i коммутации, вторая группа входов-выходов блока 28-i коммутации (, 2, ..., п-1) соединена с третьей группой входов-выходов блока 28-(i+1), вторая группа входов-выходов блока 28-п коммутации соединена с входами-выходами переноса разряда 27 - (п+1) распределителя импульсов, соединенного другой группой входов-выходов переноса с входами-выходами переноса разряда 27-(п+2), другая группа входов-выходов которого соединена с третьей группой вхо- дов-вых одов блока 28-1 коммутации. Управляющие входы блоков 28 коммутации соединены с входными информационными

шинами 9. Выходами сканирующего типлексора являются импульсные и потенциальные выходы разрядов 27-i распределителя импульсов. Входы сброса разрядов распределителя 27-i импульсов соединены с входом сброса сканирующего мультиплексора, а их счетные входы - со счетным входом мультиплексора.

Адаптивный сканирующий мультиплексор может быть реализован при любой (регу- лирной) реализации распределителя импульсов. Разница заключается в требуемом количестве коммутаторов в каждом блоке 28 коммутации (по числу пар входов-выходов переноса в разряде распределителя импульсов). С входами каждого коммутатора соединяются одноименные выходы данного и предыдущего (последующего, если перенос в данный разряд по данному входу происходит из последующего разряда) разрядов распределителя импульсов, его первый выход соединяется с соответствующим входом данного разряда, а второй является выходом блока коммутации.

Схемная реализация разряда 27 распределителя импульсов изображена на фиг. 7 , где также показаны схемная реализация блока 28 коммутации (нижний блок).

Сканирующий мультиплексор может быть выполнен в виде распределителя импульсов на п + 1 разряд, выходы первых п разрядов которого соединены каждый с входами своего элемента И, вторые входы элементов И являются информационными входами сканирующего мультиплексора.

Выходы элементов И являются импульсными выходами разрядов сканирующего мультиплексора. При реализации разрядов распределителя импульсов, показанной на фиг. 7 (верхний блок), потенциальный выход триггера является выходом разряда.

Разряд 27 распределителя импульсов (фиг. 7) имеет два входа 29-1 и 29-2 и один выход 30 переноса с предыдущего разряда и соответственно два выхода 31 - 1 и 31-2 и один вход 32 переноса с последующего разряда. Парами входов-выходов разрядов 27 являются входы и выходы 29-1 и 31 - 1729-2 и 31-2, 32 и 30. В соответствии с этим каждый блок 28 коммутации содержит три коммутатора 33-1 - 33-3, управляющие входы которых соединены вместе и с входной щиной устройства. Вход коммутатора 33-1 соединен с выходом

входом 29-1. Вход коммутатора 33-2 соединен с выходом 31-2 разряда 27, а первый выход - с его входом 29-2. Вход коммутатора 33-3 соединен с выходом 30 разряда 27, а первый выход - с его входом 32. Выходы разряда 27 соединены с первыми входами коммутаторов 28, а вторые входы являются входами блока коммутации.

При подаче тактовых ществляется последовательн ние на выходах разрядов причем на выходах только для которых . Таким о чается опрос входных щин Х,0, что обеспечивает повы действия.

Таким образом, опрос все осуществляется не за п та вестном устройстве, а лишь

Триггер 5 по выполняемы ляется тактируемым D-тригге выше схема блока 6 сброс случаю, когда разрещение за триггера осуществляется сиг тельной полярности. В про первый элемент И блока 6

40

45

-1 разряда 27, а первый выход - с его заменить элементом И-НЕ.

55

Блок сброса может быт в виде элемента ИЛИ, вход ляются вторым и третьим а выход соединен с первым элемента И, выход которого вым выходом блока, выход соединен также с входом элем (на время , есл

5

0

Схемная реализация адаптивного сканирующего мультиплексора показана на фиг. 8 для случая схемной реализации разряда распределителя импульсов, изображенной на фиг. 7.

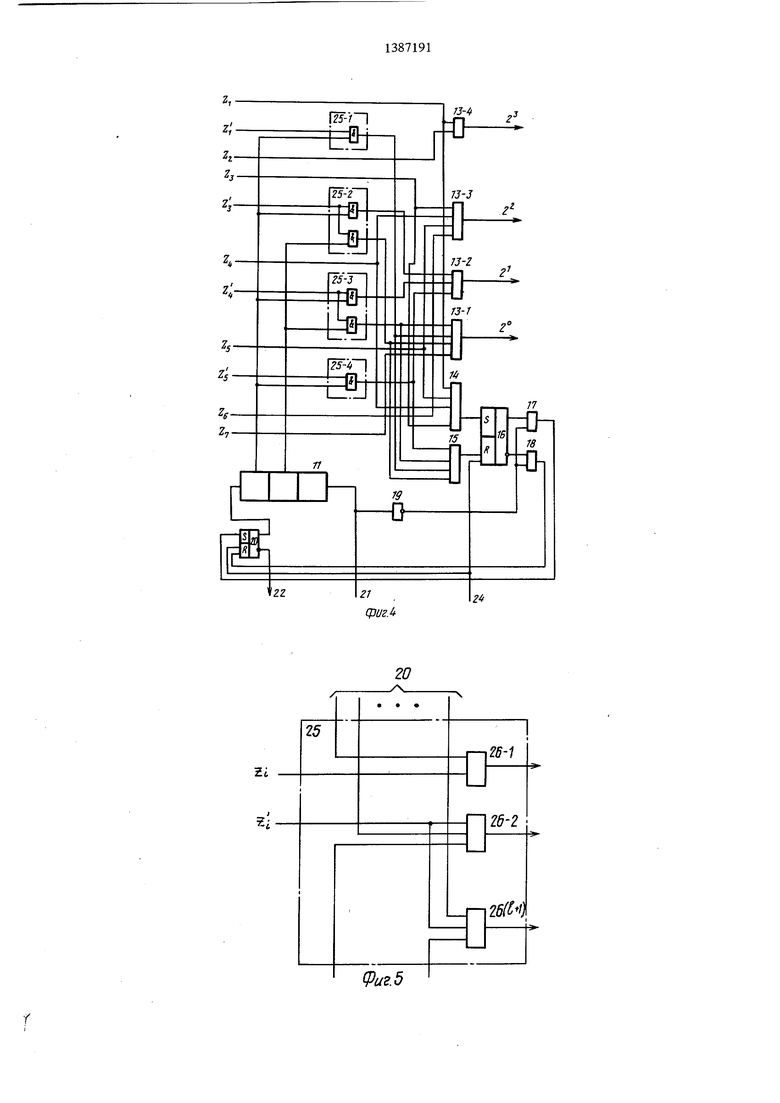

Схемная реализация коммутаторов для случая импульсов отрицательной полярности показана на фиг. 9, а для случая импульсов положительной полярности - на фиг. 4. На фиг. 4 и 9 первым входом коммутатора является вход, соединенный с нижним из трех элементов И (И-НЕ), а вторым входом - вход, соединенный с входами верхнего и среднего элементов И (И- НЕ). Первым выходом коммутатора является выход верхнего элемента И (И-НЕ).

Адаптивный сканирующий мультиплексор функционирует следующим образом.

Если на входную щину X,- подан нулевой потенциал, то блок 28-i коммутации отключает входы-выходы разряда 27-i распределителя импульсов от предыдущего и последующего разрядов и работает в режиме трансляции сигналов, поступающих на его входы с выходов блока (разрядов) 28-(i+ ,,. -f 1) и 28-(i-1) коммутации на входы бло- ков 28-(1-1) и 28-(i 4-1) соответственно. Если Х,, то блок 28-i коммутации подключает входы-выходы разряда 27-i распределителя импульсов к входам-выходам блоков 28-(i-1) и 28-(i+1) коммутации. 0 В результате все разряды 27-i распределителя импульсов, для которых Х,, оказываются отключенными и образуется распределитель импульсов только из разрядов, для которых Х, 1.

При подаче тактовых импульсов осуществляется последовательное формирование на выходах разрядов 27 импульсов, причем на выходах только тех разрядов, для которых . Таким образом исключается опрос входных щин, для которых Х,0, что обеспечивает повыщение быстродействия.

Таким образом, опрос всех входных щин осуществляется не за п тактов., как в известном устройстве, а лишь за llX/ тактов.

Триггер 5 по выполняемым функциям является тактируемым D-триггером. Описанная выше схема блока 6 сброса соответствует случаю, когда разрещение записи по Т-входу триггера осуществляется сигналом положительной полярности. В противном случае первый элемент И блока 6 сброса следует

5

0

5

заменить элементом И-НЕ.

заменить элементом И-НЕ.

55

Блок сброса может быть выполнен и в виде элемента ИЛИ, входы которого являются вторым и третьим входами блока, а выход соединен с первым входом первого элемента И, выход которого является первым выходом блока, выход элемен ы ИЛИ соединен также с входом элемента задержки (на время , если , и на

время , если , где тимп, тп - длительность импульса и паузы тактовых импульсов), выход которого соединен с входом второго элемента И, инверсный вход которого соединен с вторым входом первого элемента И и является третьим входом блока. Выход второго элемента И является вторым выходом блока. Данная схема также соответствует случаю, когда сброс блоков 1-3 и запись в триггер 5 производятся сигналом положительной полярности.

В дальнейшем при описании функционирования устройства (фиг. 1) будем полагать, что сброс всех блоков производится импульсом положительной полярности. Если схемная реализация какого-либо из блоков требует сигнала отрицательной полярности (нулевого потенциала), то на его входе сброса следует установ ить инвертор, вход которого при этом и будет входом сброса.

Распределитель импульсов в сканирующем мультиплексоре 1 (фиг. 1) может иметь любую из известных схемных реализаций комбинированного распределителя, обеспечивающего одновременно распределение импульсов и потенциалов.

Для повышения быстродействия сигнал переноса может сниматься с выхода предпоследнего п-го разряда распределителя импульсов, что обеспечит сокращение на один такт цикл работы устройства в слуti

чае 2w,-X,a.

iM

Используемый в блоке 2 (фиг. 2-4) распределитель 11 импульсов может иметь любую из известных реализаций, в том числе и реализацию, рассмотренную выще для распределителя в сканирующем мультиплексоре 1.

В схемах на фиг. 2-4 и описании функционирования полагается, что сброс распределителя 11 импульсов производится импульсом отрицательной полярности (нулевым сигналом). Если используемая схемная реализация требует для сброса сигнал положительной полярности (единичным сигналом), необходимо либо подавать сигнал на вход сброса через инвертор, либо использовать сигнал с инверсного плеча триггера 20 (фиг. 2-4).

В приводимом далее описании функционирования устройства в целом и блока 2 формирования пачек импульсов полагаем, что RS-триггеры 16 и 20 (фиг. 2-4) переключаются импульсом положительной полярности. Если использовать RS-триггеры, переключаемые импульсом отрицательной полярности (нулевым сигналом), необходимо элементы ИЛИ 14 и 15 и И 17 и 18 (фиг. 2-4) заменить элементами ИЛИ-НЕ и И-НЕ соответственно. При этом необходимо учесть, что потребуется нулевой сигнал сброса, т.е. требуется либо установка на входе сброса инвертора, обеспечивающего инвертирование сигнала сброса положите,;1ьной полярности, либо (если сброс всех блоков на фиг. 1 осуществляется нулевым сигналом) замена в блоке сброса второго элемента И элементом И-НЕ.

Напопитель 3 может быть выполнен в виде двоичного счетчика, выход переноса i-ro разряда которого соединяется со счетным входом (i-fl)-ro разряда через элемент ИЛИ, второй вход которого является вхо дом накопителя с весом 2. Количество

п разрядов накопителю равно log2(2w,-|-l) .

Схема такой реализации накопителя практи5 чески представляет собой счетчик с последовательным переносом. Входы сброса всех триггеров соединяются с входом сброса накопителя.

В описании функционирования устройства и в схемах на фиг. 1 предполагает0 ся, что переключение накопителя 2 осуществляется по переднему фронту импульса на счетном входе (полагаем импульс положительной полярности) и в течение длительности тактового импульса на его выходе

5 появляется результат. При использовании реализации накопителя 3, формирование результата на выходе которого осуществляется по заднему фронту счетных импульсов (по переднему фронту импульсов отрицательной полярности), устройство функционирует в

0 том же порядке, как описано далее. Разница заключается в том, что окончание цикла работы устройства в случае записи в накопитель 3 кода числа, большего или равного порогу а, происходит на следующем такте.

5 Для повыщения быстродействия устройства накопитель может быть реализован на счетчике с параллельным переносом. Счетным входом с весом 2 является вход первого триггера. Его прямой выход (Q-выход, на котором сигнал появляется в момент

0 прихода заднего фронта тактового импульса положительной полярности) соединяется с первым входом элемента И, второй вход которого соединяется со счетным входом первого триггера. Выход элемента И соединен со входом элемента ИЛИ, второй вход которого является входом накопителя с весом 2, а выход соединен со счетным входом триггера следующего (второго) разряда накопителя импульсов. Указанный элемент ИЛИ является первым элементом ИЛИ второго

Q разряда накопителя, а его вход, соединенный с выходом элемента И - первым входом второго разряда.

Второй и третий элементы ИЛИ второго разряда соединены первыми входами с выходом (прямым) первого триггера и его счет5 ным входом соответственно и являются соответственно вторым и третьим входами второго разряда накопителя. Вторые входы элементов ИЛИ (второго и третьего) второго

разряда накопителя соединены с вторым входом первого элемента ИЛИ. Выход второго элемента ИЛИ соедннен с первым входом первого элемента И, второй вход которого соединен с прямым выходом триггера второго разряда (р-выход, на котором сигнал появляется в момент окончания тактового импульса на счетном входе - по его заднему фронту), а выход является вторым выходом второго разряда накопителя. Выход первого элемента И соединен также с первым входом второго элемента И, второй вход которого соединен с выходом третьего элемента ИЛИ, а выход является первым выходом второго разряда накопителя. Третьим выходом второго разряда накопителя является выход третьего элемента ИЛИ.

Последующие разряды накопителя имеют такую же схемную реализацию, как и второй разряд, описанный выше, а их соединение осуществляется таким образом, что первый, второй и третий выходы i-ro разряда соединяются с первым, вторым и третьим входами (i+l)-ro разряда. Разряды накопителя, не имеющие дополнительного счетного входа, отличаются от рассмотренных выще отсутствием элементов ИЛИ, т.е. первый вход разряда соединен непосредственно со счетным входом триггера, второй вход - с первым входом первого элемента И, а третий вход - со вторым входом второго элемента И и третьим выходом. Порядок соединения разрядов сохраняется, т.е. выходы от первого до третьего i-ro разряда соединяются соответственно с входами от первого до третьего (i+l)-ro разряда.

Выходами накопителя являются прямые выходы триггеров, на которых сигнал появляется в момент появления счетного импульса на счетном входе.

Входы сброса всех разрядов накопителя (входы сброса счетных триггеров) соединяются с вхоДом сброса накопителя:

В рассмотренном случае требуется сигнал сброса отрицательной полярности (нулевой сигнал). В 1}риводимом далее описании работы устройства полагаем сигнал сброса положительной полярности. В этом случае требуется подавать сигнал сброса на входы разрядов накопителя через инвертор либо проинвертировать его в блоке сброса.

С целью повыщения быстродействия схема разряда накопителя 3, рассмотренная выше для его реализации на счетчике с параллельным переносом, может быть изменена. Вместо соединения выхода первого элемента И с первым входом второго элемента И, входы первого элемента И соединяются с первым и третьим входами второго элемента И, а его второй вход остается соединенным с выходом третьего элемента ИЛИ.

Пороговый элемент фун.кционирует следующим образом.

В исходном состоянии сканирующий мультиплексор 1, блок 2 формирования пачек импульсов и накопитель 3 сброшены. При этом в накопитель 3 записан нулевой код, а на выходе блокировки блока 2 формирования пачек импульсов присутствует еди- ничный логический сигнал, который поступает на вход элемента И 8, разрещая прохождение тактовых импульсов с выхода генератора 7 на счетный вход сканирующего мультиплексора 1.

, При поступлении тактовых импульсов на счетный вход сканирующего мультиплексора 1 он производит последовательный опрос входных информационных шин 9. При этом он последовательно подключает каждый i-й вход к i-му выходу. Если на -i-й входной 5 шине имеется единичный сигнал, то во время ее опроса единичный сигнал появляется на i-M выходе сканирующего мультиплексора 1 (каждый i-й выход содержит две щины, по которым подаются импульсный и потенциальный выходной сигнал i-ro разряда 0 сканирующего мультиплексора, причем импульсный сигнал имеет место только в течение длительности тактового импульса, а потенциальный - также и в течение паузы до прихода следующего тактового импульса 5 на вход мультиплексора). Единичный сигнал с i-ro выхода сканирующего мультиплек- сора 1 поступает на управляющий вход блока 2 формирования пачек импульсов. Если в двоичном представлении Wt имеется только одна единица в j-M разряде с весом , то 0 импульс с выхода мультиплексора 1 проходит на выход блока 2 и в течение длительности тактового импульса на информационном выходе блока 2, имеющем вес 2 появляется единичный сигнал, поступающий на вход-накопителя 3, имеющий вес , при 5 этом к содержимому накопителя прибавляется код числа 2 . Далее на следующем такте происходит опрос следующего входа. Если в двоичном представлении веса w, опрашиваемого входа имеется более одной единицы, то в момент поступления им- пульса на управляющий вход блока 2 формирования пачек импульсов он инициализируется, при этом в течение длительности текущего импульса и последующих тактовых импульсов на выходах блока 2 с весами, 5 равными весам единичных разрядов двоичного представления веса w, входа, появляются единичные сигналы, поступающие на входы накопителя 3 с соответствующими весами, который при этом прибавляет к своему содержимому коды чисел, равные ве- 0 сам единичных разрядов двоичного представления веса W,.

После окончания тактового импульса, по которому производится опрос данной входной щины устройства, на выходе блокировки блока 2 появляется нулевой сигнал, поступающий на вход элемента И 8 и запрещающий дальнейщее прохождение тактовых импульсов на счетный вход сканирующего

мультиплексора 1. По окончании цикла работы блока 2 формирования пачек импульсов, в течение которого к содержимому накопителя 3 прибавляется код числа Wi, в паузу между тактовыми импульсами на выходе блокировки блока 2 появляется единичный потенциал и следующий тактовый импульс проходит на счетный вход Сканирующего мультиплексора 1. Работа порогового элемента происходит таким образом до момента появления на выходах накопителя, кода числа, большего или равного порогу элемента, или до момента опроса всех входов устройства.

В первом случае в момент, когда на вы- ходах накопителя 3 появляется код числа, больщего или равного порогу а, на выходе блока 4 формирования порога появляется единичный сигнал, поступающий на информационный вход триггера 5 и третий вход блока 6 сброса. При этом в течение длительности тактового импульса на первом выходе блока 6 сброса появляется единичный сигнал, поступающий на вход резрещения записи триггера 5, разрещая запись в него единичного сигнала с выхода блока 4 формирования порога, при этом на выходе триггера 5 появляется единичный сигнал.

Во втором случае после опроса всех входов X, в накопителе 8 оказывается записан код числа, меньщего порога а. При поступлении очередного тактового импульса на выходе переноса сканирующего мультиплексора 1 появляется единичный сигнал, поступающий на вход блока 6 сброса. На первом выходе блока б сброса появляется единичный сигнал, разрещающий запись в триггер 5 нулевого сигнала с выхода блока 4 формирования порога.

В обоих рассмотренных случаях после записи в триггер 5 результата вычисления, на втором выходе блока 6 сброса в меж ду тактовыми импульсами появляется единич ный сигнал, поступающий на входы сброса

сканирующего мультиплексора 1, блока 2 формирования пачек импульсов и накопителя 3, возвращающий их в исходное состояние, гЦикл работы порогового элемента оконпчен. Если 2w,, то на выходе триггера 5

10

присутствует единичный сигнал, в противном случае - нулевой.

Формула изобретения

Пороговый элемент, содержащий триггер, выход которого соединен с выходом по5 рогового элемента, сканирующий мультиплексор, соединенный информационными входами с входными информационными шинами порогового элемента, входом сброса - с входом сброса накопителя и вторым выходом блока сброса, соединенного первым

0 входом с выходом генератора тактовых импульсов, вторым входом - с выходом переноса сканирующего мультиплексора, третьим входом - с информационным входом триггера, а первым выходом - с входом разрешения записи триггера, отличающийся тем,

что, с целью повышения быстродействия, введены блок формирования пачек им уль- сов, блок формирования порога и элемент И, причем блок формирования порога соединен входами с выходами накопителя, а

Q выходом - с информационным входом триггера и третьим входом блока сброса, блок формирования пачек импульсов соединен управляющими входами с информационными выходами сканирующего мультиплексора, счетным входом - с первым входом элемента И и выходом генератора тактовых им5

пульсов, группой выходов - со счетными входами накопителя, входом сброса - с вторым выходом блока сброса, а выходом блокировки - с вторым входом элемента И, выход которого соединен со счетным входом сканирующего мультиплексора.

Z,

г;

5 ;Zs-2,.

22

/7

тО-1

7,

f7

(риг4

г

u2.7

.8

Фиг.З

Авторы

Даты

1988-04-07—Публикация

1986-05-28—Подача