Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении различных устройств обработки дискретной информации.

Целью изобретения является повышение быстродействия.

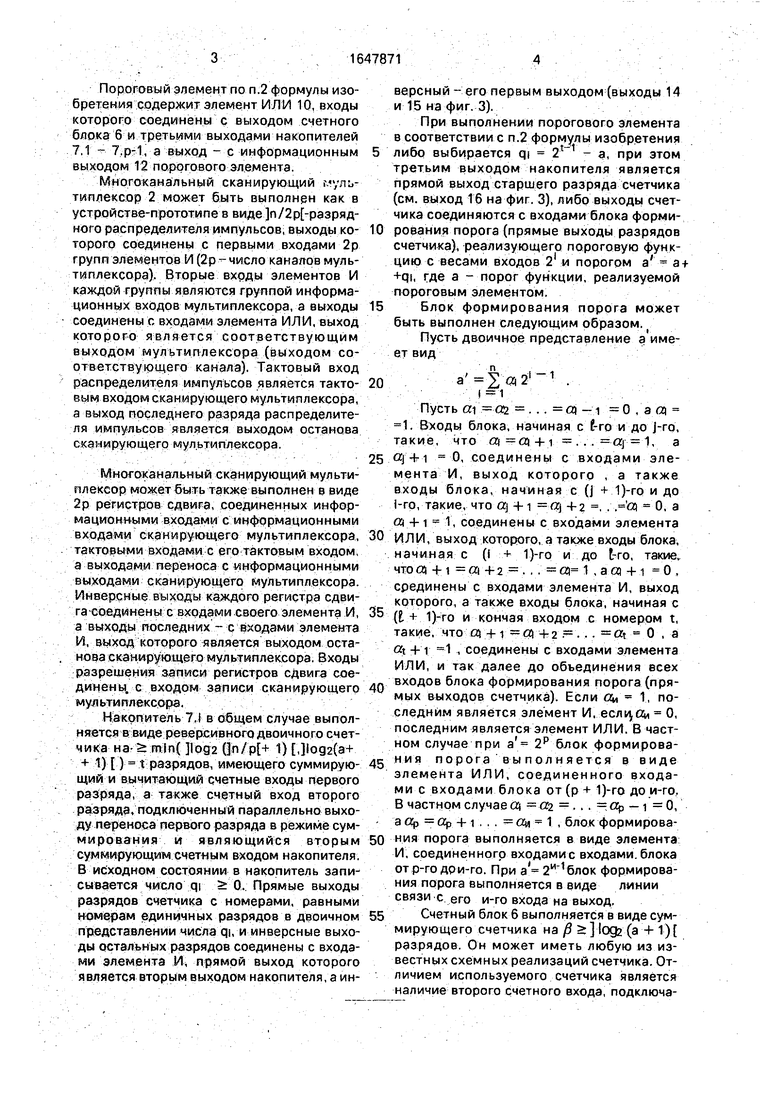

На фиг. 1 изображена структурная схема порогового элемента; на фиг. 2 - структурная схема порогового элемента по п.2 формулы изобретения; на фиг. 3 - схема накопителя.

Пороговый элемент содержит генератор 1 тактовых импульсов, многоканальный сканирующий мультиплексор 2, триггер 3, полусумматоры 4.1 - 4,р, элемент ИЛИ 5, счетный блок 6, накопители 7.1 - 7.р-1, элементы И 8.1 - 8.р-1, элемент И 9, элемент ИЛИ 10, входные информационные шины 11, информационный выход 12, выход 13 конца работы порогового элемента.

Многоканальный сканирующий мультиплексор 2 соединен тактовым входом с выходом генератора 1 тактовых импульсов,

информационными входами с входными информационными шинами 11, выходом останова - с входом триггера 3, i-м и (р + ij-м выходами (f 1,..., р) - с входами полусумматора 4.I. Выходы суммы и переноса полусумматора 4.J 0 1,2 р-1) соединены с

первым и вторым счетными входами накопителя 7J, первый выход которого соединен с первым входом элемента И 8.J, соединенного входами с выходом генератора 1 тактовых импульсов 1, выходом триггера 3 и вторыми выходами накопителей 7.1 - 7J-1, а выходом с вычитающим входом накопителя 7.J и j-м входом элемента ИЛИ 5, соединенного р-м входом с выходом суммы полусумматора 4.р, а выходом с первым счетным входом счетного блока б. Второй счетный вход последнего соединен с выходом переноса полусумматора 4.р, а выход - с информационным выходом 12 порогового элемента. Вторые выходы порогового элемента соединены с входами элемента И 9, соединенного входом с выходом триггера 3, а выходом с выходом 13 конца работы порогового элемента.

XI

00

XI

Пороговый элемент по п.2 формулы изобретения содержит элемент ИЛИ 10, входы которого соединены с выходом счетного блока б и третьими выходами накопителей 7,1 - 7.р-1, а выход - с информационным выходом 12 порогового элемента.

Многоканальный сканирующий мультиплексор 2 может быть выполнен как в устройстве-прототипе в виде п/2р -разряд- ного распределителя импульсов, выходы которого соединены с первыми входами 2р групп элементов И (2р - число каналов мультиплексора). Вторые входы элементов И каждой группы являются группой информационных входов мультиплексора, а выходы соединены с входами элемента ИЛИ, выход которого является соответствующим выходом мультиплексора (выходом соответствующего канала). Тактовый вход распределителя импульсов является тактовым входом сканирующего мультиплексора, а выход последнего разряда распределителя импульсов является выходом останова сканирующего мультиплексора.

Многоканальный сканирующий мультиплексор может быть также выполнен в виде 2р регистров сдвига, соединенных информационными входами с информационными входами сканирующего мультиплексора, тактовыми входами с его тактовым входом, а выходами переноса с информационными выходами сканирующего мультиплексора. Инверсные выходы каждого регистра сдви- га-соединены с входами своего элемента И, а выходы последних - с входами элемента И, выход которого является выходом останова сканирующего мультиплексора. Входы разрешения записи регистров сдвига соединены, с входом записи сканирующего мультиплексора.

Накопитель 7J в общем случае выполняется в виде реверсивного двоичного счетчика на- min( Jloga 1) ,11од2(а+ + 1) ) t разрядов, имеющего суммирующий и вычитающий счетные входы первого разряда, а также счетный вход второго разряда, подключенный параллельно выходу переноса первого разряда в режиме сум- мирования и являющийся вторым суммирующим счетным входом накопителя. В исходном состоянии в накопитель записывается число qi 0. Прямые выходы разрядов счетчика с номерами, равными номерам единичных разрядов в двоичном представлении числа qi, и инверсные выходы остальных разрядов соединены с входами элемента И, прямой выход которого является вторым выходом накопителя, а инверсный - его первым выходом (выходы 14 и 15 на фиг. 3).

При выполнении порогового элемента в соответствии с п.2 формулы изобретения

либо выбирается qi - а, при этом третьим выходом накопителя является прямой выход старшего разряда счетчика (см. выход 16 на фиг. 3), либо выходы счетчика соединяются с входами блока форми0 рования порога (прямые выходы разрядов счетчика), реализующего пороговую функцию с весами входов 21 и порогом а at +qi, где а - порог функции, реализуемой пороговым элементом.

5 Блок формирования порога может быть выполнен следующим образом.

Пусть двоичное представление а име- ет вид

.

1

Пусть ... 0 , a oi 1. Входы блока, начиная с f-ro и до j-ro, такие, что at 034-1 5. . . aj 1, а

5 Щ +1 О соединены с входами элемента И, выход которого , а также входы блока, начиная с (J + 1)-го и до 1-го, такие, что а -ы щ 4- 2 ...- (% - 0, а «1 + 1 1, соединены с входами элемента

0 ИЛИ, выход которого, а также входы блока, начиная с (i + 1)-го и до t-ro, такие что ж +1 at 4- 2 ... ся 1 , а cq +1 0, срединены с входами элемента И, выход которого, а также входы блока, начиная с

5 (I + 1)-Го и кончая входом с номером t, такие, что ... 0 , а #t + 1 1 , соединены с входами элемента ИЛИ, и так далее до объединения всех

входов блока формирования порога (пря- мых выходов счетчика). Если «и 1, последним является элемент И, О, последним является элемент ИЛИ. В частном случае при а 2Р блок формирова5 ния порога выполняется в виде элемента ИЛИ, соединенного входами с входами блока от (р + 1)-го до и-го. В частном случае ,--сьр-1 0, + i..., блок формирова0 ния порога выполняется в виде элемента И, соединенного входамис входами.блока от р-го дри-го. При а блок формирования порога выполняется в виде линии связи с его и-ro входа на выход,

5 Счетный блок 6 выполняется в виде суммирующего счетчика на /3 IfXfc (a 4-1) разрядов. Он может иметь любую из известных схемных реализаций счетчика. Отличием используемого счетчика является наличие второго счетного входа, подключаемого к счетному входу второго разряда счетчика параллельно переносу из первого разряда. Такой счетчик может быть выполнен, например, на Tt-триггерах, соединенных последовательно, причем выход переноса каждого триггера соединен с входом переноса (счетным входом) следующего триггера, выход переноса первого триггера соединен с входом переноса (счетным входом) второго триггера через элемент ИЛИ, второй вход которого является вторым счетным входом счетного блока. 8 исходном состоянии в счетчик записан код числа q 0.

При выборе q 2 1 -а прямой выход старшего разряда счетчика является выходом счетного узла. В противном случае прямые выходы счетчика соединяются с входами блока формирования порога, равного q + а, реализуемого в описанном выше порядке, выход которого и является выходом счетного блока.

Триггер 3, как и в устройстве-прототипе, выполняется в виде RS-триггера при реализации многоканального сканирующего мультиплексора на регистрах сдвига или при его реализации на распределителе импульсов, когда импульс на выходе останова синхронизирован с паузой между тактовыми импульсами, либо в виде счетного триггера, когда многоканальный сканирующий мультиплексор выполнен на распределителе импульсов, а импульс на выходе останова синхронизирован с тактовым импульсом.

Функционирует предлагаемый пороговый элемент следующим образом.

В исходном состоянии многоканальный сканирующий мультиплексор 2, счетный блок 6, накопители 7 и триггер 3 сброшены. При этом на выходе триггера находится нулевой сигнал, блокирующий прохождение тактовых импульсов через элементы И 8. При выполнении сканирующего мультиплексора 2 на регистрах сдвига входной код с входных информационных шин 11 записан в регистры сдвига.

При поступлении тактовых импульсов с выхода генератора 1 тактовых импульсов на тактовый вход многоканального сканирующего мультиплексора 2 последний преобразует параллельный код, подаваемый на группу входных информационных шин 11.1 (входы 1-го канала сканирующего мультиплексора 2), в последовательность импульсов на его 1-м выходе (выходе (-го канала). Причем за время работы мультиплексора 2 на его 1-м выходе формируется число импульсов, равное числу единичных сигналов на группе входных информационных шин 11.1.

Импульсы с 1-го и (р + выходов сканирующего мультиплексора 2 поступают на входы полусумматора 4.1. Если импульс поступает на один его вход, это вызывает им- 5 пульс на его выходе суммы, соединенном с первым счетным входом накопителя 7.1, при Кр и первым счетным входом накопителя счетного блока 6 через элемент ИЛИ 5 при I р, к содержимому которых при этом при10 бавляется единица. Если импульс поступает на оба входа полусумматора 4.I, это вызывает импульс на его выходе переноса, соединенном с вторым суммирующим счетным входом накопителя 7.I при р и счетного

5 блока 6 при I р, к содержимому которых при этом прибавляется число два.

Если за время работы сканирующего мультиплексора 2 на входы полусумматора 4.р поступает не менее а импульсов, то на

0 выходе счетного блока 6 формируется единичный сигнал, поступающий на выход 12 порогового элемента, являющийся результатом работы и одновременно свидетельст- вующий об окончании цикла работы.

5 Результат снимается с выхода 12 счетного блока 6. Если за время работы сканирующего мультиплексора 2 в счетном блоке 6 не происходит накопление требуемого числа импульсов, то работа продолжается в опи0 санном выше порядке до опроса всех входных информационных шин, для чего потребуется }п/2р тактов, где п - разрядность входного кода. При этом по окончании работы многоканального сканирующего

5 мультиплексора 2 он самоблокируется и далее на своих информационных выходах импульсов не формирует. При этом на его выходе останова формируется импульс, пе реключающий триггер 3 (в паузу между так0 товыми импульсами). При этом на выходе триггера 3 появляется единичный сигнал, разрешающий прохождение тактовых импульсов через элементы И 8.

Далее происходит процесс последо5 вательного пересчета содержимого накопителей 7 в счетный блок 6. Пусть 7.1 - наименьший номер накопителя, в который записан код, отличный от исходного qi, т.е. за время работы многоканального сканиру0 ющего мультиплексора 2 на его счетные входы поступают импульсы, при этом на его первом выходе, соединенном с входом элемента И 8, находится единичный сигнал, а на втором, соединенном с входами элемен5 тов И 8.1+1 - 8.р-1, - нулевой, запрещающий прохождение тактовых импульсов на их выходы. Таким образом, на всех входах элемента И 8.I, соединенных с вторыми выходами накопителей 7.1-7.1-1, имеются единичные сигналы. В результате тактовые

импульсы проходят через элемент И 8.I на вычитающий счетный вход накопителя 7.1, от содержимого которого при этом вычитается единица, и через элемент ИЛИ 5 на счетный вход (первый) счетного блока 6, к содержимого которого при этом прибавляется единица. Работа продолжается таким образом до возвращения накопителя 7. в исходное состояние. При этом на его первом выходе появляется нулевой сигнал, запрещающий дальнейшее прохождение тактовых импульсов на выход элемента И 8.1, а на втором выходе - единичный сигнал, разрешающий прохождение тактовых импульсов на выходы элементов И 8.1+1 - 8.р-1. Далее аналогично осуществляется пересчет содержимого накопителей 7.I+ 1 - 7.р-1 в счетный блок 6.

п

Если Ј xi - а 1 то в некоторый момент

i 1

времени в счетчике счетного блока будет записан код числа q + а, где q - код числа исходного состояния счетчика счетного блока 6. При этом на выходе счетного блока б появляется единичный сигнал, поступающий на выход 12 порогового элемента, являющийся результатом работы и свидетельствующий об окончании цикла работы.

Если Ј xi а , то по окончании переi 1

счета содержимого всех накопителей 7 в счетный блок 6 на их вторых выходах оказываются единичные сигналы, свидетельствующие об их возвращении в исходное состояние, что вызывает единичный сигнал на выходе элемента И 9, свидетельствующий об окончании цикла работы и поступающий на выход 13 конца работы порогового элемента.

При этом с выхода 12 порогового элемента снимается нулевой выходной сигнал.

п

Таким образом, при Ј xi а на выходе i 1

порогового элемента формируется единичный сигнал, а в противном случае - нулевой.

В случае устройства по п.2 формулы изобретения, работа порогового элемента осуществляется в том же порядке, что и описанный выше.

Разница заключается в том, что при поступлении на входы некоторого полусумматора 4.1 числа импульсов, равного порогу а или а + 1, в счетчике накопителя 7.I будет записан код соответствующего числа, что вызывает единичный сигнал на его третьем выходе, поступающий на вход элемента ИЛИ 10, что вызывает на его выходе

12, являющемся информационным выходом порогового элемента, единичный сигнал, являющийся результатом работы и свидетельствующий об окончании цикла работы.

Работа порогового элемента оканчивается при появлении единичного сигнала на одном из выходов 12 или 13. Результат снимается с информационного выхода 12 порогового элемента.

0 Таким образом, на выходе порогового элемента формируется единичный сигнал, если на его входы подано число единичных сигналов большее или равное порогу, в противном случае на выходе порогового эле5 мента формируется нулевой сигнал.

Пороговый элемент обеспечивает повышение быстродействия.

Формула изобретения

1.Пороговый элемент, содержащий 0 многоканальный сканирующий мультиплексор, соединенный тактовым входом с выходом генератора тактовых импульсов, информационными входами с входными информационными шинами, выходом остано5 ва с входом триггера, элемент ИЛИ, соединенный выходом со счетным входом счетного блока, выход которого является информационным выходом порогового элемента, р-1 накопителей и р элементов И,

0 первый выход 1-го накопителя соединен с входом 1-го элемента И, выход которого соединен с i-м входом элемента ИЛИ и вычитающим входом 1-го накопителя, а входы - с выходом генератора тактовых импульсов,

5 триггера и вторыми выходами накопителей от первого до (М)-го, вторые выходы накопителей соединены с входами элемента И, выход которого соединен с выходом Окончание работы порогового элемента, а вход 0 с выходом триггера, отличающийся тем, что, с целью повышения быстродействия, в него введены р-1 полусумматоров, причем входы 1-го полусумматора соединены с i-м и (р+1)-м информационными выхода5 ми многоканального сканирующего

мультиплексора (1 1,2р), выход суммы

р-го полусумматора соединен с входом элемента ИЛИ, а выход переноса - с вторым суммирующим входом счетного блока,вы0 ходы суммы и переноса j-ro полусумматора 0 1- 2 .... р-1) соединены с первым и вторым суммирующими входами j-ro накопителя.

2.Элемент по п. 1,отличающийся 5 тем, что, с целью повышения быстродействия, третьи выходы накопителей соединены с входами второго элемента ИЛИ, соединенного входом с выходом счетного блока, а выходом с информационным выходом порогового элемента.

j/J j

1

Јj

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОРОГОВЫЙ ЭЛЕМЕНТ | 1987 |

|

RU2034401C1 |

| Пороговый элемент | 1987 |

|

SU1584098A1 |

| Устройство для обнаружения ошибок в равновесном коде К из @ | 1987 |

|

SU1564731A1 |

| Пороговый элемент | 1985 |

|

SU1297219A1 |

| Пороговый элемент | 1985 |

|

SU1297220A1 |

| Пороговый элемент | 1986 |

|

SU1387185A2 |

| Пороговый элемент | 1983 |

|

SU1126924A1 |

| Устройство для контроля равновесного кода | 1987 |

|

SU1580563A1 |

| Пороговый элемент | 1986 |

|

SU1387191A1 |

| Пороговое устройство (его варианты) | 1984 |

|

SU1352449A1 |

Изобретение относится к области авто- магикм и вычислительной техники и может быть использовано при построении различных устройств обработки дискретной информации. Цель изобретения - повышение быстродействия - достигается тем, что в пороговый элемент введены полусумматоры 4.1 - 4.р. Устройство также содержит генератор 1 тактовых импульсов, многоканальный сканирующий мультиплексор 2, триггер 3, элемент ИЛИ 5, счетный блок б, накопители 7.1 - 7.р-1, элементы И 8.1 - 8.р-1, элемент И 9. элемент ИЛ И 10, входные информационные шины 11, информационный выход 12, выход 13 конца работы порогового элемента. 1 з.п.ф-лы, 3 ил.

| Пороговый элемент | 1984 |

|

SU1277370A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-05-07—Публикация

1987-12-08—Подача