со о

00

;о

QO

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый элемент | 1986 |

|

SU1387191A1 |

| Пороговый элемент | 1985 |

|

SU1297219A1 |

| Пороговый элемент | 1985 |

|

SU1297220A1 |

| Пороговый элемент | 1987 |

|

SU1584098A1 |

| Пороговое устройство (его варианты) | 1984 |

|

SU1352449A1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ | 1987 |

|

RU2034401C1 |

| Пороговый элемент | 1983 |

|

SU1126924A1 |

| Пороговый элемент | 1984 |

|

SU1261100A1 |

| Пороговый элемент | 1987 |

|

SU1647871A1 |

| Пороговый элемент | 1984 |

|

SU1236602A1 |

.{I

Изобретение относится к автоматике и вычислительной технике и может быть использовано для формирования пороговой функции для логических сигналов в системах обработки дискретной информации.

Цель изобретения - повышение быстродействия и упрощение.

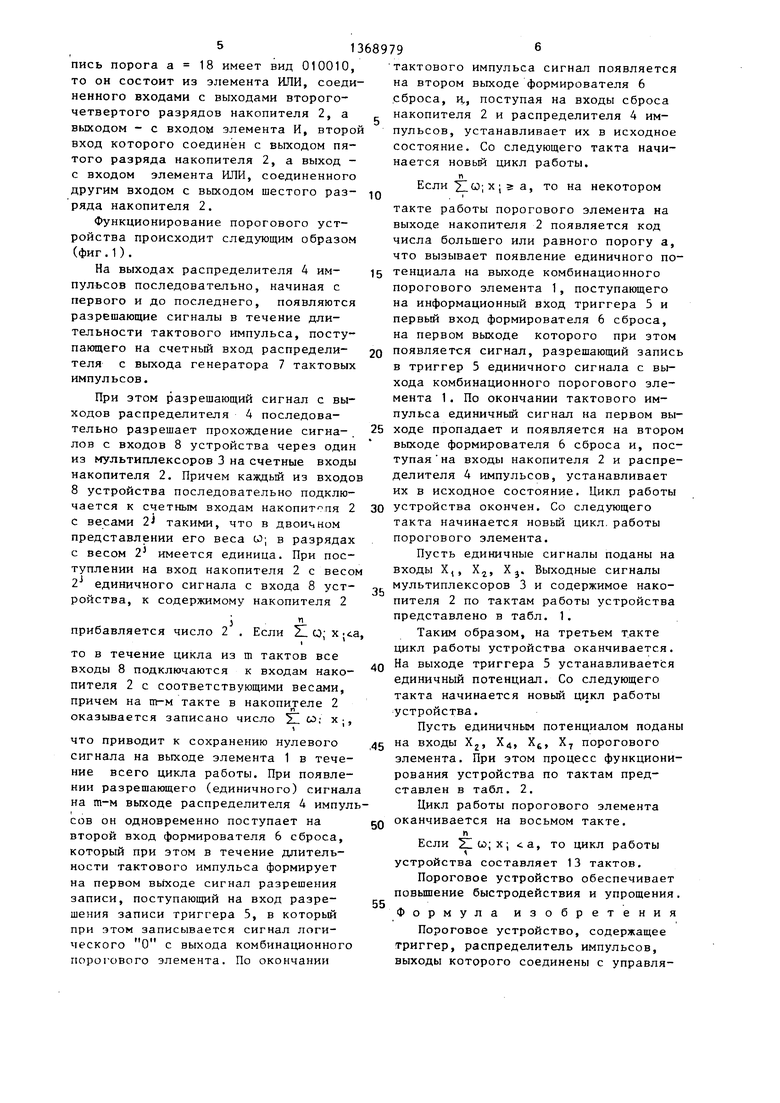

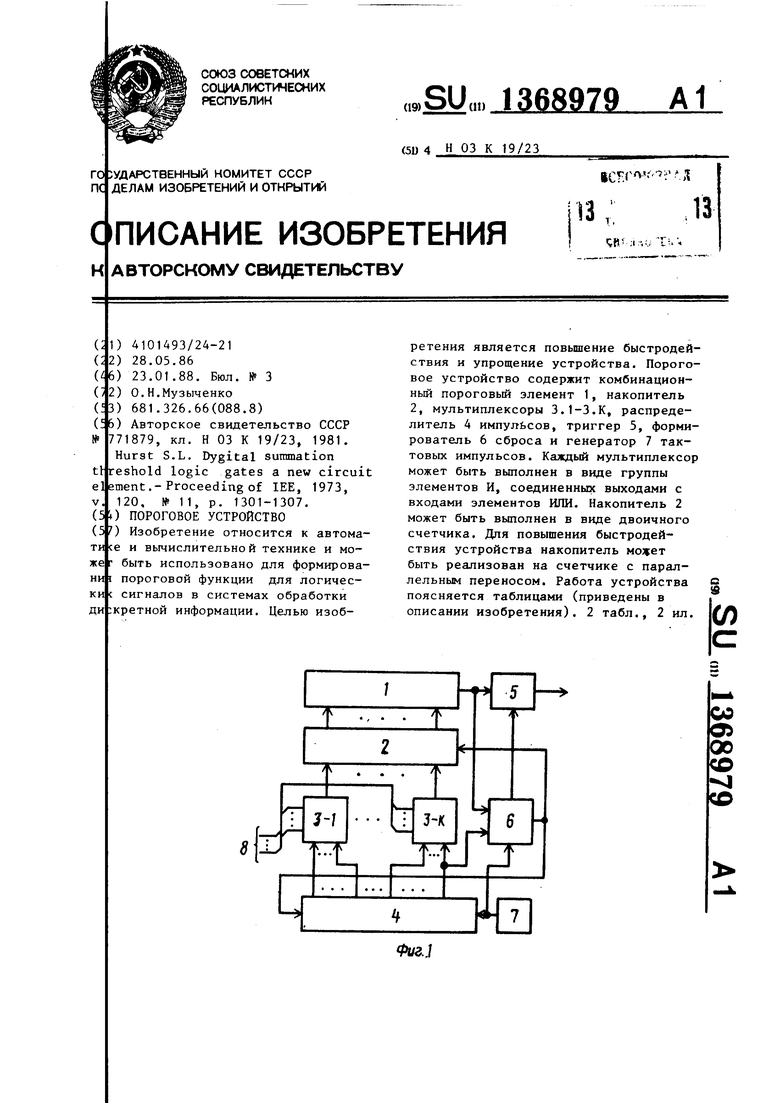

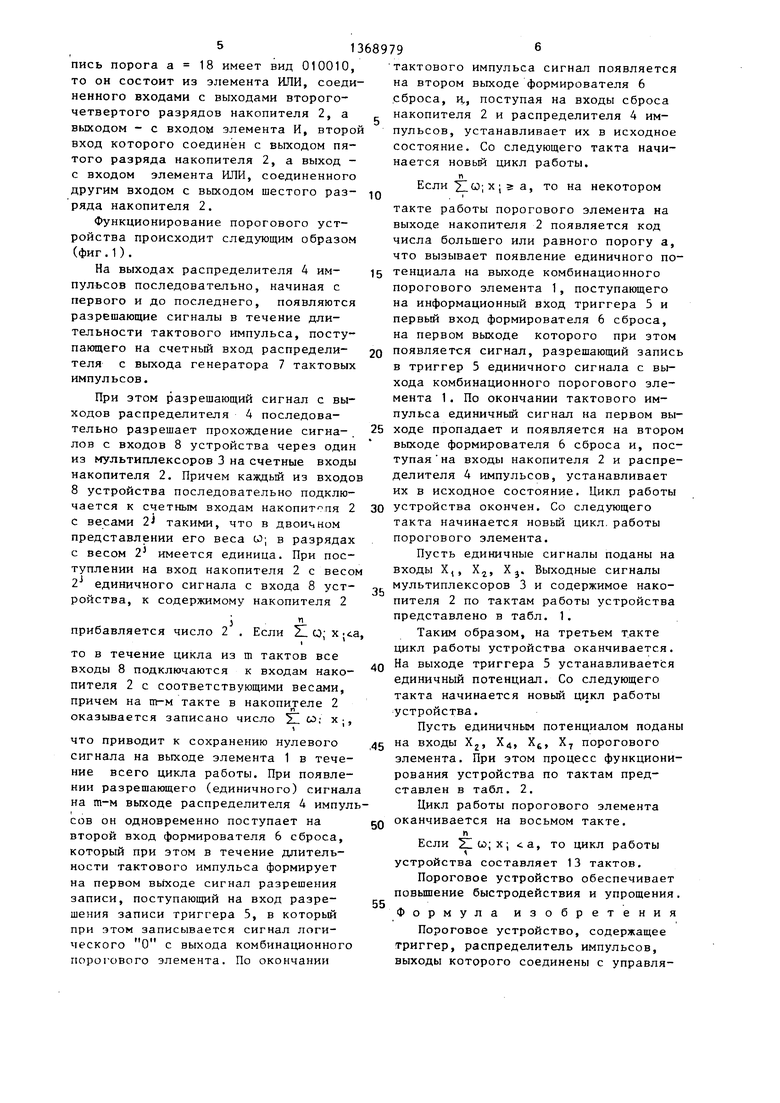

На фиг.1 изображена структурная схема предлагаемого порогового устройства для общего случая; на фиг.2- схема предлагаемого порогового устройства для случая семи входов с весами

5

7,

15

OD 6,

СО, 9, C0i 8, 00 7,

б 4, CD, 1.

Пороговое устройстйо содержит комбинационный пороговый элемент 1, накопитель 2, мультиплексоры 3-1-3-К, распределитель А импульсов, триггер 20-1 и г

5, формирователь 6 сброса и генератор log ( 1л . Схема такой реали J I L

Накопитель 2 может быть выполнен в виде двоичного счетчика, отличающегося тем, что выход переноса i-ro разряда соединяется со счетным входом i+1-го разряда через элемент ИЛИ, второй вход которого является входом накопителя с весом 2. Количество разрядов накопителя равно

7 тактовых импульсов.

Выходы распределителя импульсов 4 соединены с управляющими входами мультиплексоров 3-1-3-К, информацион- 25 ные входы которых соединены с входными информационными пшнами 8, а выходы - со счетными входами накопителя 2, соединенного выходами с входами комбинационного порогового эЛе- ЗО мента 1, выход которого соедине с информационным входом триггера 5 и первым входом формирователя 6 сброса, соединенного вторым и третьим

зации накопителя приведена на фиг.2. Практически она представляет собой счетчик с последовательным переносом

В описании функционирования устройства : и схемах (фиг.1 и 2) предполагается, что переключение накопителя 2 осуществляется по переднему фронту импульса на счетном входе (полагаем импульс положительной полярности) и в течение длительности тактового импyhьca на его выходе появляется результат. При использовании реализации накопителя 2, формирование

В описании функционирования устройства : и схемах (фиг.1 и 2) предполагается, что переключение накопителя 2 осуществляется по переднему фронту импульса на счетном входе (полагаем импульс положительной полярности) и в течение длительности тактового импyhьca на его выходе появляется результат. При использовании реализации накопителя 2, формирование

входами с последним выходом распреде- g результата на выходе которого осуще- лителя (выходом последнего разряда) ствляется по заднему фронту счетных и

4 импульсов и генератора 7 тактовых импульсов, первым выходом - с входом разрешения записи триггера 5, а вторым выходом - с входами сброса накопителя 2 и распределителя А импульсов, счетный -вход которого соединен с выходом генератора 7 тактовых импульсов. Причем количество К мультиплексоров 3 равно количеству ненулевых разрядов в двоичном представлении дизъюнкции двоичных представлений (поразрядной) весов входов О; (i 1, ..., п. Каждый мультиплексор J-j, соединенный выходом с входом накопителя log (со

формационными входами с теми входными шинами 8, в двоичном- представлении веса которых в разряде с весом 2 имеется единица. Порядок соединения выходов распределителя 4 импульсов с входами мультиплексоров 3 произвольный. Единственным требованием явимпульсов, устройство функционирует в том же порядке, как описано, разни40

2 с весом 7. (с 0,1,..., «а« + ),- соединен ин- .

цикла работы устройства в случае записи в накопитель кода числа большег порога а происходит на следующем такте (сигнал на второй вход блока 6 сброса при этом должен подаваться с 45 выхода m+1-ro разряда распределителя 4 импульсов).

Для повышения быстродействия устройства накопитель может быть реализован на счетчике с параллельным переносом.

50

55

U Формирователь может быть вьтолнен в виде элемента ИЛИ 9, входы которого являются первым и вторым входами блока, а выход соединен с первым входом первого элемента И 10, выход которог является первым выходом блока, выход элемента ИЛИ соединен также с входом элемента 11 задержки (на время

-1 и г

ляется соединение каждого выхода распределителя 4 имПульсов только с одним входом одного из мультиплексоров 3.

Каждый мультиплексор 3 может быть выполнен в виде группы элементов И, соединенных выходами с входами элемента ИЛИ. Один вход каждого элемента И является управляющим, а второй - информационным.

Накопитель 2 может быть выполнен в виде двоичного счетчика, отличающегося тем, что выход переноса i-ro разряда соединяется со счетным входом i+1-го разряда через элемент ИЛИ, второй вход которого является входом накопителя с весом 2. Количество разрядов накопителя равно

зации накопителя приведена на фиг.2. Практически она представляет собой счетчик с последовательным переносом

В описании функционирования устройства : и схемах (фиг.1 и 2) предполагается, что переключение накопителя 2 осуществляется по переднему фронту импульса на счетном входе (по лагаем импульс положительной полярности) и в течение длительности тактового импyhьca на его выходе появляется результат. При использовании реализации накопителя 2, формирование

результата на выходе которого осуще- ствляется по заднему фронту счетных

результата на выходе которого осуще- ствляется по заднему фронту счетных

импульсов, устройство функционирует в том же порядке, как описано, разни

цикла работы устройства в случае записи в накопитель кода числа большего порога а происходит на следующем такте (сигнал на второй вход блока 6 сброса при этом должен подаваться с выхода m+1-ro разряда распределителя 4 импульсов).

Для повышения быстродействия устройства накопитель может быть реализован на счетчике с параллельным переносом.

U Формирователь может быть вьтолнен в виде элемента ИЛИ 9, входы которого являются первым и вторым входами блока, а выход соединен с первым входом первого элемента И 10, выход которого является первым выходом блока, выход элемента ИЛИ соединен также с входом элемента 11 задержки (на время

а ti, 2 -t-odj2 - ,+ ... + .,4,2- -н .

i Гп . если Гимп i,

1 и на время

/7 Т

Э - имп

если с

HWn

где

- длительность импульса и паузы тактовых импульсов), выход которого соединен с входом второго элемента И 12, инверсный вход которого

оединен с вторым входом первого элемента И 10 и является третьим входом блока. Выход второго элемента И 12 является вторым выходом блока.

В том случае, когда сброс накопителя 2 и распределителя 4 импульсов требует импульса отрицательной полярности, второй элемент И 12 следует заменить элементом И-НЕ. В схемах (фиг.1 и 2) полагают, что для сброса указанных блоков требуется импульс положительной полярности.

Комбинационный пороговьй элемент является пороговым элементом с весам входов, равными 2 (i 0,1,2,...), i может иметь любую из известных реализаций. Он может быть, например, выполнен на элементах И, ИЛИ следующим образом. Пусть двоичное представлени порога

+ . . . ote.,2 +

+ 0. + oi-j, 2 р-г

... -- afp.,2 « Р де р J log,j( 1) .

+ й(р 2

р-1

. . . oij., 0. Вы начиная с 1-го и

Пусть 0, ,

соды накопителя 2,

;о j-ro, такие, что Ы j , ...

1, а eij ,, О, соединены с хо; ами элемента И, выход которо.го, I также выходы накопителя 2, начиная : j + 1-го и до i-ro такие, чтоо, fi,2. ... о ; О, а oiit, 1,

оединены с входами элемента ИЛИ, вы сод которого, а также выходы накопи- еля 2, начиная с (i+1)-ro и конча ыходом с номером t, таких, ,

i 1 а ОС , 0, сое- инены со входами элемента И, и так алее до объединения всех выходов на- опителя 2. Если

последним

вляется элемент И, если ei р О, по- ледним является элемент ИЛИ, выход оторого является выходом блока форшрования порога 1. В частном случае

ри а 2 блок формирования порога

вьтолняется в виде элемента ИЛИ в соответствии с приведенным описа:ием), если же все Ы; , начиная с не- оторого равны единице, то блок фор1ирования порога вьтолняется в виде

лемента И.

Рассмотрим предлагаемое техническое решение для случая семи входов с весями со, 9, cOj 8, со 7, со, . 7, и, 6, са 4, ц 1 и порога а 18 (фиг.2).

Двоичные представления весов входов имеют вид

W, 1 COj 1 СО, О

СО, «5

07

О О О

о

о о 1 1 1 1 о

о о 1 1 1

о о

1

о 1 1

о о

1

В соответствии с этим число разрядов распределителя 4 импульсовm 13.

Разрядность накопителя 2 равна 1о8г(9 + 7 + 7 + 1) 6. Количество мультиплексоров 3 равно четырем. Мультиплексор 3-1, соединенный входом с первым счетным входом накопителя 2, имеющим вес 2

1

1, соединен, входами с информацион- 25 ными (входными шинами) X.. X,, X

X

30

35

40

45

50

, v , л ,

устройства.

Мультиплексор 3-2, соединенный вы- ходом с вторым счетным входом накопителя 2, имеющим вес 2 , соединен входами с входными информационными шинами Х, Х4, X. устройства.

Мультиплексор 3-3, соединенный выходом с третьим счетным входов накопителя 2, имеющим вес 2, соединен входами с входными информационными шинами Х, Х, Ху, Xg устройства.

Мультиплексор 3-4, соединенный вь(- ходом с четвертым счетным входом накопителя 2, имеющим вес 2, соединен входами с входныют информационными шинами Xj и X, устройства.

Управляющие входы мультиплексоров 3 соединены каждый со своим выходом

распределителя 4 импульсов.

Накопитель 2 выполнен в виде 6 счетных триггеров, соединенных последовательно. Счетный вход i-ro триггера (i 2,3,4,5,6) соединен с выходом переноса (i-l)-ro триггера. Причем у второго-четвертого триггеров данное соединение осуществляется через элемент ИЖ, второй вход которого является счетным входом накопителя с весом 2

1-

Счетный вход первого

триггера является счетным входом накопителя с весом 2 1.

Комбинированный пороговый элемент 1 выполнен в соответствии с приведенным описанием. Так как двоичная запись порога а 18 имеет вид 010010, то он состоит из элемента ИЛИ, соединенного входами с выходами второго- четвертого разрядов накопителя 2, а выходом - с входом элемента И, второ вход которого соединён с выходом пятого разряда накопителя 2, а выход - с входом элемента ИЛИ, соединенного другим входом с выходом шестого раз- ряда накопителя 2.

Функционирование порогового устройства происходит следующим образом (фиг.1).

На выходах распределителя 4 им- пульсов последовательно, начиная с первого и до последнего, появляются разрешающие сигналы в течение длительности тактового импульса, поступающего на счетный вход распредели- теля с выхода генератора 7 тактовых импульсов.

При этом разрешающий сигнал с выходов распределителя 4 последовательно разрешает прохождение сигна- лов с входов 8 устройства через один из мультиплексоров 3 на счетные входы накопителя 2. Причем каждый из входо 8 устройства последовательно подключается к счетным входам накопит Г Ля 2 с весами 2 такими, что в двоичном представлении его веса W; в разрядах с весом 2 имеется единица. При поступлении на вход накопителя 2 с весо 2 единичного сигнала с входа 8 устройства, к содержимому накопителя 2

i прибавляется число 2 . Если 2 О; х-с

то в течение цикла из m тактов все входы 8 подключаются к входам нако- пителя 2 с соответствующими весами, причем на т-м такте в накопителе 2

ц

оказывается записано число 51 W; х;,

что приводит к сохранению нулевого сигнала на выходе элемента 1 в течение всего цикла работы. При появлении разрешающего (единичного) сигнал на т-м выходе распределителя 4 импулсов он одновременно поступает на второй вход формирователя 6 сброса, который при этом в течение длительности тактового импульса формирует на первом вьгходе сигнал разрешения записи, поступающий на вход разре- шения записи триггера 5, в который при этом записывается сигнал логического О с выхода комбинационного порогового элемента. По окончании

5 0

5 0

5 Q gg

5

тактового импульса сигнал появляется на втором выходе формирователя 6 сброса, и,, поступая на входы сброса накопителя 2 и распределителя 4 импульсов, устанавливает их в исходное состояние. Со следующего такта начинается новьй цикл работы. п

Если X ; г а, то на некотором

такте работы порогового элемента на выходе накопителя 2 появляется код числа большего или равного порогу а, что вызывает появление единичного потенциала на выходе комбинационного порогового элемента 1, поступающего на информационный вход триггера 5 и первый вход формирователя 6 сброса, на первом выходе которого при этом появляется сигнал, разрешающий запись в триггер 5 единичного сигнала с выхода комбинационного порогового элемента 1. По окончании тактового импульса единичньш сигнал на первом выходе пропадает и появляется на втором выходе формирователя 6 сброса и, поступая на входы накопителя 2 и распределителя 4 импульсов, устанавливает их в исходное состояние. Цикл работы устройства окончен. Со следующего такта начинается новьй цикл, работы порогового элемента.

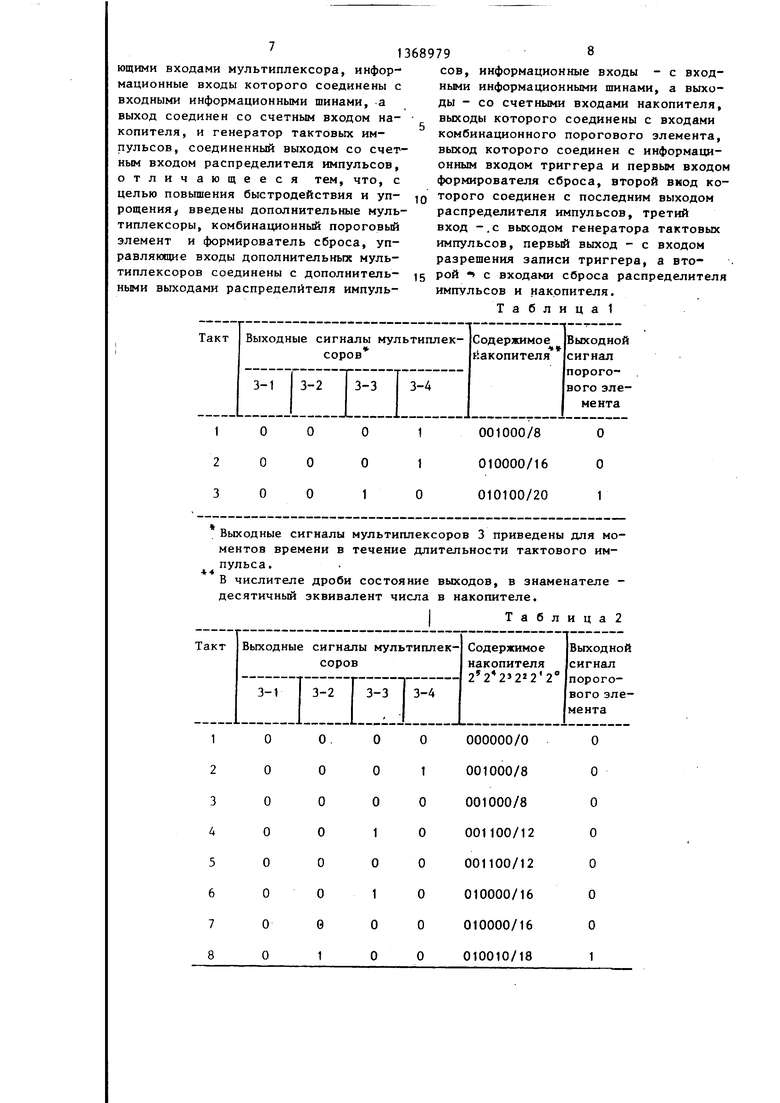

Пусть единичные сигналы поданы на входы X,, Xj, Xj. Выходные сигналы мультиплексоров 3 и содержимое накопителя 2 по тактам работы устройства представлено в табл. 1.

Таким образом, на третьем такте цикл работы устройства оканчивается. На выходе триггера 5 устанавливается единичный потенциал. Со следующего такта начинается новый цикл работы устройства.

Пусть единичным потенциалом поданы на входы Х, Хд, Хб, Х порогового элемента. При этом процесс функционирования устройства по тактам представлен в табл. 2.

Цикл работы порогового элемента

оканчивается на восьмом такте.

п Если ZIco;x; а, то цикл работы

устройства составляет 13 тактов.

Пороговое устройство обеспечивает повьш1ение быстродействия и упрощения.

Формула изобретения

Пороговое устройство, содержащее триггер, распределитель импульсов, выходы которого соединены с управля 1

ющими входами мультиплексора, инфор- мационные входы которого соединены с входными информационньми шинами, а выход соединен со счетным входом на- копителя, и генератор тактовых импульсов, соединенный выходом со счетным входом распределителя импульсов, отличающееся тем, что, с целью повьшения быстродействия и уп- рощения, введены дополнительные мультиплексоры, комбинационный пороговый элемент и формирователь сброса, управляющие входы дополнительных мультиплексоров соединены с дополнитель- ными выходами распределителя импуль

+ 4

Выходные сигналы мультиплексоров 3 приведены для моментов времени в течение длительности тактового импульса.

В числителе дроби состояние выходов, в знаменателе - десятичный эквивалент числа в накопителе.

I Таблица2

8

сов

, информационные входы - с входными информационными шинами, а выходы со счетными входами накопителя, выходы которого соединены с входами комбинационного порогового элемента, выход которого соединен с информационным входом триггера и первым входом формирователя сброса, второй вход которого соединен с последним выходом распределителя импульсов, третий вход -.с выходом генератора тактовых импульсов, первый выход - с входом разрешения записи триггера, а второй с входами сброса распределителя импульсов и накопителя. Т а б л и ц а 1

О О О О О О О

1

Авторы

Даты

1988-01-23—Публикация

1986-05-28—Подача