1.12

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения различных устройств обработки дискретной информации.

Целью изобретения является расширение функциональных возможностей, за счет работы с отрицательными весами, и повышение быстродействия.

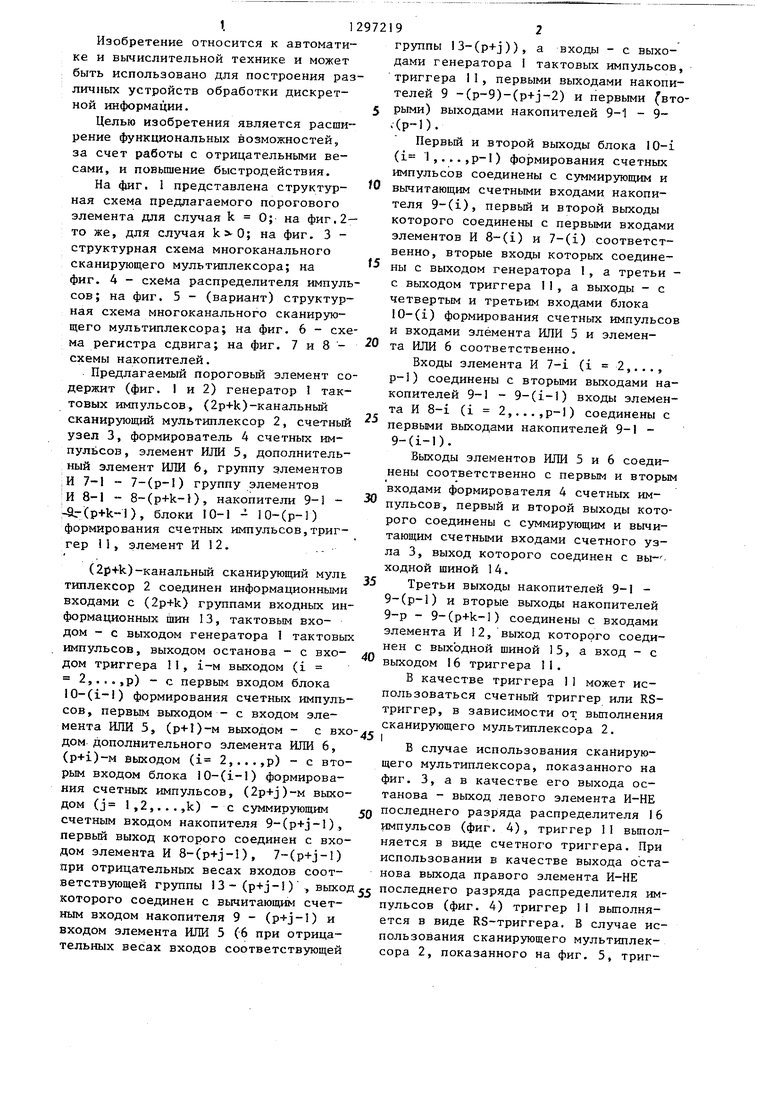

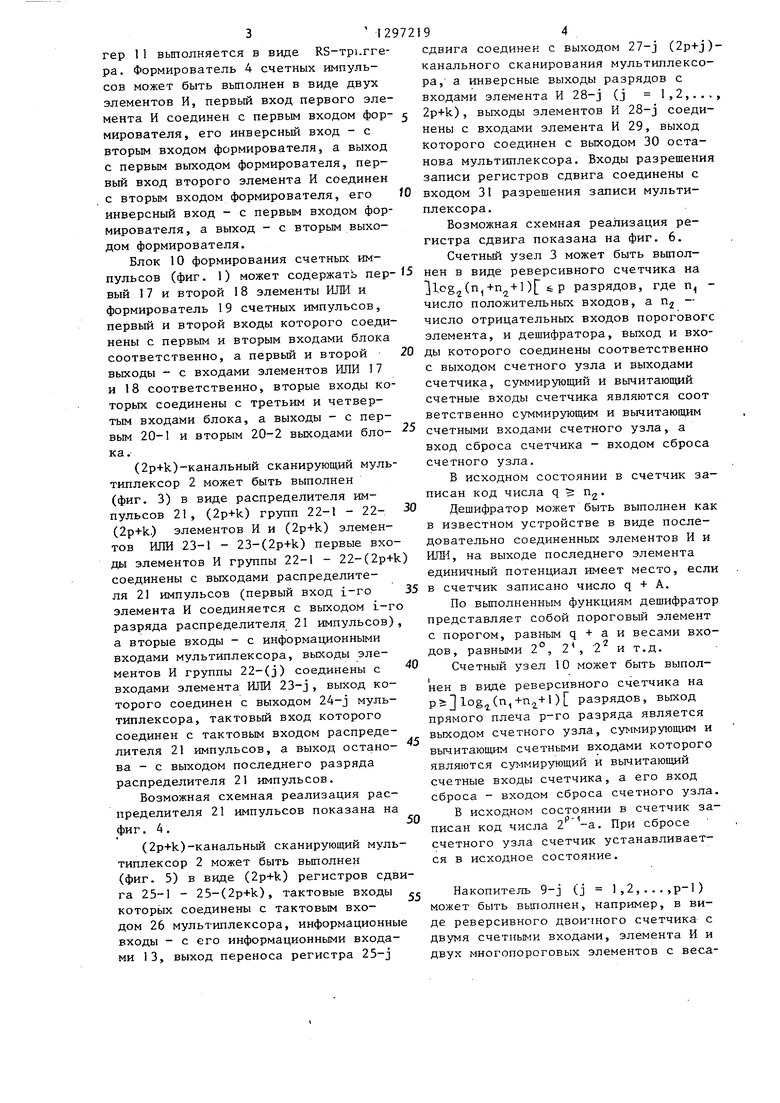

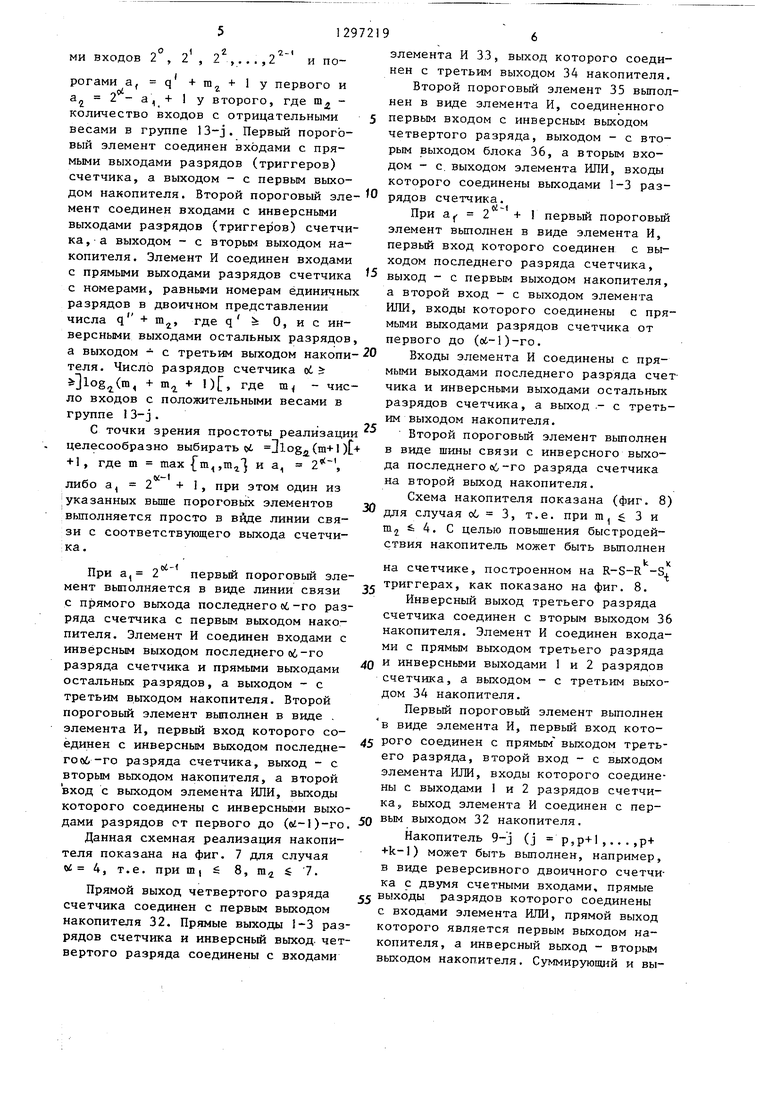

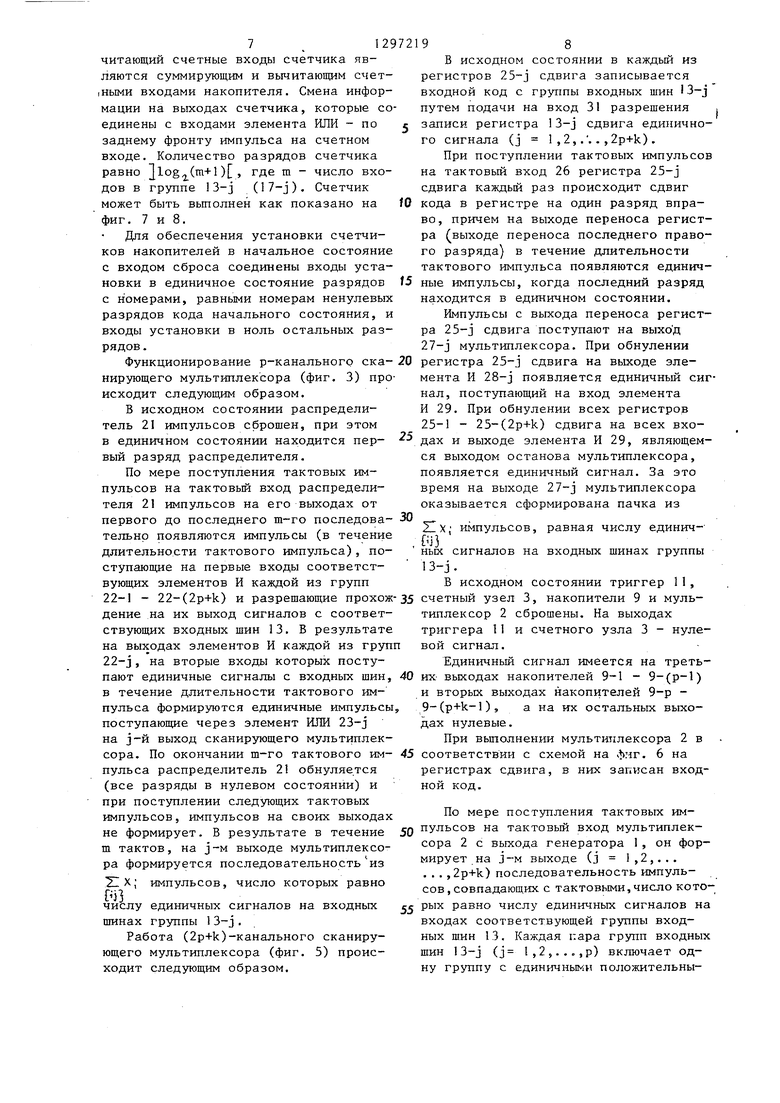

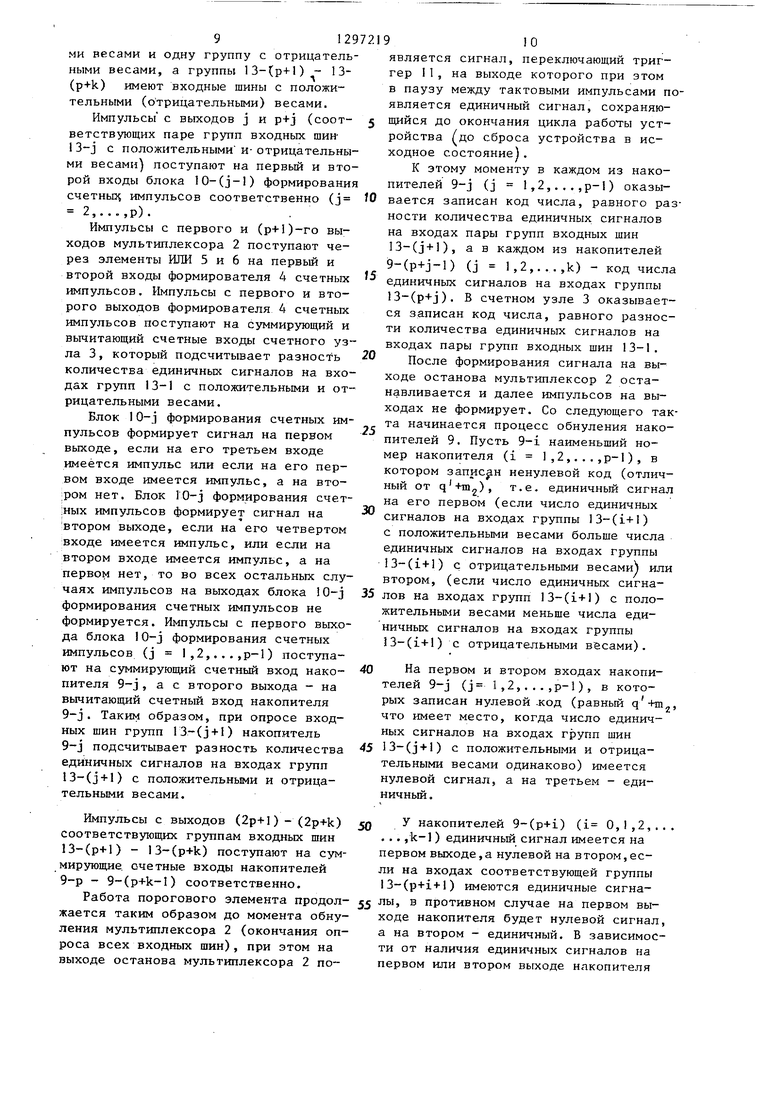

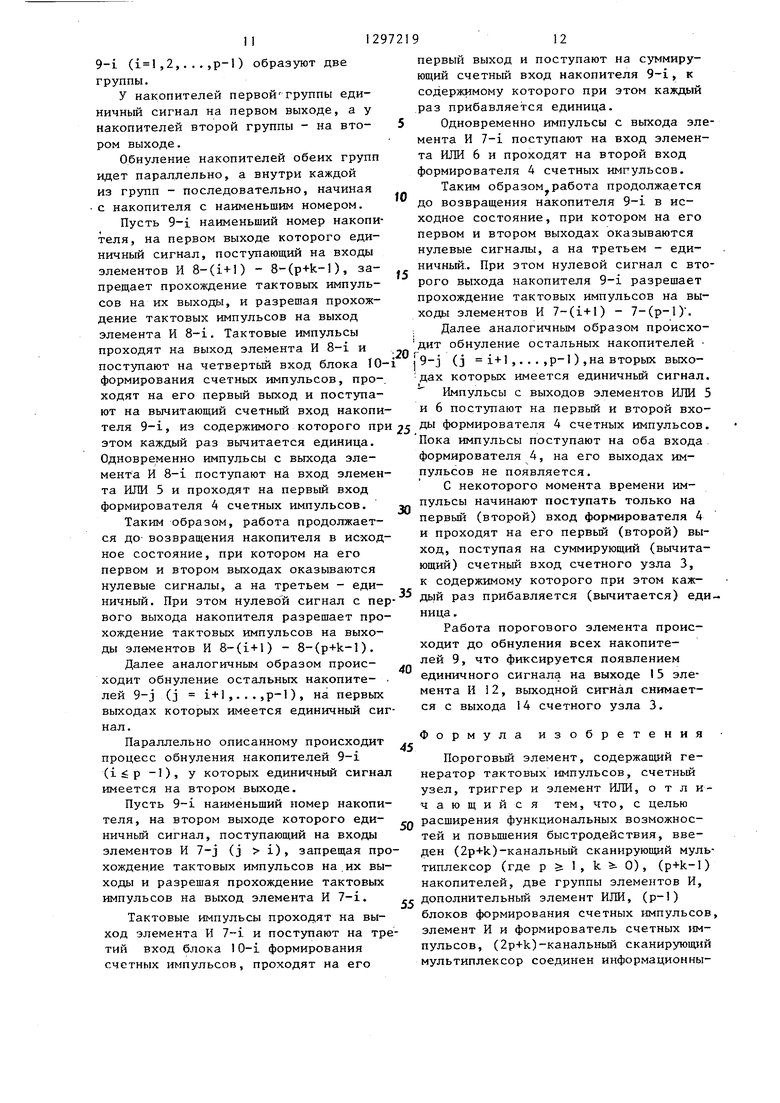

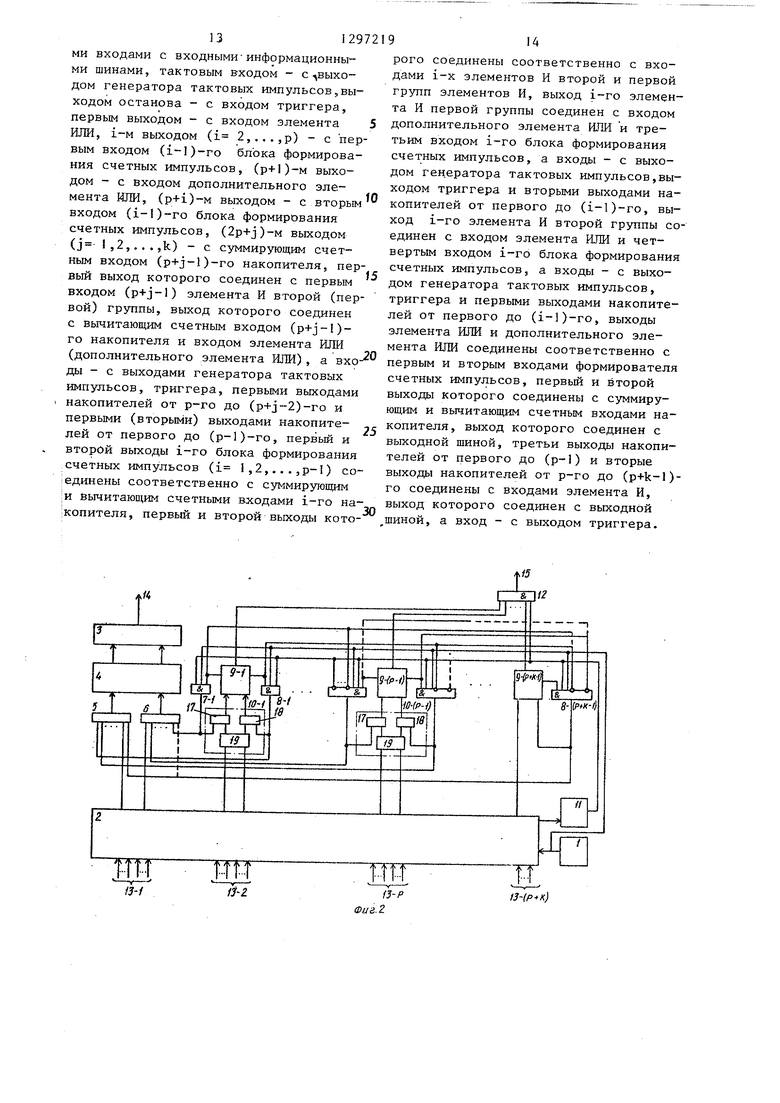

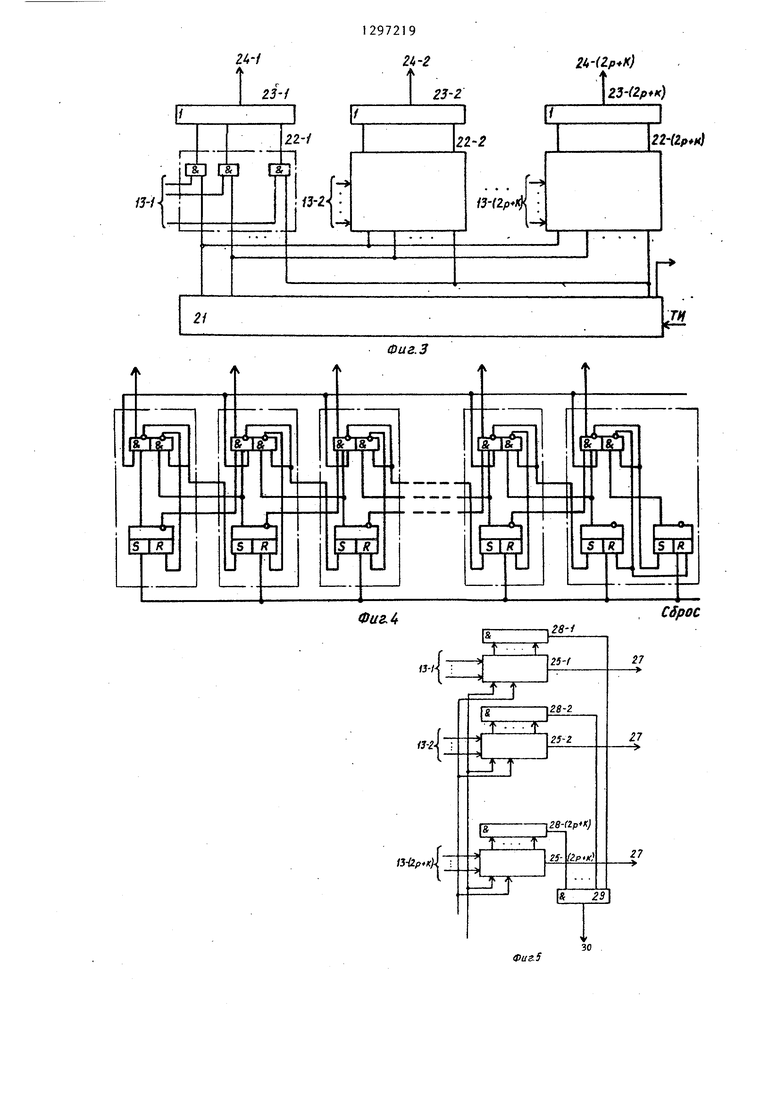

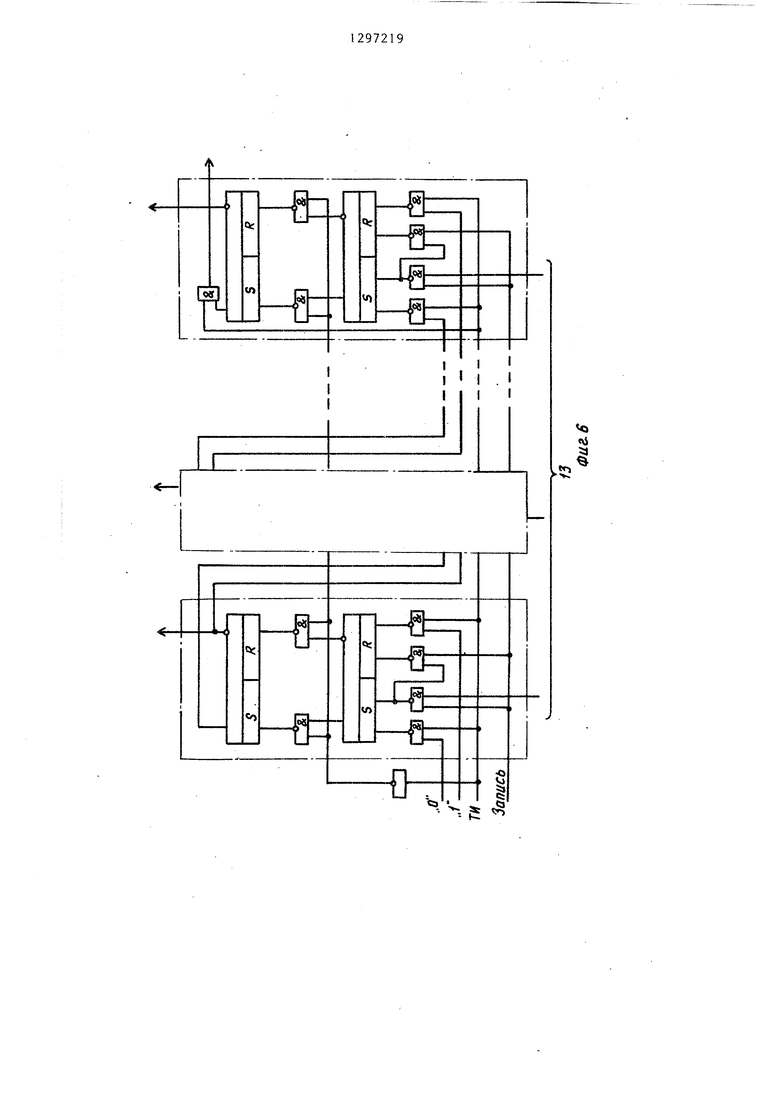

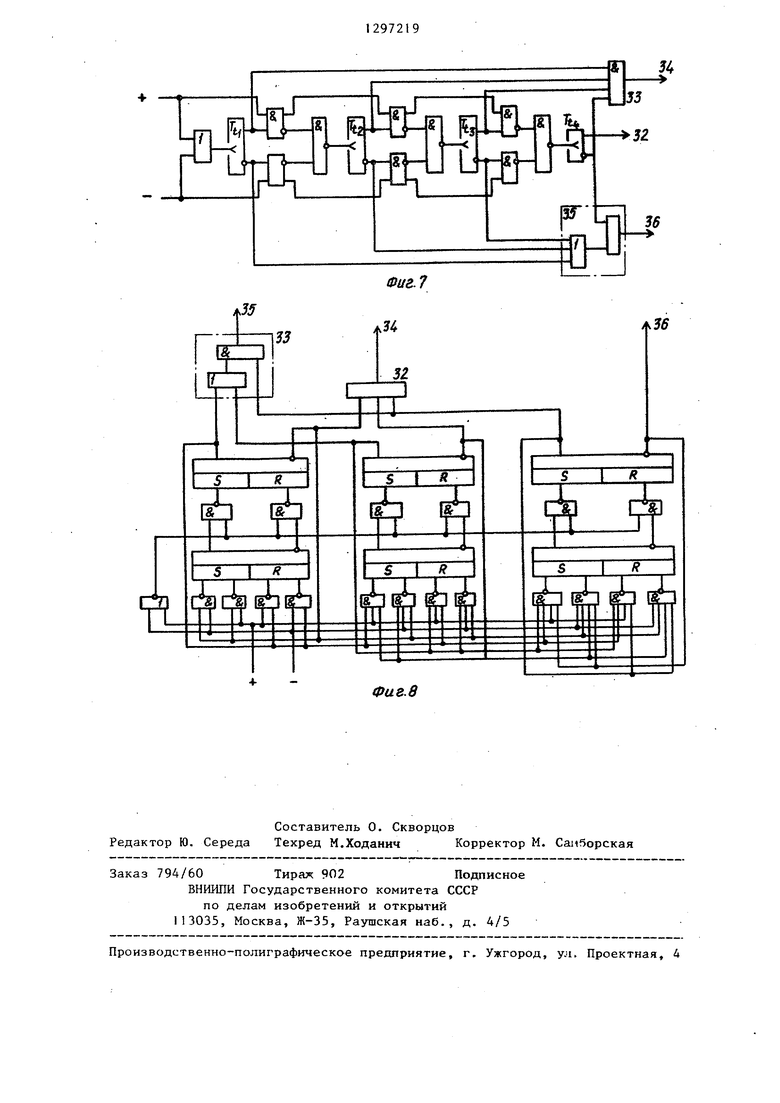

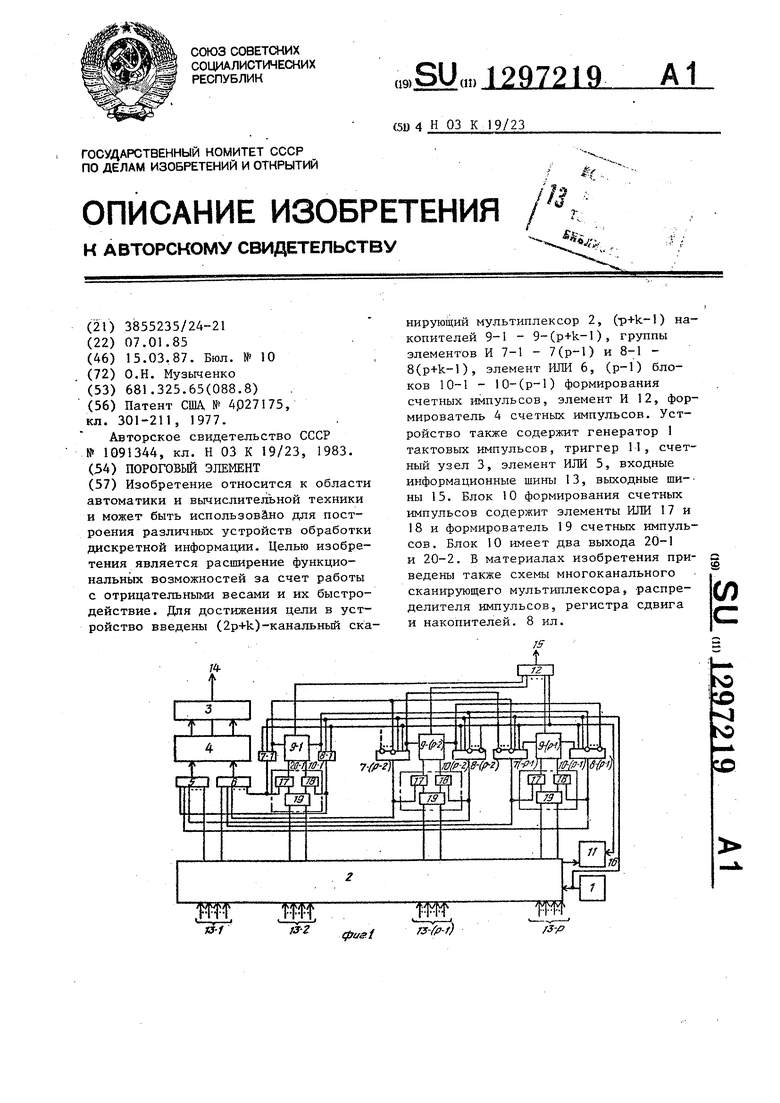

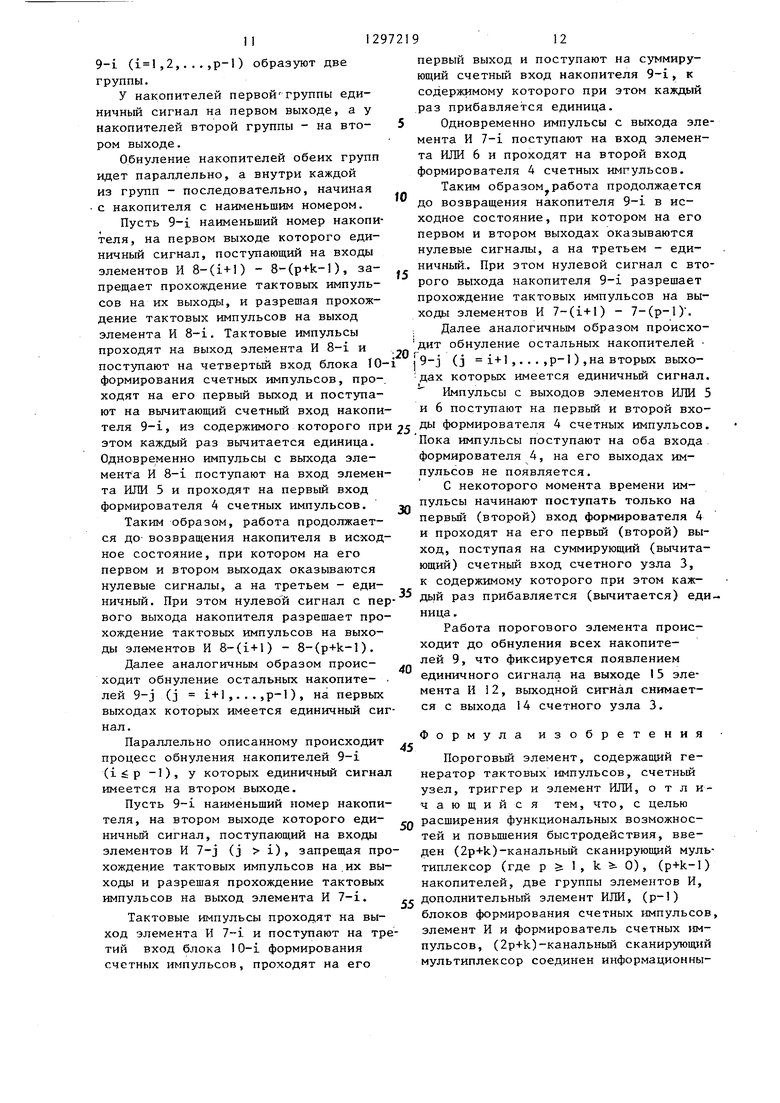

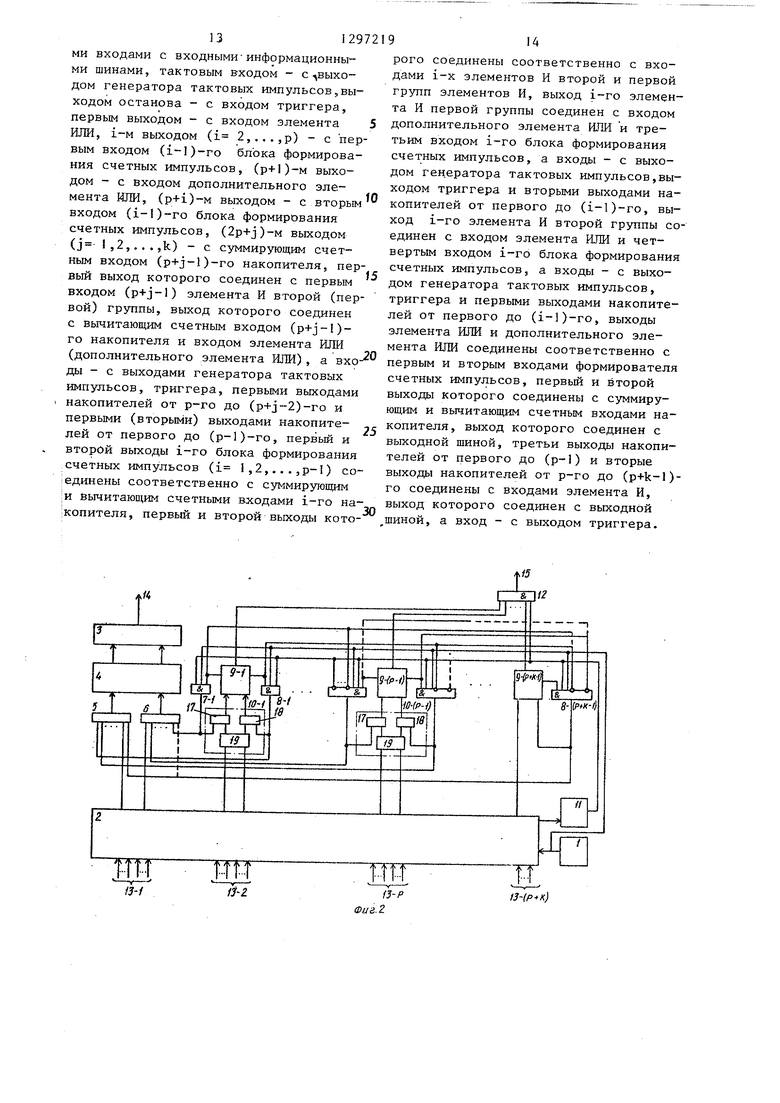

На фиг. I представлена структур- нал схема предлагаемого порогового элемента для случая k О; на фиг.2- то же, для случая на фиг. 3 - структурная схема многоканального сканирующего мультиплексора; на фиг. 4 - схема распределителя импульсов; на фиг. 5 - (вариант) структурная схема многоканального сканирующего мультиплексора; на фиг. 6 - схема регистра сдвига; на фиг. 7 и 8 - схемы накопителей.

Предлагаемый пороговьй элемент содержит (фиг. I и 2) генератор 1 тактовых импульсов, (2р+К)-канальный сканирующий мультиплексор 2, счетный узел 3, формирователь 4 счетных импульсов , элемент ИЛИ 5, дополнительный элемент ИЛИ 6, группу элементов ;И 7-1 - 7-(р-1) группу элементов И 8-1 8-(p+k-}), накопители 9-1 - (p+k-i), блоки 10-1 - lO-(p-l) формирования счетных импульсов,триггер П, элемент И 12. .,

(2p+k)-канальный сканирующий муль типлексор 2 соединен информационными входами с (2p+k) группами входных информационных йин 13, тактовым входом - с выходом генератора 1 тактовых импульсов, выходом останова - с вхо- дом триггера 11, i-м выходом (i 2,...,р) - с первым входом блока lO-(i-l) формирования счетных импульсов, первым выходом - с входом элемента ИЛИ 5, (р+1)-м выходом - с вхо дом дополнительного элемента ИЛИ 6, (p+i)-M выходом (i 2,...,р) - с вторым входом блока iO-(i-l) формирования счетных импульсов, (2p+j)-M выходом (j l,2,...,k) - с суммирующим счетным входом накопителя 9-(p+j-l), первый выход которого соединен с входом элемента И 8-(p+j-l), 7-(p+j-l) при отрицательных весах входов соответствующей группы 13- (p+j-1) , выхо которого соединен с вычитающим счетным входом накопителя 9 - (p+j-I) и входом элемента ИЛИ 5 (6 при отрицательных весах входов соответствующей

5

5

21

, Q з д е

92

группы 3-(p+j)), а входы - с выходами генератора I тактовых импульсов, триггера 1I, первыми выходами накопителей 9 -(p-9)-(p+j-2) и первыми (вторыми) выходами накопителей 9-1 - 9- .(р-1).

Первьш и второй выходы блока lO-i (i 1,...,р-1) формирования счетных импульсов соединены с суммирующим и вычитающим счетными входами накопителя 9-(i), первый и второй выходы которого соединены с первыми входами элементов И 8-(i) и 7-(i) соответственно, вторые входы которых соединены с выходом генератора 1, а третьи - с выходом триггера I1, а выходы - с четвертым и третьим входами блока lO-(i) формирования счетных импульсов и входами элемента ИЛИ 5 и элемента ИЛИ 6 соответственно.

Входы элемента И 7-i (i 2,..., p-i) соединены с вторыми выходами накопителей 9-1 - 9-(i-I) входы элемента И 8-1 (i 2,...,р-1) соединены с первьми выходами накопителей 9-1 - 9-(i-l).

Выходы элементов ИЛИ 5 и 6 соединены соответственно с первым и вторым входами формирователя 4 счетных импульсов, первый и второй выходы которого соединены с суммирующим и вычитающим счетными входами счетного узла 3, выход которого соединен с вы- ходной щиной 14.

Третьи выходы накопителей 9-1 - 9-(р-1) и вторые выходы накопителей 9-р - 9-(p+k-l) соединены с входами элемента И 12, выход которого соединен с выходной шиной 15, а вход - с выходом I6 триггера 1I.

В качестве триггера 11 может использоваться счетный триггер или RS- триггер, в зависимости от выполнения

сканирующего мультиплексора 2. I

В случае использования сканирующего мультиплексора, показанного на фиг. 3, а в качестве его выхода останова - выход левого элемента И-НЕ последнего разряда распределителя 16 импульсов (фиг. 4), триггер II выполняется в виде счетного триггера. При использовании в качестве выхода останова выхода правого элемента И-НЕ последнего разряда распределителя импульсов (фиг. 4) триггер i1 выполняется в виде RS-триггера. В случае использования сканирующего мультиплексора 2, показанного на фиг. 5, триг3 12972194

rep 11 вьшолняется в виде RS-трьгге- сдвига соединен с выходом 27-j (2p+j)канального сканирования мультиплексора, а инверсные выходы разрядов с

ра. Формирователь 4 счетных импульсов может быть выполнен в виде двух элементов И, первый вход первого эле- входами элемента И 28-j (j 1,2,..,, мента И соединен с первым входом фор- 5 2p+k), выходы элементов И 28-j соедимирователя, его инверсный вход - с вторым входом формирователя, а выход с первым выходом формирователя, первый вход второго элемента И соединен с вторым входом формирователя, его инверсный вход - с первым входом формирователя, а выход - с вторым выходом формирователя.

Блок 10 формирования счетных имнены с входами элемента И 29, выход которого соединен с выходом 30 останова мультиплексора. Входы разрешения записи регистров сдвига соединены с 10 входом 31 разрешения записи мультиплексора.

Возможная схемная реализация регистра сдвига показана на фиг. 6.

Счетный узел 3 может быть выпол- пульсов (фиг. 1) может содержать пер-15 нен в виде реверсивного счетчика на вый 17 и второй 18 элементы ИЛИ и l g i 2 f Р разрядов, где п - формирователь 19 счетных импульсов, число положительных входов, а п - первый и второй входы которого соеди- число отрицательных входов порогового нены с первым и вторым входами блока элемента, и дешифратора, выход и вхо- соответственно, а первый и второй 20 ды которого соединены соответственно выходы - с входами элементов ИЛИ 17 и 18 соответственно, вторые входы которых соединены с третьим и четвертым входами блока, а выходы - с первым 20-1 и вторым 20-2 выходами бло-

с выходом счетного узла и выходами счетчика, суммирующий и вычитающий счетные входы счетчика являются соот ветственно суммирующим и вычитающим счетными входами счетного узла, а

ка.

вход сброса счетчика - входом сброса счетного узла.

В исходном состоянии в счетчик записан код числа q

.1,

(2p+k)-канальный сканирующий мультиплексор 2 может быть выполнен (фиг. 3) в виде распределителя импульсов 21, (2p+k) групп 22-1 - 22- 0 Дешифратор может быть выполнен как (2p+k.) элементов И и (2p+k) элемен- в известном устройстве в виде после- тов ИЛИ 23-1 - 23-(2p+k) первые вхо- довательно соединенных элементов И и ды элементов И группы 22-1 - 22-(2p+k) ИЛИ, на выходе последнего элемента соединены с выходами распределите- единичный потенциал имеет место, если ля 21 импульсов (первый вход i-ro 35 в счетчик записано число q + А. элемента И соединяется с выходом i-ro разряда распределителя 21 импульсов), а вторые входы - с информационными входами мультиплексора, выходы элементов И группы 22-(j) соединены с входами элемента ИЛИ 23-j, выход которого соединен с выходом 24-j мультиплексора, тактовый вход которого соединен с тактовым входом распреде40

По выполненным функциям дещифратор представляет собой пороговый элемент с порогом, равным q + а и весами входов, равными 2°, 2,.д.

Счетный узел 10 может быть выполнен в виде реверсивного счетчика на

р5: 10g(n, ) разрядов, ВЫХОД

прямого плеча р-го разряда является выходом счетного узла, суммирующим и

50

лителя 21 импульсов, а выход остано- (5 зющим счетными входами которого ва - с выходом последнего разряда являются суммирующий и вычитающий распределителя 21 импульсов.счетные входы счетчика, а его вход

Возможная схемная реализация рас- сброса - входом сброса счетного узла пределителя 21 импульсов показана на фиг. 4.

(2p+k)-канальный сканирующий мультиплексор 2 может быть выполнен (фиг. 5) в виде (2p+k) регистров сдвига 25-1 - 25-(2p+k), тактовые входы которых соединены с тактовым входом 26 мультиплексора, информационные входы - с его информационными входами 13, выход переноса регистра 25-j

55

В исходном состоянии в счетчик записан код числа 2 -а. При сбросе счетного узла счетчик устанавливается в исходное состояние.

Накопитель 9-j (j ,2,...,р-1) может быть выполнен, например, в виде реверсивного двоичного счетчика с двумя счетными входами, элемента И и двух многопороговых элементов с весаСчетный узел 3 может быть выпол- нен в виде реверсивного счетчика на l g i 2 f Р разрядов, где п - число положительных входов, а п - число отрицательных входов порогового элемента, и дешифратора, выход и вхо- ды которого соединены соответственно

с выходом счетного узла и выходами счетчика, суммирующий и вычитающий счетные входы счетчика являются соот ветственно суммирующим и вычитающим счетными входами счетного узла, а

вход сброса счетчика - входом сброса счетного узла.

В исходном состоянии в счетчик за Дешифратор может быть выполнен как в известном устройстве в виде после- овательно соединенных элементов И и ИЛИ, на выходе последнего элемента единичный потенциал имеет место, если в счетчик записано число q + А.

писан код числа q

.1,

Дешифратор может быть в известном устройстве в довательно соединенных э ИЛИ, на выходе последнег единичный потенциал имее в счетчик записано число

Дешифратор может быть выполнен как в известном устройстве в виде после- довательно соединенных элементов И и ИЛИ, на выходе последнего элемента единичный потенциал имеет место, если в счетчик записано число q + А.

По выполненным функциям дещифратор представляет собой пороговый элемент с порогом, равным q + а и весами входов, равными 2°, 2,.д.

Счетный узел 10 может быть выпол Дешифратор может быть выполнен как в известном устройстве в виде после- довательно соединенных элементов И и ИЛИ, на выходе последнего элемента единичный потенциал имеет место, если в счетчик записано число q + А.

нен в виде реверсивного счетчика на

р5: 10g(n, ) разрядов, ВЫХОД

прямого плеча р-го разряда является выходом счетного узла, суммирующим и

(5 зющим счетными входами которого являются суммирующий и вычитающий счетные входы счетчика, а его вход

сброса - входом сброса счетного узла

В исходном состоянии в счетчик записан код числа 2 -а. При сбросе счетного узла счетчик устанавливается в исходное состояние.

Накопитель 9-j (j ,2,...,р-1) может быть выполнен, например, в виде реверсивного двоичного счетчика с двумя счетными входами, элемента И и двух многопороговых элементов с весами входов 2

2%.

,2

2-1

И порогами a

- о а. 2 -

.(

q + m, + 1 у первого и

а +

fO

f5

1 у второго, где т - количество входов с отрицательными весами в группе 13-j. Первый пороговый элемент соединен входами с прямыми выходами разрядов (триггеров) счетчика, а выходом - с первым выходом накопителя. Второй пороговый элемент соединен входами с инверсными выходами разрядов (триггеров) счетчика, а выходом - с вторым выходом накопителя . Элемент И соединен входами с прямыми выходами разрядов счетчика с номерами, равными номерам ёдиничньпс разрядов в двоичном представлении числа q + m,,, где q О, и с инверсными выходами остальных разрядов, а выходом - с третьим выходом накопи- 20 теля. Число разрядов счетчика ot i (m, + m,, + 1), где m - число входов с положительными весами в группе I3-J.

С точки зрения простоты реализации целесообразно выбирать oi л1о§д(т+1 ). . . и а,

2972196

элемента И 33, выход которого соединен с третьим выходом 34 накопителя.

Второй пороговый элемент 35 выполнен в виде элемента И, соединенного первым входом с инверсным выходом четвертого разряда, выходом - с вторым выходом блока 36, а вторым входом - с. выходом элемента ИЛИ, входы которого соединены выходами 1-3 разрядов

25

max

m ,го

+1, где m

либо а, 2 +1, при этом один из указанных вьше пороговых элементов вьшолняется просто в виде линии свя аи с соответствующего выхода счетчика.

При а, 2 первьй пороговый элемент выполняется в виде линии связи с прямого выхода последнего ci-го разряда счетчика с первьм выходом накопителя. Элемент И соединен входами с инверсным выходом последнего об-го разряда счетчика и прямыми выходами остальных разрядов, а выходом - с третьим выходом накопителя. Второй пороговый элемент выполнен в виде . элемента И, первый вход которого соединен с инверсным выходом последне- гооб-го разряда счетчика, выход - с вторым вьпсодом накопителя, а второй вход с выходом элемента ИЛИ, выходы которого соединены с инверсными выходами разрядов от первого до (ог-1)-го.

Данная схемная реализация накопителя показана на фиг. 7 для « 4, т.е. при Ш) 8, га2 S 7.

Прямой выход четвертого разряда счетчика соединен с первым выходом накопителя 32. Пряные выходы 1-3 разрядов счетчика и инверсный выход, четвертого разряда соединены с входами

30

счетчика.

При а,- 2 + первьй пороговый элемент выполнен в виде элемента И, первьй вход которого соединен с выходом последнего разряда счетчика, выход - с первым выходом накопителя, а второй вход - с выходом элемента ИЛИ, входы которого соединены с прямыми выходами разрядов счетчика от первого до (о.-1)-го.

Входы элемента И соединены с прямыми выходами последнего разряда счетчика и инверсными выходами остальных разрядов счетчика, а выход .- с третьим выходом накопителя.

Второй пороговый элемент выполнен в виде шины связи с инверсного выхода последнего об-го разряда счетчика на второй выход накопителя.

Схема накопителя показана (фиг. 8) для случая об 3, т.е. при т 3 и ffij fc 4. С целью повьшения быстродействия накопите-ль может быть вьшолнен

35

40

на счетчике, построенном на R-S-R -S триггерах, как показано на фиг. 8.

Инверсный выход третьего разряда счетчика соединен с вторым выходом 36 накопителя. Элемент И соединен входами с прямым выходом третьего разряда и инверсными выходами 1 и 2 разрядов счетчика, а вьссодом - с третьим выходом 34 накопителя.

Первьй пороговьй элемент выполнен в виде элемента И, первьй вход кото45 рого соединен с прямым выходом третьего разряда, второй вход - с вькодом элемента ИЛИ, входы которого соединены с выходами 1 и 2 разрядов счетчика выход элемента И соединен с пер5Q вым выходом 32 накопителя.

Накопитель 9-j (j р,р+1,...,р+ +k-l) может быть вьшолкен, например, в виде реверсивного двоичного счетчика с двумя счетными входами, прямые

выходы разрядов которого соединены с входами элемента ИЛИ, прямой выход которого является первым выходом накопителя, а инверсный выход - вторым выходом накопителя. Суммирующий и выO

5

0

Второй пороговый элемент 35 выполнен в виде элемента И, соединенного первым входом с инверсным выходом четвертого разряда, выходом - с вторым выходом блока 36, а вторым входом - с. выходом элемента ИЛИ, входы которого соединены выходами 1-3 разрядов

5

0

счетчика.

При а,- 2 + первьй пороговый элемент выполнен в виде элемента И, первьй вход которого соединен с выходом последнего разряда счетчика, выход - с первым выходом накопителя, а второй вход - с выходом элемента ИЛИ, входы которого соединены с прямыми выходами разрядов счетчика от первого до (о.-1)-го.

Входы элемента И соединены с прямыми выходами последнего разряда счетчика и инверсными выходами остальных разрядов счетчика, а выход .- с третьим выходом накопителя.

Второй пороговый элемент выполнен в виде шины связи с инверсного выхода последнего об-го разряда счетчика на второй выход накопителя.

Схема накопителя показана (фиг. 8) для случая об 3, т.е. при т 3 и ffij fc 4. С целью повьшения быстродействия накопите-ль может быть вьшолнен

35

40

на счетчике, построенном на R-S-R -S триггерах, как показано на фиг. 8.

Инверсный выход третьего разряда счетчика соединен с вторым выходом 36 накопителя. Элемент И соединен входами с прямым выходом третьего разряда и инверсными выходами 1 и 2 разрядов счетчика, а вьссодом - с третьим выходом 34 накопителя.

Первьй пороговьй элемент выполнен в виде элемента И, первьй вход кото45 рого соединен с прямым выходом третьего разряда, второй вход - с вькодом элемента ИЛИ, входы которого соединены с выходами 1 и 2 разрядов счетчика выход элемента И соединен с пер5Q вым выходом 32 накопителя.

Накопитель 9-j (j р,р+1,...,р+ +k-l) может быть вьшолкен, например, в виде реверсивного двоичного счетчика с двумя счетными входами, прямые

выходы разрядов которого соединены с входами элемента ИЛИ, прямой выход которого является первым выходом накопителя, а инверсный выход - вторым выходом накопителя. Суммирующий и вы7 12972198

читающий счетные входы счетчика яв- в исходном состоянии в каждый из ляются суммирующим и вычитающим счет-регистров 25-j сдвига записывается |Ными входами накопителя. Смена инфор-входной код с группы входных шин 13-j мации на выходах счетчика, которые со-путем подачи на вход 31 разрешения , единены с входами элемента ИЛИ - по «записи регистра 13-j сдвига единично- заднему фронту импульса на счетномго сигнала (j 1 ,2,... ,,2p+k). входе. Количество разрядов счетчика При поступлении тактовых импульсов равно ) , где m - число вхо-на тактовый вход 26 регистра 25-j дов в группе 13-j (17-j). Счетчиксдвига каждый раз происходит сдвиг может быть вьшолнен как показано на 10кода в регистре на один разряд впра- фиг, 7 и 8.во, причем на выходе переноса регистДля обеспечения установки счетчи-ра (выходе переноса последнего право- ков накопителей в начальное состояниего разряда) в течение длительности с входом сброса соединены входы уста-тактового импульса появляются единич- новки в единичное состояние разрядов 15ные импульсы, когда последний разряд с номерами, равными номерам ненулевыхнаходится в единичном состоянии, разрядов кода начального состояния, и Импульсы с выхода переноса регист- входы установки в ноль остальных раз-ра 25-j сдвига поступают на выход рядов.27-J мультиплексора. При обнулении

Функционирование р-канального ска- 20регистра 25-j сдвига на выходе эленирующего мультиплексора (фиг. 3) про-мента И 28-j появляется единичный сигисходит следующим образом. нал, поступающий на вход элемента

В исходном состоянии распредели-И 29. При обнулении всех регистров

тель 21 импульсов сброшен, при этом25-1 - 25-(2p+k) сдвига на всех вхов единичном состоянии находится пер- и выходе элемента И 29, являющемвый разряд распределителя.ся выходом останова мультиплексора,

По мере поступления тактовых им-появляется единичный сигнал. За это

пульсов на тактовый вход распредели-время на выходе 27-j мультиплексора

теля 21 импульсов на его выходах отоказь вается сформирована пачка из

первого до последнего т-го последова- 30 , ,

, , импульсов, равная числу единич- тельнр появляются импульсы (в течение

длительности тактового импульса), по- ных сигналов на входных шинах группы

ступающие на первые входы соответст- 1 3-j .

вующих элементов И каждой из групп В исходном состоянии триггер 11,

22-1 - 22-(2p-bk) и разрешающие прохож-35 счетный узел 3, накопители 9 и мульдение на их выход сигналов с соответ- типлексор 2 сброшены. На выходах

ствующих входных шин 13. В результате триггера 11 и счетного узла 3 - нулена выходах элементов И каждой из групп вой сигнал.

22-J, на вторые входы которых посту- Единичный сигнал имеется на третьпают единичные сигналы с входных шин, 40 их выходах накопителей 9-1 - 9-(р-1)

в течение длительности тактового им- и вторых выходах накопителей 9-р пульса формируются единичные импульсы, 9-(p+k-i)5 а на их остальных выхопоступающие через элемент ИЛИ 23-j дах нулевые.

на j-й выход сканирующего мультиплек- При выполнении мультиплексора 2 в

сора. По окончании т-го тактового им- 45 соответствии с схемой на фиг. 6 на

пульса распределитель 21 обнуляется регистрах сдвига, в них вход(все разряды в нулевом состоянии) и ной код.

при поступлении следующих тактовых

импульсов, импульсов на своих выходах о мере поступления тактовых имне формирует. В результате в течение 50 на тактовый вход мультиплекm тактов, на j-м выходе мультиплексо- ора 2 с вьпсода генератора I, он форра формируется последовательность из мирует.на J-M выходе (j 1,2,...

... ,2p+k) последовательность импуль- импульсов, число которых равно сов,совпадающих с тактовыми,число коточислу единичных сигналов на входных рых равно числу единичных сигналов на шинах группы 13-j.входах соответствующей группы входРабота (2p-bk)-канального сканиру- ных шин 13. Каждая пара групп входных ющего мультиплексора (фиг. 5) проис- шин 13-j (j 1,2,..с,р) включает од- ходит следующим образом.ну группу с единичными положительны9129

ми весами и одну группу с отрицательными весами, а группы 13-(р+1) - 13- (p+k) имеют входные шины с положительными (отрицательными) весами.

Импульсы с выходов j и P+J (COOT- ветствующих паре групп входных шин- 13-J с положительными и- отрицательными весами) поступают на первый и второй входы блока lO-(j-l) формирования счетньщ импульсов соответственно (j 2,,..,р).

Импульсы с первого и (р+1)-го выходов мультиплексора 2 поступают через элементы ИЛИ 5 и 6 на первый и второй входы формирователя 4 счетных импульсов. Импульсы с первого и второго выходов формирователя 4 счетных импульсов поступают на суммирующий и вычитающий счетные входы счетного узла 3, который подсчитывает разность количества единичных сигналов на входах групп 13-1 с положительными и отрицательными весами.

Блок I0-J формирования счетных импульсов формирует сигнал на первом выходе, если на его третьем входе имеется импульс или если на его первом входе имеется импульс, а на втором нет. Блок ro-j формирования счет- ;ных импульсов формирует сигнал на втором выходе, если на его четвертом входе имеется импульс, или если на втором входе имеется импульс, а на первом нет, то во всех остальных случаях импульсов на выходах блока 10-j формирования счетных импульсов не формируется. Импульсы с первого выхода блока 10-J формирования счетных импульсов (J 1,2,..,,р-1) постзша- ют на суммирующий счетный вход нако- пителя 9-J, а с второго выхода - на вычитающий счетный вход накопителя 9-J. Таким образом, при опросе входных шин групп ГЗ-(3+1) накопитель 9-J подсчитывает разность количества единичных сигналов на входах групп 13-(j+l) с положительными и отрицательными весами.

Импульсы с выходов (2р+1) - (2p+k) соответствующих группам входных шин 13-(р+1) - 13-(p+k) поступают на суммирующие, счетные входы накопителей 9-р - 9-(p+k-l) соответственно.

Работа порогового элемента продолжается таким образом до момента обнуления мультиплексора 2 (окончания опроса всех входных шин), при этом на выходе останова мультиплексора 2 по

10

является сигнал, переключающий триггер II, на выходе которого при этом в паузу между тактовыми импульсами появляется единичный сигнал, сохраняю- до окончания цикла работы устройства до сброса устройства в исходное состояние).

К этому моменту в каждом из накопителей 9-J (j 1,2,...,р-1) оказывается записан код числа, равного разности количества единичных сигналов на входах пары групп входных шин I3-(j+i), а в каждом из накопителей 9-(p+j-l) (j 1,2,...,k) - код числа единичных сигналов на входах группы 13-(p+j). В счетном узле 3 оказывается записан код числа, равного разности количества единичных сигналов на входах пары групп входных шин 13-1.

После формирования сигнала на выходе останова мультиплексор 2 останавливается и далее импульсов на выходах не формирует. Со следующего такта начинается процесс обнуления накопителей 9. Пусть 9-i наименьший номер накопителя (i ,2,...,р-1), в котором записан ненулевой код (отличный от q +mg), т.е. единичный сигнал на его первом (если число единичных сигналов на входах группы 13-(1+1) с положительньпчи весами больше числа единичных сигналов на входах группы 13-(i+l) с отрицательными весами или втором, (если число единичных сигналов на входах групп 13-(i+l) с положительными весами меньше числа единичных сигналов на входах группы 13-(i+l) с отрицательными весами).

На первом и втором входах накопителей 9-j (j 1 ,2,...,р-1), в которых записан нулевой-код (равный , что имеет место, когда число единичных сигналов на входах групп шин 13-(j+l) с положительными и отрицательными весами одинаково) имеется нулевой сигнал, а на третьем - единичный ,

yj У накопителей 9-(p+i) (i 0,1,2,.. . .. ,k-l ) единичный сигнал имеется на первом выходе, а нулевой на в тором, если на входах соответствующей группы I3-(p+i+l) имеются единичные сигна55 лы, в противном случае на первом выходе накопителя будет нулевой сигнал, а на втором - единичный. В зависимости от наличия единичных сигналов на первом или втором выходе накопителя

11129721912

9-i (,2,..,,p-l) образуют двепервый выход и поступают на суммиругруппы.ющий счетный вход накопителя 9-i, к

У накопителей первой группы еди-содержимому которого при этом каждый

ничный сигнал на первом выходе, а ураз прибавляется единица, накопителей второй группы - на вто- 5 Одновременно импульсы с выхода элером выходе. мента И 7-i поступают на вход элеменОбнуление накопителей обеих группта ИЛИ 6 и проходят на второй вход

идет параллельно, а внутри каждойформирователя 4 счетных импульсов. из групп - последовательно, начиная Таким образом работа продолжается

с накопителя с наименьшим номером.ДО возвращения накопителя 9-i в исПусть 9-i наименьший номер накопи-ходное состояние, при котором на его

теля, на первом выходе которого еди-первом и втором выходах оказываются

ничный сигнал, поступающий на входынулевые сигналы, а на третьем - едиэлементов И 8-(i+l) - 8-(p+k-l), за- ничный.. При этом нулевой сигнал с втопрещает прохождение тактовых импуль-Рого выхода накопителя 9-i разрешает

сов на их выхода, и разрешая прохож-прохождение тактовых импульсов на выдение тактовых импульсов на выходходы элементов И 7-(i+l) - 7-(р-1) элемента И 8-i. Тактовые импульсы ; Далее аналогичным образом происхо- проходят на выход элемента И 8-1 и обнуление остальных накопителей

поступают на четвертьш вход блока lO-i| J J i+l ,.., ,р-1),на вторых выхоформирования счетных импульсов, про-. дах которых имеется единичный сигнал,

ходят на его первый выход и поступа- Импульсы с выходов элементов ИЛИ 5

ют на вычитающий счетный вход накопи-и 6 поступают на первый и второй вхотеля 9-i, из содержимого которого при формирователя 4 счетных импульсов,

этом каждый раз вычитается единица.Пока импульсы поступают на оба входа

Одновременно импульсы с выхода эле-формирователя 4, на его выходах иммента И 8-i поступают на вход элемен-пульсов не появляется, та ИЛИ 5 и проходят на первый вход С некоторого момента времени имформирователя 4 счетных импульсов. начинают поступать только на

Таким образом, работа продолжает-первый (второй) вход формирователя 4

ся до возвращения накопителя в исход-« проходят на его первый (второй) выное состояние, при котором на поступая на суммирующий (вычитапервом и втором выходах оказываютсяющий) счетньш вход счетного узла 3,

нулевые сигналы, а на третьем - еди-« содержимому которого при этом кажничный. При этом нулево й сигнал с пер-Дь™ раз прибавляется (вычитается) едивого выхода накопителя разрешает про-ница.

хождение тактовых импульсов на выхо- Работа порогового элемента происды элементов И 8-(i-t-l) - 8-(p+k-l).ходит до обнуления всех накопитеДалее аналогичным образом проис- длей 9, что фиксируется появлением

ходит обнуление остальных накопите- единичного сигнала на выходе 15 элелей 9-J (J i+l,...,р-1), на первыхмента И 12, выходной сигнал снимаетвыходах которых имеется единичный сиг- выхода 14 счетного узла 3. нал.

Параллельно описанному происходит Формула изобретения процесс обнуления накопителей 9-i Пороговьй элемент, содержащий ге(i р -1), у которых единичный сигналнератор тактовыхИмпульсов, счетный

имеется на втором выходе.узел, триггер н элемент ИЛИ, о т л иПусть 9-i наименьший номер накопи-чающийся тем, что, с целью

теля, на втором выходе которого еди- расширения функциональных возможносничный сигнал, поступающий на входытей и повышения быстродействия, ввеэлементов И 7-j (j i), запрещая про-ден (2р+и)-канальный сканирующий мульхожден.ие тактовых импульсов на.их вы-типлексор (где р 5: 1 , k 5 0), (p+k-1)

ходы и разрешая прохождение тактовыхнакопителей, две группы элементов И,

импульсов на выход элемента И 7-i. дополнительный элемент ИЛИ, (р-1)

Тактовые импульсы проходят на вы-блоков формирования счетных импульсов,

ход элемента И 7-i и поступают на тре-элемент И и формирователь счетных имтий вход блока I0-i формированияпульсов, (2p+k)-кaнaльньri сканирующий

счетных импульсов, проходят на егомультиплексор соединен информационны1312972

ми входами с входными-информационными шинами, тактовым входом - с .выходом генератора тактовых импульсов ..выходом останова - с входом триггера, первым выходом - с входом элемента 5 ИЛИ, i-M выходом (i 2,,..,р) - с первым входом (i-I)-ro блока формирования счетных импульсов, (р+1)-м выходом - с входом дополнительного элемента ИЛИ, (p+i)-M выходом - с BTOpbiM входом (i-I)-ro блока формирования счетных импульсов, (2p+j)-M выходом (,2,,,.,k) - с суммирующим счетным входом (p+j-l)-ro накопителя, пер- вый выход которого соединен с первым входом (p+j-1) элемента И второй (первой) группы, выход которого соединен с вычитающим счетным входом (p+j-1)- го накопителя и входом элемента ИЛИ (дополнительного элемента ИЛИ), а вхо- ды - с выходами генератора тактовых импульсов, триггера, первыми выходами накопителей от р-го до (p+j--2)-ro и первыми (вторыми) выходами накопителей от первого до (p-l)-ro, первый и второй выходы i-ro блока формирования счетных импульсов (i 1,2,...,р-1) со- 1 единены соответственно с суммирующим

15

25

::И вычитающим счетными входами 1-го на копителя, первый и второй выходы кото

5

5

0

914

рого соединены соответственно с входами i-x элементов И второй и первой групп элементов И, выход i-ro элемента И первой группы соединен с входом дополнительного элемента ИЛИ и третьим входом i-ro блока формирования счетных импульсов, а входы - с выходом генератора тактовых импульсов,выходом триггера и вторыми выходами накопителей от первого до (i-l)-ro, выход 1-го элемента И второй группы соединен с входом элемента ИЛИ и четвертым входом i-ro блока формирования счетных импульсов, а входы - с выходом генератора тактовых импульсов, триггера и первыми выходами накопителей от первого до (i-l)-ro, выходы элемента ИЛИ и дополнительного элемента ИЛИ соединены соответственно с первым и вторым входами формирователя счетных импульсов, первый и второй выходы которого соединены с суммирующим и вычитающим счетным входами накопителя, выход которого соединен с выходной шиной, третьи выходы накопителей от первого до (р-1) и вторые выходы накопителей от р-го до (p+k-1)- го соединены с входами элемента И, выход которого соедршен с вькодной ,шиной, а вход - с выходом триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый элемент | 1985 |

|

SU1297220A1 |

| Пороговое устройство (его варианты) | 1984 |

|

SU1352449A1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ | 1987 |

|

RU2034401C1 |

| Пороговый элемент | 1983 |

|

SU1126924A1 |

| Пороговый элемент | 1987 |

|

SU1584098A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587642A1 |

| Пороговый элемент | 1986 |

|

SU1387185A2 |

| Пороговый элемент | 1986 |

|

SU1387191A1 |

| Пороговый элемент | 1987 |

|

SU1647871A1 |

| Пороговый элемент | 1984 |

|

SU1261100A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использов&но для построения различных устройств обработки дискретной информации. Целью изобретения является расширение функцио- нальньпс возможностей за счет работы с отрицательными весами и их быстродействие. Для достижения цели в устройство введены (2p+k)-канальный сканирующий мультиплексор 2, (p+k-1) накопителей 9-1 - 9-(p+k-l), группы элементов И 7-1 - 7(р-1) и 8-1 - 8(p+k-l), элемент ИЛИ 6, (р-1) блоков 10-1 - 10-(р-1) формирования счетных импульсов, элемент И 12, формирователь 4 счетных импульсов. Устройство также содержит генератор 1 тактовых импульсов, триггер 11, счетный узел 3, элемент ИЛИ 5, входные информационные шины 13, вькодные ши- ны 15. Блок 10 формирования счетных импульсов содержит элементы ИЛИ 17 и 18 и формирователь 19 счетных импульсов. Блок 10 имеет два выхода 20-1 и 20-2. В материалах изобретения приведены также схемы многоканального сканирзтощего мультиплексора, распределителя импульсов, регистра сдвига и накопителей. 8 ил. (О (Л № «Гг efjust

f3-P

3-(р- К)

24-/

I г/-/

Z2-i Ш dj

ff

u-i

21

Фиг.З

1

гз-г

2n.-()

гз-(

zi-z

ZZ-lZp H

13-(2р

TH

ire.

Lnni,,

L.r L.

&

ииТш

ST

IJU

Фиг. 4

Сброс

28-i

13-izp K

1 1 I I I .1 I I I

.-

o

fc

«o

pe

{}

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Прибор для исправления снимков рельефа местности | 1921 |

|

SU301A1 |

| Пороговый элемент | 1982 |

|

SU1091344A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-03-15—Публикация

1985-01-07—Подача