со

00

ю

о ю

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок | 1984 |

|

SU1287296A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Декодер мажоритарного двоичного кода | 1988 |

|

SU1566488A1 |

| Устройство для исправления пакетных ошибок модульными кодами | 1988 |

|

SU1596465A1 |

| Устройство декодирования с исправлением ошибок | 1985 |

|

SU1293855A1 |

| Устройство коррекции двойных ошибок с использованием кода Рида-Соломона | 1988 |

|

SU1662010A1 |

| Устройство декодирования линейногоциКличЕСКОгО КОдА | 1979 |

|

SU809568A1 |

| ДЕКОДЕР С ИСПРАВЛЕНИЕМ ОШИБОК | 1993 |

|

RU2054224C1 |

| Устройство для декодирования итеративного кода | 1988 |

|

SU1547080A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

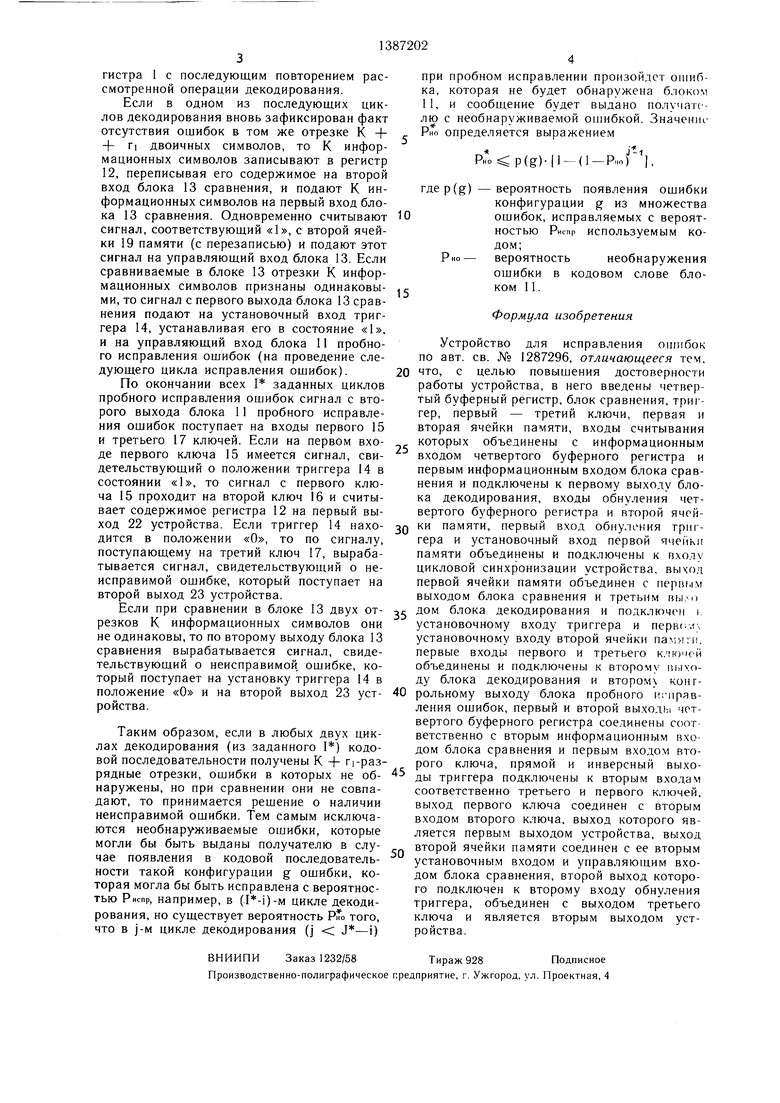

Изобретение относится к вычислительной технике и является усовершенствованием устройства по авторскому свидетельству № 1287296. Его использование в системах передачи информации позволяет повысить достоверность работы устройства. Устройство для исправления ошибок содержит приемный и буферные регистры 1 и 5-7, блок 2 суммирования, блок 3 деления, блок 4 декодирования, генераторы 8 и 9 псевдослучайной последовательности и блок 11 пробного исправления ошибок. Благодаря введению буферного регистра 12, блока 13 сравнения, триггера 14, ключей 15-17 и ячеек 18 и 19 памяти обеспечивается обнаружение тех ошибок, которые, являясь исправимыми в одном из циклов пробного исправления, могли быть замаскированы случайной ошибкой в каком-либо предшествующем цикле так, что в нужном цикле принятая ошибка (исправимая в принципе) не будет обнаружена. 1 ил. S (Л

No

Изобретспио относится к вычислительной технике, может быть использовано в системах передачи цифровой информации и является усовершенствованием устройства по авт. св. № 1287296.

Цель изобретения - повышение достоверности работы устройства.

На чертеже приведена блок-схема устройства для исправления ошибок.

Устройство для исправления ошибок сов первый буферный регистр 5, а ni k + Г| ее символов, подвергнутых на передающем конце псевдостохастическому преобразованию, записывают в приемный регистр 1.

По сигналу цикловой синхронизации с входа 21, соответствующему началу проведения заданного числа I циклов декодирования кодовой последовательности, устанавливают в положение «О регистр 12, преддержит приемный регистр 1, блок 2 сумми- 10 назначенный для промежуточного хранения, рования, блок 3 деления, блок 4 декодиро- и триггер 14, записывают «1 в первую ячей- вания, первый - третий буферные регист- ку 18 памяти и «О во вторую ячейку 19 пары 5-7, первый 8 и второй 9 генера- мяти, устанавливают в исходное состояние торы псевдслучайной последовательности коммутатор 10 и блок И пробного исправ- (ПСП), коммутатор 10, блок 11 пробного ления ошибок, формируют в первом 8 и во исправления ошибок, четвертый буферный втором 9 генераторах псевдослучайной посла- регистр 12, блок 13 сравнения, триггер 14, довательности очередные значения двух от- первый - третий ключи 15-17, первую 18 и резков псевдослучайных последовательнос- вторую 19 ячейки памяти. На чертеже обоз- тей длины ni К + TI двоичных симво- начены информационный вход 20, вход 21лов каждый, которые через коммутатор 10

цикловой синхронизации, первый 22 и вто- 20 заносятся и запоминаются в буферных ре- рой 23 выходы.гистрах 6 и 7.

Входы обнуления триггера 14 и уста-По завершению приема п-разрядной коновочные входы ячейки 19 объединены по довой последовательности с приемного регист- схеме ИЛИ. Вход обнуления ячейки 19 мо- ра 1 считывают преобразованный на пере- жет быть объединен с ее входом считы- даче отрезок кодовой последовательности вания. Регистр 12 имеет импульсный (пер- 25 длины П| К -4- Г| в блок 2 сумми- вый) и потенциальный (второй) выходы. рования, где складывают его по модулю два Устройство для исправления ошибок ра- с первым (П|)-разрядным отрезком псевдо- ботает следующим образом.случайной последовательности, находящимПусть п-разрядная кодовая последова- ся в регистре б, а затем делят по моду- тельность была сформирована на передаче лю неприводимого полинома степени П) ре- следующим образом. К К двоичным инфор- - зультат суммирования в блоке 3 на значение мационным символам, подлежащим переда-(П|)-разрядного отрезка псевдослучайной

че, добавляют г( двоичных проверочных последовательности, хранящееся в регист- символов Г| Г; + loggn, полученных в со- ре 7. Результат деления в виде отрезка ответствии с используемым (П|, к)-кодом, длины К -(- Г двоичных символов подают при этом щ NI, где NI и А, - целые числа.в блок 4 декодирования, где в соответНад полученной последовательностью длины ствии с введенными при кодировании проП двоичных символов производят операцию псевдостохастического преобразования, заключающуюся в умножении по модулю неприводимого полинома степени HI на (П|)верочными символами проверяют этот отрезок на наличие ошибок. При обнаружении ошибок в блоке 4 декодирования сигнал с его третьего выхода поступает на упразрядную псевдослучайную последователь- 40 равляющий вход блока 11 пробного исправность, и сложение по модулю два результата умножения с другой (П|)-разрядной псевдослучайной последовательностью.

Последовательность, полученную после псевдостохастического преобразования, длиления ошибок.

При необнаружении ошибок К информационных символов записывают в блок 12 промежуточного хранения и подают на перны П| N|A разделяют на NI отрезков вход блока 13 сравнения.

Одновременно считывают первую ячейку 18 памяти, в которую была записана единица в начале процесса декодирования. Сигнал с ячейки 18 сдвига подают на единичный вход триггера 14, устанаврочного отрезка длины 1 Г2 двоичных ливая его в положение «1, на управляю- символов, которые добавляют при передаче щий вход блока 11 пробного исправления

ошибок для организации пробного исправления ошибок и на установочный вход второй ячейки 19 памяти, записывая в нее

(Ni 4- 1)Х двоичных символов, а общее 55 единицу. По окончании пробного исправле- число проверочных символов равным г ния ошибок отрезок длины К -+- Г: двоич : г Г;..ных символов подают через информационП: м п-р;1зрядную последователь-ный выход блока 11 пробного исправлеHociii xo b i 0 устройства записывают ния ошибок на второй вход приемного редлины Я, каждый и производят кодирование второй ступени, в соответствии с кото- ры.м одноименные символы полученных отрезков складывают по модулю два с получением в результате суммирования провек П| двоичным символам. В результате общая длина передаваемой кодовой последовательности делается равной п N2.

верочными символами проверяют этот отрезок на наличие ошибок. При обнаружении ошибок в блоке 4 декодирования сигнал с его третьего выхода поступает на управляющий вход блока 11 пробного исправления ошибок.

При необнаружении ошибок К информационных символов записывают в блок 12 промежуточного хранения и подают на перв й вход блока 13 сравнения.

гистра 1 с последующим повторением рассмотренной операции декодирования.

Если в одном из последующих циклов декодирования вновь зафиксирован факт отсутствия ошибок в том же отрезке К + + г двоичных символов, то К информационных символов записывают в регистр 12, переписывая его содержимое на второй вход блока 13 сравнения, и подают К информационных символов на первый вход блока 13 сравнения. Одновременно считывают Ю сигнал, соответствующий «1, с второй ячейки 19 памяти (с перезаписью) и подают этот сигнал на управляющий вход блока 13. Если сравниваемые в блоке 13 отрезки К информационных символов признаны одинаковы- ми, то сигнал с первого выхода блока 13 сравнения подают на установочный вход триггера 14, устанавливая его в состояние «1, и на управляющий вход блока 11 пробного исправления ощибок (на проведение следующего цикла исправления ощибок).

По окончании всех I заданных циклов пробного исправления ошибок сигнал с второго выхода блока 11 пробного исправления ошибок поступает на входы первого 15 и третьего 17 ключей. Если на первом вхопри пробном исправлении произойдет ошибка, которая не будет обнаружена блоком И, и сообщение будет выдано получателю с необнаруживаемой ошибкой. Значенж определяется выражением

(g).l-(l-P,,o) Y

гдep(g) -вероятность появления ошибки конфигурации g из множества ощибок, исправляемых с вероятностью Риспр используемым кодом;

Рно- вероятностьнеобнаружения

ощибки в кодовом слове блоком 11.

Формула изобретения

Устройство для исправления ошибок по авт. св. № 1287296, отличающееся тем, 20 что, с целью повышения достоверности работы устройства, в него введены четвертый буферный регистр, блок сравнения, триг - гер, первый - третий ключи, первая и вторая ячейки памяти, входы считывания которых объединены с информационным

де первого ключа 15 имеется сигнал, сви- входом четвертого буферного регистра и детельствующий о положении триггера 14 в первым информационным входом блока срав- состоянии «1, то сигнал с первого ключа 15 проходит на второй ключ 16 и считывает содержимое регистра 12 на первый вынения и подключены к первому выходу блока декодирования, входы обнуления четвертого буферного регистра и второй ячейход 22 устройства. Если триггер 14 нахо- о памяти, первый вход обнуления тригдится в положении «О, то по сигналу,гера и установочный вход первой ччемкгг

поступающему на третий ключ 17, выраба-памяти объединены и подключены к вхолу

тывается сигнал, свидетельствующий о не-цикловой синхронизации устройства, выход

исправимой ошибке, который поступает напервой ячейки памяти объединен с перпмм

второй выход 23 устройства.выходом блока сравнения и третьим вым)

Если при сравнении в блоке 13 двух от- 05ДОм блока декодирования и подключен к

резков К информационных символов ониустановочному входу триггера и nepB(v,i

не одинаковы, то по второму выходу блока 13установочному входу второй ячейки ,

сравнения вырабатывается сигнал, свиде-первые входы первого и третьего ключей

тельствующий о неисправимой, ошибке, ко-объединены и подключены к второму i i ivoторый поступает на установку триггера 14 вду блока декодирования и второмх конгположение «О и на второй выход 23 уст- 40рольному выходу блока пробного игпрявройства.ления ошибок, первый и второй выходь четвертого буферного регистра соединены соотТаким образом, если в любых двух цик-ветственно с вторым информационным вхолах декодирования (из заданного I) кодо-дом блока сравнения и первым входом втовой последовательности получены К Ч-Г -раз-рого ключа, прямой и инверсный выхорядные отрезки, ошибки в которых не об- ды триггера подключены к вторым входам

наружены, но при сравнении они не совпа-соответственно третьего и первого ключей,

дают, то принимается решение о наличиивыход первого ключа соединен с вторым

неисправимой ошибки. Тем самым исключа-входом второго ключа, выход которого явются необнаруживаемые ошибки, которыеляется первым выходом устройства, выход

могли бы быть выданы получателю в слу-второй ячейки памяти соединен с ее вторым

чае появления в кодовой последовательности такой конфигурации g ошибки, которая могла бы быть исправлена с вероятностью Риспр, например, в (.)-м цикле декодирования, но существует вероятность того, что в J-M цикле декодирования (j : )

установочным входом и управляющим входом блока сравнения, второй выход которого подключен к второму входу обнуления триггера, объединен с выходом третьего ключа и является вторым выходом устройства.

при пробном исправлении произойдет ошибка, которая не будет обнаружена блоком И, и сообщение будет выдано получателю с необнаруживаемой ошибкой. Значенж определяется выражением

(g).l-(l-P,,o) Y

гдep(g) -вероятность появления ошибки конфигурации g из множества ощибок, исправляемых с вероятностью Риспр используемым кодом;

Рно- вероятностьнеобнаружения

ощибки в кодовом слове блоком 11.

Формула изобретения

Устройство для исправления ошибок по авт. св. № 1287296, отличающееся тем, что, с целью повышения достоверности работы устройства, в него введены четвертый буферный регистр, блок сравнения, триг - гер, первый - третий ключи, первая и вторая ячейки памяти, входы считывания которых объединены с информационным

установочным входом и управляющим входом блока сравнения, второй выход которого подключен к второму входу обнуления триггера, объединен с выходом третьего ключа и является вторым выходом устройства.

| Устройство для исправления ошибок | 1984 |

|

SU1287296A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-04-07—Публикация

1986-07-11—Подача