мент И 8, делитель 9 частоты , счетчики 10 и 11 импульсов, блок памяти 12 и кодопреобразователь 13. Кодовое слово циклического кода поступает на формирователь синдрома 3, в котором производится деление этого кодового слова на делители порождающего код многочлена. Остатки от деления поступают в блок определения позиции ошибки 4, в котором осуществляется

1

Изобретение относится к электросвязи, и может использоваться в цифровых системах передачи информации для декодирования сигналов циклического кода и исправления ошибок.

Цель изобретения - увеличение помехоустойчивости декодирования путем уменьшения вероятности внесения дополнительных ошибок.

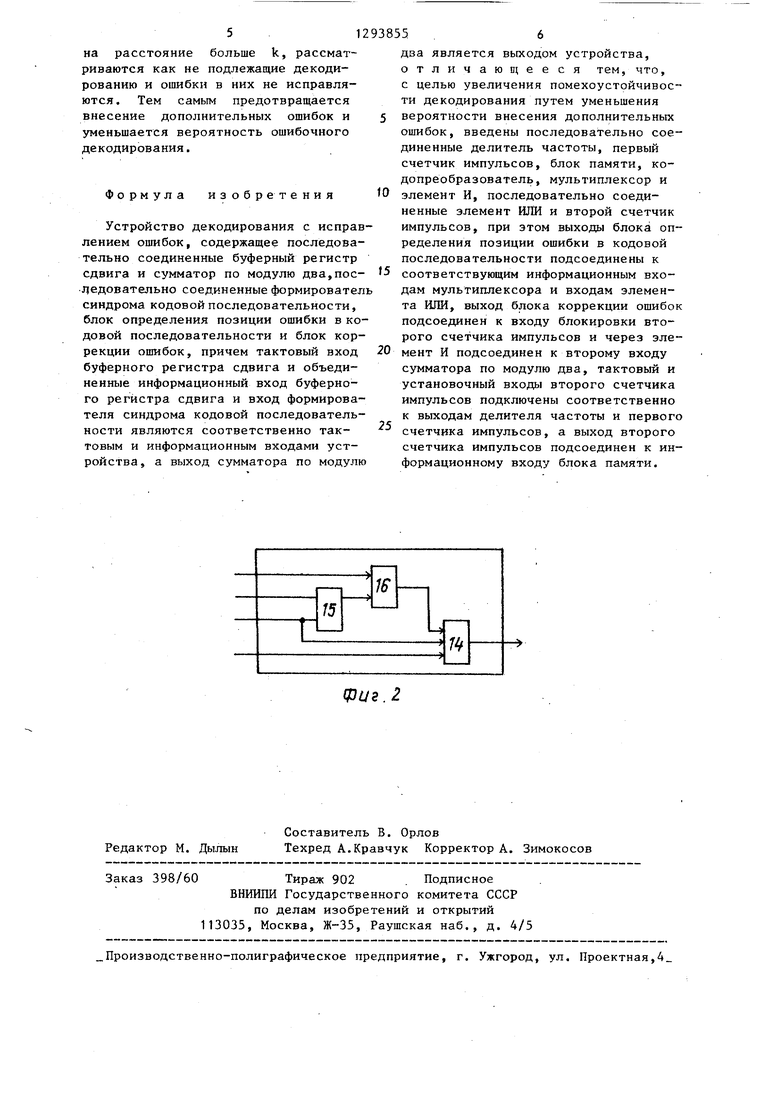

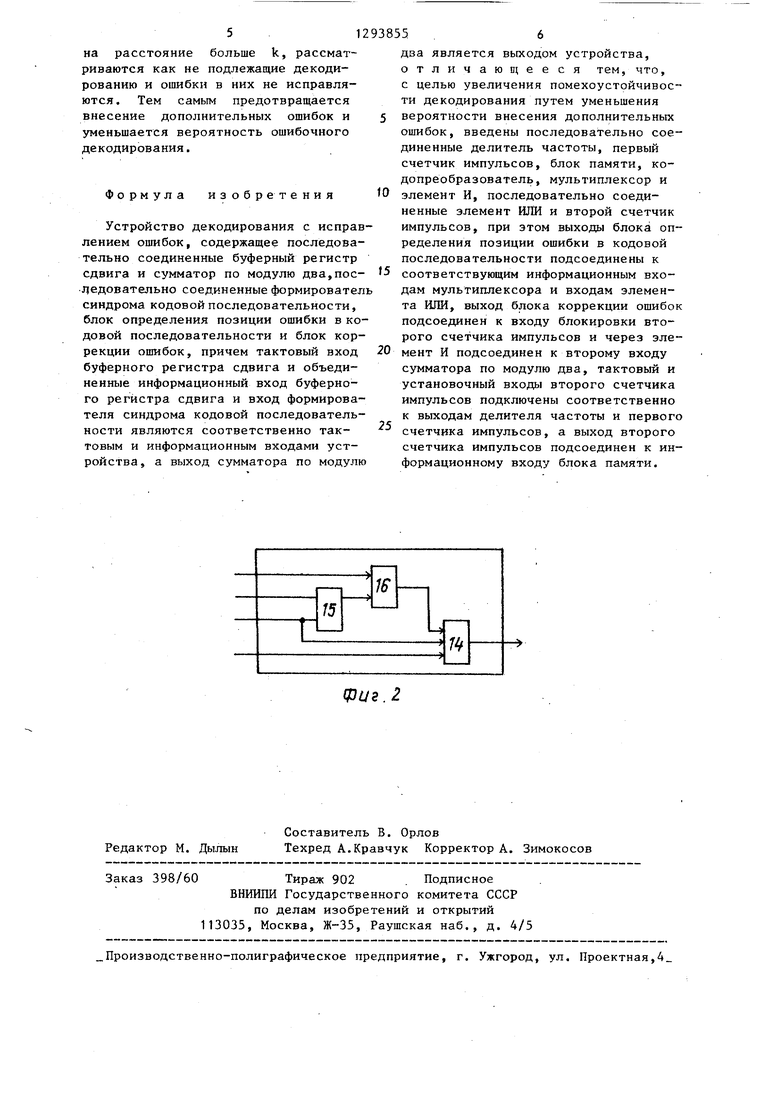

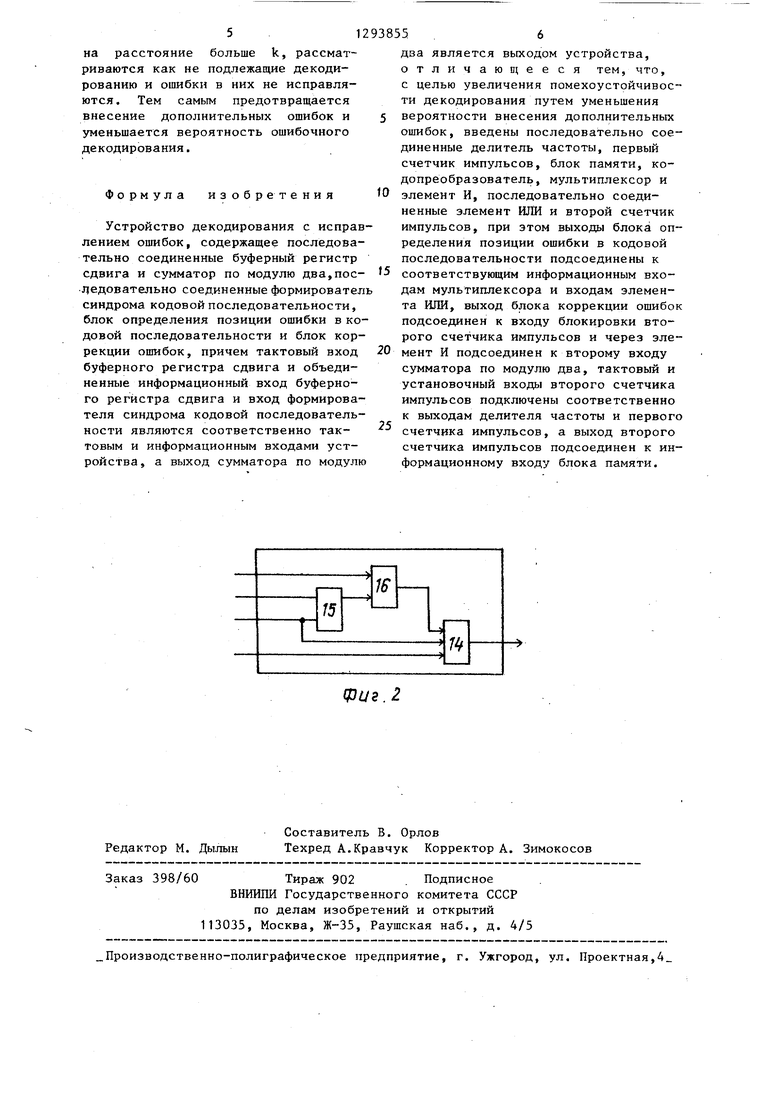

На фиг.1 представлена структурная электрическая схема устройства декодирования с исправлением ошибокJ на фиг.2 - структурная электрическая схема второго счетчика импульсов

Устройство декодирования с исправлением ошибок содержит буферный регистр 1 сдвига, сумматор 2 по модулю два, формирователь синдрома 3 кодовой последовательности, блок 4 определения позиции ошибки в кодовой последовательности, блок 5 коррекции ошибок, элемент ИЛИ 6, мультиплексор 7, элемент И 8, делитель 9 частоты, первый и второй счетчики 10 и 11 импульсов, блок 12 памяти, кодопреобразователь 13.

Втором счетчик 11 импульсов содержит двоичный счетчик 14, D-триг- гер 15 и элемент ИЛИ 16.

Устройство декодирования с исправлением ошибок работает следующим образом.

Кодовое слово циклического кода (входной кодовой последовательности) поступает на вход формирователя синдрома 3 (фиг.1), в котором производится деление этого кодового слова на неприводимые делители порождающего код многочлена, и в буферный ревычисление коэф. многочлена локаторов ошибок. Вычисленные значения поступают в БКО 5 для определения местоположения ошибок, БКО 5 формирует сигнал об исправлении, соответствующий локаторам ошибок, обращающим многочлен в О. Сигнал проходит на сумматор 2. Мультиплексор 7 в определенных условиях может заблокировать прохождение этого сигнала. 2 ил.

гистр 1, в котором кодовое слово задерживается на время декодирования,

Остатки от деления из формирователя синдрома 3 поступают в блок 4 определения позиции ошибки, в котором осуществляется вычисление коэффициентов многочлена локаторов ошибок :

W

6(Z).(6. ,G,...6j,)zJ,,

JM

где Z - локаторы ошибок;

t - количество ошибок, которое

может исправить код,

(6j, (ojj . . 6js ) - вектор-коэффициент многочлена локаторов ошибок. Сигналы, соответствующие коэффициентам многочлена локаторов ошибок,

поступают в блок 5 коррекции ошибок для определения местоположения ошибок. Блоком 5 коррекции ошибок формируется сигнал об исправлении, со- ответствуюищй локаторам ошибок,обращающим многочлен в 0.

Прохождение сигнала об исправлении ошибок на сумматор 2 через элемент И 8 может быть заблокировано мультиплексором 7, в котором выходные сигналы блока 5 коррекции ошибок сначала объединяются в соответствии с алгоритмом: A.-l

...у 4...v( (,., V )

(4. .

v...v(...v()

.o,

затем один нз сигналов Л.

А,

А

-О -

А ...А , А коммутируется на выход мультиплексора 7 в зависимости от кода, поданного на управляющие входы мультиплексора 7 из кодопреобразователя 13.

Если на выход.мультиплексора 7 Iкоммутируется сигнал А 1, то он блокирует исправление каких бы то ни было символов входной кодовой последовательности, В этом случае информация не исправляется и дополнительные ошибки устройством декодирования с исправлением ошибок не вносятся.

Если на выход мультиплексора 7 коммутируется сигнал А , то исправсчетчика 14 блокируется всякий раз, когда многочлен локаторов ошибок имеет решение (сигналом с выхода бло ка 5 коррекции ошибок) или когда мно

ление символов разрешается только в тех кодовых словах, которым соответствует многочлен локаторов ошибок

с нулевыми коэффициентами, кроме пер-- гочлен локаторов ошибок имеет все вого (6 6 ...6 )нулевые коэффициенты (сигналом с выТакой многочлен имеет только одно решение и, следовательно, в этом случае устройство декодирования с исправлением ошибок будет вносить не более чем одну дополнительную ошибку на каждое кодовое слово в случае превышения исправляющей способности кода и вместе с тем сохраняет способность исправлять все одиночные ошибки, если исправляющая способность

кода не превышена. I

Если на выход мультиплексора 7 коммутируется сигнал А, то исправление символов разрешается только в тех кодовых словах, которым соответствует многочлен локаторов ошибок с нулевыми коэффициентами, кроме коэффициентов с первого по k-й. Такой многочлен имеет k решений и, следовательно, в этом случае устройство декодирования с исправлением ошибок может вносить не более чем k дополнительных ошибок на кодовое слово в случае цревышения исправляющей способности кода и вместе с тем сохраняет способность исправлять все ошибки веса не более k, если исправляющая способность кода не превышена.

Если на выход мультиплексора 7 коммутируется сигнал , то блокировка прохождения сигнала об исправлении не производится.

Кодопреобразователь 13 управляет подключением того или иного сигнала на выход мультиплексора 7 с учетом качества канала, оцененного за предыдущий отрезок времени, продолжитель25

30

хода элемента ИЛИ б). Второй счет- чик 11 подсчитывает только те кодовые слова, для которых многочлен локаторов ошибок не имеет решений,что имеет место тогда, когда превышена величина исправляющей способности- кода,

По окончании промежутка времени, задаваемого пег-вь : ;.четчиком 10,производится перепись числа из второго счетчика 11 в блок 12 памяти и обнуление второго счетчика 11.

Кодопреобразователь 13 преобразует число, записанное в блоке 12 памяти, в код управления мультиплексором 7. Кодопреобразователь 13, выполняя функции порогового элемента, должен иметь возможность гибкой мо- дификации, так как конкретная зависимость, задаваемая кодопреобразователем 13, определяется структурой кода и видом искажений в канале связи. Например, кодопреобразователь 13 может быть выполнен в виде постоянного запоминающего блока.

35

45

50

55

Если кодопреобразователем 13 задается код, при котором на выход мультиплексора 7 выдается сигнал А,, то устройство декодирования с исправлением ошибок будет исправлять ошибки весом не более k. Все кодовые слова, которые находятся в пределах расстояния k от кодового слова, считаются возникшими из этого слова и ошибки в них исправляются, в то время как принимаемые слова, отличающиеся от всех кодовых слов

ность которого определяется емкостью первого счетчика 10, который подключен к выходу делителя 9. Коэффициент деления делителя 9 равен количеству бит в кодовом слове. Первый счетчик 10 подсчитывает количество кодовых слов и по истечении заданного отрезка времени выдает импульс переполнения и обнуляется.

Второй счетчик 11 (фиг,2), содер- жащий последовательно соединенные D-триггер 15, элемент ИЛИ 16 и двоичный счетчик 14, также осуществляет подсчет количества кодовых слов. При этом счетный вход двоичного

счетчика 14 блокируется всякий раз, когда многочлен локаторов ошибок имеет решение (сигналом с выхода блока 5 коррекции ошибок) или когда мно

гочлен локаторов ошибок имеет все нулевые коэффициенты (сигналом с вы

хода элемента ИЛИ б). Второй счет- чик 11 подсчитывает только те кодовые слова, для которых многочлен локаторов ошибок не имеет решений,что имеет место тогда, когда превышена величина исправляющей способности- кода,

По окончании промежутка времени, задаваемого пег-вь : ;.четчиком 10,производится перепись числа из второго счетчика 11 в блок 12 памяти и обнуление второго счетчика 11.

Кодопреобразователь 13 преобразует число, записанное в блоке 12 памяти, в код управления мультиплексором 7. Кодопреобразователь 13, выполняя функции порогового элемента, должен иметь возможность гибкой мо- дификации, так как конкретная зависимость, задаваемая кодопреобразователем 13, определяется структурой кода и видом искажений в канале связи. Например, кодопреобразователь 13 может быть выполнен в виде постоянного запоминающего блока.

Если кодопреобразователем 13 задается код, при котором на выход мультиплексора 7 выдается сигнал А,, то устройство декодирования с исправлением ошибок будет исправлять ошибки весом не более k. Все кодовые слова, которые находятся в пределах расстояния k от кодового слова, считаются возникшими из этого слова и ошибки в них исправляются, в то время как принимаемые слова, отличающиеся от всех кодовых слов

51293855

расстояние больше k, рассматаются как не подлежащие декодианию и ошибки в них не исправляя. Тем самым предотвращается сение дополнительных ошибок и 5 ньшается вероятность ошибочного одирования.

Формула изобретения 0

дв о с ти ве ош ди сч до эл не им ре по со да та по ро ме су ус им к сч сч

Устройство декодирования с исправлением ошибок, содержащее последовательно соединенные буферный регистр сдвига и сумматор по модулю два,пос- Ледовательно соединенные формировател синдрома кодовой последовательности, блок определения позиции ошибки в кодовой последовательности и блок коррекции ошибок, причем тактовый вход буферного регистра сдвига и объединенные информационный вход буферного регистра сдвига и вход формирователя синдрома кодовой последовательности являются соответственно тактовым и информационным входами устройства, а выход сумматора по модулю

Фиг. 2

Редактор М, Дылын

Составитель В, Орлов

Техред А.Кравчук Корректор А. Зимокосов

398/60

Тираж 902 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

„Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

два является выходом устройства, отличающееся тем, что, с целью увеличения помехоустойчивости декодирования путем уменьшения вероятности внесения дополнительных ошибок, введены последовательно соединенные делитель частоты, первый счетчик импульсов, блок памяти, кодопреобразователь, мультиплексор и элемент И, последовательно соединенные элемент ИЛИ и второй счетчик импульсов, при этом выходы блока определения позиции ошибки в кодовой последовательности подсоединены к соответствующим информационным входам мультиплексора и входам элемента ИЛИ, выход блока коррекции ошибок подсоединен к входу блокировки второго счетчика импульсов и через элемент И подсоединен к второму входу сумматора по модулю два, тактовый и установочный входы второго счетчика импульсов подключены соответственно к выходам делителя частоты и первого счетчика импульсов, а выход второго счетчика импульсов подсоединен к информационному входу блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ ЦИКЛИЧЕСКОГО КОДА ХЕММИНГА | 2004 |

|

RU2270521C1 |

| Устройство декодирования произведений кодов Рида-Соломона | 2017 |

|

RU2677372C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КОДОВ РИДА-СОЛОМОНА | 2006 |

|

RU2314639C1 |

| Запоминающее устройство с исправлением ошибок | 1984 |

|

SU1226536A1 |

| Декодер циклического кода | 1988 |

|

SU1599996A1 |

| Декодер сверточного кода (его варианты) | 1985 |

|

SU1320875A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| ПОРОГОВЫЙ ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1991 |

|

RU2023349C1 |

| Способ кодовой цикловой синхронизации для каскадного кода Рида-Соломона и Боуза-Чоудхури-Хоквингема [РС(32,16,17), БЧХ(31,16,7)] при одновременном применении жестких и мягких решений | 2020 |

|

RU2747623C1 |

Изобретение относится к электросвязи и может использоваться в цифровых системах передачи информации для декодирования сигналов циклического кода и исправления ошибок. Цель изобретения - увеличение помехоустойчивости декодирования .путем уменьшения вероятности внесения дополнительных ошибок. Устр-во содержит буферный регистр 1 сдвига,сумматор 2 по модулю два, формирователь синдрома 3 кодовой последовательности, блок определения позиции ошибки 4 в кодовой последовательности, блок коррекции ошибок (БКО) 5, элемент ИЛИ 6, мультиплексор 7, элесл с Ф1Л.Г

| Устройство для декодирования помехустойчивых кодов в каналах передачи непрерывных сообщений | 1975 |

|

SU568182A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Берлекэмп Э | |||

| Алгебраическая теория кодирования | |||

| - М.: Мир, 1971, с | |||

| Приспособление, увеличивающее число оборотов движущихся колес паровоза | 1919 |

|

SU146A1 |

Авторы

Даты

1987-02-28—Публикация

1985-04-08—Подача