315

Изобретение относится к технике связи с использованием помехоустойчивого кодирования и предназначено для исправления ошибок, возникших в канале связи.

Цель изобретения - повышение помехоустойчивости устройства.

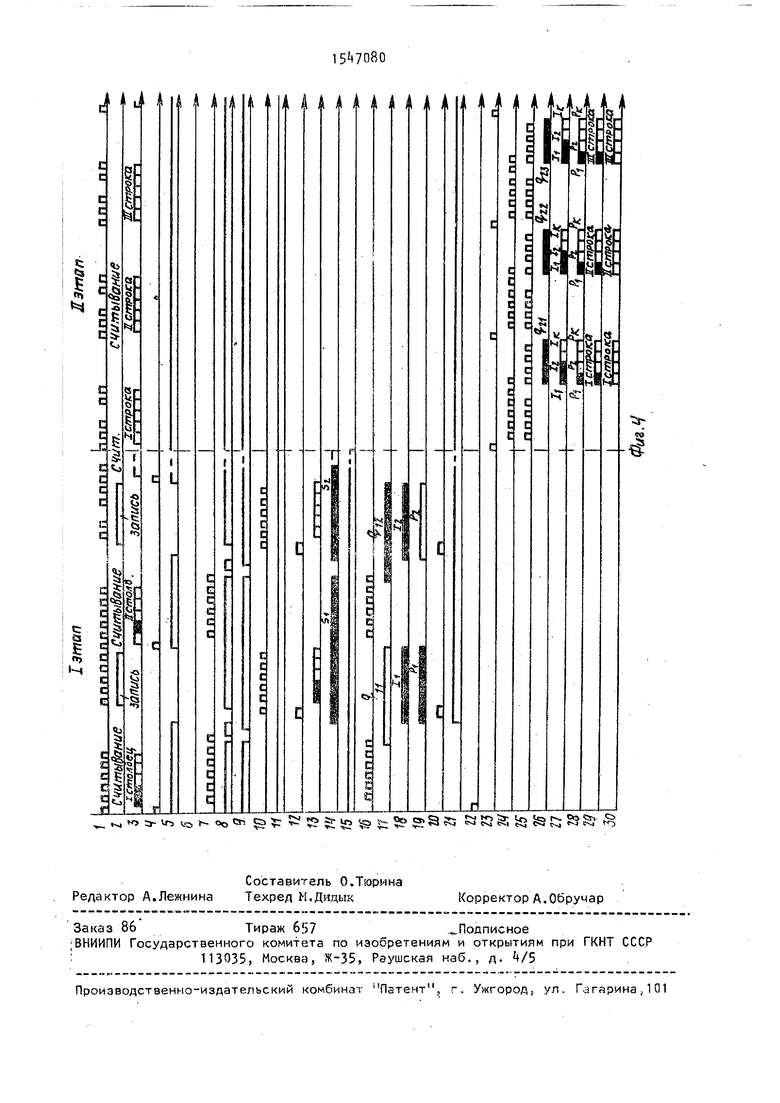

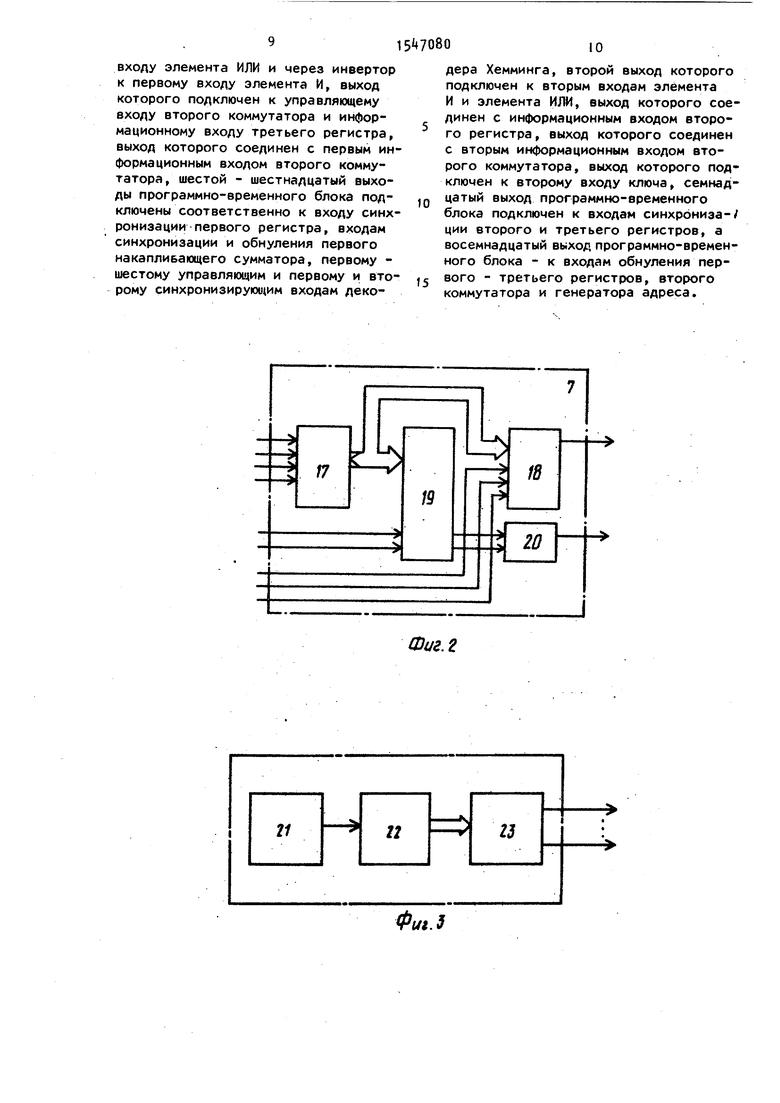

На фиг.1 представлена схема предлагаемого устройства; на фиг.2 - структурная схема декодера Хемминга; на фиг.З - структурная схема программно-временного блока; на фиг.4 - временные диаграммы сигналов, поясняющие работу устройства.

Устройство для декодирования итеративного кода содержит генератор 1 адреса, программно-временной блок 2, блок 3 памяти, элемент k НЕРАВНОЗНАЧНОСТЬ, коммутаторы 5 и 6, де- кодер 7 Хемминга, накапливающие сумматоры 8 и 9, регистры 10, 11 и 12, инвертор 13, элемент ИЛИ Н, элемент И 15 и ключ 16.

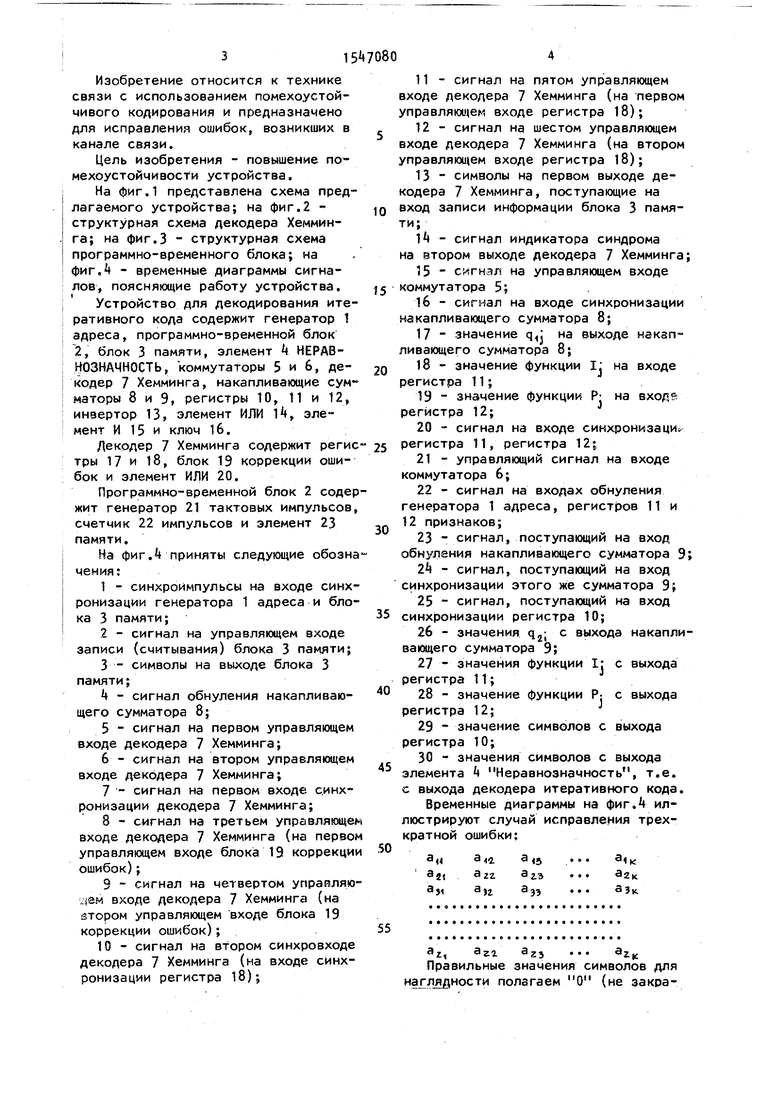

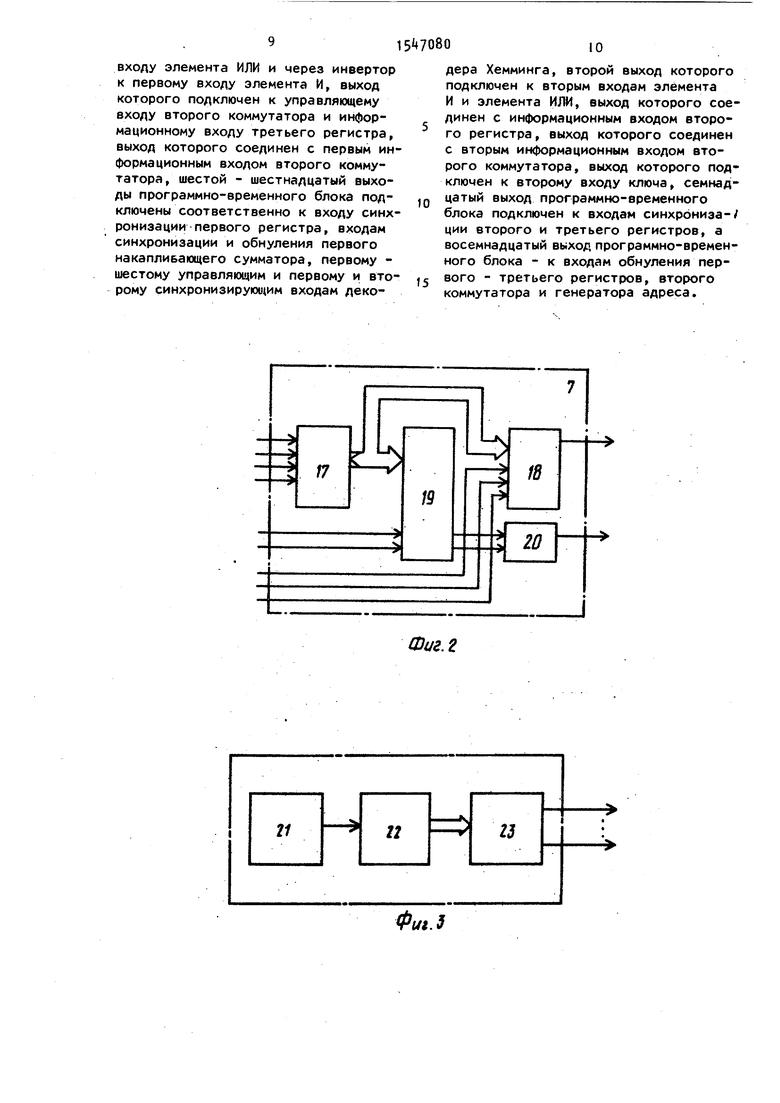

Декодер 7 Хемминга содержит регис тры 17 и 18, блок 19 коррекции ошибок и элемент ИЛИ 20.

Программно-временной блок 2 содержит генератор 21 тактовых импульсов, счетчик 22 импульсов и элемент 23 памяти.

На фиг. приняты следующие обозна чения:

1- синхроимпульсы на входе синхронизации генератора 1 адреса и блока 3 памяти;

2- сигнал на управляющем входе записи (считывания) блока 3 памяти;

3- символы на выходе блока 3 памяти;

- сигнал обнуления накапливаю- щего сумматора 8;

5- сигнал на первом управляющем входе декодера 7 Хемминга;

6- сигнал на втором управляющем входе декодера 7 Хемминга;

7- сигнал на первом входе синхронизации декодера 7 Хемминга;

8- сигнал на третьем управляющее входе декодера 7 Хемминга (на первом управляющем входе блока 19 коррекции ошибок);

9- сигнал на четвертом управляю- дам входе декодера 7 Хемминга (на зтором управляющем входе блока 19 коррекции ошибок);

10 - сигнал на втором синхровходе декодера 7 Хемминга (на входе синхронизации регистра 18);

0

5

5

0

0

5

11- сигнал на пятом управляющем входе декодера 7 Хемминга (на первом управляющем входе регистра 18);

12- сигнал на шестом управляющем входе декодера 7 Хемминга (на втором управляющем входе регистра 18);

13- символы на первом выходе декодера 7 Хемминга, поступающие на вход записи информации блока 3 памяти;

1А - сигнал индикатора синдрома на втором выходе декодера 7 Хемминга;

15- сигнал на управляющем входе коммутатора 5;

16- сигнал на входе синхронизации накапливающего сумматора 8;

17- значение на выходе накапливающего сумматора 8;

18- значение функции I на входе регистра 11;

19- значение функции Р- на вход регистра 12;

20- сигнал на входе синхронизации регистра 11, регистра 12;

21- управляющий сигнал на входе коммутатора 6;

22- сигнал на входах обнуления генератора 1 адреса, регистров 11 и 12 признаков;

23- сигнал, поступающий на вход обнуления накапливающего сумматора 9;

2k - сигнал, поступающий на вход синхронизации этого же сумматора 9;

25- сигнал, поступающий на вход синхронизации регистра 10;

26- значения q2; с выхода накапливающего сумматора 9;

27- значения функции I: с выхода регистра 11;

28- значение функции Р- с выхода регистра 12;

29- значение символов с выхода регистра 10;

30- значения символов с выхода элемента Неравнозначность, т.е. с выхода декодера итеративного кода.

Временные диаграммы на фиг.4 иллюстрируют случай исправления трехкратной ошибки;

Эгг

23

Правильные значения символов для нагл дности полагаем О (не закра5151 7080

шены на фиг.А), ошибочные - 1 (закрашенные) .

Устройство работает следующим образом.

В блоке 3 памяти записано кодовое слово итеративного кода в виде матрицы А

инвертирование символов а;

находящихся на пересечении столбцов, для которых значение и строк, для которых , в случае, если для всех , ..., k+1 , в противном случае (если хотя бы для одного значения ) - инвертирование

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство декодирования для системы передачи цифровых сигналов | 1985 |

|

SU1305884A1 |

| Устройство для декодирования двоичных блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1587644A1 |

| Устройство декодирования произведений кодов Рида-Соломона | 2017 |

|

RU2677372C1 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОГО СООБЩЕНИЯ И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2179365C1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| Устройство для декодирования блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1543552A1 |

| КОМПОНЕНТНЫЙ ДЕКОДЕР И СПОСОБ ДЕКОДИРОВАНИЯ В СИСТЕМЕ МОБИЛЬНОЙ СВЯЗИ | 2000 |

|

RU2247471C2 |

| УСТРОЙСТВО ИТЕРАТИВНОГО ДЕКОДИРОВАНИЯ БЛОКОВЫХ ТУРБОКОДОВ И SISO ДЕКОДЕР ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2012 |

|

RU2504901C2 |

| Запоминающее устройство с исправлением дефектов и ошибок | 1987 |

|

SU1536445A1 |

| СИСТЕМА ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ С ИСПРАВЛЕНИЕМ ОШИБОК | 1991 |

|

RU2007042C1 |

Изобретение относится к технике связи с использованием помехоустойчивого кодирования и предназначено для исправления ошибок, возникших в канале связи. Цель изобретения - повышение помехоустойчивости устройства. Устройство содержит генератор 1 адреса, первый и второй коммутаторы 5 и 6, декодер 7 Хемминга, накапливающие сумматоры 8 и 9, регистры 10,11 и 12, элемент ИЛИ 14, инвертор 13 и элемент И 15, программно-временный блок 2, блок 3 памяти, элемент 4 НЕРАВНОЗНАЧНОСТЬ, ключ 16. Устройство позволяет, помимо проверки на четность по строке и по столбцу, осуществить декодирование кода Хемминга по столбцу и вычислить логические функции I и Р, используемые для коррекции ошибок. 4 ил.

«Р4

РК

гк-н

rMt

p-f 1

аГ-ИК+1

im

та

тк

тки

м-1-11

am+-4i( amti k-M

В матрице А каждый столбец состоит из символов расширенного кода Хемминга V (n+1, г, 4), т.е. кода Хемминга (ш, г, 3), дополненного общей проверкой на четность по столбцу (символ m+1-й строки), а каждая из г первых строк дополнена символом четности по строке (символ k+1-го столбца) и представляет собой код V4 с общей проверкой на четность.

Таким образом, матрица А является кодовым словом итеративного кода V образованного из кодов V (по столбцам) и V2 (по строкам), Данный код V позволяет исправлять любую комбинацию ошибок кратности не выше трех.

Введем обозначения: V,: - кодовое слово кода V«, образующее j-й столбец матрицы A; Va; - кодовое слово кода V, образующее i-ю строку матрицы A; q - результат общей проверки на четность в кодовом слове V,j ; qa; - индикатор синдрома: , если синдром кодового слова равен нулю, и в противном случае.

Алгоритм декодирования кода V реализуется за следующие 5 шагов:

декодирование кодов V,j , вычисление Sj (, ..., k+1);

вычисление общей проверки на четы ность q,; в кодах V ;

Ч

вычисление значений функции -SjVq,j и Pj SjAqjj ;

вычисление проверки на четность q2; в кодах Vc; ;

символов а

U Л

находящихся на пересечении столбцов, для которых Р., и строк, для которых Ч2; 1.

25

45

50

20

30

При всех возможных комбинациях однократных, двукратных и трехкратных ошибок при данном построении

1 кода V приведенный выше алгоритм декодирования исправляет все эти ошибки.

В работе устройства можно выделить два этапа.

На первом этапе работы производится считывание матрицы А из блока 3 памяти по столбцам, начиная с первого (по адресам, вырабатываемым генератором 1 адреса), при этом на управляющий вход первого коммутатора 5 подается сигнал, переводящий коммутатор 5 в состояние, когда информация с его информационного входа поступает на информационные входы декодера 7 Хемминга и накапливающего сумматора 8. В этом сумматоре производится вычисление q для данного столбца, а в декодере 7 Хемминга - его декодирование, при котором исправляются однократные ошибки. Зна35 чения декодированных символов столбца с первого выхода декодера 7 Хемминга перезаписываются в блок 3 памяти на свои старые места, а значение индикатора синдрома декодирования этого столбца Sj с второго выхода декодера 7 Хемминга поступает на первые входы элемента ИЛИ I и элемента И 15 на второй вход элемента ИЛИ Н подается значение q , на второй вход элемента И 15 это же значение q; подается инвертированным при помощи инвертора 13. На выходе элемента ИЛИ 14 формируется значение , а на выходе элемента И 15 . Значения Ij и PJ записываются в соответствующие ячейки регистра 11 (там записываются значения Ij) и регистра Т2 (там записываются значения Pj). Такой процесс

55 осуществляется для всех столбцов

матрицы А, считываемых последовательно из блока 3. В результате в блок 3 будут записаны символы матрицы А

40

с исправленными однократными ошибками в столбцах (т.е. матрица А ), а в регистрах 11 и 12 - значения Ij и р- для всех столбцов, причем второй коммутатор 6 будет находиться в поло же)нии, когда на его выход будет подаваться сигнал с выхода регистра 11, если все значения , в противном случае, как только для какого-либо значения j (, 2, ..., k+1) - сигнал с выхода элемента И 15, подаваемый на управляющий вход второго коммутатора 6, переключит его в поло же|ние, когда нэ его выход будет про- хр|дить сигнал с выхода регистра 12. Теперь наступает второй этап работы, лр|и котором производится считывание последовательно по строкам символов матрицы А1, которые поступают на ин- Ф | рмационный вход первого коммутато- Р$ 5, на управляющий вход которого поступает сигнал, переключающий его в положение, когда информация е его информационного входа поступает на зХод регистра 10 и накапливающего сумматора 9, который вычисляет значение q . для данной строки. Значения символов это,й строки записываются и хранятся в регистре 10, пока Hfe закончится вычисление q2j. Значение q2; с выхода накапливающего с|умматора 9 подается на второй вход кЫюча 16 переписи информации, на первый вход которого в это время ч|ерез второй коммутатор 6 поступает Значение I (если все ), либо Pf (в противном случае), сигнал с выхода ключа 16 переписи информации равен единице лишь в том случае Когда q2;-1 и 1, 1 (если все ),

Либо Р, 1 (в противном случае), т.е «ели считываемый в это время из регистра 10 символ (в данном случае а 1, )находится на пересечении ошибочных столбца и строки. В таком

4 Нслучае на первый вход элемента равнозначность

Подается 1 и символ а

с выхода ключа 16

fj , поступающий с выхода регистра 10 на второй вход элемента И, проходит на ее вых инвертированным, т.е. исправленным. Если же символ правильный, он проходит на выход без изменения. Аналогичным образом исправляются ошибки во всех символах строки, считываемых последовательно из регистра 10. Затем производится считывание из блока 3 следующей строки и т.д.

5

0

5

0

5

0

5

0

5

Таким образом, предлагаемый декодер итеративного кода позволяет полнее использовать корректирующие свойства итеративного кода за счет применения в процессе коррекции наряду с проверкой на четность символов строк и столбцов декодирования по Хеммингу символов столбцов, а также использования в процессе декодирования результатов вычисления некоторых логических функций I и Р, благодаря чему корректирующая способность декодера возросла в 3 раза. Формула изобретения

Устройство для декодирования итеративного кода, содержащее первый регистр, информационные входы которого объединены с информационными входами первого накапливающего сумматора, выход которого соединен с первым входом ключа, выход которого подключен к первому входу элемента НЕРАВНОЗНАЧНОСТЬ, выход которого

является выходом устройства, второй регистр и блок памяти, отличающееся тем, что, с целью повышения помехоустойчивости устройства, в него введены третий регистр, второй накапливающий сумматор, инвертор, элемент ИЛИ, элемент И, коммутаторы, декодер Хемминга, программно-временной блок и генератор адреса, выходы которого подключены к адресным входам блока памяти, выход которого подключен к информационному входу первого коммутатора, пе0вый выход которого соединен с информационным входом первого регистра, выход которого подключен к второму входу элемента НЕРАВНОЗНАЧНОСТЬ, первый выход программно-временного блока подключен к входам синхронизации генератора адреса и блока памяти, второй и третий выходы программно-временного блока подключены соответственно к входу управления режимами блока памяти и управляющему входу первого коммутатора, второй выход которого подключен к информационным входам второго накапливающего сумматора и декодера Хемминга, первый выход которого подключен к входу записи блока памяти „ четвертый и пятых выходы программно-временного блока подключены соответственно к входам синхронизации и обнуления второго накапливающего сумматора, выход которого подключен непосредственно к первому

входу элемента ИЛИ и через инвертор к первому входу элемента И, выход которого подключен к управляющему входу второго коммутатора и информационному входу третьего регистра, выход которого соединен с первым информационным входом второго коммутатора, шестой - шестнадцатый выходы программно-временного блока подключены соответственно к входу синхронизации первого регистра, входам синхронизации и обнуления первого накапливающего сумматора, первому - шестому управляющим и первому и второму синхронизирующим входам деко17

дера Хемминга, второй выход которого подключен к вторым входам элемента И и элемента ИЛИ, выход которого соединен с информационным входом второго регистра, выход которого соединен с вторым информационным входом второго коммутатора, выход которого подключен к второму входу ключа, семнадцатый выход программно-временного блока подключен к входам синхрониза-/ ции второго и третьего регистров, а восемнадцатый выход программно-временного блока - к входам обнуления первого - третьего регистров, второго коммутатора и генератора адреса.

18

Фиг. .

Фиг.З

А А

с

С

С

с к

4s

а

4|

Clfc

с 5 с§

ПИ

с

1

M

Ј

С

1

| Иак-Вильямс Ф.Дж., Слоэн Н.Дж | |||

| Теория кодов, исправляющих ошибки | |||

| M.S Связь, 1979, с | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Микросхема обнаружения и исправления ошибок в ЗУ | |||

| - Электронная промышленность, 1983, вып.А | |||

Авторы

Даты

1990-02-28—Публикация

1988-06-24—Подача