V21) 1

(22) 16.09.85

(46) 15.04.88. Бюл. № 14

(72) А.И.Квасов, В.В.Лузянин,

В.П.Луэянин и А.В.Мурин

(53)681.333(088.8)

.(56) Авторское свидетельство СССР № 750503, кл. G 06 F 7/122, 1978.

Авторское свидетельство СССР № 304,585, кл. G 06 F 15/44 1971.

(54)УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ БИМАТРИЧНЫХ ИГР

(57) Изобретение относится к вычислительной технике и используется для решения задач математической теории

игр. Цель изобретения - расширение функциональных возможностей устройства за счет решения биматричных игр с ненулевой суммой выигрышей сторон. Устройство содержит два блока памяти, в которых записаны стратегии сторон в биматричной игре. Код стратегии, выбранный одной из сторон, яв- J}яeтcя адресом памяти для выбора ответных стратегий другой стороны. Вы- игрьппи сторон после каждого хода поступают в вычислительные блоки, которые формируют значения максимальных и минимальных цен выигрышей сторон и вероятности появления стратегий каждой стороны. 4 ил., 1 табл.

(g

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для опроса информационных каналов | 1982 |

|

SU1062677A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ В АДАПТИВНЫХ ТЕЛЕМЕТРИЧЕСКИХ СИСТЕМАХ | 1995 |

|

RU2103745C1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Устройство для определения пересечения множеств | 1990 |

|

SU1756903A1 |

| Устройство для решения задач теории игр | 1988 |

|

SU1608687A1 |

| Многоканальное устройство для быстрого преобразования Фурье с конвейерной обработкой операндов | 1984 |

|

SU1211752A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

00 00

00 оо

4

Изобретение относится к вычислительной технике и может быть использовано для решения задач математической теории игр.

Цель изобретения - расширение функциональных возможностей за счет решения биматричных игр с ненулевой суммой выигрьшюй сторон.

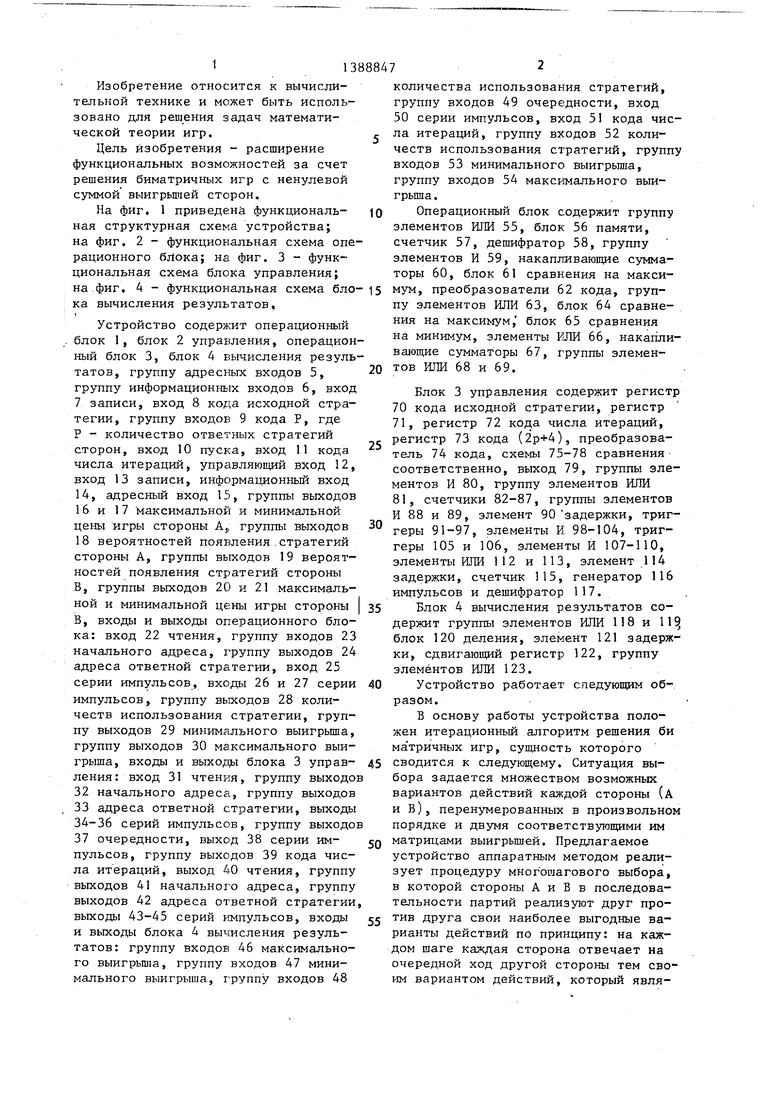

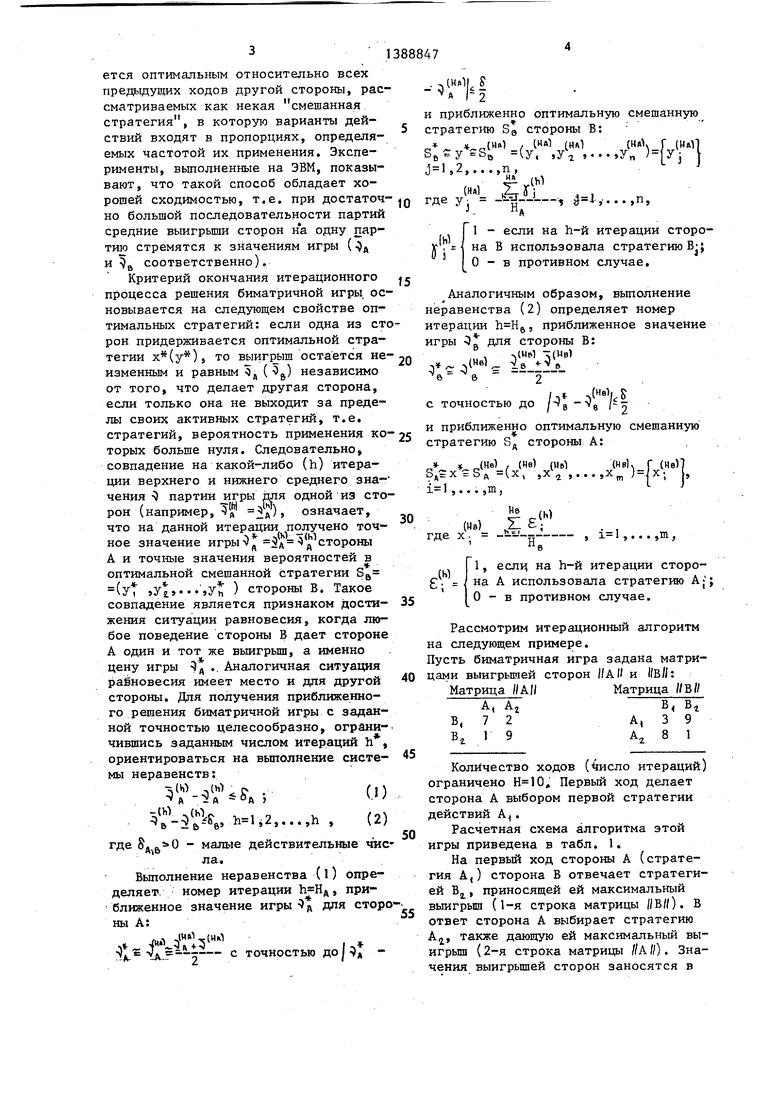

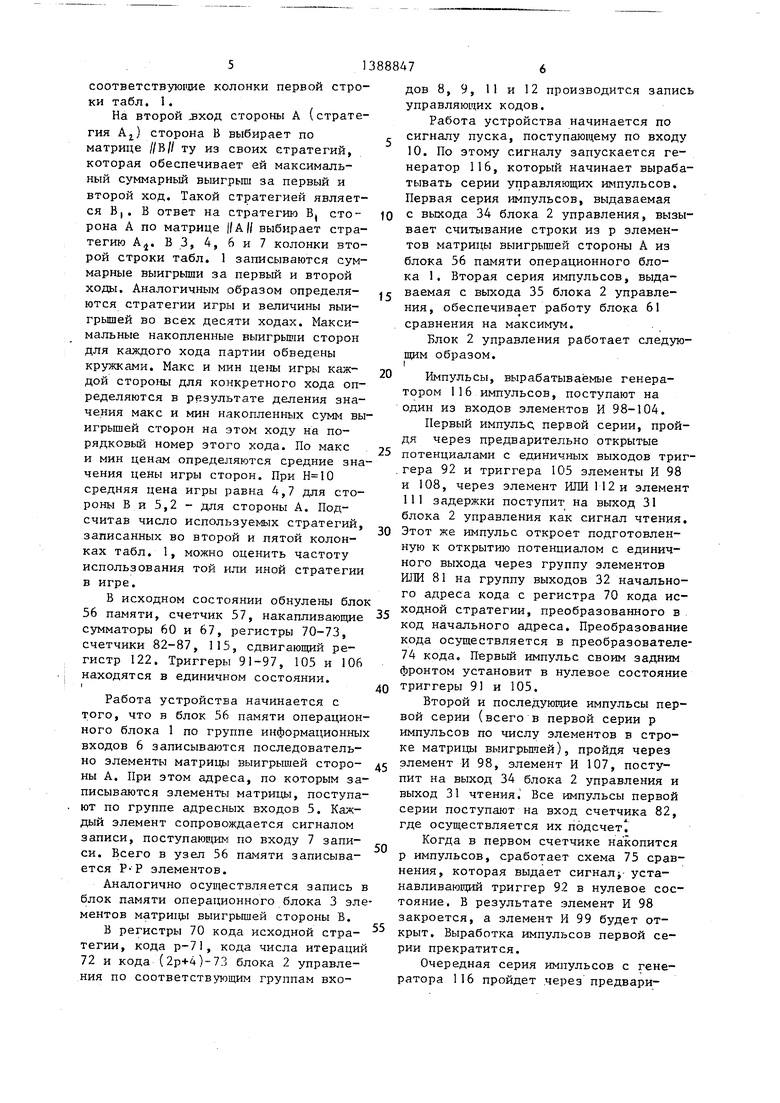

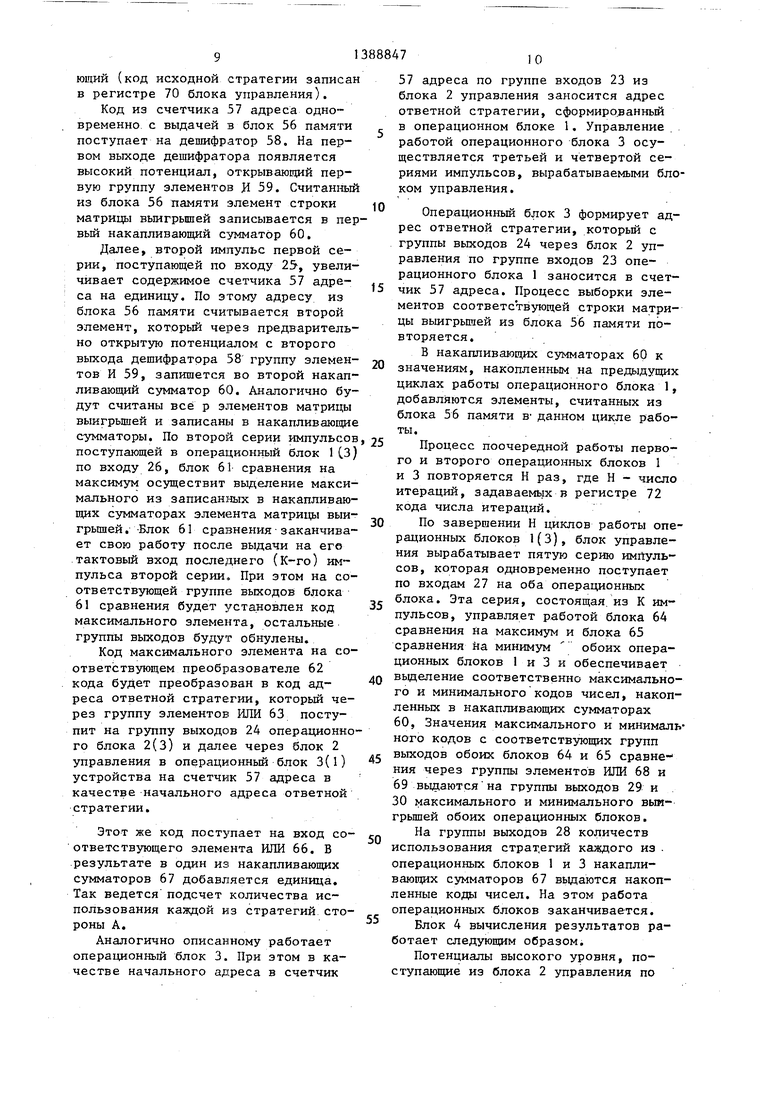

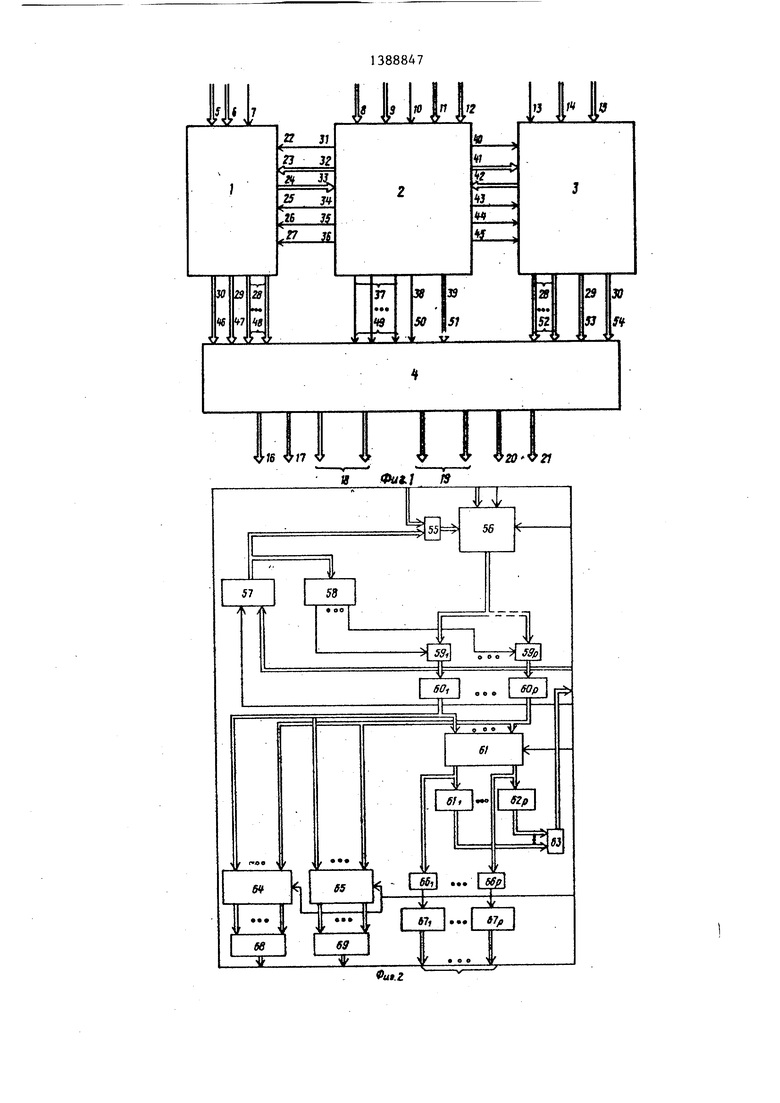

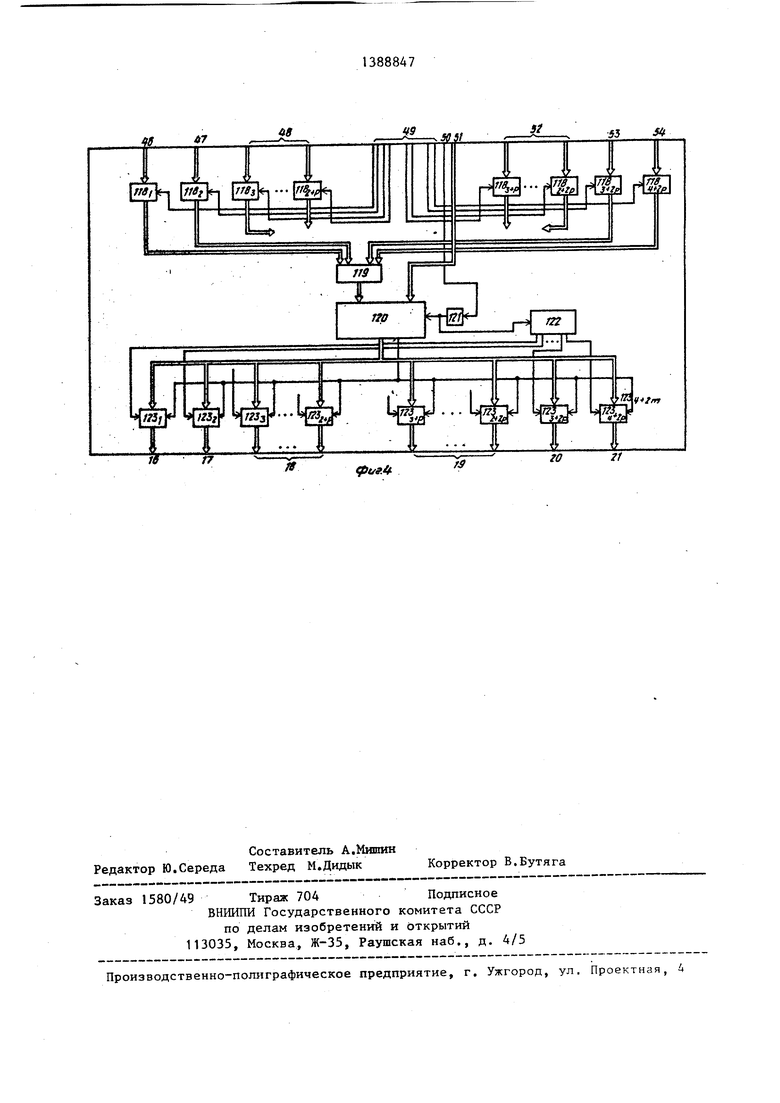

На фиг. 1 приведена функциональ- нал структурная схема устройства; на фиг. 2 - функциональная схема операционного блока; на фиг. 3 - функциональная схема блока управления; на фиг. 4 - функциональная схема бло- ка вычисления результатов,

Устройство содержит операционный блок 1, блок 2 управления, операционный блок 3, блок 4 вычисления результатов, группу адресных входов 5, группу информационных входов 6, вход 7 записи, вход 8 кода исходной стратегии, группу входов 9 кода Р, где Р - количество ответных стратегий сторон, вход 10 пуска, вход 11 кода числа итераций, управляющий вход 12, вход 13 записи, информационный вход 14, адресный вход 15, группы выходов 1 6 и 1 7 максимальной и минимальной цены игры стороны А,, группы выходов 18 вероятностей появления .стратегий стороны А, группы выходов 19 вероятностей появления стратегий стороны В, группы выходов 20 и 21 максималъ- ной и минимальной цены игры стороны В, входы и выходы операционного блока: вход 22 чтения, группу входов 23 начального адреса, группу выходов 24 адреса ответной стратегии, вход 25 серии импульсов, входы 26 и 27 серии импульсов, группу вьжодов 28 количеств использования стратегии, группу выходов 29 минимального выигрьшга, группу выходов 30 максимального выигрыша, входы и выхода блока 3 управ- ления: вход 31 чтения, группу выходо

32начального адреса, группу выходов

33адреса ответной стратегии, выходы 34-36 серий импульсов, группу выходо 37 очередности, выход 38 серии им- пульсов, группу выходов 39 кода числа итераций, выход 40 чтения, группу выходов 41 начального адреса, группу выходов 42 адреса ответной стратегии выходы 43-45 серий импульсов, входы и выходы блока 4 вычисления результатов: группу входов 46 максимального выигрьшш, группу входов 47 минимального выигрыша, группу входов 48

количества использования стратегий, группу входов 49 очередности, вход 30 серии импульсов, вход 51 кода числа итераций, группу входов 52 количеств использования стратегий, группу входов 53 минимального выигрьша, группу входов 54 максимального выи- грьш1а.

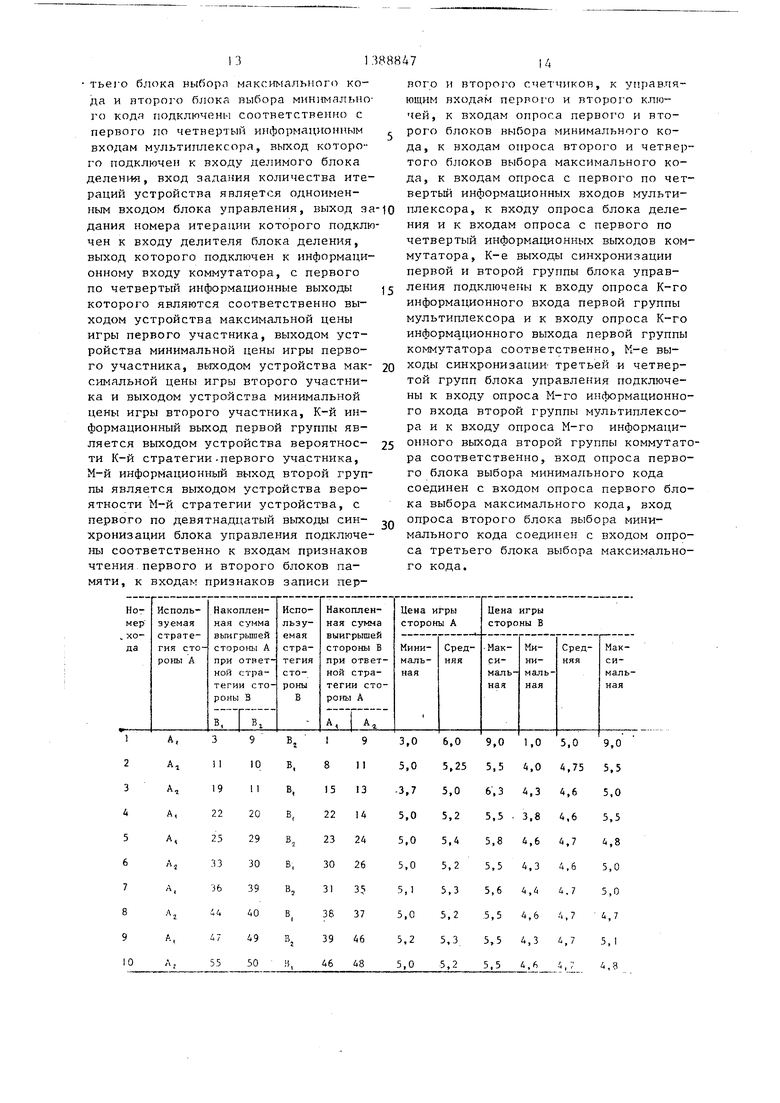

Операционный блок содержит группу элементов ИЛИ 55, блок 56 памяти, счетчик 57, дешифратор 58, группу элементов И 59, накапливающие сумматоры 60, блок 61 сравнения на максимум, преобразователи 62 кода, группу элементов Р1ЛИ 63, блок 64 сравнения на максимум, блок 65 сравнения на минимум, элементы ИЛИ 66, накапли- закщке сумматоры 67, группы элементов ИЛИ 68 и 69.

Блок 3 управления содержит регистр 70 кода исходной стратегии, регистр 71, регистр 72 кода числа итераций, регистр 73 кода (2р+4), преобразователь 74 кода, схемы 75-78 сравнения- соответственно, выход 79, группы элементов И 80, группу элементов ИЛИ 81, счетчики 82-87, группы элементов И 88 и 89, элемент 90 задержки, триггеры 91-97, элементы И 98-104, триггеры 105 и 106, элементы И 107-110, элементы ИЛИ 112 и 113, элемент 114 задержки, счетчик 115, генератор 116 импульсов и дешифратор 117.

Блок 4 вычисления результатов содержит группы элементов ИЛИ 118 и 11 блок 120 деления, элемент 121 задержки, сдвигающий регистр 122, группу элементов ИЛИ 123.:

Устройство работает следующим образом.

В основу работы устройства положен итерационный алгоритм решения би ма тричных игр, сушдость которого сводится к следующему. Ситуация выбора задается множеством возможных вариантов действий каждой стороны (А и в), перенумерованных в произвольном порядке и двумя соответствующими им матрицами выигрьшгей. Предлагаемое устройство аппаратным методом реализует процедуру многошагового выбора, в которой стороны А и В в последовательности партий реализуют друг против друга свои наиболее выгодные варианты действий по принципу: на каждом шаге каждая сторона отвечает на очередной ход другой стороны тем своим вариантом действий, который явля

ется оптимальным относительно всех предыдущих ходов другой стороны, рассматриваемых как некая смешанная стратегия, в которую варианты действий входят в пропорциях, определяемых частотой их применения. Эксперименты, вьтолненные на ЭВМ, показывают, что такой способ обладает хорошей сходимостью, т.е. при достаточно большой последовательности партий средние выигрыши сторон н а одну партию стремятся к значениям игры (д и ц соответственно).

Критерий окончания итерационного процесса решения биматричной игры, основывается на следующем свойстве оптимальных стратегий: если одна из строн придерживается оптимальной стратегии х(у), то выигрыш остается не изменным и равным 5д(5) независимо от того, что делает другая сторона, если только она не вьпсодит за пределы своих активных стратегий, т.е. стратегий, вероятность применения ко торых больше нуля. Следовательно, совпадение на какой-либо (h) итерации верхнего и нижнего среднего значения- партии игры для одной из сторон (например, й дК означает, что на данной итерации получено точное значение игры 5д д тороны А и точные значения вероятностей в оптимальной смешанной стратегии 3 (уТ ) стороны В. Такое совпадение является признаком достижения ситуации равновесия, когда любое поведение стороны В дает стороне А один и тот же выигрьш, а именно цену игры 9д . Аналогичная ситуация равновесия имеет место и для другой стороны. Для получения приближенного решения биматричной игры с заданной точностью целесообразно, ограничившись заданным числом итераций li, ориентироваться на вьшолнение системы неравенств:

ч(Ь ,Ch) А .

.: А А В 2

(J) (2)

где ялые действительные числа.

Выполнение неравенства (О определяет, номер итерации , приближенное значение игры J д для стороны А:

ГиЛ (1

--SI л

s. j ---с точностью

А Г2

и приближенно оптимальную смешанную стратeriflo Sg стороны В:

с, r, f t (« CH Г (НдЛ (У, У7 )yj ) ,

м ryf ,

где у. , ,-...,п.

Н.

Jbl

1 - если на Ь-й итерации стороГ- { на В использовала стратегию О-в противном случае.

Аналогичным образом, выполнение неравенства (2) определяет номер итерации , приближенное значение игры для стороны В:

.„ , ,( -(Мв) ч(в1

/,1- (,S с точностью до в I о

и приближенно оптимальную смешанную стратегию S. стороны А:

-

5 д(Н«1( («1 J«b1 :з:Од ул jJv

i-1 ,... ,m,

2 j.

где X.

. )

(L н:

1 1,... ,т,

.

1, если на h-й итерации сторона А использовала стратегию AJ ; О-в противном случае.

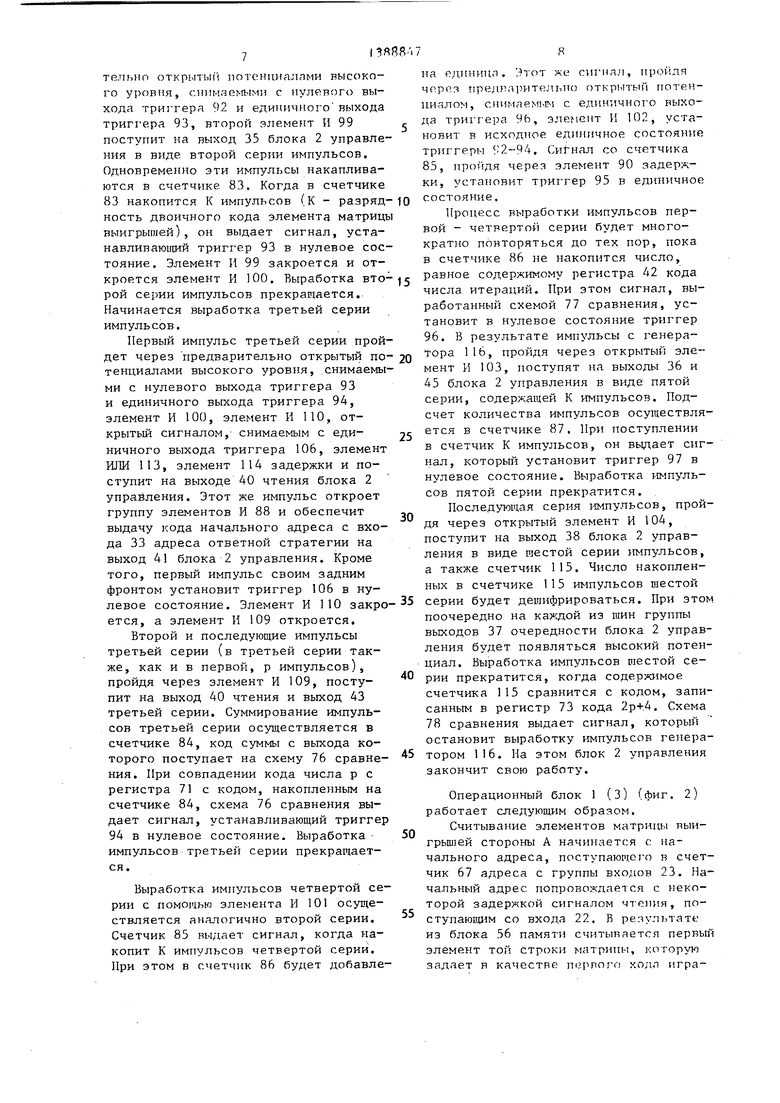

Рассмотрим итерационный алгоритм на следующем примере. Пусть биматричная игра задана матри- цами выигрьшей сторон I/AI и ИвИ:

Матрица //АИ Матрица //В//

А, AJ 7 2 Г 9

А, А.

В«

3

8

В

9

1

Количество ходов (4исло итераций) ограничено , Первый ход делает сторона А выбором первой стратегии действий А,.

Расчетная схема алгоритма этой игры приведена в табл. 1.

На первый ход стороны А (стратегия А,) сторона В отвечает стратегией Ъ,, приносящей ей максимальный выигрыш (1-я строка матрицы |/В//). В ответ сторона А выбирает стратегию А, также дающую ей максимальный выигрыш (2-я строка матрицы 11АII. Значения выигрьш1ей сторон заносятся в

.5

соответствуюрдае колонки первой строки табл. 1.

На второй лход стороны А (стратегия А2) сторона В выбирает по матрице //В// ту из своих стратегий, которая обеспечивает ей максимальный суммарный выигрыш за первый и второй ход. Такой стратегией является В,. В ответ на стратегию В сто- рона А по матрице |/А|/ выбирает стратегию A,j. ВЗ, 4, 6 и 7 колонки второй строки табл. 1 записываются суммарные выигрьши за первый и второй ходы. Аналогичным образом определяются стратегии игры и величины выигрышей во всех десяти ходах. Максимальные накопленные выигрьшш сторон для каждого хода партии обведены кружками. Макс и мин цены игры каждой стороны для конкретного хода определяются в результате деления значения макс и мин накопленных сумм выигрышей сторон на этом ходу на порядковый номер этого хода. По макс и мин ценам определяются средние значения цены игры сторон. При средняя цена игры равна 4,7 для стороны В и 5,2 - для стороны А. Подсчитав число используемых стратегий, записанных во второй и пятой колонках табл. 1, можно оценить частоту использования той или иной стратегии в игре.

В исходном состоянии обнулены бло 56 памяти, счетчик 57, накапливающие С5гмматоры 60 и 67, регистры 70-73, счетчики 82-87, 115, сдвигающий регистр 122. Триггеры 91-97, 105 и 106 находятся в единичном состоянии.

1

Работа устройства начинается с того, что в блок 56 памяти операционного блока 1 по группе информационных входов 6 записываются последовательно элементы матрицы выигрышей стороны А. При этом адреса, по которым записываются элементы матрицы, поступают по группе адресных входов 5. Каждый элемент сопровождается сигналом записи, поступающим по входу 7 записи. Всего в узел 56 памяти записывается Р-Р элементов.

Аналогично осуществляется запись в блок памяти операционного блока 3 элементов матршц. выигрышей стороны В.

В регистры 70 кода исходной стра- тегии, кода р-7, кода числа итераций 72 и кода (2р+4)-73 блока 2 управления по соответствующим группам вхо

ю

888476

дов 8, 9, 11 и 12 производится запись управляющих кодов.

Работа устройства начинается по сигналу пуска, поступающему по входу 10. По этому сигналу запускается генератор 116, который начинает вырабатывать серии управляющих импульсов. Первая серия импульсов, выдаваемая с выхода 34 блока 2 управления, вызывает считывание строки из р элементов матрицы выигрьппей стороны А из блока 56 памяти операционного блока 1. Вторая серия импульсов, выдаваемая с выхода 35 блока 2 управления, обеспечивает работу блока 61 сравнения на максимуг-.

Блок 2 управления работает следую15

щим образом.

0

5

0

5

Импульсы, вырабатываемые генератором I16 импульсов, поступают на один из входов элементов И 98-104.

Первый импульс, первой серии, пройдя через предварительно открытые потенциалами с единичных выходов триггера 92 и триггера 105 элементы И 98 и 108, через элемент ИЛИ 112 и элемент 111 задержки поступит на выход 31 блока 2 управления как сигнал чтения. Этот же импульс откроет подготовленную к открытию потенциалом с единичного выхода через группу элементов ИЛИ 81 на группу выходов 32 начального адреса кода с регистра 70 кода ис- с ходной стратегии, преобразованного в код начального адреса. Преобразование кода осуществляется в преобразователе- 74 кода. Первый импульс своим задним фронтом установит в нулевое состояние триггеры 91 и 105.

Второй и последующие импульсы первой серии (всего в первой серии р импульсов по числу элементов в строке матрицы выигрьшей), пройдя через элемент И 98, элемент И 107, поступит на выход 34 блока 2 управления и выход 31 чтения. Все импульсы первой серии поступают на вход счетчика 82, где осуществляется их подсчет.

Когда в первом счетчике накопится р импульсов, сработает схема 75 сравнения, которая выдает сигнал - устанавливающий триггер 92 в нулевое состояние. В результате элемент И 98 закроется, а элемент И 99 будет открыт. Выработка импульсов первой серии прекратится.

Очередная серия импульсов с генератора 116 пройдет через предвари0

0

7

открытыГ( потснииаллми высокого уровня, cnjit-iaeNfbiMn с пулевого выхода триггера 92 и единичного выхода триггера 93, второй элемент И 99 поступит на выход 35 блока 2 управления в виде, второй серии импульсов. Одновременно эти импульсы накапливаются в счетчике 83. Когда в счетчике 83 накопится К импульсов (К - разряд- ность двоичного кода элемента матрицы выигрышей), он выдает сигнал, уста- навливаю1гсий триггер 93 в нулевое состояние. Элемент И 99 закроется и откроется элемент И 100. Выработка второй серии импульсов прекращается. Начинается выработка третьей серии импульсов.

Первый импульс третьей серии пройдет через предварительно открытый по- тенциалами высокого уровня, снимаемыми с нулевого выхода триггера 93 и единичного выхода триггера 94, элемент И 100, элемент И 110, открытый сигналом, снимаемым с еди- ничного выхода триггера 106, элемент ИЛИ 113, элемент 114 задержки и поступит на выходе 40 чтения блока 2 управления. Этот же импульс откроет группу элементов И 88 и обеспечит выдачу кода начального адреса с входа 33 адреса ответной стратегии на выход 41 блока 2 управления. Кроме того, первый импульс своим задним фронтом установит триггер 106 в нулевое состояние. Элемент И ПО закроется, а элемент И 109 откроется.

Второй и последующие импульсы третьей серии (в третьей серии также, как и в первой, р импульсов), пройдя через элемент И 109, поступит на выход 40 чтения и выход 43 третьей серии. Суммирование импульсов третьей серии осуществляется в счетчике 84, код суммы с выхода которого поступает на схему 76 сравне- ния. При совпадении кода числа р с регистра 71 с кодом, накопленным на счетчике 84, схема 76 сравнения выдает сигнал, устанавливающий триггер 94 в нулевое состояние. Выработка импульсов третьей серии прекращается.

Выработка импульсов четвертой серии с помощью элемента И 101 осул;е- ствляется аналогично второй серии. Счетчик 85 выдает сигнал, когда накопит К импульсов четвертой серии. При этом в счетчик 86 будет добавле

ас ее- Ю ы

- 20 25т ,,. о

50

40

55

78

на единица. Этот же сигнал, пройдя через Г1ред трите.;11,1то открытый потен- пиалом, снимаемы с единичного выхода триггера 96, элемент И 102, установит в исходное единичное состояние триггеры 92-94. Сигнал со счетчика 85, пройдя через элемент 90 задержки, установит триггер 95 в единичное состояние.

Процесс выработки импульсов первой - четвертой серии будет многократно повторяться до тех пор, пока в счетчике 86 не накопится число, равное содержимому регистра 42 кода числа итераций. При этом сигнал, выработанный схемой 77 сравнения, установит в нулевое состояние триггер 96. В результате импульсы с генератора 116, пройдя через открытый элемент И 103, поступят на выходы 36 и 45 блока 2 управления в виде пятой серии, содержащей К импульсов. Подсчет количества импульсов осуществляется в счетчике 87. При поступлении в счетчик К импульсов, он выдает сигнал, который установит триггер 97 в нулевое состояние. Выработка импульсов пятой серии прекратится. ,

Последующая серия импульсов, пройдя через открытый элемент И 104, поступит на выход 38 блока 2 управления в виде шестой серии импульсов, а также счетчик 115. Число накопленных в счетчике 115 импульсов шестой серии будет дешифрироваться. При этом поочередно на каждой из шин группы выходов 37 очередности блока 2 управления будет появляться высокий потенциал. Выработка импульсов шестой серии прекратится, когда содержимое счетчика 115 сравнится с кодом, запи- санньш в регистр 73 кода 2р+4. Схема 78 сравнения выдает сигнал, который остановит выработку импульсов генератором 116. Па этом блок 2 управления закончит свою работу.

Операционный блок 1 (З) (фиг. 2) работает следующим образом.

Считывание элементов матрицы пыи- грьш1ей стороны А начинается с начального адреса, поступаюр;его в счетчик 67 адреса с группы входов 23. Начальный адрес попровождается с некоторой задержкой сигналом чтения, поступающим со входа 22. В результате из блока 56 памяти считывается первый элемент той строки матрипы, которую задает в качестве первого ходл играющий (код исходной стратегии записан в регистре 70 блока управления).

Код из счетчика 57 адреса одновременно с выдачей в блок 56 памяти поступает на дешифратор 58. На первом выходе дешифратора появляется высокий потенциал, открывающий первую группу элементов Д 59. Считанный из блока 56 памяти элемент строки матрицы выигрьшей записывается в первый накапливающий с:/ммат6р 60,

Далее, второй импульс первой серии, поступающей по входу 25, увеличивает содержимое счетчика 57 адре- са на единицу. По этому адресу из блока 56 памяти считывается второй элемент, который через предварительно открытзда потенциалом с второго выхода дешифратора 58 группу элемен- тов И 59, запишется во второй накапливающий сумматор 60. Аналогично будут считаны всё р элементов матрицы выигрышей и записаны в накапливающие сумматоры. По второй серии импульсов поступающей в операционный блок 1(3) по входу 26, блок 61 сравнения на максимум осуществит выделение максимального из записанных в накапливгио- щих сумматорах элемента матрицы выигрьшей . -Блок 61 сравнениязаканчивает свою работу после выдачи на его тактовый вход последнего (К-го) импульса второй серии При этом на соответствующей группе выходов блока 61 сравнения будет установлен код максимального элемента, остальные группы выходов будут обнулены.

Код максимального элемента на соответствующем преобразователе 62 кода будет преобразован в код адреса ответной стратегии, который через группу элементов ИЛИ 63 поступит на группу выходов 24 операционного блока 2(3) и далее через блок 2 управления в операционный блок 3(1) устройства на счетчик 57 адреса в качестве начального адреса ответной стратегии.

Этот же код поступает на вход соответствующего элемента ИЛИ 66. В результате в один из накапливающих сумматоров 67 добавляется единица. Так ведется подсчет количества использования каждой из стратегий стороны А.

Аналогично описанному работает операционньй блок 3. При этом в качестве начального адреса в счетчик

0 5

0

5

0

0

5

57 адреса по группе входов 23 из блока 2 управления заносится адрес ответной стратегии, сформиро.ванньш в операционном блоке 1. Управление работой операционного блока 3 осуществляется третьей и четвертой сериями импульсов, вырабатываемыми блоком управления.

Операционньй блок 3 формирует адрес ответной стратегии, который с группы вьпсодов 24 через блок 2 управления по группе входов 23 операционного блока 1 заносится в счетчик 57 адреса. Процесс выборки элементов соответствующей строки матрицы выигрьш1ей из блока 56 памяти повторяется.

В накапливающих сумматорах 60 к значениям, накопленным на предыдущих циклах работы операционного блока 1, добавляются элементы, считанных из блока 56 памяти В данном цикле работы.

Процесс поочередной работы первого и второго операционных блоков 1 и 3 повторяется Н раз, где Н - число итераций, задаваемь1х в регистре 72 кода числа итераций.

По завершении Н циклов работы операционных блоков 1(3), блок управления вырабатывает пятую серию имйуль- сов, которая одновременно поступает по входам 27 на оба операционных блока. Эта серия, состоящая, из К импульсов, управляет работой блока 64 сравнения на максимум и блока 65 сравнения на минимум обоих операционных блоков 1 и 3 и обеспечивает выделение соответственно максимального и минимального кодов чисел, накопленных в накапливающих сумматорах 60, Значения максимального и минимального кодов с соответствующих групп выходов обоих блоков 64 и 65 сравнения через группы элементов ИЛИ 68 и 69 выдаются на группы выходов 29 и 30 максимального и минимального вьт- грьш1ей обоих операционных блоков.

На группы выходов 28 количеств использования страт.егий каждого из . операционных блоков 1 и 3 накапливающих сумматоров 67 вьщаются накопленные коды чисел. На этом работа операционных блоков заканчивается.

Блок 4 вычисления результатов работает следующим образом.

Потенциалы высокого уровня, поступающие из блока 2 управления по

одной из цепей группы входов 49 в блок 4 вычисления результатов, поочередно будут открывать одну из групп элементов. Тем самым обеспечивается поочередная запись через группу элементов ИЛИ 119 в блок 120 деления кодов чисел с групп входов 46-48 и 52-54 блока 4 вычисления результатов По первой группе входных информационных цепей в блок 120 деления заносится очередное делимое, а по второй группе - делитель. Код делителя поступает из блока управления в блок вычисления результатов по группе входов 51 числа итераций. Запуск блока 120 деления, вьшолнение одной операции деления и формирование одного результата осуществляется по каждому из импульсов шестой серии, поступающей из блока 2 управления в блок 4 вычисления результатов по входу 50.

Очередной импульс шестой серии пройдет через элемент 121 задержки, поступит на вход опроса блока 120 деления и запустит его. Операция деления будет вьшолнена над делимым и делителем, записанными в блок деления , ,

Код результата вьщается на все группы элементов И 123, Тот же нм- пульс осуществит сдвиг единицы, записанной в сдвигающем регистре 122, Код. результата пройдет через открытую группу элементов И 123 и поступит на одну из группы выходов 16-21 устройства. Аналогично импульсами шестой серии будут опрошены все группы элементов И 118,соответствующие результаты обработаны блоком 120 деления и выданы через группы элементов И 123 на выходы 16-21-устройства На этом работа блока 4 вычисления результатов и соответственно всего устройства закончится.

Формула изобретения

Устройство для моделирования би- матричных игр, содержащее блок памяти, блок з равления и группу накап- ливающих сумматоров, о т л и ч а- ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет решения биматричных игр с ненулевой суммой выигрьшей сторон,

в него введены второй блок памяти, два счетчика, вторая группа накапливающих сумматоров, четыре блока .

0

5

0

5

0

5

0 5

выбора максимального кода, два блока выбора минимального кода, два ключа, две группы счетчиков, мультиплексор, блок деления и коммутатор, причем входы начальной загрузки блоков памяти являются одноименными входами устройства, вход установки первого счетчика является входом задания начальной стратегии устройства, выход первого счетчика подключен к адресному входу первого блока памяти, К-й информационный вьпсод которого (,,,,,р, где р - количество ответных стратегий первого участника в каждом ходе биматричной игры) подключен к входу слагаемого К-го накапливающего сумматора первой группы, выход которого подключен к К-м информационным входам первого блока выбора минимального кода, первого блока выбора максимального кода и второго блока выбора максимального кода, К-й разряд выхода позиционного кода максимального числа подключен к рующему входу К-го счетчика первой группы, выход которого подключен к информационному входу первой группы мультиплексора, информационный выход второго блока выбора максимального кода подключен к информационному входу первого ключа, выход которого подключен к информационному входу второго счетчика, выход которого подключен к адресному входу второго блока памяти, М-й информационный выход которого (,.,,,Т, где Т - количество ответных стратегий второго участника в каждом ходе биматричной игры) подключен к входу слагаемого М-го накапливающего сумматора второй группы, выход которого подключен к М-м входам третьего блока выбора максимального кода, второго блока выбора минимального кода и четвертого блока выбора максимального кода, М-й информационный выход которого подключен к суммирующему входу , М-го счетчика, информационный выход которого подключен к М-му информационному входу второй группы мультиплексора, информационный выход четвертого блока выбора максимального кода подключен к информационному входу второго КЛЮЧ9, выход которого подключен к информа ционному входу первого счетчика, выходы первого блока выбора максимального кода, первого блока выбора минимального кода, тре

тьего блока выборл максимального кода и нторого блока выбора минимально го кодя подключени соответственно с первого по четвертый информационным входам мультиплексора, выход которого подключен к входу делимого блока делен1- я, вход задания количества итераций устройства является одноименным входом блока управления, выход за Дания номера итерации которого подключен к входу делителя блока деления, выход которого подключен к информационному входу коммутатора, с первого по четвертый информационные выходы которого являются соответственно выходом устройства максимальной цены игры первого участника, выходом устройства минимальной цены игры первого участника, вьтходом устройства максимальной цены игры второго участника и выходом устройства минимальной цены игры второго участника, К-й информационный выход первой группы является выходом устройства вероятности К-й стратегии-первого участника, М-й информационный выход второй группы является выходом устройства вероятности М-й стратегии устройства, с первого по девятнадцатый выходы синхронизации блока управления подключены соответственно к входам признаков чтения первого и второго блоков памяти, к входам признаков записи пер

4714

ног о и второго счетчиков, к управляющим входам первого и второг о ключей, к входам опроса первого и вто5

ю с рого блоков выбора минимального кода, к входам опроса второго и четвертого блоков выбора максимального кода, к входам опроса с первого по четвертый информационных входов мультиплексора, к входу опроса блока деления и к входам опроса с первого по четвертый информационных выходов коммутатора, К-е выходы синхронизации первой и второй группы блока управления подключены к входу опроса К-го информационного входа первой группы мультиплексора и к входу опроса К-го информационного выхода первой группы коммутатора соответственно, К-е выходы синхронизации- третьей и четвертой групп блока управления подключены к входу опроса М-го информационного входа второй группы мультиплексора и к входу опроса М-го информационного выхода второй группы коммутатора соответственно, вход опроса первого блока выбора минимального кода соединен с входом опроса первого блока выбора максимального кода, вход опроса второго блока выбора минимального кода соединен с входом опроса третьего блока выбора максимального кода.

20

5

0

Ц.1.

/7

0 Ф( /9

1 Г Г г 1 г F

23 V

ill Ш iJtri HS

...Т Т ...т 1

re/7

ff

.ffrs

го

//

Авторы

Даты

1988-04-15—Публикация

1986-09-16—Подача