Изобретение относится к автоматике и вычислительной технике и может найти применение в распределенных системах программного управления, программируемых контроллерах, станках с числовым программным управлением, АСУ технологическими процессами.

Известно устройство для программного управления, содержащее блок набора программ, задатчик длительности временного интервала, генератор импульсов, три чика,. блок задержки, регистр сдвига, блок элементов И, формирователь импульсов.

Недостатком устройства является сложность модификации программ при изменении функций системы управления. Кроме того, устройство не позволяет выдавать команды управления одновременно по нескольким каналам, что снижает его производительность, а следовательно, ограничивает область применения.

Известно устройство для программного управления, содержащее запоминающий блок, процессор, селекторы - демультип- лексоры, дешифратор, счетчик, генератор импульсов, блок формирования выходных сигналов, блок элементов И.

Недостатком устройства является ограниченная область его применения, обусловленная сложностью модификации программы управления при расширении функций управления и низкой помехоустойчивостью. Отсутствие возможности работы устройства с несколькими объектами управления снижает производительность системы, приводит к увеличению потребного

ч Ю

Nj О

ю о

объема памяти, что также ограничивает область применения устройства.

Известен программируемый контроллер, содержащий блок памяти, регистр адреса, выходные регистры, демультиплек- соры, генератор импульсов, блок элементов И, элементы И, ИЛИ.

Недостатком контроллера является избыточность блока памяти, что снижает его функциональную надежность.

Известна система для программного управления, содержащая каналы, а в каждом канале - блок памяти, блок проверки условий, регистр адреса, два триггера, два элемента ИЛИ, элемент НЕ.

В известной системе взаимодействие между каналами организованы, виде команд передачи управления в одном направлении, что ограничивает класс обменных взаимодействий и увеличивает класс обменных взаимодействий и увеличивает время взаимодействия. Кроме того, недостатком системы является ограниченная область ее применения в структурах конвейерного типа и отсутствие возможности применения в матричных структурах программного управления. Отмеченные недостатки ограничивают область целесообразного применения,

Известна распределенная система для программного управления, содержащая каналы, блок памяти, шину данных, шину адреса, шину управления, блок элементов ИЛИ.

Недостатком известной системы является ограниченная пропускная способность, обусловленная строго последовательным режимом работы отдельных каналов. Кроме того, недостатком известного устройства является ограниченное число обменных взаимодействий в системе, построенной по модульному принципу отдель- ных каналов, что ограничивает функциональные возможности, а следовательно, и область целесообразного, применения.

Наиболее близким по технической сущности и достигаемому положительному эффекту к предлагаемому решению является распределенная система для программного управления технологическими процессами, содержащая n x m каналов, где n m- a n - число каналов в строке матричной организации системы, m - число строк, причем i-й канал (I 1,n ) системы содержит блок памяти программ, коммутатор адреса, ре- гистр адреса, регистр команд, мультиплексор логических условий, блок синхронизации, блок элементов И, элемент И, причем первый управляющий выход ко0

торого соединен с синхронизирующим входом регистра адреса, выход которого соединен со входом блока памяти программ, выход блока памяти программ соединен с

информационным входом регистра команд, синхронизирующий вход которого соединен со вторым входом блока синхронизации, выход поля проверяемых логических условий регистра команд соединен с первым информационным входом мультиплексора логических условий, выход модифицируемого разряда адреса регистра команд соединен со вторым информационным входом мультиплексором логических

5 условий, выход которого соединен со входом модифицируемого разряда адреса первого информационного входа коммутатора адреса, выход которого соединен с информационным входом регистра адреса, вход логических условий канала соединен с управляющим мультиплексора логических условий, выход поля немодифицируемых разрядов адреса регистра команд соединен со входами немодифицируемых разрядов

5 адреса первого информационного входа . коммутатора адреса, выход операционного поля регистра команд соединен с информационным входом блока элементов И, выход которого соединен с первым информационным выходом канала, выход поля конца программы регистра команд соединен с прямыми инверсным управляющими входами коммутатора адреса и вторым входом блока синхронизации, второй управляющий

5 вход канала соединен с третьим входом блока синхронизации, второй информацион- ный выход К-го (К 1, п-1) канала v-й ( v 1,m) строки каналов соединен со вторым информационным входом (К+1)-го канала v - и строки, второй информационный выход п-го канала v строки соединен со вторым информационным входом первого канала V- й строки, каждый канал содержит буферный запоминающий блок сообщений, блок ана5 лиза, второй блок элементов И, причем информационный выход буферного запоминающего блока соединен со вторым информационным входом коммутатора адреса, выход операционного поля регистра команд соединен с информационным входом второго блока элементов И, выход кото рого и выход элемента И соединены с первым входом блока анализа, управляющий выход которого соединен с управляю5 щим входом буферного запоминающего, блока сообщений, управляющий выход которого соединен с четвертым входом блока синхронизации, третий выход которого соединен с первым входом элемента И, выход

0

0 й

0

поля передачи управления регистра команд соединен с инверсным управляющим входом первого блока элементов И, прямым управляющим входом второго блока элементов И и вторым входом элемента И, первый информационный выход блока анализа соединен с первым информационным входом буферного запоминающего блока сообщений, выход поля конца программы регистра команд соединен со вторым управляющим входом буферного запоминающего блока сообщений, первый информационный вход канала соединен со вторым ин- формационным входом . буферного запоминающего блока, второй информационный вход канала соединен со вторым входом блока анализа, второй информационный выход которого соединен со вторым информационным выходом канала, третий информационный вход канала соединен с третьим входом блока анализа, третий информационный выход которого соединен с третьим информационным выходом канала, третий информационный выход j-ro 0 ггТГТ) fi -го столбца (/г 1, п) каналов соединен с третьим информационным входом ()ro канала, третий информационный выход первого канала /л -го столбца каналов соединен с третьим информационным входом т-го канала соответствующего столбца каналов.

Недостатком известной распределенной системы является ограниченная об-, ласть ее применения, обусловленная отсутствием средств контроля, позволяющим осуществлять контроль передаваемой информации. Отсутствие средств контроля снижает достоверность функционирования распределенной системы для программного управления технологическими процессорами, : .

Целью изобретения является повышение достоверности передаваемой транзитной информации.

Поставленная цель достигается тем, что в распределенной системе для программного управления блок анализа дополнительно содержит блок памяти сигнатур, коммутатор, блок элементов суммы по модулю два, второй и третий элементы И, триггер управления.

: Сущность предлагаемого изобретения состоит в следующем:

Распределенная система для программного управления технологическими процессами состоит из множества однотипных каналов, объединенных в матричную структуру. Каждый отдельный канал системы уп- равления определенной группой

технологических процессов, образующих программный уровень управления. Множество программ управления, выполняемых каналом, состоит из двух подмножеств ко5 манд Mi и М2. Первый тип команд Mi предназначен непосредственно для управления соответствующим технологическим процессом.

Во время выполнения программы канал

0 может выдавать в одно из двух направлений команды второго типа М2, образующие команды обмена (передачи управления). Формат данной команды представляется в виде

5

М2 Кпр # Коп # So,

где КПр - номер (код) канала - приемника информации;

0 Коп - номер (код) программы, которую должен выполнить канал - приемник информации

S0 - код сигнатуры;

# - знак конкатенации (сцепления).

5 Каждому каналу входящему в состав распределенной системы, присваивается, номер (идентификатор), определяющий его местоположение в матрице каналов. Обмен командами передачи управления может

0 производиться между каналами системы либо по строке каналов (слева направо), либо, в столбце каналов (снизу вверх). Каналы, расположенные в одном столбце (строке) образуют кольцевую структуру. Поэтому ко5 манда обмена с (q, v)-ro канала (q. vЈ 1, n) поступает либо на{д+1, vj-й канал (движение по строке каналов, либо на (q, 1 -1}-й канал движения по столбцу каналов. Очевидно, при организации двойного конвейера пере0 мещения информации между каналами системы организация движения вертикаль - горизонталь тождественна движению горизонталь- вертикаль. Пусть движение информации в матрице каналов будет

5 организовано по принципу вертикаль - горизонталь. При такой дисциплине организации взаимодействия отдельных каналов характеристикой маршрута продвижения информации может служить некоторое чис0 ло (сигнатура).

При выдаче команды обмена сообщение дополняется из отдельного блока памяти сигнатурой, идентифицирующей путь прохождения информации между каналами.

5 При поступлении сообщения на соседний канал темы определяется, ему ли предназначена поступившая информация. Определение принадлежности информации происходит путем сравнения когда канала

приемника информации с кодом (идентификатором) канала. При несовпадении этих кодов поступившая информация отправляется к следующему каналу и т.д. до совпадения кодов либо в столбце, либо в строке каналов.

При совпадении одного из двух кодов меняется направление продолжения информации.

По мере транзитного прохождения информации код сигнатуры модифицируется идентификаторами (каналов и направлениями выдачи информации). При достижении канала - приемника информации сообщения полученная сигнатура должна быть нулевой - в противном случае пройденный маршрут не соответствует требуемому а следовательно, произошла ошибка в назначении поступившего на обслуживание сообщения (ошибка адреса). .

При совпадении адресной части сообщения с кодом - идентификатором канала и нулевой сигнатурой информации о коде программы управления заносится в буферный запоминающий блок для дальнейшего в соответствии е правилом: первый пришел - первый обслужен (организация типа F1FO). : . ;

Сущность изобретения реализуется путем введения следующей совокупности конструктивных признаков, обуславливающих соответствие заявленного технического решения критерию новизна.

Введение блока памяти сигнатур и обусловленных им связей обусловлено необходимостью задания кодов, определяющих однозначно путь прохождения команд обмена между каналами распределенной сис темы.

Введение блока элементов суммы по модулю два и обусловленных им связей необходимо для модификации кода сигнатуры номере прохождения команды обмена между транзитными каналами: системы.

Введение связей коммутатора .необходимо для коммутации кода сигнатуры либо от собственного канала, либо после модификации кода сигнатуры при передаче команды обмена транзитом от соседних каналов системы.

Введение (соединение) связей триггера управления необходимо для формирования признака неверного прохождения команды обмена (при ненулевой сигнатуре) по приходу команды обмена данному каналу.

Таким образом, предложенная распределенная система для программного управления технологическими процессами соответствует критерию существенные отличия, поскольку в известных технических

решениях 1-6 отсутствует указанная выше совокупность конструктивных признаков, что не позволяет организовать контроль прохождения команд обмена между каналами распределенной системы. Обеспечение за счет введения совокупности отличительных признаков контроля обмена информацией повышает достоверность обрабатываемой информации в раЪпреде0 ленной системе для программного управления технологическими процессами.

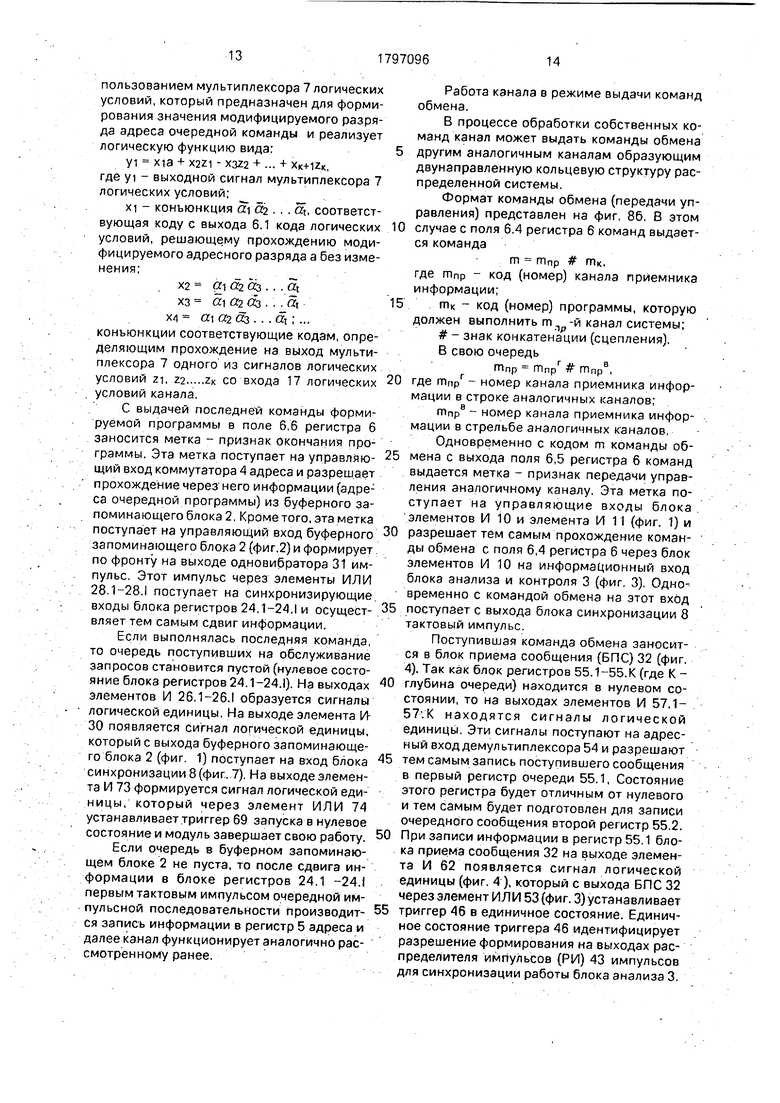

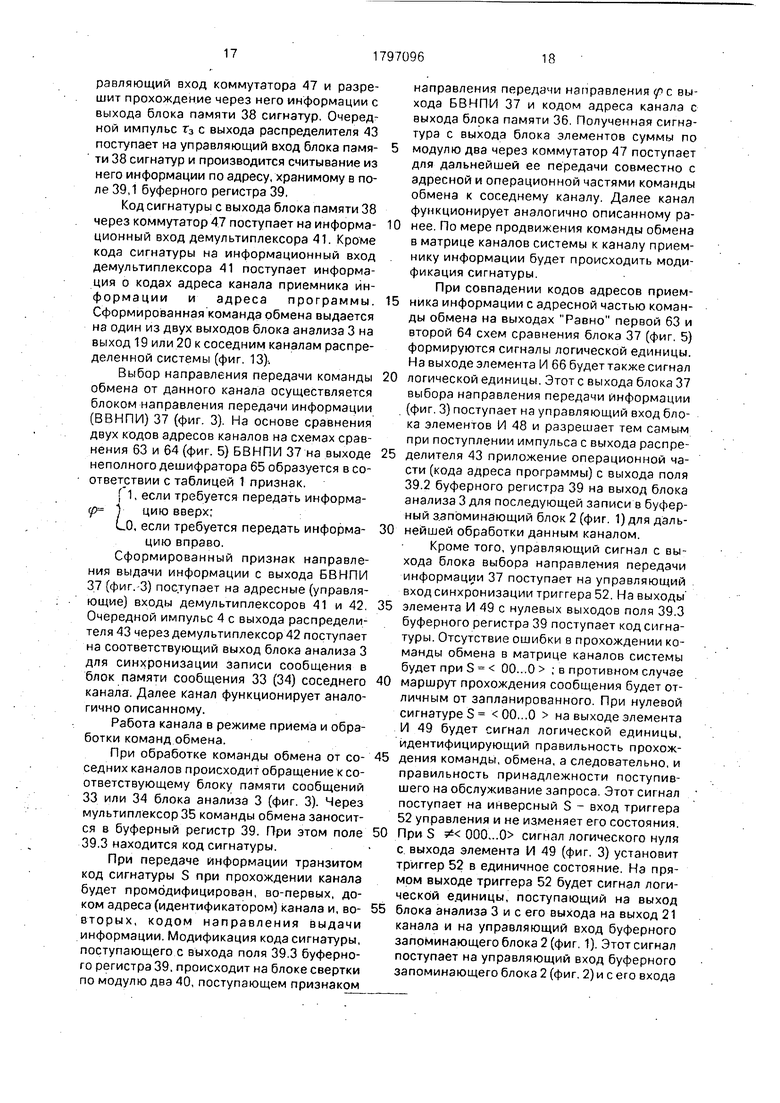

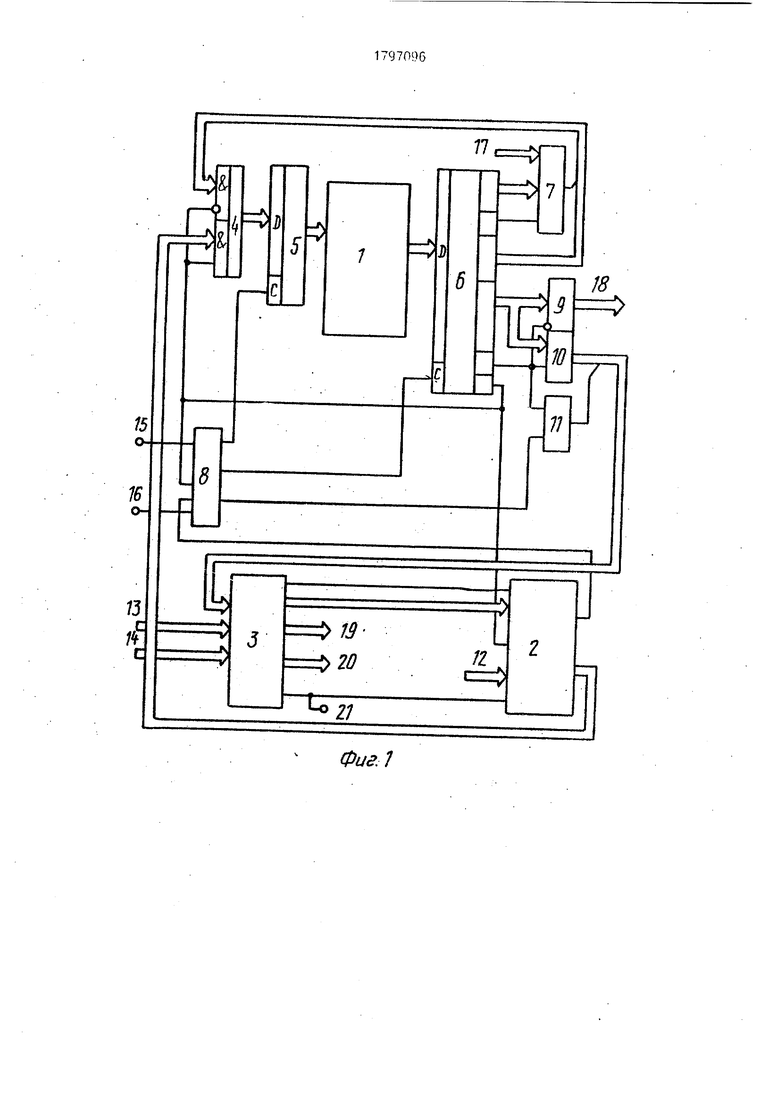

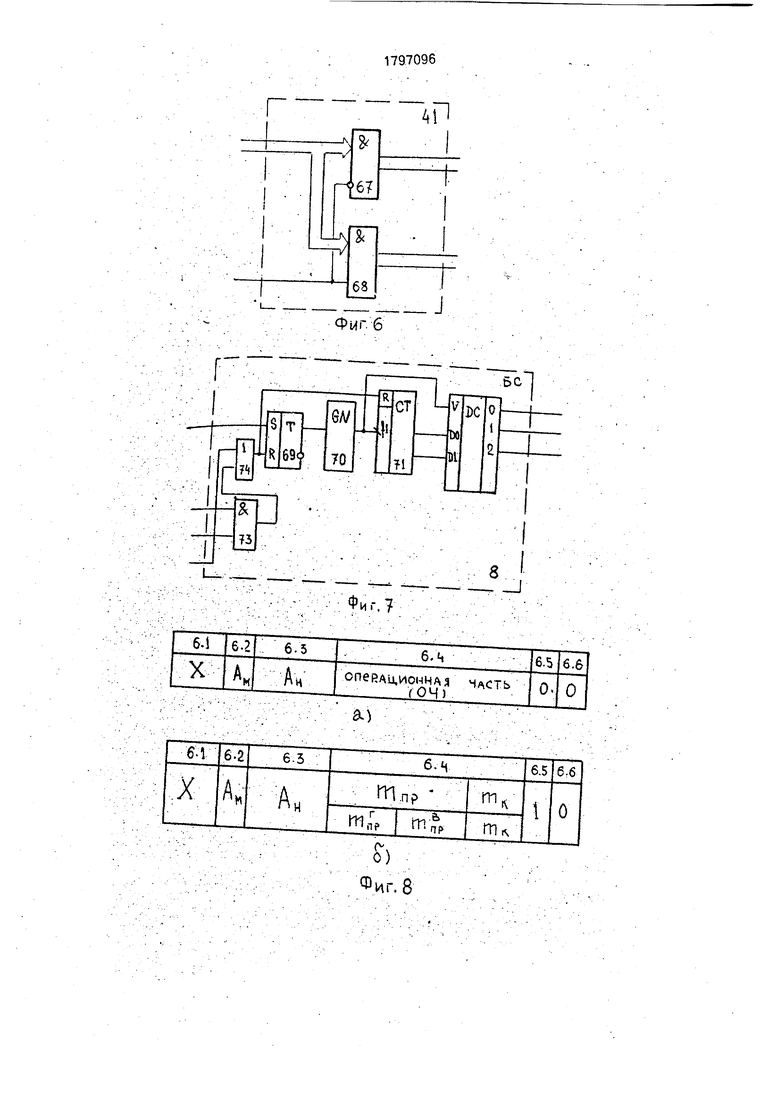

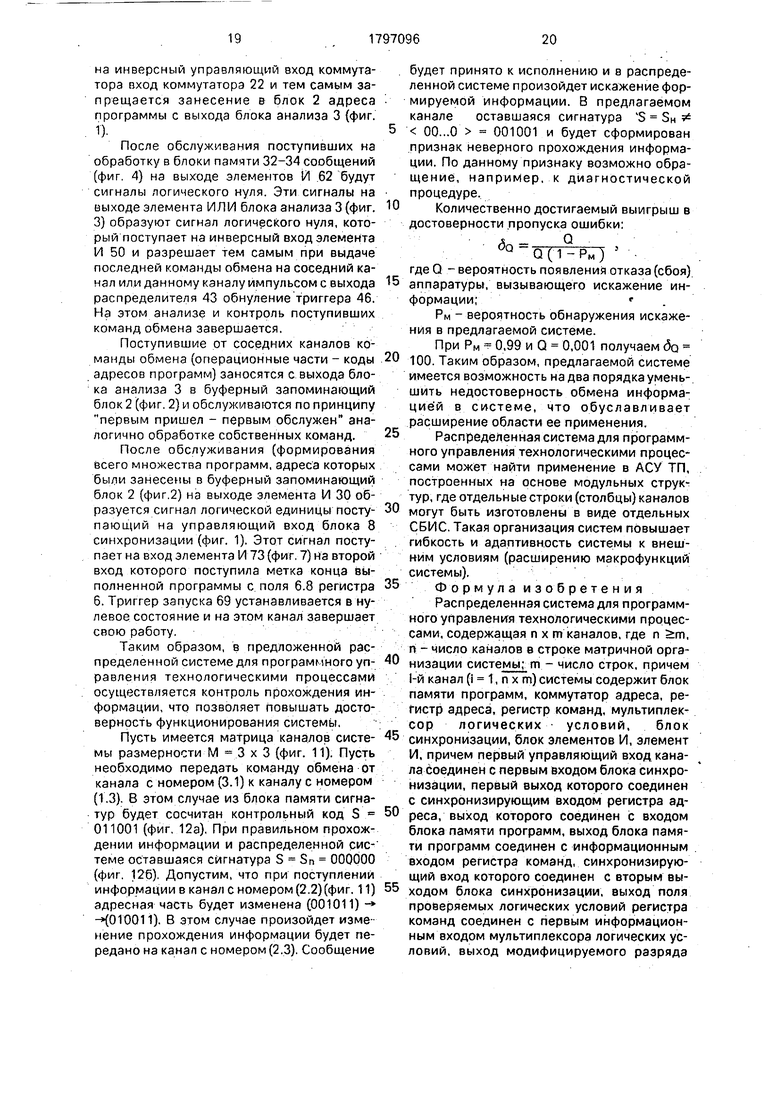

На фиг. 1 представлена функциональная схема 1-го (i Y, rfxTrh) канала распределенной системы для программного

5 управления технологическими процессами; на фиг. 2 - функциональная схема буферного запоминающего блока; на фиг. 3 - функциональная схема блока анализа; на фиг. 4

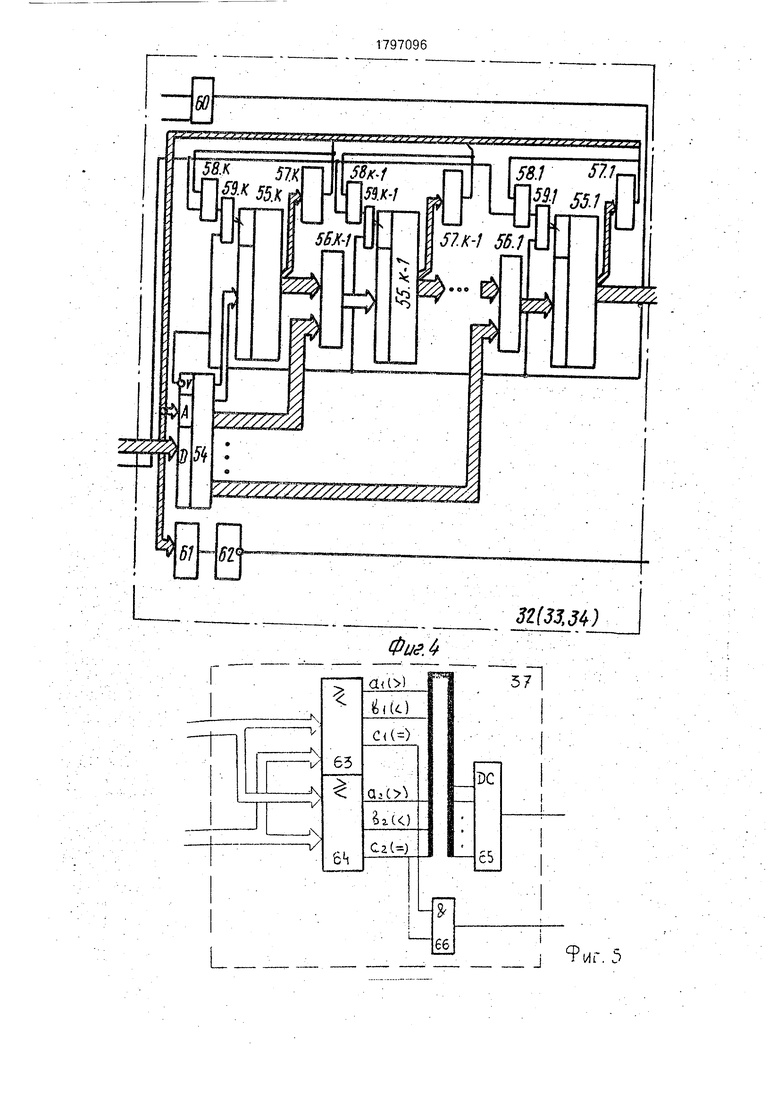

- функциональная .схема первого (второго, 0. третьего) .блока памяти сообщений; на фиг. 5 - функциональная схема блока выбора направления передачи информации; на фиг. 6

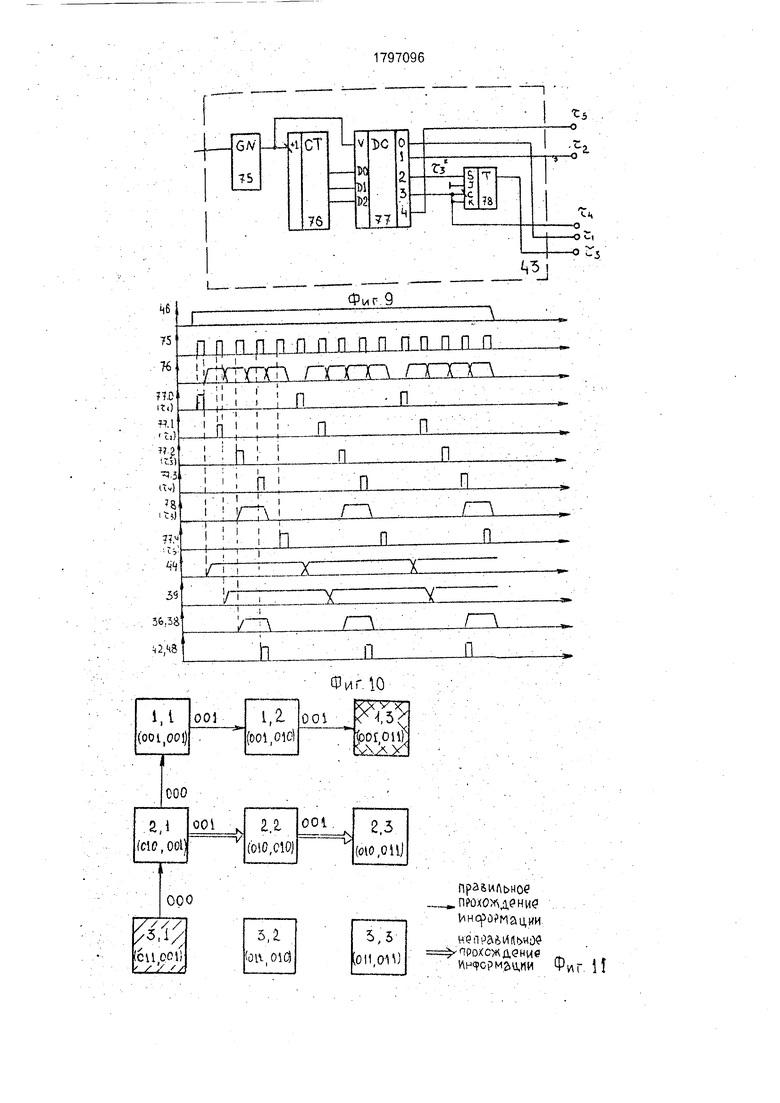

-функциональнаясхема выходногодемуль- типлексора; на фиг. 7 - функциональная схе5 ма блока синхронизации (БС); на фиг. 8 - формат команды а обработки, б обмена; на фиг. 9 - функциональная схема распределителя импульсов (РИ); на фиг. 10-временные диаграммы функционирования

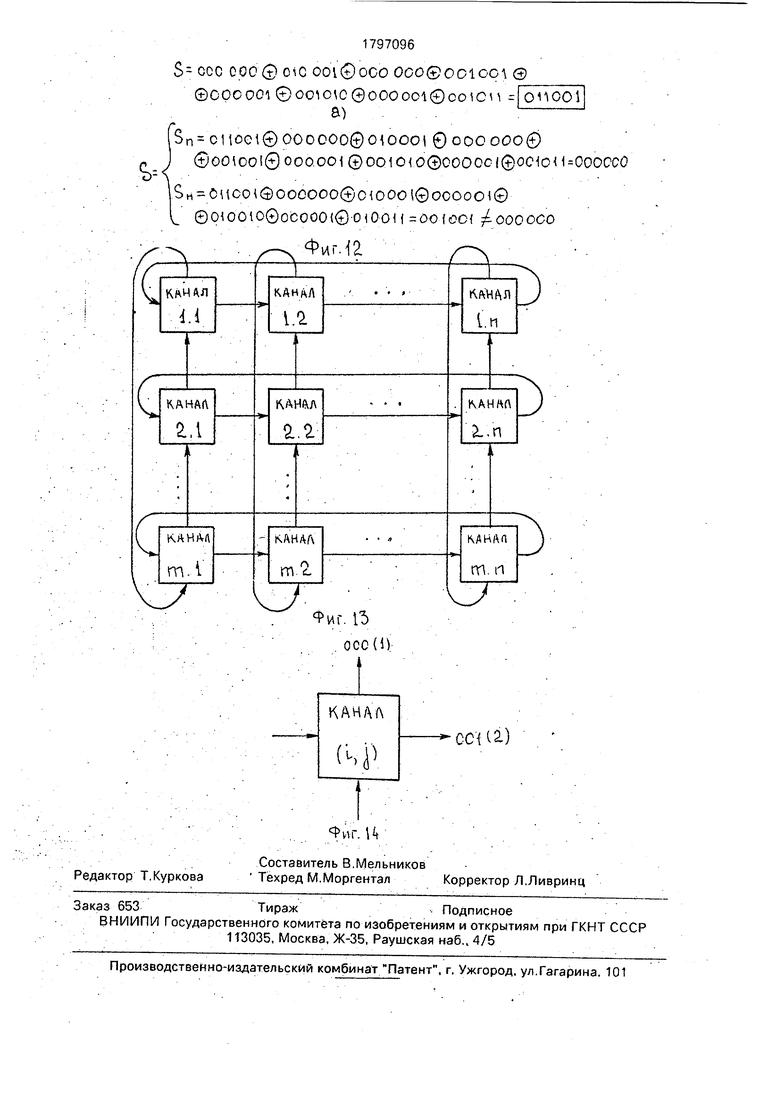

0 распределителя импульсов; на фиг. 11 - пример кодирования матрицы каналов распределительной системы размерности 3x3 и направлений передач сообщений (команд обмена) от канала (3, 1) к каналу (1; 3); на

5 фиг.12а - пример кода сигнатуры, хранимого в специальном блоке памяти и используемого при передаче команды обмена от команд (3, 1) к каналу (1. 3); на фиг. 126 - пример модификации кода сигнатуры при

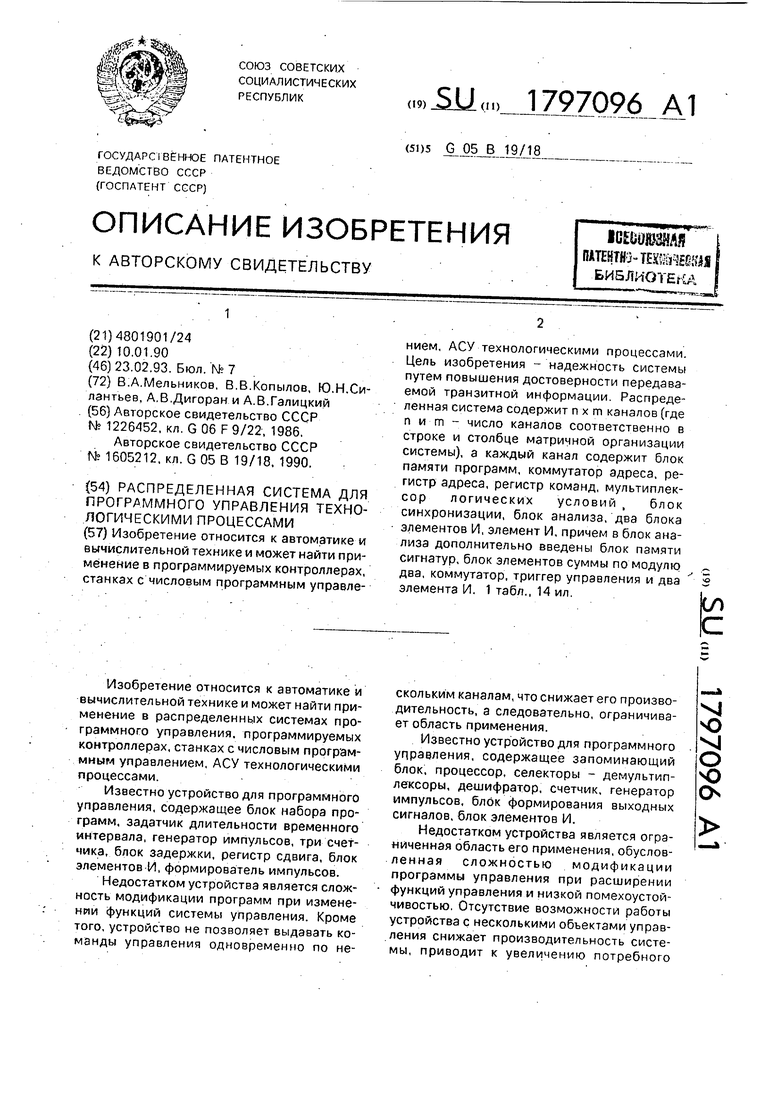

0 правильной (Sn) и неправильной (SM) передаче команды обмена; на фиг. 13 - пример организации распределенной системы размерности n x rn на однотипных каналах сис- темы; на фиг. 14 - пример кодирования

5 направлений передачи сообщения от (I, j)-ro канала.

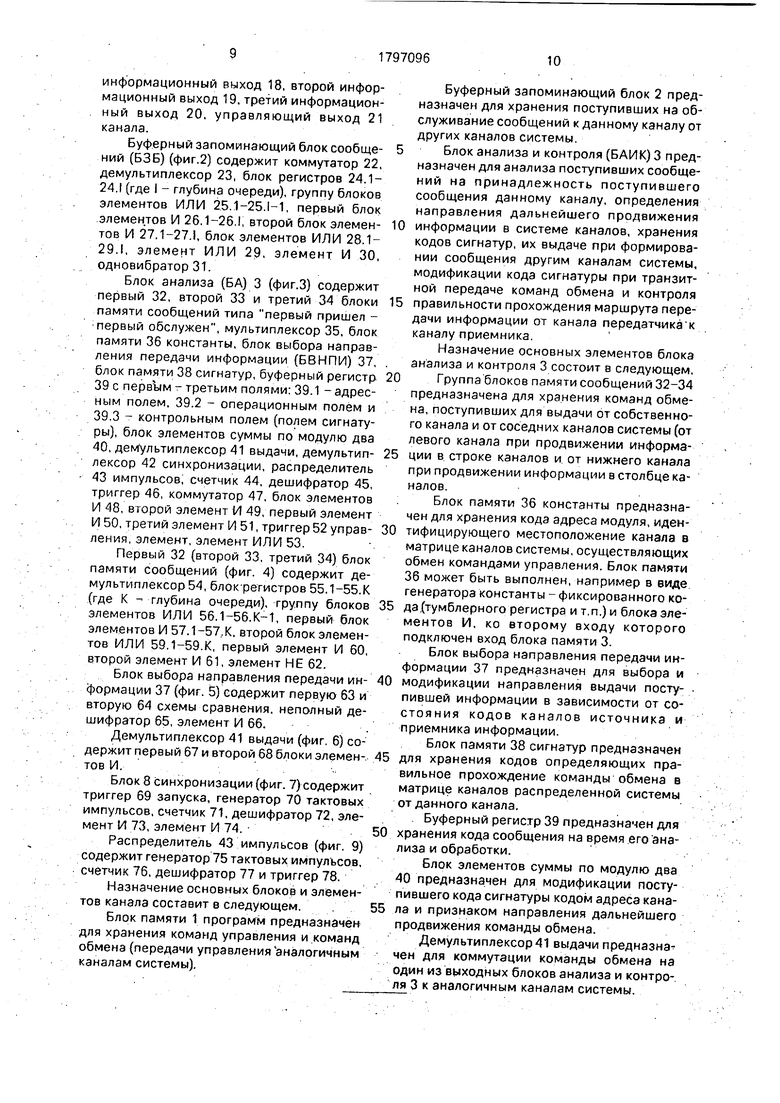

1-й канал распределенной системы для программного управления технологическими процессами (фиг.1) содержит блок памя0 ти 1 программ, буферный запоминающий блок (БЗБ) 2, блок анализа (БА) 3, коммутатор 4 адреса, регистр 5 адреса, регистр 6 . команд, мультиплексор 7 логических условий, блок синхронизации 8, первый блрк

5 элементов И 9, второй блок элементов И 10, элемент И 11. первый информационный вход 12. второй информационный вход 13, третий информационный вход 14, первый управляющий вход 15, второй управляющий вход 16, вход 17 логических условий, первый

информационный выход 18, второй информационный выход 19, третий информационный выход 20, управляющий выход 21 канала.

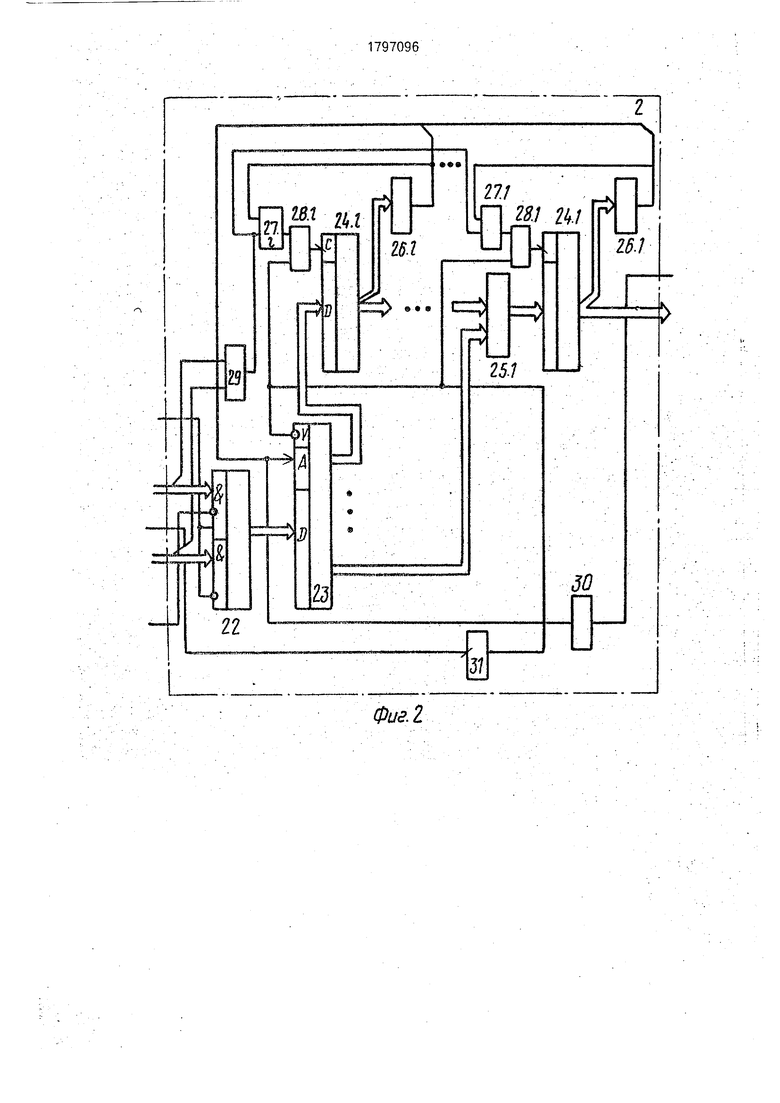

Буферный запоминающий блок сообщений (БЗБ) (фиг.2) содержит коммутатор 22, демультиплексор 23, блок регистров 24.1- 24.1 (где I - глубина очереди), группу блоков элементов ИЛИ 25.1-25.1-1, первый блок элементов И 26.1-26.1, второй блок элементов И 27.1-27.1, блок элементов ИЛИ 28.1- 29.1, элемент ИЛИ 29, элемент И 30, одновибратор 31.

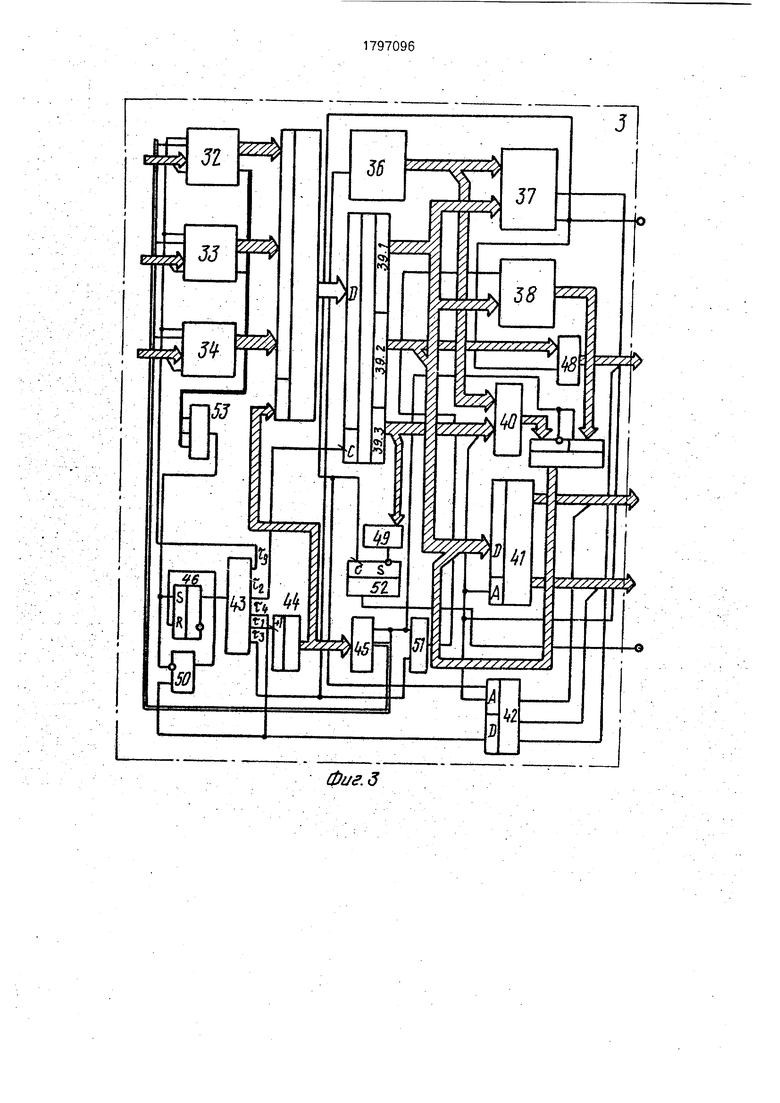

Блок анализа (БА) 3 (фиг.З) содержит первый 32, второй 33 и третий 34 блоки памяти сообщений типа первый пришел - :первый обслужен, мультиплексор 35, блок памяти 36 константы, блок выбора направления передачи информации (БВНПИ) 37, блок памяти 38 сигнатур, буферный регистр 39 с первом - третьим полями: 39.1 - адресным полем, 39.2 - операционным полем и 39.3 - контрольным полем (полем сигнатуры), блок элементов суммы по модулю два 40, демультиплексор 41 выдачи, демультиплексор 42 синхронизации, распределитель 43 импульсов; счетчик 44, дешифратор 45, триггер 46, коммутатор 47, блок элементов И 48, второй элемент И 49, первый элемент И 50, третий элемент И 51, триггер 52 управления, элемент, элемент ИЛИ 53.

Первый 32 (второй 33, третий 34) блок памяти сообщений (фиг. 4) содержит демультиплексор 54, блок-регистров 55.1-55.К (где К - глубина очереди), группу блоков элементов ИЛИ 56.1-56. К-1, первый блок элементов И 57.1-57,К. второй блок элементов ИЛИ 59.1-59.К, первый элемент И 60, второй элемент И 61, элемент НЕ 62.

Блок выбора направления передачи информации 37 (фиг. 5) содержит первую 63 и вторую 64 схемы сравнения, неполный дешифратор 65, элемент И 66.

Демультиплексор 41 выдачи (фиг. 6) содержит первый 67 и второй 68 блоки элементов И.

Блок 8 синхронизации (фиг. 7) содержит триггер 69 запуска, генератор 70 тактовых импульсов, счетчик 71, дешифратор 72, элемент И 73, элемент И 74. .

Распределитель 43 импульсов (фиг. 9) содержит генератор 75 тактовых импульсов, счетчик 76, дешифратор 77 и триггер 78.

Назначение основных блоков и элементов канала составит в следующем.

Блок памяти 1 программ предназначен для хранения команд управления и команд обмена (передачи управления аналогичным каналам системы).

Буферный запоминающий блок 2 предназначен для хранения поступивших на обслуживание сообщений к данному каналу от других каналов системы.

5Блок анализа и контроля (БАНК) 3 предназначен для анализа поступивших сообщений на принадлежность поступившего сообщения данному каналу, определения направления дальнейшего продвижения

0 информации в системе каналов, хранения кодов сигнатур, их выдаче при формировании сообщения другим каналам системы, модификации кода сигнатуры при транзитной передаче команд обмена и контроля

5 правильности прохождения маршрута передачи информации от канала передатчика к каналу приемника.

Назначение основных элементов блока анализа и контроля 3 состоит в следующем.

0Группа блоков памяти сообщений 32-34 предназначена для хранения команд обмена, поступивших для выдачи от собственного канала и от соседних каналов системы (от левого канала при продвижении информз5 ции в строке каналов и от нижнего канала при продвижении информации в столбце каналов.

: Блок памяти 36 константы предназначен для хранения кода адреса модуля, иден0 тифицирующего местоположение канала в матрице каналов системы, осуществляющих обмен командами управления. Блок памяти 36 может быть выполнен, например в виде, генератора константы - фиксированного ко5 да (тумблерного регистра и т.п.) и блока элементов И, ко второму входу которого подключен вход блока памяти 3.

Блок выбора направления передачи информации 37 предназначен для выбора и

0 модификации направления выдачи поступившей информации в зависимости от состояния кодов каналов источника и приемника информации.

Блок памяти 38 сигнатур предназначен

5 для хранения кодов определяющих правильное прохождение команды обмена в матрице каналов распределенной системы от данного канала.

. Буферный регистр 39 предназначен для

0 хранения кода сообщения на время его анализа и обработки.

Блок элементов суммы по модулю два 40 предназначен для модификации поступившего кода сигнатуры кодом адреса кана5 ла и признаком направления дальнейшего продвижения команды обмена.

Демультиплексор 41 выдачи предназна чен для коммутации команды обмена на один из выходных блоков анализа и контроля 3 к аналогичным каналам системы.

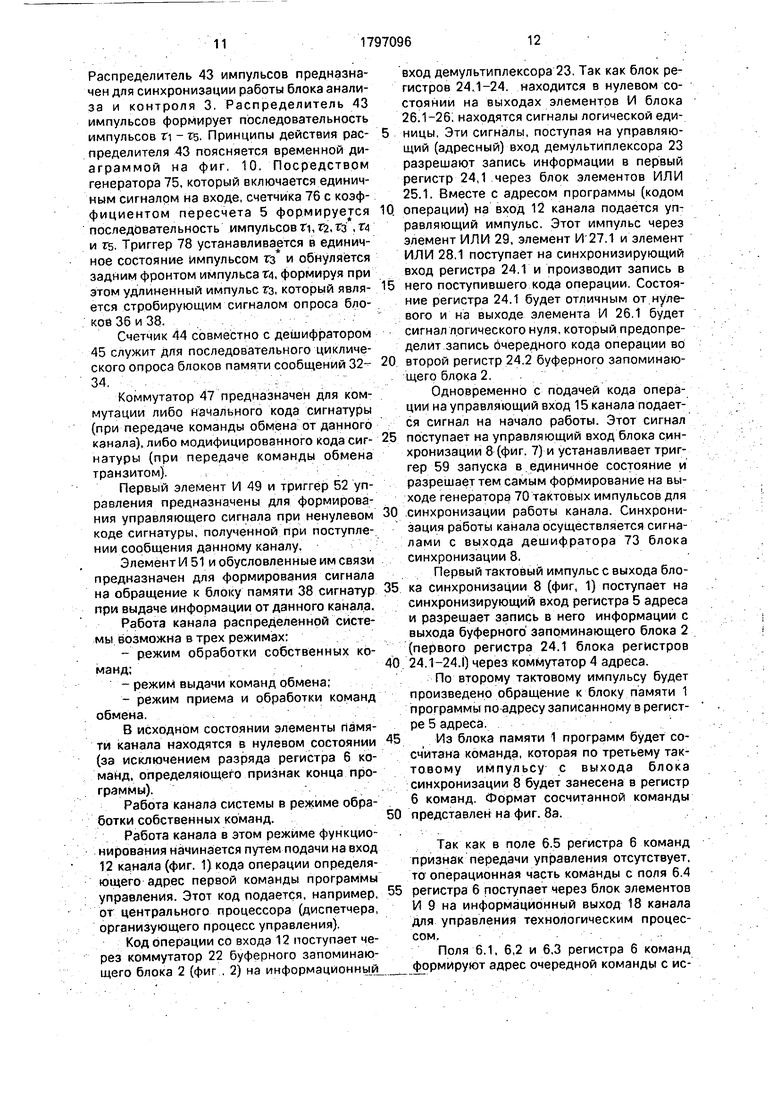

Распределитель 43 импульсов предназначен для синхронизации работы блока анализа и контроля 3. Распределитель 43 импульсов формирует последовательность импульсов Г| - Г5. Принципы действия распределителя 43 поясняется временной ди- аграммой на фиг, 10, Посредством генератора 75, который включается единичным сигналом на входе, счетчика 76 с коэффициентом пересчета 5 формируется последовательность импульсов Г1,Гг,тз , Г4 и ГБ. Триггер 78 устанавливается в единичное состояние импульсом гз и обнуляется задним фронтом импульса Т4, формируя при этом удлиненный импульс Гз, который является стробирующим сигналом опроса блоков 36 и 38.

Счетчик 44 совместно с дешифратором 45 служит для последовательного циклического опроса блоков памяти сообщений 34. . . .. ,..; .;,... - .

Коммутатор 47 предназначен для коммутации либо начального кода сигнатуры (при передаче команды обмена от данного канала), либо модифицированного кода сигнатуры {при передаче команды обмена транзитом. .:;

Первый элемент И 49 и триггер 52 управления предназначены для формирования управляющего сигнала при ненулевом коде сигнатуры, полученной при поступлении сообщения данному каналу,.

Элемент И 51 и обусловленные им связи предназначен для формирования сигнала на обращение к блоку памяти 38 сигнатур при выдаче информации от данного канала.

Работа канала распределенной системы возможна в трех режимах:

-режим обработки собственных команд;

- режим выдачи команд обмена;

- режим приема и обработки команд обмена.

В исходном состоянии элементы памяти канала находятся в нулевом состоянии (за исключением разряда регистра 6 команд, определяющего признак конца программы).

Работа канала системы в режиме обработки собственных команд.

Работа канала в этом режиме функционирования начинается путем подачи на вход 1.2 канала (фиг. 1) кода операции определяющего адрес первой команды программы управления. Этот код подается, например, от центрального процессора (диспетчера, организующего процесс управления).

Код операции со входа 12 поступает через коммутатор 22 буферного запоминающего блока 2 (фиг . 2) на информационный

вход демультиплексора 23. Так как блок регистров 24,1-24. находится в нулевом состоянии на выходах элементов И блока 26.1-26. находятся сигналы логической единицы, Эти сигналы, поступая на управляющий (адресный) вход демультиплексора 23 разрешают запись информации в первый регистр 24,1 через блок элементов ИЛИ 25.1. Вместе с адресом программы (кодом

операции) на вход 12 канала подается управляющий импульс. Этот импульс через элемент ИЛИ 29, элемент И 27.1 и элемент ИЛИ 28.1 поступает на синхронизирующий вход регистра 24.1 и производит запись в

него поступившего кода операции, Состояние регистра 24.1 будет отличным от нулевого и на выходе элемента И 26.1 будет сигнал логического нуля, который предопределит запись Очередного кода операции во

второй регистр 24.2 буферного запоминаю- щего блока 2.

Одновременно с подачей кода операции на управляющий вход 15 канала подается сигнал на начало работы. Этот сигнал

поступает на управляющий вход блока синхронизации 8 (фиг. 7) и устанавливает триггер 59 запуска в единичное состояние и разрешает тем самым формирование на выходе генератора 70 тактовых импульсов для

.синхронизации работы канала. Синхронизация работы канала осуществляется сигналами с выхода дешифратора 73 блока синхронизации 8,

Первый тактовый импульс с выхода блока синхронизации 8 (фиг, 1) поступает на синхронизирующий вход регистра 5 адреса и разрешает запись в него информации с выхода буферного запоминающего блока 2 (первого регистра 24.1 блока регистров

24.1-24.1) через коммутатор 4 адреса.

По второму тактовому импульсу будет произведено обращение к блоку памяти 1 программы по адресу записанному в регистре 5 адреса.

Из блока памяти 1 программ будет сосчитана команда, которая по третьему тактовому импульсу с выхода блока синхронизации 8 будет занесена в регистр 6 команд. Формат сосчитанной команды

представлен на фиг. 8а.

Так как в поле 6.5 регистра 6 команд признак передачи управления отсутствует, то операционная часть команды с поля 6.4 регистра 6 поступает через блок элементов И 9 на информационный выход 18 канала для управления технологическим процессом,..

Поля 6.1, 6,2 и 6,3 регистра 6 команд формируют адрес очередной команды с использованием мультиплексора 7 логических условий, который предназначен для формирования значения модифицируемого разряда адреса очередной команды и реализует логическую функцию вида:

У1 Х13 + X2Z1 - X3Z2 + .- + XK+UK,

где yi - выходной сигнал мультиплексора 7 логических условий;

xi - коньюнкция . . . Ot, соответствующая коду с выхода 6,1 кода логических условий, решающему прохождению модифицируемого адресного разряда а без изменения;

Х2 «1 2 «3 «t

хз а «2 Й . . . at Х4 «1 ог «з «t;... конъюнкции соответствующие кодам, определяющим прохождение на выход мультиплексора 7 одного из сигналов логических условий zi, Z2,...,zK со входа 17 логических условий канала,

С выдачей последней команды формируемой программы в поле 6,6 регистра 6 заносится метка - признак окончания программы. Эта метка поступает на управляющий вход коммутатора 4 адреса и разрешает прохождение через него информации (адреса очередной программы) из буферного запоминающего блока 2. Кроме того, эта метка поступает на управляющий вход буферного запоминающего блока 2 (фиг.2) и формирует. по фронту на выходе одновибратора 31 импульс. Этот импульс через элементы ИЛИ 28.1-28.1 поступает на синхронизирующие, входы блока регистров 24.1 -24.1 и осуществляет тем самым сдвиг информации.

Если выполнялась последняя команда, то очередь поступивших на обслуживание запросов становится пустой (нулевое состояние блока регистров 24.1-24.1). На выходах элементов И 26.1-26.1 образуется сигналы логической единицы. На выходе элемента И- 30 появляется сигнал логической единицы, который с выхода буферного запоминающего блока 2 (фиг. 1) поступает на вход блока синхронизации 8 (фиг...7). На выходе элемента И 73 формируется сигнал логической единицы, который через элемент ИЛИ 74 устанавливает триггер 69 запуска в нулевое состояние и модуль завершает свою работу.

Если очередь в буферном запоминающем блоке 2 не пуста, то после сдвига информации в блоке регистров 24.1 -24.1 первым тактовым импульсом очередной импульсной последовательности производится запись информации в регистр 5 адреса и далее канал функционирует аналогично рассмотренному ранее..

Работа канала в режиме выдачи команд обмена.

В процессе обработки собственных команд канал может выдать команды обмена 5 другим аналогичным каналам образующим двунаправленную кольцевую структуру распределенной системы.

Формат команды обмена (передачи управления) представлен на фиг. 86. В этом 0 случае с поля 6.4 регистра 6 команд выдается команда

m rrinp # глк,

где тпр - код (номер) канала приемника информации;

5 гпк - код (номер) программы, которую должен выполнить m -и канал системы; # - знак конкатенации (сцепления). В свою очередь

ГПпр ГПпр # ГПпр ,

0 где тПрГ - номер канала приемника информации в строке аналогичных каналов;

ftinp8 - номер канала приемника информации в стрельбе аналогичных каналов. Одновременно с кодом m команды об5 мена с выхода поля 6,5 регистра 6 команд выдается метка - признак передачи управления аналогичному каналу. Эта метка поступает на управляющие входы блока . элементов И 10 и элемента И 11 (фиг. 1) и

0 разрешает тем самым прохождение команды обмена с поля 6,4 регистра 6 через блок элементов И 10 на информационный вход блока анализа и контроля 3 (фиг. 3), Одновременно с командой обмена на этот вход

5 поступает с выхода блока синхронизации 8 тактовый импульс.

Поступившая команда обмена заносится в блок приема сообщения (БПС) 32 (фиг. 4). Так как блок регистров 55.1-55. К (где К 0 глубина очереди) находится в нулевом состоянии, то на выходах элементов И 57.1- 57-.К находятся сигналы логической единицы. Эти сигналы поступают на адресный вход демультиплексора 54 и разрешают

5 тем самым запись поступившего сообщения в первый регистр очереди 55,1, Состояние этого регистра будет отличным от нулевого и тем самым будет подготовлен для записи очередного сообщения второй регистр 55.2.

0 При записи информации в регистр 55.1 блока приема сообщения 32 на выходе элемента И 62 появляется сигнал логической единицы (фиг. 4), который с выхода БПС 32 через элемент ИЛИ 53 (фиг. 3) устанавливает

5 триггер 46 в единичное состояние. Единичное состояние триггера 46 идентифицирует разрешение формирования на выходах распределителя импульсов (РИ) 43 импульсов для синхронизации работы блока анализа 3.

Синхронизация работы блока анализа 3 происходит по импульсам, которые формируются на первом-пятом выходах распределителя 43 импульсов (фиг.9) и представляют собой пять импульсных по- следовательностей (фиг. 10). Такт (цикл) работы состоит из пяти фаз. Каждая фаза работы блока анализа 3 начинается тактовым импульсом соответствующей импульс- ной последователь- ности.

По первому тактовому импульсу происходит обращение к соответствующему блоку памяти сообщений 32-34 путем увеличения содержимого счетчика 44 на единицу.

По второму тактовому импульсу производится запись сообщения в буферный регистр 39.

По третьему тактовому импульсу происходит обращение к блокам памяти 38 и кон- стант 36.

По четвертому тактовому импульсу производится выдача команды обмена либо к соседним каналам системы, либо к данному каналу для ее дальнейшей обработки.

По пятому тактовому импульсу производится сдвиг информации в блоке памяти сообщений из которого была сосчитана информация для анализа и контроля.

Далее такт (цикл) работы блока анализа 3 повторяется путем обращения к очередному блоку памяти сообщении 32-34.

Источниками информации для данного блока анализа 3 могут быть: собственно канал системы при передаче сообщения другим ка- налам системы и соседние каналы, находя щи- есявматрице каналов снизу и слева (фиг. 13). В свою очередь, потребителями информации выступают: собственко канал при поступлении сообщения (команды обмена) данному каналу и соединим каналам, находящимся вверху и справа матрицы каналов при передаче сообщений транзитом.

Каждому каналу в системе присваивается свой идентификатор - адрес, определяю- щий местоположение канала (номер строки и номер столбца в матрице системы). Передаваемая информация состоит из трех частей: адресной, операционной и контрольной. Адресная часть представляет собой код адреса канала, которому предназначена данная операционная часть (номер программы). Контрольная часть слова представляет собой код (сигнатуру) однозначно определяющий путь между двумя каналами - передатчиком и приемником информации. По мере подтверждения команды обмена и матрицы каналов происходит модификация сигнатуры, во-первых, кодом (идентификатором) транзитною канала и, во-вторых, направлением выдачи информации. При выдаче информации от данного канала она дополняется кодом сигнатуры.

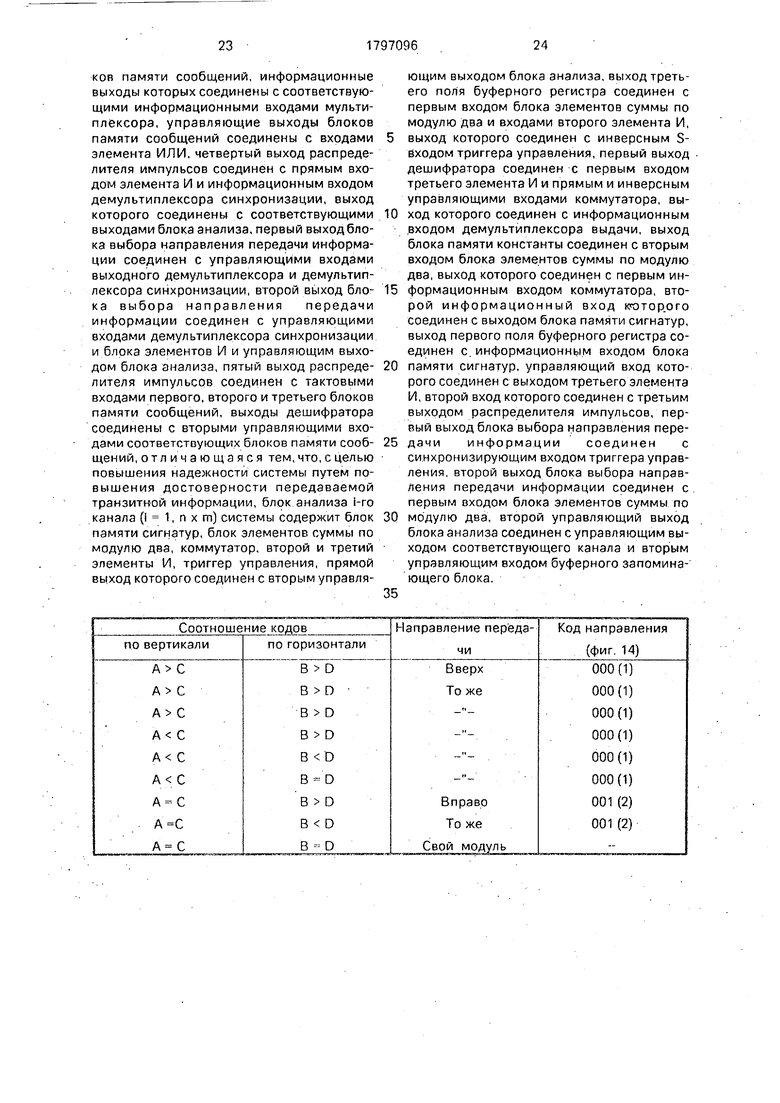

Выбор направления передачи информации блоком анализа 3 осуществляется следующим образом.

Адресная часть поступившего сообщения сравнивается с адресом (идентификатором) данного канала по нормам строки и столбца и определяется одно из трех возможных направлений передачи (два - на соседние каналы и третье - на обработку данному каналу) по следующему правилу.

Путь А и В коды адресов канала источника информации по горизонтали и вертикали (строки и столбца) размещения каналов в системе, а С и D - коды адресов канала приемника информации. Процедура выбора направления передачи информации реализуемой блоком 37 определяется табл. 1..-.-.

В блоке памяти 36 блока анализа 3 (фиг. 3) записан код адреса (идентификатор) (код строки и код столбца) данного канала относительно других каналов в однородной структуре распределенной системы.

При занесении информации (команды обмена) в блок памяти сообщений 32 тактовый импульс с выхода распределителя 43 (фиг. 3 ) увеличивает содержимое счетчика 44 на единицу. На выходе дешифратора 45 инициатируется единичный сигнал для опроса блока памяти сообщений 32. Код с выхода счетчика 44, поступая на управляющий (адресный) вход мультиплексора 35 и разрешает тем самым запись информации по второму импульсу с блока памяти 32 в буферный регистр 39.

Считываемая информация из блока памяти 32 сообщений (фиг. 3) состоит из трех частей - адресной, операционной и контрольной, которые заносятся соответственно в поля 39.1, 39.2 и 39.3 буферного регистра 39.

Отличие функционирования канала в режиме передачи команды обмена от собственного канала заключается в следующем.

Команда обмена в передаваемом сообщении должна быть дополнена контрольной информацией (сигнатурой) в зависимости от кода (номера) канала приемника информации. Все сигнатуры прохождения команд обмена от данного канала записаны в блоке памяти сигнатур 38. В поле 39.3 буферного регистра находится нулевая контрольная информация.

Счетчик 44 будет находиться в состоянии, Определяющем обращение к блоку памяти сообщений 32. На соответствующем выходе дешифратора 45 будет сигнал логической единицы. Этот сигнал поступает на управляющий вход коммутатора 47 и разрешит прохождение через него информации с выхода блока памяти 38 сигнатур. Очередной импульс Т3 с выхода распределителя 43 поступает на управляющий вход блока памяти 38 сигнатур и производится считывание из него информации по адресу, хранимому в поле 39,1 буферного регистра 39,

Код сигнатуры с выхода блока памяти 38 через коммутатор 47 поступает на информационный вход демультиплексора 41. Кроме кода сигнатуры на информационный вход демультиплексора 41 поступает информация о кодах адреса канала приемника информации и адреса программы. Сформированная команда обмена выдается на один из двух выходов блока анализа 3 на выход 19 или 20 к соседним каналам распределенной системы (фиг. 13)-.

Выбор направления передачи команды обмена от данного канала осуществляется блоком направления передачи информации (ВВНПИ) 37 (фиг. 3). На основе сравнения двух кодов адресов каналов на схемах сравнения 63 и 64 (фиг. 5} БВНПИ 37 на выходе неполного дешифратора 65 образуется в соответствии с таблицей 1 признак.

( 1, если требуется передать информа- р 1 цию вверх;:

Lo, если требуется передать информацию вправо.

Сформированный признак направления выдачи информации с выхода БВНПИ 37 (фиг.-З) поступает на адресные (управляющие) входы демультиплексоров 41 и 42. Очередной импульс 4 с выхода распределителя 43 через демультиплексор 42 поступает на соответствующий выход блока анализа 3 для синхронизации записи сообщения в блок памяти сообщения 33 (34) соседнего канала. Далее канал функционирует аналогично описанному.

Работа канала в режиме приема и обработки команд обмена.

При обработке команды обмена от соседних каналов происходит обращение к соответствующему блоку памяти сообщений 33 или 34 блока анализа 3 (фиг. 3). Через мультиплексор 35 команды обмена заносится в буферный регистр 39. При этом поле 39,3 находится код сигнатуры.

При передаче информации транзитом код сигнатуры S при прохождении канала будет промодифицирован, во-первых, доком адреса (идентификатором) канала и, во- вторых, кодом направления выдачи информации. Модификация кода сигнатуры, поступающего с выхода поля 39.3 буферного регистра 39. происходит на блоке свертки по модулю два 40, поступающем признаком

направления передачи направления р с выхода БВНПИ 37 и кодом адреса канала с выхода блока памяти 36. Полученная сигнатура с выхода блока элементов суммы по 5 модулю два через коммутатор 47 поступает для дальнейшей ее передачи совместно с адресной и операционной частями команды обмена к соседнему каналу. Далее канал функционирует аналогично описанному ра0 нее. По мере продвижения команды обмена в матрице каналов системы к каналу приемнику информации будет происходить модификация сигнатуры.

При совпадении кодов адресов прием5 ника информации с адресной частью команды обмена на выходах Равно первой 63 и второй 64 схем сравнения блока 37 (фиг, 5) формируются сигналы логической единицы. На выходе элемента И 66 будет также сигнал

0 логической единицы. Этот с выхода блока 37 выбора направления передачи информации (фиг. 3) поступает на управляющий вход блока элементов И 48 и разрешает тем самым при поступлении импульса с выхода распре5 делителя 43 приложение операционной части (кода адреса программы) с выхода поля 39.2 буферного регистра 39 на выход блока анализа 3 для последующей записи в буферный запоминающий блок 2 (фиг. 1) для Даль- 0 нейшей обработки данным каналом.

Кроме того, управляющий сигнал с выхода блока выбора направления передачи информации 37 поступает на управляющий вход синхронизации триггера 52. На выходы

5 элемента И 49 с нулевых выходов поля 39.3 буферного регистра 39 поступает код сигнатуры. Отсутствие ошибки в прохождении команды обмена в матрице каналов системы будет при S 00...0 ; в противном случае

0 маршрут прохождения сообщения будет отличным от запланированного. При нулевой сигнатуре 5 00..,0 на выходе элемента И 49 будет сигнал логической единицы, идентифицирующий правильность прохож5 дения команды, обмена, а следовательно, и правильность принадлежности поступившего на обслуживание запроса. Этот сигнал поступает на инверсный S - вход триггера 52 управления и не изменяет его состояния.

0 При S 5 000...0 сигнал логического нуля с. выхода элемента И 49 (фиг, 3) установит триггер 52 в единичное состояние. На прямом выходе триггера 52 будет сигнал логической единицы, поступающий на выход

5 блока анализа 3 и с его выхода на выход 21 канала и на управляющий вход буферного запоминающего блока 2 (фиг. 1). Этот сигнал поступает на управляющий вход буферного запоминающего блока 2 (фиг. 2) и с его входа

на инверсный управляющий вход коммутатора вход коммутатора 22 и тем самым запрещается занесение в блок 2 адреса программы с выхода блока анализа 3 (фиг.

1)После обслуживания поступивших на

обработку в блоки памяти 32-34 сообщений (фиг. 4) на выходе элементов И .62 будут сигналы логического нуля. Эти сигналы на выходе элемента ИЛИ блока анализа 3 (фиг. 3) образуют сигнал логического нуля, который поступает на инверсный вход элемента И 50 и разрешает тем самым при выдаче последней команды обмена на соседний канал или данному каналу импульсом с выхода распределителя 43 обнуление триггера 46. На этом анализе и контроль поступивших команд обмена завершается.

Поступившие от соседних каналов команды обмена (операционные части - коды адресов программ) заносятся с выхода блока анализа 3 в буферный запоминающий блок 2 (фиг. 2) и обслуживаются по принципу первым пришел - первым обслужен аналогично обработке собственных команд.

После обслуживания (формирования всего множества программ, адреса которых были занесены в буферный запоминающий блок 2 (фиг.2) на выходе элемента И 30 образуется сигнал логической единицы поступающий на управляющий вход блока 8 синхронизации (фиг. 1). Этот сигнал поступает на вход элемента И 73 (фиг. 7) на второй вход которого поступила метка конца выполненной программы с поля 6.8 регистра 6. Триггер запуска 69 устанавливается в нулевое состояние и на этом канал завершает свою работу.:

Таким образом, в предложенной распределенной системе для программного управления технологическими процессами осуществляется контроль прохождения информации, что позволяет повышать достоверность функционирования системы. -;

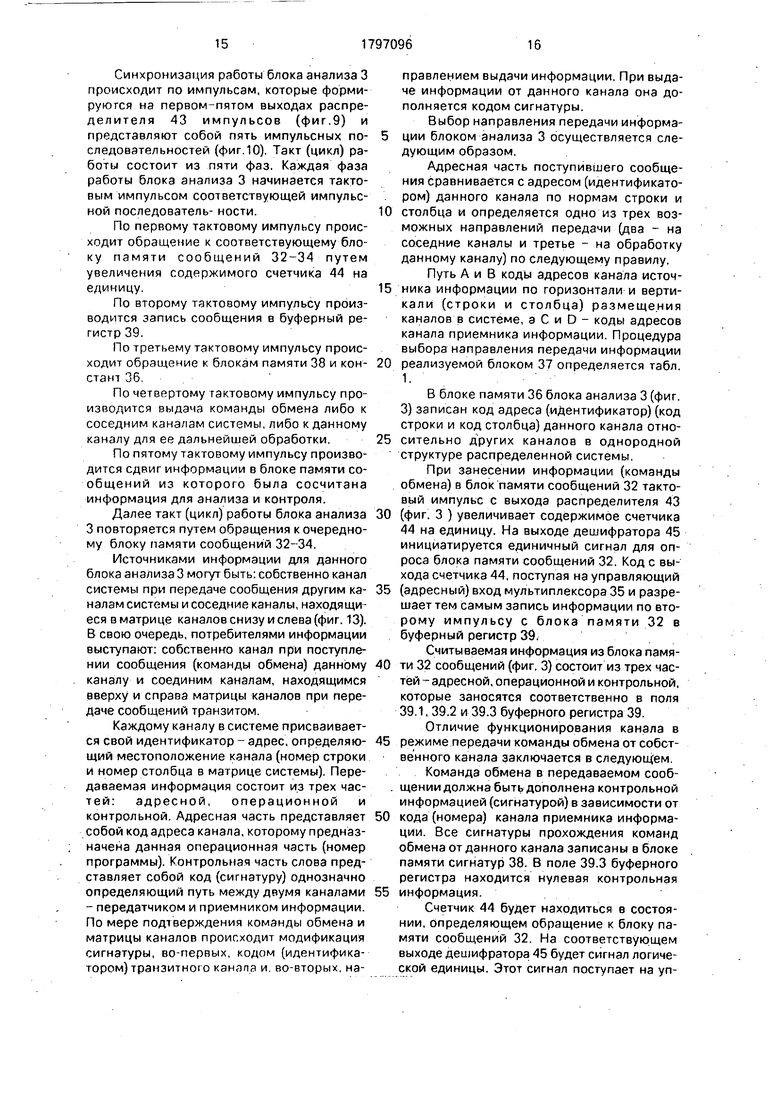

Пусть имеется матрица каналов системы размерности М 3 х 3 (фиг. 11). Пусть необходимо передать команду обмена от канала с номером (3.1) к каналу с номером (1.3). В этом случае из блока памяти сигнатур будет сосчитан контрольный код S 011001 (фиг. 12а), При правильном прохождении информации и распределенной сис- теме оставшаяся сигнатура S Sn 000000 (фиг. 126). Допустим, что при поступлений информации в канал с номером (2.2) (фиг. 11) адресная часть будет изменена (001011) - -(010011). В этом случае произойдет изменение прохождения информации будет передано на канал с номером (2.3). Сообщение

0

5

0

5

0

5

0

5

0

5

будет принято к исполнению и в распределенной системе произойдет искажение формируемой информации. В предлагаемом канале оставшаяся сигнатура S SH 00...О 001001 и будет сформирован .признак неверного прохождения информации. По данному признаку возможно обращение, например, к диагностической процедуре.

Количественно достигаемый выигрыш в достоверности .пропуска ошибки:

(1-PM) .. где Q - вероятность появления отказа (сбоя) аппаратуры, вызывающего искажение информации;

Рм - вероятность обнаружения искажения в предлагаемой системе.

При Рм 0,99 и Q 0,001 получаем 5о 100. Таким образом, предлагаемой системе имеется возможность на два порядка уменьшить недостоверность обмена информацией в системе, что обуславливает расширение области ее применения.

Распределенная система для программного управления технологическими процессами может найти применение в АСУ ТП, построенных на основе модульных структур, где отдельные строки (столбцы) каналов могут быть изготовлены в виде отдельных СБИС. Такая организация систем повышает гибкость и адаптивность системы к внешним условиям (расширению макрофункций системы).

Формула изобретения

Распределенная система для программного управления технологическими процессами, содержащая n x m каналов, где n m, п - число каналов в строке матричной организации системы; m - число строк, причем 1-й канал (i 1, n x m) системы содержит блок памяти программ, коммутатор адреса, регистр адреса, регистр команд, мультиплексор логических условий, блок синхронизации, блок элементов И, элемент И, причем первый управляющий вход канала соединен с первым входом блока синхронизации, первый выход которого соединен с синхронизирующим входом регистра адреса, выход которого соединен с входом блока памяти программ, выход блока памяти программ соединен с информационным входом регистра команд, синхронизирующий вход которого соединен с вторым выходом блока синхронизации, выход поля проверяемых логических условий регистра команд соединен с первым информационным входом мультиплексора логических условий, выход модифицируемого разряда

адреса регистра команд соединен с вторым информационным входом мультиплексора логических условий, выход которого соединен с входом модифицируемого разряда адреса первого информационного входа коммутатора адреса, выход которого соединен с информационным входом регистра адреса, вход логических условий канала соединен с управляющим входом мультиплексора логических условий, выход поля немодифицируемых разрядов адреса регистра команд соединен с соответствующими входами немодифицируемых разрядов адреса первого информационного входа коммутатора адреса, выход операционного поля регистра команд соединен с информационным входом блока элементов И, выход которого соединен с первым информационным выходом канала, выход поля конца программы регистра команд соединен с прямым и инверсным управляющими входами коммутатора адреса и вторым входом блока синхронизации, второй управляющий вход канала соединен с третьим входом блока синхронизации, второй информации онн.ый выход К-го (К 1, п-1) канала (v, m) строки каналов соединен с вторым информационным входом (К+1)-го канала v-й строки, второй информационный выход п-го канала v-й строки соединен с вторым информационным входом первого канала v-й строки, кроме того, каждый канал содержит буферный запоминающий блок, блок анализа, второй блок элементов И. причем информационный выход буферного запоминающего блока соединен с вторым информационным входом коммутатора адреса, выход операционного поля регистра команд соединен с информационным входом второго блока элементов И, выход которого и выход элемента И соединены с первым входом блока анализа, управляющий выход которого соединен с управляющим входом буферного запоминающего блока, управляющий выход которого соединен с четвертым входом блока синхронизации, третий выход которого соединен с первым входом элемента И, выход поля передачи управления регистра команд соединен с инверсным управляющим входом первого блока элементов И, прямым управляющим входом второго блока элементов И и вторым входом элемента И, первый информационный выход блока анализа соединен с первым информационным входом буферного запоминающего блока, выход поля конца программы регистра команд соединен с вторым управляющим входом буферного запоминающего блока, первый информационный вход канала соединен с вторым информационным входом буферного запоминающего блока, второй информационный вход канала соединен с вторым входом блока анализа, второй ин- 5 формационный выход которого соединен с вторым информационным выходом канала, третий информационный вход канала соединен с третьим входом блока анализа, третий информационный выход которого - с

0 третьим информационным выходом канала, третий информационный выход j-ro Q п, 1) канала fi-ro столбца ( fi T7h) каналов соединен с третьим информационным входом (j-T}-ro канала, третий информационный вы5 ход первого канала fi -го столбца каналов соединен с третьим информационным входом т-го канала соответствующего столбца каналов, причем блок анализа содержит первый, второй и третий блоки памяти сооб0 щений, мультиплексор, блок памяти константы, блок выбора направления передачи информации, триггер, буферный регистр, блок элементов И, выходной демультиплек- сор, демультиплексор синхронизации, де5 шифратор, счетчик, распределитель импульсов, элемент И и элемент ИЛИ, выход которого соединен с S-ro входом триггера и инверсным входом элемента И, выход которого соединен с R-входом триггера,

0 прямой выход триггера соединен с управляющим входом распределителя импульсов, первый выход которого соединен со счетным входом счетчика, выходы счетчика соединены с входами дешифратора и

5 управляющими входами мультиплексора, выход которого соединен с информационным входом буферного регистра, синхронизирующий вход которого соединен с вторым выходом распределителя импульсов, третий

0 выход распределителя импульсов соединен с входом считывания блока памяти константы, выход которого соединен с первым вхо- -дом блока выбора направления передачи информации, второй вход которого соеди5 нен с выходом адресного поля буферного регистра, выход операционного поля буферного регистра соединен с информационным входом блока элементов И, выход которого соединен с первым информационным выхо0 дом блока анализа, выходы адресного и операционного полей буферного регистра соединены с информационным входом вы- . ходного демультиплексора, первый и второй выходы которого соединены

5 соответственно с вторым и третьим информационными выходами блока анализа, первый, второй и третий входы которого соединены с информационным и первым управляющим входами соответствующих блоков памяти сообщений, информационные выходы которых соединены с соответствующими информационными входами мультиплексора, управляющие выходы блоков памяти сообщений соединены с входами элемента ИЛИ, четвертый выход распределителя импульсов соединен с прямым входом элемента И и информационным входом демультиплексора синхронизации, выход которого соединены с соответствующими выходами блока анализа, первый выход блока выбора направления передачи информации соединен с управляющими входами выходного демультиплексора и демультиплексора синхронизации, второй выход блока выбора направления передачи информации соединен с управляющими входами демультиплексора синхронизации и блока элементов И и управляющим выходом блока анализа, пятый выход распределителя импульсов соединен с тактовыми входами первого, второго и третьего блоков памяти сообщений, выходы дешифратора соединены с вторыми управляющими входами соответствующих блоков памяти сообщений, отличаю ща я с я тем, что, с целью повышения надежности системы путем повышения достоверности передаваемой транзиткой информации, блок анализа i-ro канала (I 1, n x m) системы содержит блок памяти сигнатур, блок элементов суммы по модулю два, коммутатор, второй и третий элементы И, триггер управления, прямой выход которого соединен с вторым управля0

5

0

5

0

5

ющим выходом блока анализа, выход третьего поля буферного регистра соединен с первым входом блока элементов суммы по модулю два и входами второго элемента И, выход которого соединен с инверсным S- бходом триггера управления, первый выход дешифратора соединен с первым входом третьего элемента И и прямым и инверсным управляющими входами коммутатора, выход которого соединен с информационным .входом демультиплексора выдачи, выход блока памяти константы соединен с вторым входом блока элементов суммы по модулю два, выход которого соединен с первым информационным входом коммутатора, второй информационный вход кгатор.ого соединен с выходом блока памяти сигнатур, выход первого поля буферного регистра соединен с. информационным входом блока памяти сигнатур, управляющий вход которого соединен с выходом третьего элемента И, второй вход которого соединен с третьим выходом распределителя импульсов, первый выход блока выбора направления передачи информации соединен с синхронизирующим входом триггера управления, второй выход блока выбора направления передачи информации соединен с . первым входом блока элементов суммы по модулю два, второй управляющий выход блока анализа соединен с управляющим выходом соответствующего канала и вторым управляющим входом буферного запоминающего блока.

960Л61I

Г

АР

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для программного управления технологическими процессами | 1990 |

|

SU1784940A1 |

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1988 |

|

SU1571594A1 |

| Распределенная система для программного управления технологическими процессами | 1988 |

|

SU1605212A1 |

| Устройство для обмена данными в распределенной вычислительной системе | 1988 |

|

SU1580382A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1988 |

|

SU1501080A1 |

| Устройство для диагностики абонентов вычислительной сети | 1989 |

|

SU1679488A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

Изобретение относится к автоматике и вычислительной технике и может найти применение в программируемых контроллерах, станках с числовым программным управлением, АСУ технологическими процессами. Цель изобретения - надежность системы путем повышения достоверности передаваемой транзитной информации. Распределенная система содержит n x m каналов (где пит- число каналов соответственно в строке и столбце матричной организации системы), а каждый канал содержит блок памяти программ, коммутатор адреса, регистр адреса, регистр команд, мультиплексор логических условий , блок синхронизации, блок анализа, два блока элементов И, элемент И, причем в блок анализа дополнительно введены блок памяти сигнатур, блок элементов суммы по модулю два, коммутатор, триггер управления и два элемента И. 1 табл., Нил. Ё

Фиг. 6

&

3

Фи г. 7

ф.иг. а

Фиг. Ю

Фиг. И

КАНАЛ

(sp

ecu a.)

| Авторское свидетельство СССР № 1226452,кл.G 06 F 9/22, 1986 | |||

| Распределенная система для программного управления технологическими процессами | 1988 |

|

SU1605212A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Способ приготовления консистентных мазей | 1919 |

|

SU1990A1 |

Авторы

Даты

1993-02-23—Публикация

1990-01-10—Подача