второй выход блока управления соединен со счетным входом первого счечика, отличающееся тем что, с целью повышения быстродействия и расширения области применения за счет увеличений диапазона изменения аргумента и возможности непрерывного генерирования функций с управляемым шагом, оно дополнительно содержит четвертый и пятый регистры, коммутатор и блок нормализации числа, адресный, информационные и операционный входы которого соединены с параллельным выходом первого счетчика, информационными входами блока анализа знака и выходом регистра кода операций соответственно, ин(юрмационные выходы блока нормализации числа соединены с адресно шиной устройства, выход второго блока памяти соединен с параллельным входом второго счетчика, параллельный выход которого подключен к информационному входу коммутатора, выход которого соединен с синхронизирующим входом блока нормализации числа, последовательный выход второго счетчика соединен со стробирующими входами блока анализа знака и блока нормализации числа, управляющий выход которого соединен с пятым входом блока управления, четвертый выход которого соединен с, управляющими входами четвертого и ПЯТОГО регистров и второго счетчика, пятый и шестой выходы блока управления соединены с управляющими входами первого блока памяти и блока нормализации числа соответственно, .выходы первого и второго регистров соединены с параллельными информационными входами четвертого и пятого регистров соответственно, первый и второй тактирующие входы которых соединены соответственно с вторым и третьим выходами блока управления, седьмой и восьмой выходы которого соединены соответственно с входом обнуления первого счетчика и управляющим входом коммутатора, девятый выход блока управления соединен с управляющими входами первого и второго переключателей, выходы которых соединены с первыми информационными входами четвертого и пятого сумматоров соответственно, выходы которых соединены с последовательными информационными входами четвертого и пятого регистров соответственно, выходы которых соединены с вторыми информационными входами четвертого и пятого сумматоров соответственно, выходы первого и второго блоков сдвига соединены с вторыми информационными входами второго и первого сумматоров соответственно, запускающий вход устройства соединен с входом обнуления блока нормализации числа.

2. Устройство по п. 1, отличающееся тем, что, блок нормализации числа содержит мультиплексор, двоичный счетчик, четыре триггера, узел памяти, элемент НЕ, схему сравнения и два элемента И-НЕ, выходы которых соединены с входами устанобки в 1 первого и второго триггеров соответственно, выходы которых соединены с инАормационными входами третьего триггера, выход которого является управляющим выходом блока, информационные и операционные входы блока соединены с соответствующими входами мультиплексора, выход которого соединен с информационным входом четвертого триггера, первым адресным входом записи узла памяти и с первым входом первого элемента непосредственно, а с первым входом второго элемента Й-НЕ - чере элемент НЕ, управляюв|ий вход блока нормализации числа соединен с вторыми входами элементов И-НЕ и входами установки в О первого и второго триггеров, стробирующие входы которых и стробирующий вход узла памяти соединены с синхронизирующим входом блока, адресный вход блока соединен с первым входом схемы сравнения и информационным входом узла памяти, выход которого соединен с вторым входом схемы сравнения, выхо которой и выход узла памяти являются информационными выходами блока, стробирующий вход блока соединен со стробируюидими входами третьего и четвертого триггеров и со счетным входом двоичного счетчика, прямой и инверсный выходы которого соединены соответственно с первым адресным входом считывания и вторым адресным входом записи узла памяти второй адресный вход считывания которого соединен с выходом четвертого триггера, вход обнуления блока соединен с входом установки в О третьего триггера.

3. Устройство no п. 1, отличающееся тем, что блок анаг лиза знака содержит регистр, одноразрядный узел памяти и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ., выход которого и выход одноразрядного узла памяти являются выходами блока, стробирующий и информационные входы блока соединены соответственно с управляющим и информационными входами регистра, выход которого соединен с первым адресным входом одноразрядного узла памяти, второй адресный вход которого соединен с управляющим входом блока, входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с выходом одноразрядного узла памяти и управляимцим входом блока соответственно.

4. Устройство по п,.1, отличающееся тем, что блок управления содержит генератор импульсов, регистр, мультиплексор, четыре элемента И-НЕ, два элемента И, элемент НЕ и элемент задержки, выход которого соединен с первым вы.ходом блока, первый вход блока соединен с управляющим входом генератора импуль сов, входом обнуления регистра и с первым входом первого разряда мультиплексора, второй вход первого разряда которого соединен с шиной сигнала О блока и с первым входом второ го разряда мультиплексора, третий вход первого разряда которого соединен с выходом первого элемента И-НЕ, первый вход которого соединен с третьим входом блока, четвертый вход блока соединен с вторым входом первого элемента И-НЕ и с и четвертым входами второго разряда мультиплексора, четвертый вход первого разряда которого соединен с вторым входом второго разряда мультиплексора и с шиной сигнала 1 блока, пятый вход блока соединен со стробирующим входом мультиплексора и с входом элемента НЕ, выход которого соединен с первым входом второго, элемента И-НЕ, выход которого соединен с входом элемента задержки второй выход блока соединен с первым выходом генератора импульсов и с управляющим входом регистра, перв и второй информационные входы которого соединены с выходами соответственно первого и второго разрядов мультиплексора, первый адресный вхо которого соединен с первыми входами первого и второго элементов И и с первым прямым выходом регистра, второй прямой выход которого соединен с вторым адресным входом мультиплексора, с первыми входами третьего и четвертого элементов И-НЕ, с шестым выходом блока и с вторым входом первого И, выход которого соединен с девятым выходом блока, четвертый выход блока соединен с выходом второго элемента И, второй вход которого соединен с вторым входом второго элемента И-НЕ и выходом блока, первЬ1й инверсг. ный выход регистра соединен с третьим входом второго элемента И-НЕ и вторым входом четвертого элемента И-НЕ, второй инверсный выход регистра соединен с седьмым выходом блока, второй выход генератора импульсов соединен с восьмым выходом блока и с вторым входом третьего элемента И-НЕ, выход которого соединен с третьим выходом блока, второй вход блока соединен с третьим входом четвертого элемента И-НЕ, выход которого соединен с пятым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1980 |

|

SU940155A1 |

| Устройство для вычисления функции | 1984 |

|

SU1180884A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1130861A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Устройство для сопряжения цифровой вычислительной машины с устройством ввода изображений | 1983 |

|

SU1176339A1 |

| Устройство для вычисления скользящего спектра | 1986 |

|

SU1363240A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1315999A1 |

| Устройство для реализации быстрого преобразования Фурье | 1988 |

|

SU1672468A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1783581A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1124379A1 |

1

Изобретение относится к вычислительной технике, а именно к классу арифметических устройств для вычисления трансцендентных функций, и может быть использовано в цифровых моделирующих, управляющих и вычислительных системах как общего, так и специального назначения.

Известно цифровое устройство для вычисления ряда элементарных функций, реализующее алгоритм Волдера, содержащее регистры, блоки сдвига, блоки памяти, сумматоры-вычитатели, блок управления, анализатор сходимости и т.п., причем процесс вычислений заключается в совместной реализации алгоритмов псевдоумножения и псевдоделения 1J. Недостатками устройства являются ограниченные функциональные воз можности и невысокое быстродействи Функциональные возможности ограничены вследствие появления при реализации, алгоритма Волдера коэффициента деформации решения f) , который различен для разных классов функций и зависит от состава наборов величин шагов интегрирования. Компенсация коэффициента деформации решения осуществляется упрощением наборов формируемых функций, вводом начальных условий типа выполнением определенных последовательностей шагов интегрирования. Так как наличие ухудшает сходимость для ряда элементарных функций с заданным набором шагов интег рирования, приходится, например, удваивать процедуры на каждой И1герэции, что увеличивает полное врем вычислений, т.е. снижает быстродействие. ( Известно цифровое устройство для вычисления элементарных функций, также реализующее алгоритм Волдера в котором для устранения деформации выбирается такая величина шага интегрирования, при которой fbo 1 причем для повышения быстродействия кроме простейших используются также формулы численного интегрирования более высоких порядков С 23. Недостатками устройства являются пониженное быстродействие и невысокая точность. Известно цифровое устройство для вычисления элементарных функций в котором для устранения деформации решения после выполнения операции поворота вектора осуществляется умножение результата на величину l/pio выполняемое на том же оборудовании но по несколько иному алгоритму f3 Недостаток устройства - низкое быстродействие. Известно также устройство, в котором для повышения быстродействи осуществляется предварительный выбор начального шага и соответствующего представления коэффициента деформации, который далее компенсируется по мере выполнения определенных итераций L J. Однако в данном устройстве повышение быстродействия происходит лишь для малых значений аргумента. Наиболее близким к изобретению по функциональному назначению и технической сущности является устройство, которое состоит из трех регистров, четырех блоков сдвига, блока памяти, семи сумматоров, четырех переключателей, двух счетчиков, блока управления, регистра кода операций, второго блока памяти и блока анализа знака, причем коррекция деформации решения осуществляется путем вычисления на дополнительных сумматорах соответствующих поправок БТ. Недостатки этого устройства - ограниченное быстродействие и узость функциональных возможностей и области применения вследствие ограничения диапазона изменения аргумента и невозможности непрерывного генериробания функций,.в том числе с управляемым шагом, что вызвано зависимостью коэффициента деформации решения от набора итераций, в результате чего этот набор задается фиксированным, поэтому вариации его, в зависимости от аргумента или режима функционирования, недопустимы. Цель изобретения - повышение быстродействия и расшивение функциональных возможностей и области применения за счет увеличения диапазона изменения аргумента и возможности непрерывного генерирования функций с управляемым шагом. Поставленная цель достигается тем, что в устройство, содержащее первый, второй и третий регистры, первый и второй блоки сдвига, первый и второй переключатели, пять сумматоров, первый блок памяти, блок управления, второй блок памяти, первый и второй счетчики, регистр кода операций и блок анализа знака, информационные входы которого соединены с выходами первого, второго и третьего сумматоров, которые подключены также к последовательным информационным входам первого, второго и третьего регистров соответственно, параллельные информационные входы которых соединены с соответствующими информационными входами устройства, запускающий вход устройства соединен с входом занесения регистра кода операций и с первым входом блока S управления, второй вход которого сое динен с первым управляющим входом устройетв.а, второй управляющий вход устройства соединен с информационным входом регистра кода операций, выход регистра кода операций с,оединен с управляющим входо.м блока анализа знйка, выходы которого соединены с управляющими входами всех сумматоров выходы первого и второго регистров соединены с информационными входами первого и второго блоков сдвига соответственно, выходы которых соединены с информационны.ми входами второго и первого переключателей соответственно, первые информационные входы первого, второго и третьего сумматоров соединены с выходами чет вертого и пятого сумматоров и третье го регистра соответственно, второй информационный вход третьего сумматора соединен с выходом первого бло ка памяти, первый адресный вход которого coe lинeн с параллельным дом первого счетмика, последователь ный выход которого соединен с треть входом блока управления и счетным входом второго счетчика, последовательный выход которого соединен с четвертым входом блока управления, первый, второй и третий выходы крторого соединены соответственно с у равляющими, первыми тактовыми и вто рыми тактовыми входами первого, вто рого и третьего регистров, второй адресный вход первого блока памяти, адресные входы блбков сдвига и второго блока памяти соединены с адре ной шиной устройства, второй выход бЬока управления соединен со счетным входом первого счетчика, дополнительно введены четвертый и пятый регистры, коммутатор и блок нормали зации числа, адресный, информационные и операционный входы которого соединены спараллельным выходом пе вого счетчика, информационными входами блока анализа знака и выходом регистра кода операций соответственно, информационные выходы блока нормализации числа соединены с адресной шиной устройства, выход второго блока .памяти соединен с параллельным входом второго счетчика, параллельный выход которого подключен к информационному входу коммута тора , выход которого соединен с син ронизирующим входом блока нормализа ции числа, последовательный выход i второго счетчика соединен со стробирующими входамиблока анализа знака и блока нормализации числа, управляющий выход которого соединен с пятым входом блока управления, четвертый выход которого соединен с управляющими входами четвертого и пятого регистров и второго счетчика, пятый и шестой, выходы блока управления соединены с управляющими входами перво го блока памяти и блока нормализации числа соответственно, выходы первого и BTopjoro реги ;тров соединены с параллельными информационными входами четвертого и пятого регистров соответственно, первый 41 второй тактирующие входы которых соединены соответственно с вторым и третьим выходами блока управления, седьмой и восьмой выходы которого соединены соответственно с входом обнуления первого счетчика и управляющим входом коммутатора, девятый выход блока управления соединен с управляющими входами первого и второго переключателей , выходы которых соединены с первыми информационными входами четвертого и пятого сумматоров соответственно, выходы ко.торых соединены с последовательными информат ционными входами четвертого и пятого регистров соответственно, выходы которых соединены с вторыми информационными входами четвертого и пятого сумматоров соответственно, выходы первого и второго блоков сдвига соединены с вторыми информационными входами второго и первого сумматоров соответственно, запускающий вход устройства соединен с входом обнуления блока нормализации числа . Блок нормализации числа выполнен в виде мультиплексора, двоичного счетчика, четырех триггеров, узла памяти, элемента НЕ, схемы сравнения и двух элементов И-НЕ, выходы которых соединены с входами установки в 1 первого и второго триггеров соответственно, выходы которых соединены с информационными входами третьего триггера, выход которого является управляющим выходом блокаинформационные и операционный входы блока соединены с соответствующими входами мультиплексора, выход которого соединен с информационным входом четвертого триггера, первым адресиым входом записи узла памяти и с первым входом первого элемента И-НЕ непосредственно, а с первым входом вто рого элемента И-НЕ - через элемент НЕ, управляющий вход блока нормализации числа соединен с вторыми входа ми элементов И-НЕ и входами установки в О первого и второго триггеров, стробирующие входы которых и стробирующий вход узла памяти соединены с синхронизирующим входом блока, .адресный вход блока соединен с первым входом схемы сравнения и информационным входом узла памяти выход которого соединен с вторым вхо дом схемы уравнения, выход которой и выход узла памяти являются информационными выходами блока, стробирующий аход блока соединен со стробирующими входами третьего и четвертого триггеров и со счетным входом двоичного счетчика, прямой и инверсный выходы которого соединены соответственно с первым адресным входом считывания и вторым адресным входом записи узла памяти, второй адресный вход считывания которого соединен с выходом четвертого триггера вход обнуления блока соединен с вхоО третьего тригдом установки гера. Блок анализа знака выполнен в видез0 динен

регистра, одноразрядного узла памяти и элемента ИСКШЧАЮЩЕЕ ИЛИ, выход которого и выход одноразрядного узла памяти являются выходами блока, стробирующий и информационные входы блока соединены соответственно с управляющими информационными входами регистра, выход которого соединен с первым адресным входом одноразрядного узла памяти, второй адресный вход которого соединен с управляющим входом блока, входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с выходом одноразрядного узла памяти и управляющим входом блока соответственно.

Блок управления выполнен в виде генератора импульсов, регистра, мультиплексора, четырех элементов И-НЕ, двух элементов И, элемента НЕ и элемента задержки, выход которого соединен с первым выходом блока, первый вход блока соединен с управляющим входом генератора импульсов, входом обнуления регистра и с первым еходом первого разряда мультиплек-, сора, второй вход первого разряда которого соединен с шиной сигнала О блока и с первым входом второго разряда мультиплексора, третий

типлексора, с первыми входами третьего и четвертого элементов И-НЕ, с шестым выходом блока и с вторым входом первого элемента И, выход., которого соединен с девятым выходом блока, четвертый выход J5лoкa соединен с выходом второго элемента И, второй вход которого соединен с вторым входом второго элемента И-НЕ и седьмым выходом блока, первый инвереный выход регистра соединен с третьим входом второго элемента И-Н и вторым входом четвертого элемента И-НЕ, второй инверсный выход регистра соединен с седьмым выходом блока второй выход генератора импульсов соединен с восьмым выходом блока и с вторым входом третьего элемента И-НЕ, выход которого соединен с третьим выходом блока, второй вход блока соединен с третьим входом четвертого элемента И-НЕ, выход которого соединен с пятым выходом блока.

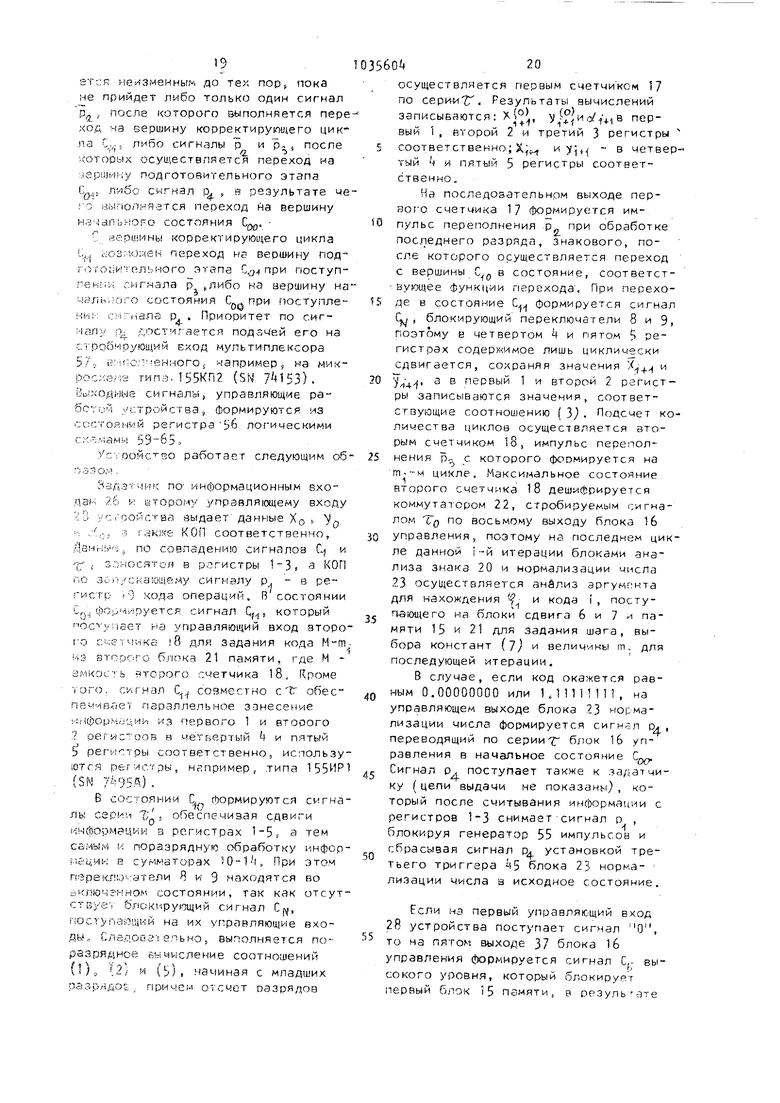

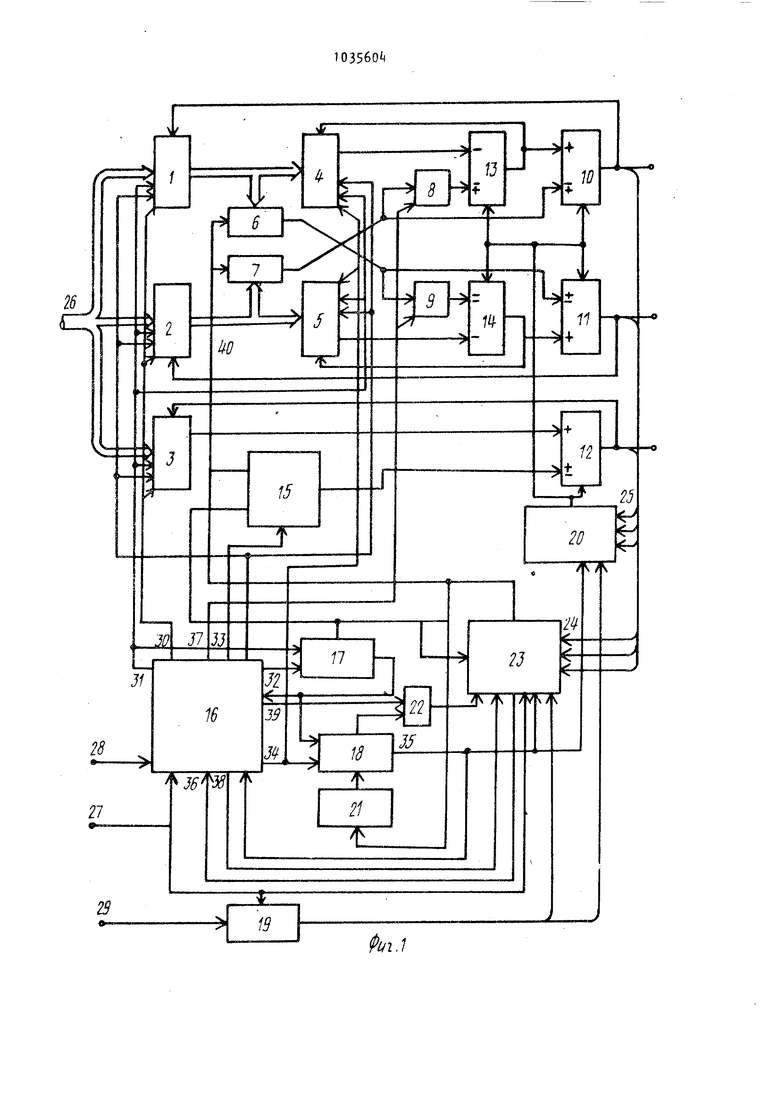

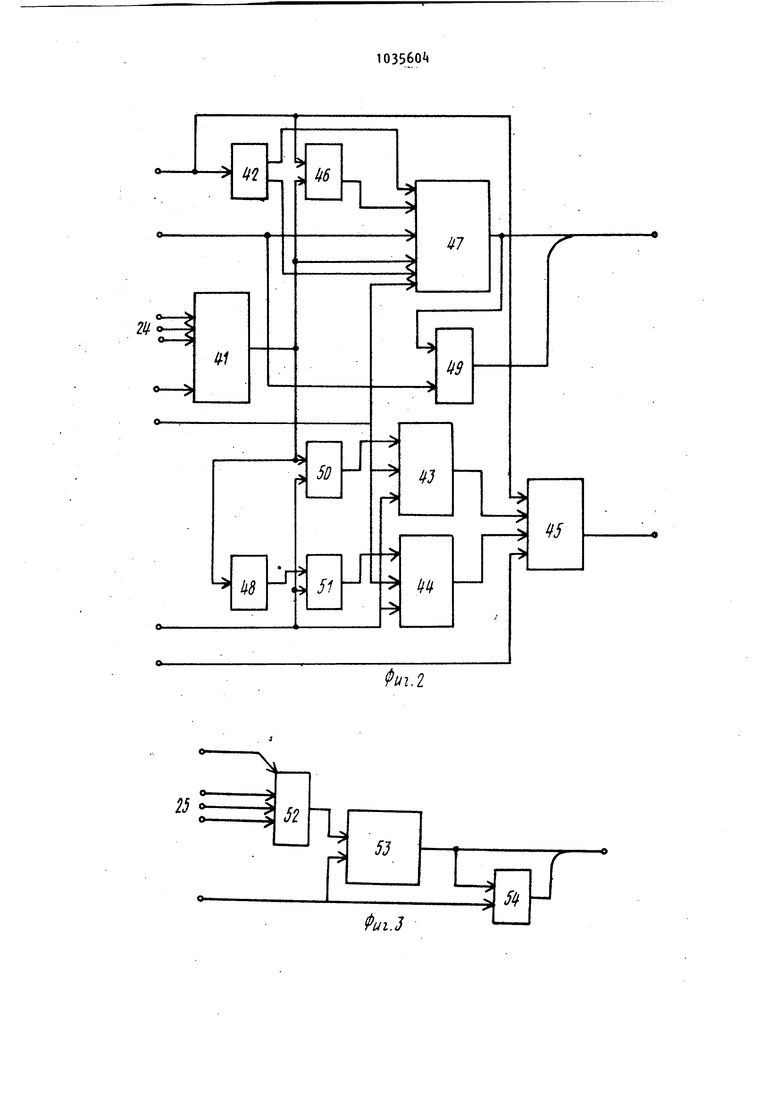

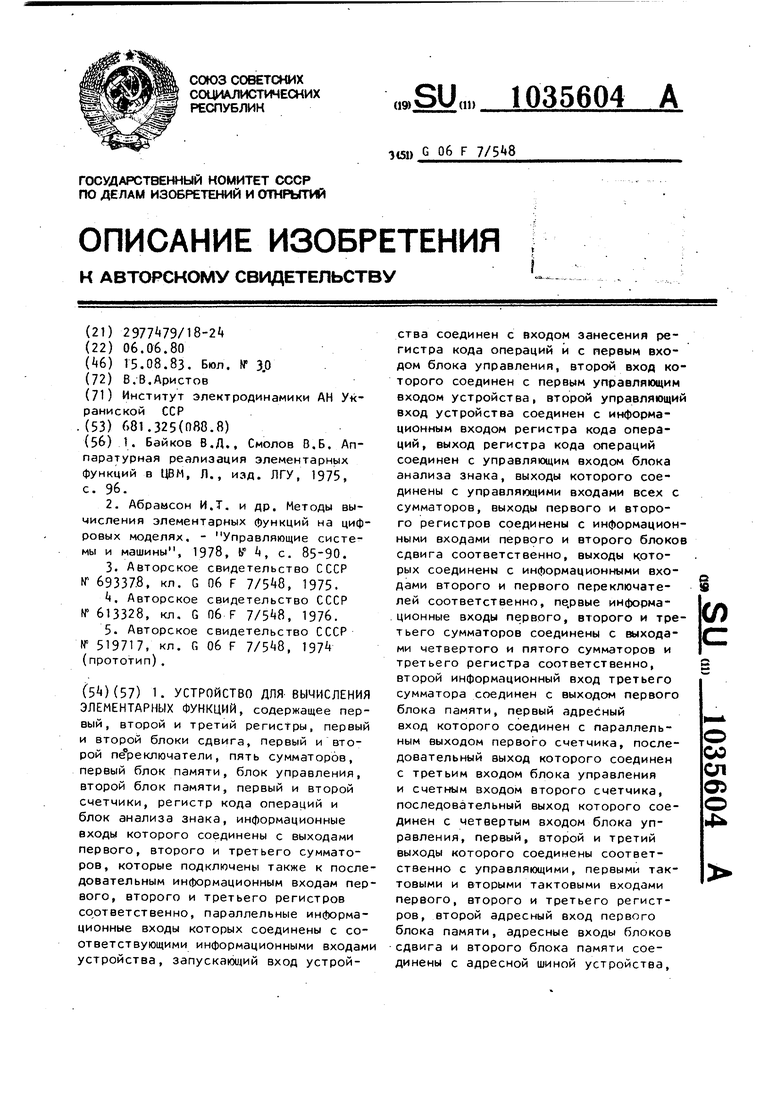

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - схема блока нормализации числа; на фиг. 3 схема блока анализа знака; на фиг. схема блока управления. вход первого разряда которого соединен с выходом первого элемента И-НЕ, первый вход которого соединен с третьим входом блока, четвертый вход блока соединен с вторым входом первого элемента И-НЕ и с третьим и четвертым входами второго разряда мультиплексора, четвертый вход первого разряда которого соединен с вторым входом второго разряда мультиплексора и с шиной сигнала 1 блока, пятый вход блока соединен со стробирующим входом мультиплексора и с входом элемента НЕ, выход которого соединен с первым входом второго элемента И-НЕ, выход которого соединен с входом элемента задержки, второй выход блока соединен с первым выходом генератора импульсов и с управляющим входом регистра, первый и второй информационные входы которого соединень с выходами соответственно первого и второго разрядов мультиплексора, первый адресный вход которого соединен с первыми входами первого и второго элементов И и с первым прямым выходом регистра, второй прямой выход которого соес вторым адресным входом муль9 . Устройство содержит первый 1, второй 2, третий 3i четвертый Ц и пятый 5 регистры, первый 6 и второй 7 блоки сдвига, первый 8 и второй 9 переключатели, первый 10, второй 11, третий 12, четвертый 13 и пятый 14 сумматоры, первый блок 15 памяти,блок 1б управления, первый 17 и второй 18 счетчики, регистр 19 кода операций, блок 20 анализа знака, второй блок 21 памяти, коммутатор 22 и блок 23 нормализации числа, информационные входы которого соединены с выходами первого 10, второго 11 и третьего 12 сумматоров и с соответствующими информационными входами 25 блока 20 анализа знака, выходы которого соединены с управляющими входами всех сумматоров 10-1.Выходы первого 10, второго 11 и третьего 12 сумматоров соединены с последовательными информационными входами первого 1, второго 2 и третьего 3 регистров соответственно, параллельные информационные входы которых соединены с информационными входами 2б устройства, запускающий вход 27 которого соединен с первым входом блока 1б управления, с входом занесения регистра 19 кода операций и с входом обнуления блока 23 норма-, лизации числа. Второй вход блока 1б управления соединен с первым управляющим входом 28 устройства, второй управляющий вход 29 которого соединен с информационным вхо- дом регистра 19 кода операций, выхо которого соединен с управляющим блока 20 анализа знака, и с операционным входом .блока 23 нормализации числа. Управляющие входы первого 1, второго 2 и третьего 3 регистров соединены с первым выходом 30 блока 1б управления, второй выход 31 которого соединен с первыми тактовыми Входами всех регистров 1-5 и со счетным входом первого счетчика 17, последовательный выход которогосоединен со счетным входом второго счетчика 18 ис третьим входом 32 блока 16 управления третий выход 33 которого соединен с вторыми тактовыми входами всех регистров 1-5. Четвертый выход З блока 1б управления соединен с управляющими входами четвертого и пятого 5 регистров и с управляющим входом второго счетчика 18, по

следовательньгй выход В5 которого соединен со стробирующими входами блока 20 анализа знака, блока 23 нормализации числа и с четвертым

5 входом блока 1б управления, пятйй вход 36 которого соединен с управляющим выходом блока 23 нормализации числа. Пятый выход 37 блока 1б-управления соединен с управляю0 щим входом первого блока 15 памяти, первый адресный вход которого соединен с параллельным выходом первого счетчика 17 и с адресным входом блока 23 нормализации числа,

15 управляющий вход которого соединен с шестым выходом 38 блока 16 управления , седьмой выход которого соединен с обнуляющим входом первого счетчика 17. Восьмой выход 39

20 блока 16 управления соединен с управляющим входом коммутатора 22, выход которого соединен с синхронизирующим входом блока 23 нормализации числа, информационные исходы которого по адресной шине 40 устройства соединены с адресными входами первого 6 и второго 7 блоков сдвига; с вторым адресным входом первого блока 15 памяти и с адресным входом

30 второго блока 21 памяти, выход которого соединен с параллельным входом второго счетчика 18, параллельный выход которого соединен с ин формационным входом коммутатора 22,

J, Девятый выход блока 16 управления соединен с управляющими входами первого 8 и второго 9 переключателей, выходы которых соединены с первыми информационными входами вертого 13 и пятого I сумматоров соответственно. Выход четвертого сумматора 13 соединен с первым информационным входом первого суммато ра 1P и с последовательным информационным входом четвертого регистра 4, выход которого соединен с вторым информационным входом четвертого сумматора 13. Выход пятого сумматора 1 соединен с первым информационным входом второго сумматора 11

50 и с последовательным информационным входом пятого регистра 5, выход которого соединен с вторым информационным входом пятого сумматора I. Выход первого регистра 1 соединен с

5 параллельным информацибнным входом четвертого регистра 4 и с информационным входом первого блока 6 сдвига, выход которого соединен с ин11формационным входом второго переключателя 9 и с вторым информацион ным входом второго сумматора 11. Вы ход второго регистра 2 соединен с параллельным информационным входом пятого регистра 5 и с информационным входом второго блока 7 сдвига, выход которого соединен с информационным входом первого переключателя 8 и с вторым информационным входом первого сумматора 10. Выход тре тьего регистра 3 соединен с первым информационным входом третьего сумматора 12, второй информационный вход которого соединен с выходом первого блока 15 памяти. Блок 23 нормализации числа (фиг содержит мультиплексор 41, двоичный счетчик А2, первый 3, второй Ц, третий 5 и четвертый 46 триггеры узел 47 памйти, элемент НЕ 8, схему 49 сравнения и два элемента И-НЕ 50 и 51. Выходы элементов НЕ 50 и 51 соединены с входами уста новки в 1 первого 43 и второго 44 триггеров соответственно, выходы которых соединены с информационными входами третьего триггера 45, выход которого является управляющим выходом блока. Информационные 24 и операционный входы блока 23 соединены с соответствующими входами мультиплексора 41, выход которого соединен с информационным входом че вертого триггера 46, первым адресным входом записи узла 47 памяти и с первым входом первого элемента И-НЕ 50 непосредственно, а с первым входом второго элемента И-НЕ 51 через элемент НЕ 48. Управляющий вход блока 23 нормализации числа со динен с вторыми входами элементов И-НЕ 50 и 51 и входами установки в О первого 43 и второго 44 триггеров, стробирующие входы которых и стробирующий вход узла памяти соединены с синхронизирующим входом блока 23. Адресный вход блока 23 соединен с первым входом схемы 49 сравнения и информационным входом узла 47 памяти, выход которого соединен с вторым входом схемы 4д срав нения, выход которой и выход узла (7 памяти являются информационными выходами блока 23. Стробирующий вход блока 23 соединен со стробирур цими входами третьего 45 и четверт го 46 триггеров и со счетным входом двоичного счетчика 42, прямой и i( инверсный выходы которого соединены соответственно с первым адресным входом считывания и вторым адресным входом записи узла 47 памяти, второй адресный вход считывания которого соединен с выходом четвертого триггера 46. Вход обнуления блока 23 соединен с входом установки в О третьего триггера 45. Блок 20 анализа знака (фиг. 3) содержит регистр 52, одноразрядный узел 53 памяти и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 54, выход которого и выход одноразрядного узла 53 памяти являются выходами блока 20. Стробирующий и информационнь1б 25 входы блока 20 соединены соответственно с управляющим и информационными входами регистра 52, выход которого соединен с первым адресным входом одноразрядного узла 53 памяти, второй адресный вход которого соединен с управляющим входом блока 20. Входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 54 соединены с выходом одноразрядного узла 53 памяти и управляющим входом блока 20 соответственно. Блок 16 управления (фиг. 4) содержит генератор 55 импульсов, регистр 5б, мультиплексор 57, четыре элемента И-НЕ 58-61, два элемента И 62 и 63, элемент НЕ 64, и элемент 65 задержки, выход которого соединен с первым выходом ЗО блока 1б. Первый вход блока 16 соединен с управляющим вхсщом генератора 55 импульсов, обнуляющим входом регистра 5б и с первым входом первого разряда мультиплексора 57, второй вход первого разряда которого соеДТинен с шиной сигнала О блока 16 и с первым входом второго разряда мультиплексора 57, третий вход первого разряда которого соединен с выходом первого элемента И-НЕ 58, первый вход которого соединен с третьим входам 32 блока 16. Четвертый вход блока 16 соединен с вторым входом первого з л€мента И-НЕ 58 и с третьим и четвертым входами второго разряда мультиплексора 57, четвертый вход первого разряда которого соединен с вторым входом второго разряда мультиплексора 57 и с шиной сигнала 1 блока 16. Пятый вход Зб блока 1б соединен со стробирующим входом мультиплексора 57 и с входом элемента НЕ 64, выход которого соединен с первым входом второго элемента И-НЕ 59, выход которого соединен с входом элемента б5 задержки. Второй выход блока 16 соединен с первым выходом генератора 55 импульсов и с управляющим входом регистра 56, первый и второй информ ационные входы которого соединены с выходами соответственно первого и второго раз рядов мультиплексора 57, первый адресный вход которого соединен с первыми в)5одами первого 62 и второго 63 элементов И и с первым прямым выходом регистра 5б, второй прямой выход которого соединен с вторым адресным входом мультиплексора 57, с первыми входами третьего 60 и четвертого 61 элементов И-НЕ, с шестым выходом38 блока 1б и с вторым входом первого элемента И б2, выход которого соединен с девятым выходом блока 1б. Четвертый выход 3 блока 16 соединен с выходом второго элемента И 63, второй вход которого соединен с вторым входом второго элемента И-НЕ 59 и седьмым выходом блока 16. Первый инверсный выход регистра 5б соединен с третьим входом второго элеме та И-НЕ 59 и вторым входом четвертого элемента И-НЕ б1, Второй инверс ный выход регистра 5б соединен с сед мым выходом блока 16. Второй выход генератора 55 импульсов соединен с восьмым выходом 39 блока 1б и вторым входом третьего элемента И-НЕбО, выход которого соединен с третьим выходом 33 блока 16. Второй вход блока 16 соединен с третьим входом четвертого элемента И-НЕ б1 .выход которого соединен с пятым выходом 37 блока 16. Последовательность работы устройства состоит в задании данных в виде кодов по информационным входам 2б устройства, управляющего и запускающего сигналов по первому управляющему 28 и запускающему 27 входам устройства соответственно, кода операций по второму управляющему входу 29 устройства и съеме данных с первого 1 , второго 2 и третье-: го 3 регистров после формирования импульсного сигнала р по управляюще му выходу бло.ка 23 нормализации числа. Работа устройства основывается на рекуррентных соотношениях ,v,2-N).{0)9. + y;l + 71 1 vr- niVf - U-i Vi- -x-i-i- l -..v i- rVci-) ...(-. ,х,,,-х;:; ..l.;); Ui-o i V С) где J - номер коррекции, j 1 ,2,3,...,m ; константы истинного значения аргумента, (Q ci u ; ,(--4 (акн ) -к/и Я--- (7) I - индекс итерации, принимаю щий целочисленные значения в диапазоне 0-п, где п - разрядность двоичного представления даннь1х. Реализация соотношений (1)-() с погрешностью до ошибок округления при вычислениях с двоичной разрядностью п эквивалентна соотношениям ,.., ,..-,,-4Хии)(8) в свою очередь, реализация соотношений 8 не приводит к появлению деформации вектора решения на любой итерации с индексом i, поэтому наборы итераций могут быть произвольными и задаваться как принудительно, например в виде одной итерации при генерировании функций с. шагом С- (7) так и автоматически, т.е. когда индексы i заранее не определы и формируются в процессе вычислений. Для определения индекса i, а также момента окончания итераций, служит блок 23 нормализации числа (фиг.2 На информационные входы 2Ц мультиплексора 1 поступают последовательные коды с выходов первого 10, второго П и третьего 12 сумматоров, представленные в дополнительном коде младшими разрядами вперед-. В соответствии с кодом операций (КОП) на выход мультцп ексора k передается кол с одного из указанных сумматореа Зыходньге коды мультиплексора 1 мО поедставлять как положительные, rai и отрицательные числа, примем знаковые разряды поступают последкмни , чап.эимер ;} O.OOOJOnOOOlO, б) I 1010001001 1 . 8 слумае положительного числа (а риа1-п Ci 1 необходимо определить ад Dec послепнего,начиная с младших рауояг -:,-н сямого левого, единичного оезрядй, а fljiR отрицательного числа (isapi;;i-:T (J ) адрес последнего, car-ore /.евогг), нулевого разряда. С з1с Л цг-лью ai-irJ iHSi/ipyeMoe число :,fv:vyr:; eT Hf. первый адресный вход I уллэ 47 памяти 7, выполнен;a,-;i-,;-fMcp. на --регистровом ЗУ ;:-. (SN 74170), Сост яние ногч:, сче 4;--i a 2 (сметного три ме-тяется по сигналу р только Г; , г;аждой итерации т.е, при эмали за кода числа информация с йпоес1-ог с- входа блока 23 нормалиойци;-- числа 4 поступая нв информа: п-;о-;нь1Й чход узла 47 памяти, запи:ь;зается а огну группу ячеек памяти 3 C-i;-vrbi8aHkie осуществляется из одно .М-;--ки памяти в.торой группы, а кото ovk; .зп --СЬ еалась информация на предыдуией -ггерации. Выбор ячейки памя -:-;.: -.3 группь: для считывания осущест яс:гс -.erseDTbis триггером i)6, н sO;cH)o.M запоминается информация о -исла Б предыдущей итерации. Адрес .ччеикч- памяти для группы заfii-uyi определяется значением разряда Рнал1/г;:ируемого числа. Так как на адоеснь й вход блока 23 нормализации чхсла по-ступают коды с параллельноО зьхода первого счетчика 17. определяющие номер текущего разряда, го, напр,и;мер, в ячейку памяти с адресом 00 записываются номера разрядов соответствующие информационно-;.У С разряда анализируемого чис ла, а 3 ячейку памяти с адресом 01 номеро рс;зрядов для информационных V S Чэазсядах анализируемого числа В KO-iije итерации, когда ана лиз:1р ется знаковьй разряд, двоичный ..че-чик -}. переключается, а сос тояние четвертого триггера 6 устанавпнзасг-.;р а соответствии со зна; овым (.; -:зрядом. ПОЭТОМУ ДЛЯ вэриамта п считывания ячейки памяти на после,г-ую1дей итерации будет 01, а , в.:;рианта о/- 00, В итоге, на .Л выходе узла памяти 47 присутстаует код номера подчеркнутого разряда соответственно для варианта . ff/. На данной очередной итерации номера разрядов, соответствующие информационному О, записываются а ячейку памяти с адресом 10, а соответствуюш,ие - в ячейку с адресом 11, что обуславливается ноаым состоянием двоичного счетчика 42. При отсутствии в узле 47 памяти входа сброса ячеек в памяти в О (для микросхем 155РП1) необходима дополнительная схема анализа на наличие всех единиц или нулей в коде af aл 1зиpyeмoгo числа, что выполняется путем занесения единичных разрядов через элемент И-НЕ 50 в первый триггер 3, а нулевых разрядов - .через элементы НЕ 48 и И-НЕ 5 во второй триггер 44. При одинаковых значениях всех разрядов анализируемого числа только один из триггеров 43 или 44 находится в единичном состоя;- ии, пс зтому на информационных входах третьего триггера 45, объединенных по схеме И-НЕ, не выполняется логика совпадения,и третий триггер 45 3 конце итерации по стробирующему входу устанавливается в единичное состояние, формируя на управляющем выходе блока 23 нормализации числа « сигнал р окончания вычислении. При обработке последовательных кодов в направлении, начиная с (ьпадших разрядов, блоки 6 и 7 сдвига представляют собой коммутаторы (мультиплексоры) , например, типа 155КП, которые необходимо блокировать для номеров текущих разрядов, больших n-f, чтобы старшие после запятой разряды сдвинутого кода соответствовали значению арифметического нуля. Для Формирования блокирующего блоки 6 и 7 сдвига сигнала используется схема 49 сравнения, осуществляющая сравнение кода текущего номера разряда с кодом номера теку1цей 1-1 итерации. Выход схемы 49 сравнения по адресной шине 40 устройства поступает на блоки 6 и 7 сдвига для блокировки. Анализ кода в блоке 23 нормализации числа осуществляется по синхронизирующему входу с поступлением при сигнала с выхода коммутатора 22. В исходное состояние третий триг: ер 45 по входу обнуления блока 23 нормализации числа устанавливается запускающим сигналом pf устройства, а пер вый 43 и второй 44 триггеры - по управляющему входу с шестого выхода 38 блока 16 управления (сигналом Г) . Для определения значения , рав ного + 1 или -1 , управляющего операциями Сложение или Вычитание все сумматоров, используется блок 20 ана лиза знака (фиг. 3). Разряды КОП, поступающие по второму управляющему входу 29 устройства, запоминаются в регистре 19 кода операций, откуда поступают на операционный вход блока 23 нормализации числа и управляющий вход блока 20 анализа знака. Знаковые разряды с выходов первого 10, второго 11 и третьего 12 сумматоров сигналом по. стробирующему входу блок 20 анализа знака (сигнал р.) в конце итераций запоминаются в регистре 52, откуда поступают на первый адрес ный вход одноразрядного блока 53 памяти , на второй адресный вход кото.рого по управляющему входу блока 20 анализа знака поступает КОП. В одноразрядном блоке 53 памяти ( представляющем собой, например, постоянное запоминающее устройство типа 155РЕЗ с коммутатором на выходе для организации типа 256-1 разряд) запи саны необходимые соотношения для выбора знаков во всех квадрантах для ка дой функции, чем задается стратегия выбора знака л для каждой-функции, т.е. обеспечивается сходимость процессов вычислений во всех квадрантах допустимой области определения функций. . Для задания q, равного +1 или -1 в формулах (1)-(8), служит элемент ИСКЛЮЧАЮ1ЦЕЕ ИЛИ 54, выход которого вместе с выходом одноразрядного бло ка 53 памяти образует противофазные (для тригонометрических функций) ил синфазные (для гиперболических и эк поненциальных функций) сигналы-управления группами сумматоров 10,13 и l1, 12, 14, С этой целью один из разрядов КОП, кодирующий значение q, поступает на второй вход элемента ИСКЛЮЧАЩЕЕ ИЛИ 54. Алгоритм функционирования устрой ства обеспечивается блоком 16 управ ления (фиг. 4). На первый вход блока 16 управления поступает запускающий сигнал р на второй вход - признак режима фун ционирования с первого управляющего входа 28 устройства ( признак режима функционального П{ еобразоваиия или режима функционального генерирования , на третий вход - сигнал р с последовательного выхода первого счетчика 17, на четвертый вход - си|- нал р с последовательного выхода второго счетчика 1В, на пятый вход сигнал р с управляющего выхода блока 23 нормализации числа. На первом выходе 30 блока 16., управления формируется сигнал С, задающий режим занесения информации . в регистры 1-3, на втором выходе 31 первая серия импульсов ТГ, на третвем выходе 33 - вторая серия импульсов на четвертом выходе. 34 - сиг Qj, задающий режим занесения информации в регистры 4 и 5 а также управлляющий занесением информации во второй счетчик 18, на пятом выходе 37 - сигнал Cg.; стробирующий первый блок 15 памяти, на шестом выходе 38 - сигнал R, поступающий на управляющий вход блока 23 нормализации числа, на седьмом выходе сигнал R, обнуляющий первый счетчик 17, на восьмом выходе 39 третья серия импульсов Т , на девяток выходе - сигнал Сщ, управляющий состоянием переключателей 8 и 9. , Запускающий сигнал р. задатчика, в качестве которого может быть, например, центральный процессор, деблокирует генератор S5 импульсов (фиг.4 разрешая формирование серий импуль- сов Т и Тр , Последовательность состояний блока 16 управления .может быть описана в виде графа из четырех вершин, соответствующих коду на выходе регистра 5б. Функции переходов реализуются с помощью мультиплексора 57. Переход блока 16 управления из одного состояния в другое осуществляется по положительному фронту первой серии импульсов 7Г. Граф содержит вершину начального состояния CQ, вершину подготовительCQ вершину предварительного этапа ного этапа С. и вершину корректирующего цикла С ЧГ как (фиг.2), в вычислений, после начале прихода р. 1, справедливо р, л р.1, 16 поэтому блок управления перехо- а этап С, на подготовительный через такт. как для р все еще так выполняется условие р -4 1 , - на предC Q, В этом случае варительныи этап 1б управления, несостояние блока смотря на поступление серии f, оста sTcK HesiSMeHHbiM до тех пор пока не прийдет либо только один сигнал p,,i после которого выполняется пере ход нэ вершину корректирующего цикла С,,; S либо сигналы р и р- , после ifoTopbix осуществляется переход на :japujMHy подготовительного этапа С,,„. л/)бо сигнал р,, , в результате че О о й полнйзтся переход на вершину на-1с5льного состчояния CjjQ. С «epuiMHb «орректируюьнего цикла С,,,, L-;o3;io;;(en переход иг вершину под Г; го1 и ельного зтапа С при поступneHiiK сигнала р либо на вершину на чэпь.ого состояния Cprt при поступле:- И -: Г;-- г Нала р, . Приоритет по сиг4:-1алу fv достигается подзчеи его на стробмрующий Бход мультиплексора 57; а;-и7О:;:еиного S например f на михросхе;-:а типзЛ55КП2 (SM ). Вьлодные сигналы, управлящме рабсчоч 1стройст8а J, формируются из состояний регистра 5б логическими сл-мами 59-65, Устоойс зо работает следующим об ПО информационным входам 2& и еторому управляющему входу 2S усУоойс- -8а эыдает данные Хо Ул :: ,-,-.,, ч также КОП соответственно, ДзнгПу-;, по совпадению сигналов С) и (- ; заносятоя в регистры а по 3 Огг у екающему сигналу р. - в ре гисгр (5 кода операций. В состоянии Сг..; формируется сигнал С(, который осуг1ает на управляющий вход зторо го с.-;стчика 8 для задания кода М-т из второго блока 21 памяти, где М змкос ь второго c-ieTMHKa 18, Кроме того, сигнал С совместно с Т обес пемчвает г|араллельное занесение М 1формйц1- и из первого 1 и второго 2 ре ги СОС в в четверть й k и пятый 5 регистры соответственно, ис:1ользу ются регистры, например, типа 155ИР (SN ). В сос-оянии С формируются сигна .1 серии Ъ ; обеспечивая сдвиги информации а регистрах 1-5( а тем самым и поразрядную обработку инфор ;&цИ1: и сумматорах lO-1i, При этом перекпочатели 8 и 9 находятся во оключгнном состоянии, так как отсут ствует блокирущий сигнал С;, iiOcTynaiOLUHfi на их управляющие входь „ (ледойЭ ельно 5 выполняется поразрядное вычисление соотношений (l)j, i2) и (S} , начиная с младших разрядос , причем отсчет разрядов 20 осуществляется первым счетчиком 17 по сери-иТГ. Результаты вычислений записываются: Xi°, v|f|и,о/у., в первый 1 , второй 2 и третий 3 регистры соответственно; Xi. четвертый ч и пятый 5 регистры соответственно. На последовательном выходе первого счетчика 17 формируется импульс переполнения р. при обработке последнего разряда, знакового, после которого осуществляется переход с вершины С.д в состояние, соответствуюи ее функ(ии перехода. При переходе в состояние С формируется сигнал С , блокирующий переключатели 8 и 9, поэтому в четвертом k и пятом Ц регистрах содержимое лишь циклически сдвигается, сохраняя знамения Х,,- и . 3 в первый 1 и второй 2 регистры записываются значения, соответствующие соотношению ( 3). Подсчет количества циклов осуществляется вторым счетчиком 18, импульс переполнения Ра с которого формируется на цикле. Максимальное состояние второго счетчика 18 дешифрируется коммутаюром 22, стробируемым сигналом TO по восьмому выходу блока 16 управления, поэтому на последнем цикле данной i-и итерации блоками анализа знака 20 и нормализации числа 23 осуществляется анйлиз аргумента ДЛЯ нахождения и кода i, поступакмцего на блоки сдвига 6 и 7 и памяти 15 и 21 для задания шага, выбора констант (7J и величины т. для последующей итерации, В случае, если код окажется равным 0,00000000 или 1 Л 1111111, на управляющем выходе блока 23 нормализации числа формируется сигнвл р, переводящий по серииj блок 16 управления в начальное состояние С Сигнал р, поступает также к задатчику (цепи выдачи не показань:} , который после считывания информации с регистров снимает сигнал р , блокируя генератор 55 импульсов и сбрасывая сигнал р установкой третьего триггера ч5 блока 23 нормализации числа в исходное состояние. Если из первый управлясщий вход 28 устройства поступает сигнал 0, то на пятом выходе 37 блока 1б управления формируется сигнал С,- еыьсо кого уровня, который блокирует первый блок 15 памяти, в результате чего содержимое третьего регистра 3 не изменяется от итерации к итерации, что необходимо для обеспечения режима функционального генериро вания. В этом случае истинная часто та f тригонометрических функций синуса и косинуса составляет . C,F nr(t+H()) где F - тактовая частота генератора 55 импульсов блока 1б у равления; разрядность устройства; определяется округлением сверху величины - Мо бли жайшего нечетного целого числа для положительных зн чений, или до нуля для отр цательных значений. При реализации соотношений { 8) о сутствует деформация .вектора решения на любой итерации с индексом i, в связи с чем упрощается сходимость вычислений, повышается быстродействие за счет меньшего числа требуемых итераций, увеличивается диапазон изменения аргумента и появляется возможность генерирования функций с дискретным шагом без накопления методической погреижости, Предлагаемое устройство последовательного типа является многофункциональным и может быть применено в качестве функциональных процессоров и расширителей для микро- и мини-ЭВМ общего и специального применения, в том числе для решения задач спектрального анализа сигналов с помощью БПФ, для преобразования прямоугольных координат в полярные и наоборот, в системах управления движением и робототехнике, для вращения координат и векторов, для синтеза криволинейных поверхностей в станках с программным управлением и т.п.

Авторы

Даты

1983-08-15—Публикация

1980-06-06—Подача