00 ос

ОС ОС ОС

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессоров через общую память в многопроцессорной системе | 1984 |

|

SU1231508A1 |

| Многопроцессорная вычислительная система | 1982 |

|

SU1168960A1 |

| Устройство для обслуживания запросов | 1987 |

|

SU1437864A1 |

| Устройство для обмена информацией | 1984 |

|

SU1180905A1 |

| Устройство для загрузки групповых данных | 1986 |

|

SU1328816A1 |

| Устройство для сигнализации между процессорами | 1991 |

|

SU1837304A1 |

| Устройство для распределения заданий процессорам | 1990 |

|

SU1780087A1 |

| Устройство для распределения заявок по процессорам | 1982 |

|

SU1121671A1 |

| Устройство управления микропрограммной ЭВМ | 1989 |

|

SU1691840A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1291983A1 |

Изобретение относится к области вычислительной техники и может быть использовано в автоматизированных : системах управления в качестве модуля обработки информации Целью изобретения является расширение функцио нальных возможностей за счет динамического переопределения приоритетов процессоров при обработке одномерных и многомерных структур данных, Для этого в микропроцессорную систему, содержащую микропроцессоры, оперативные запоминающие устройства, общие оперативные запоминающие уст- .. ройства, устройства для сопряжения процессоров через общую память, дополнительно введен блок управления режимом, состоящий из дешифратора, триггера запрета, триггера запуска, первого и второго элементов И и триггера блокировки. 1 з,п. ф-лы, 5 ил I (Г С

N

Изобретение относится к вычислительной технике, может быть использовано в автоматизированных системах управления в качестве модуля обработки информации и является дополнительным к авТоСВо №

Целью изобретения является расширение функциональных возможностей за счет динамического переопределения приоритетов процессоров при обработке одномерных и многомерных структур данных.

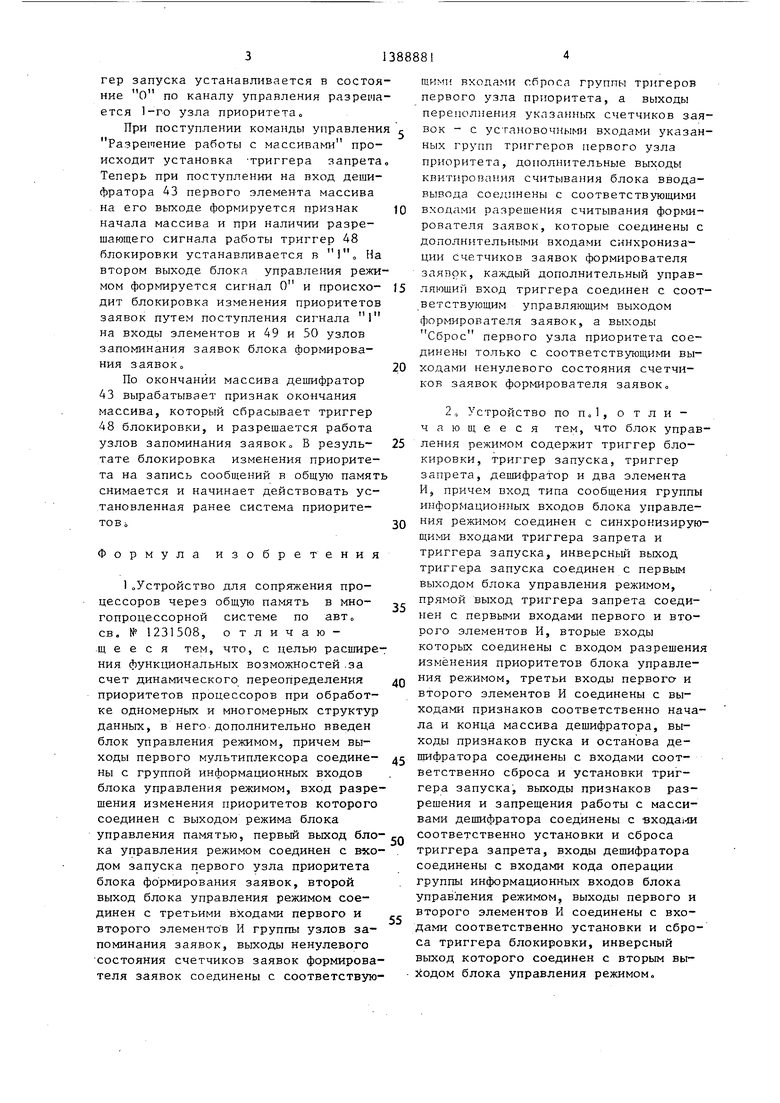

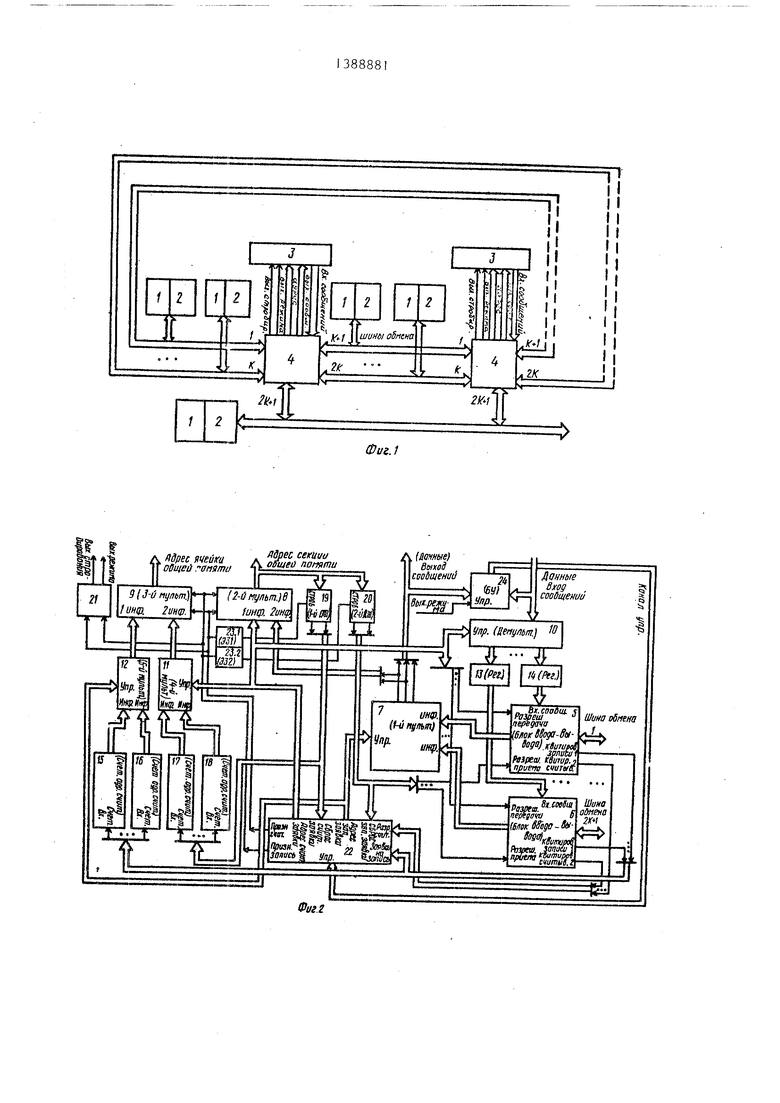

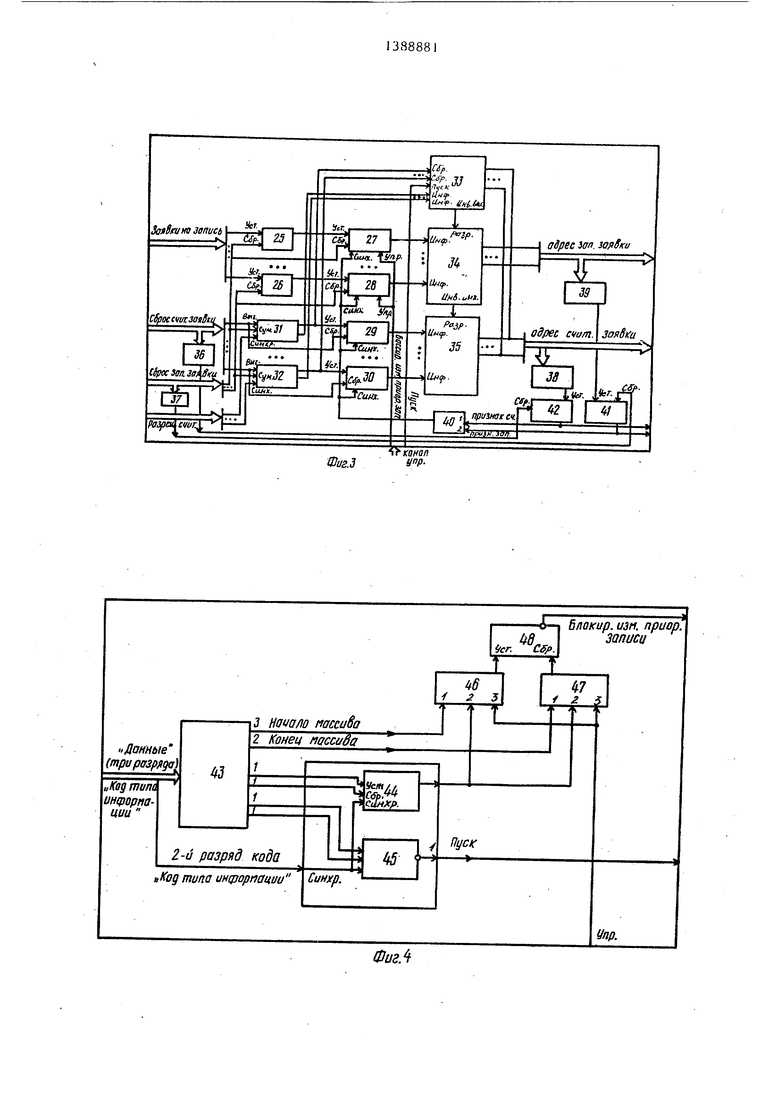

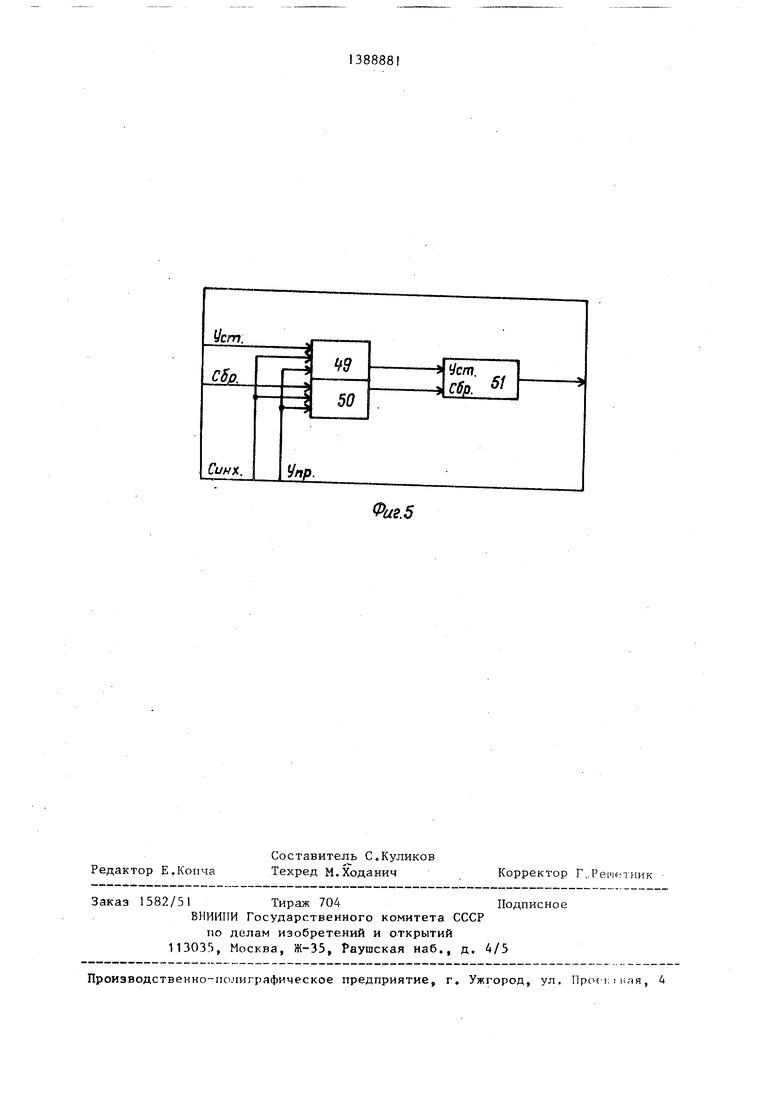

На фиГо изображена блок-схема многопроцессорной системы с использованием устройства для сопряжения процессоров; на фиг„2 - структурная схема устройства для сопряжения процессоров через общую память; на фиГоЗ - функциональная схема блока формирования заявок; на фиг.4 - функциональная схема блока управления режимом; на фиг„5 - функциональная схема узла запоминания заявок

Предлагаемое устройство содержит микропроцессоры I, один из которых центральный, местные оперативные запоминающие устройства, (ОЗУ) 2, общие оперативные запоминающие устройства 3, устройство А для сопряжения процессоров через общую йамять, содержащее первый блок 5 ввода-вьгоода, (2К+1)-й блок 6 вво- да-вьюода, первый 7, второй В и третий 9 мультиплексоры, демультиплек- сор 10, четвертый 11 и памяти 12 мультиплексоры, первый регистр 13,, (2К+Г)-й регистр 14, первый счетчик 15 адреса считьшания., (2К+1)-й счетСамостоятельно блок управления режимом не может обеспечить непрерывное считывание сообщений из общей памяти, так как это осуществляется автоматически под управлением блока формирования заявок Задача блока управления режимом состоит в том, чтобы принять адресуемое ему сообщение (признаки код типа информации и данные) и проан;1лизировать коды, содержапщеся в них о Факт необходимости анализа признака данные определяется приемом кодов 010, 011,110,

чик 16 адреса считывания, первый счетчик 17 адреса записи, (2К-И)-й счетчик 18 адреса записи, первый 19

и второй 20 дешифраторы, блок 21

управления памятью, блок 22 формирования заявок, первьш 23„1 и второй 23,2 элементы задержки, блок 24 управления режимом

Блок формирования заявок содержит первый триггер 25 первой группы, (2К+1)-й триггер 26 первой группы, первый узел 27 запоминания заявок, (2К+1)-й узел 28 запоминания заявок,

первый триггер 29 второй группы, (2К+1)-й триггер 30 второй группы, первый счетчик 31 заявок, (2К+1)-й счетчик 32 заявок, первый 33, второй 34 и третий 35 узлы приоритета, первый 36, второй 37, третий 38, четвертый 39 и пятьц 40 элементы ИЛИ, триггеры 41 и 42

Блок управления режимом содержит дешифратор 43, триггер 44 запрета,

триггер 45 запуска, первый 46 и второй 47 элементы И, триггер 48 блоки- роркИг

Узел запоминания заявок содержит первый 49 и второй 50 элементы

И, триггер 51

Устройство функционирует следующим образом

Функционирование блока управления режимом происходит под действием сигналов, сформированных в управляющей части форматов сообщений, передаваемых по выходу Выход сообщений устройства в общую память Формат этих сообщений следующий:

0

5

111 в признаке код типа информации Команда управления Начало масива в виде кода 111ХХХХХ содержится в трех первых разрядах признака Данные, команда управления Конец массива - в виде кода ОООХХХХХ, команда управления Пуск - в виде кода ПОХХХ, а команда управления Стоп - в виде кода 101ХХХХ с запоминанием в триггере запуска.

Устройство начинает работать после того, как на блок управления режимом поступает команда Пуск Тригrep запуска устанавливается в состояние о по каналу управления разрешается 1-го узла приоритета о

При поступлении команды управлени Разрешение работы с массивами происходит установка триггера запрета Теперь при поступлении на вход дешифратора 43 первого элемента массива на его выходе формируется признак начала массива и при наличии разрешающего сигнала работы триггер 48 блокировки устанавливается в 1 На втором выходе блока управления режимом формируется сигнал О и происхо- дит блокировка изменения приоритетов заявок путем поступления сигнала на входы элементов и 49 и 50 узлов запоминания заявок блока формирования заявок

По окончании массива дешифратор 43 вырабатывает признак окончания массива, который сбрасывает триггер 48 блокировки, и разрешается работа узлов запоминания заявок В резуль- тате блокировка изменения приоритета на запись сообщений в общую памят снимается и начинает действовать установленная ранее система приоритетов ь

Формула изобретения

2, Устройство по п„1, о т л и - чающееся тем, что блок управления режимом содержит триггер блокировки, триггер запуска, триггер запрета, дешифратор и два элемента И, причем вход типа сообщения группы информационных входов блока управления режимом соединен с синхронизирующими входами триггера запрета и триггера запуска, инверсный выход триггера запуска соединен с первым выходом блока управления режимом, прямой выход триггера запрета соединен с первыми входами первого и второго элементов И, вторые входы которых соединены с входом разрешени изменения приоритетов блока управления режимом, третьи входы первого- и второго элементов И соединены с выходами признаков соответственно начала и конца массива дешифратора, выходы признаков пуска и останова дешифратора соединены с входами соответственно сброса и установки триггера запуска, выходы признаков разрешения и запрещения работы с массивами дешифратора соединены с входа1-ш соответственно установки и сброса триггера запрета, входы дешифратора соединены с входами кода операции группы информационных входов блока управления режимом, выходы первого и второго элементов И соединены с входами соответственно установки и сброса триггера блокировки, инверсный выход которого соединен с вторым выходом блока управления режимом.

адрес сепии 41} понята

Фиг.З

Данные (три paspfiga.

Кад типй

инфорна- ции

2-й разряд кода

я Код типа инсрорпаиии

гканап упр.

Блокир.изн. приор запаса

Шр.

Фиг.б

| Устройство для сопряжения процессоров через общую память в многопроцессорной системе | 1984 |

|

SU1231508A1 |

Авторы

Даты

1988-04-15—Публикация

1986-03-04—Подача