та своего канала, выход триггера является соответствующим сигнальным выходом устройства и подключен к инверсным входам элементов запрета всех подканалов данного канала, выходы элементов запрета являются соответствующими информационными выходами устройства, выход элемента ИЛИ первого подканала группы является соответствующим информационным выходом устройства, выход элемента ИЛИ второго подканала устройства соединен с прямым входом элемента запрета своего подканала группы, прямой вход элемента запрета каждого подканала группы, начиная с второго, соединен с выходом, начиная с первого, узла приоритета данного канала, выход переполнения счетчика первого подканала группы соединe с единичным входом триггера данного канала, нулевой вход триггера каждого канала является соответствующим входом конца обслуживания устройства, и соединен с дополнительным элементом ИЛИ первого подканала группы данного канала, выход которого соединен с вычитающим Езходом счетчика своего подканала группы, второй вход дополнительного элемента ИЛИ первого подканала группы соединен с соответствующим ответным входом устройства.

Недостатком известного устройства, является узкая область применения. Действительно, в прототипе лишь один канал может стать критическим, требующим первоочередного обслуживания, в то время как при определенных ситуациях возможно с точки зрения пользователя требование предоставления ряду каналов требования критичности. В работе прототипа также возникают ситуации, при которых работа прототипа неясна, и некорректна: так, недостатком прототипа является отсутствие гистерезиса при включении и выключении критического потока - первая же после включения обслуженная заявка, выводит поток из состояния критического, а первая же вновь поступившая заявка снова возвращает этот поток в критическое состояние; этот факт затрудняет, а в некоторых ситуациях, а связи с нерешенными вопросами взаимодействия устройства с процессорами (приведенными при обсуждении эффективности заявляемого устройства) затрудняет выбор объема буферных регистров по потокам заявок, и нарушает корректность работы прототипа. Процедура обслуживания заявок, обеспечиваемая прототипом, таким образом, является недостаточно гибкой для организации распределения заявок (заданий) процессорам при произвольных требованиях пользователя к критичности отдельных потоков и критериях этой критичности.

Целью изобретения является расширение области применения за счет обслуживании запросов в зависимости от частоты их поступления.

Поставленная цель достигается тем, что в устройство для распределения заданий

0 процессорам, содержащее каналы, каждый из которых содержит узел приоритета и группы подканалов, каждый из которых содержит элемент ИЛИ и счетчик, причем запросные входы канала соединены с

5 суммирующими входами счетчиков соответ ствующих подканалов, в каждом подканале выходы счетчика соединены с входами элемента ИЛИ своего подканала, выход которого является первым выходом подканала,

0 введены в каждый канал регистр,генератор тактовых импульсов, распределитель импульсов, группа узлов выбора задания, блок определения минимума, блок сравнения, элемент И, формирователь импульсов,

5 два дешифратора, две группы элементов И, элемент ИЛИ и коммутатор, причем в каждый подканал введены два регистра, два блока сравнения, два формирователя импульсов, два элемента И и триггер, причем

0 в каждом канале устройства первые и вторые выходы подканалов соединены соответственно с первой и второй группой входов коммутатора, выходы узла приоритета подключены к информационным входам

5 регистра, выходы которого соединены с входами первой группы блока сравнения и с первыми группами входов узлов выбора задания группы, вторые группы входов которых являются информационными входами

0 канала, первые входы - ответными входами канала, а вторые выходы являются информационными выходами канала и соединены с входами блока определения минимума, первая группа выходов которого соединена

5 с первой группой входов блока сравнения и с входами первого дешифратора, а вторая группа выходов блока определения минимума соединена с входами второго дешифратора, выходы первого и второго

0 дешифраторов соединены соответственно с первыми входами элементов И второй и первой групп, вторые входы которых соединены с выходом формирователя импульсов, выходы элементов И первой группы соединены с вторыми входами соответствующих узлов выбора задания, и являются выходами управляющими канала, выходы элементов И второй группы соединены с вычитающими входами счетчиков соответствующих подканалов, выход генератора тактовых импульсов соединен с входом распределителя импульсов, первый выход которого подключен к третьим входам всех узлов выбора задания, и к синхровходу регистра, второй выход - к первому входу элемента И, второй вход и выход которого соединены соответственно с выходом блока сравнения и с входом формирователя импульсов, в каждом подканале канала выходы первого и второго регистров соединены с первыми входами соответственно первого и второго блоков сравнения вторые входы которых подключены к выходам счетчика, выходы первого и второго блоков сравнения соединены соответственно с входами первого и второго формирователей импульсов, выходы которых соединены соответственно с первыми входами первого и второго элементов И, выходы которых соединены соответственно с единичным и нулевым входами триггера, прямой и инверсный выходы которого соединены соответственно с вторыми входами второго и первого элементов И, прямой выход триггера является вторым выходом соответствующего подканала, кроме этого в каждом канале вторые выходы подканалов соединены с входами элемента ИЛИ, выход которого соединен с управляющим входом коммутатора, сигнальным входом узла приоритета и является сигнальным выходом канала устройства.

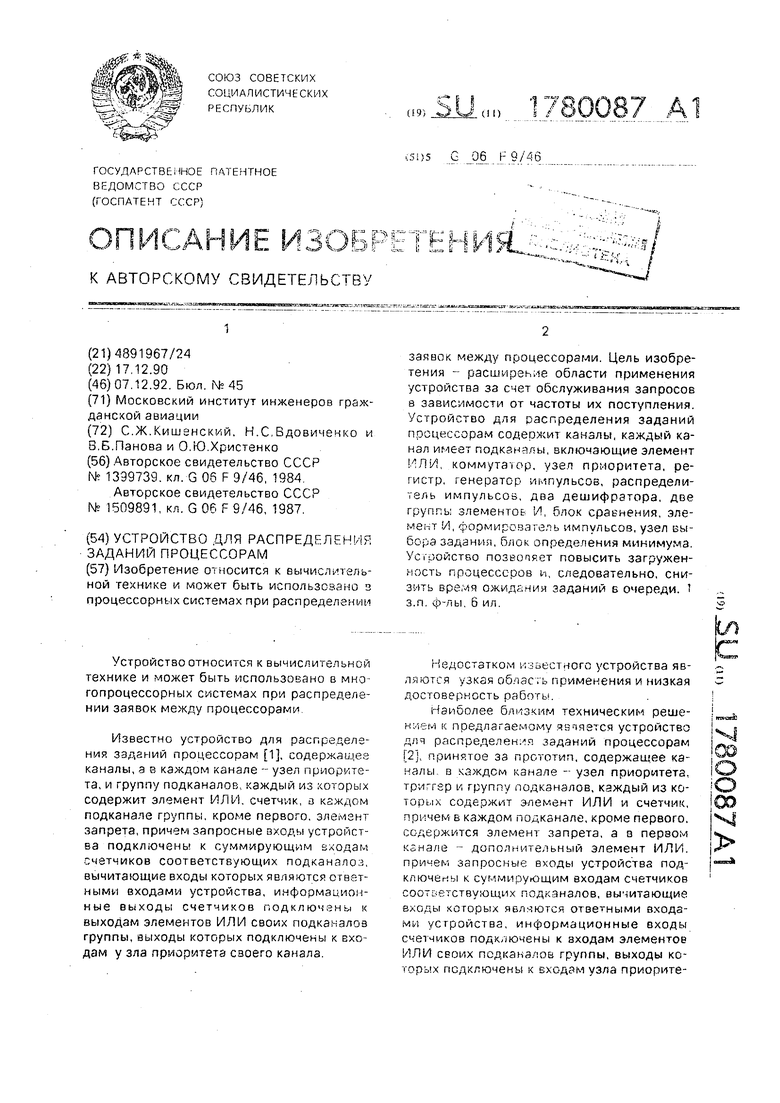

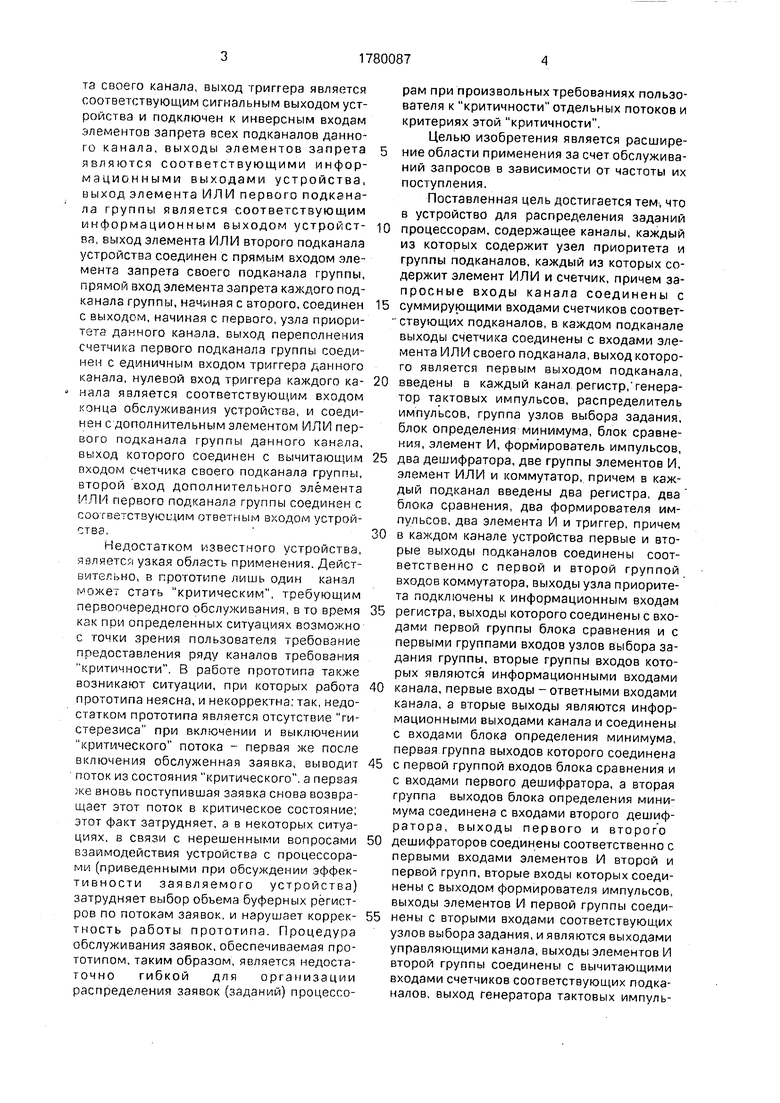

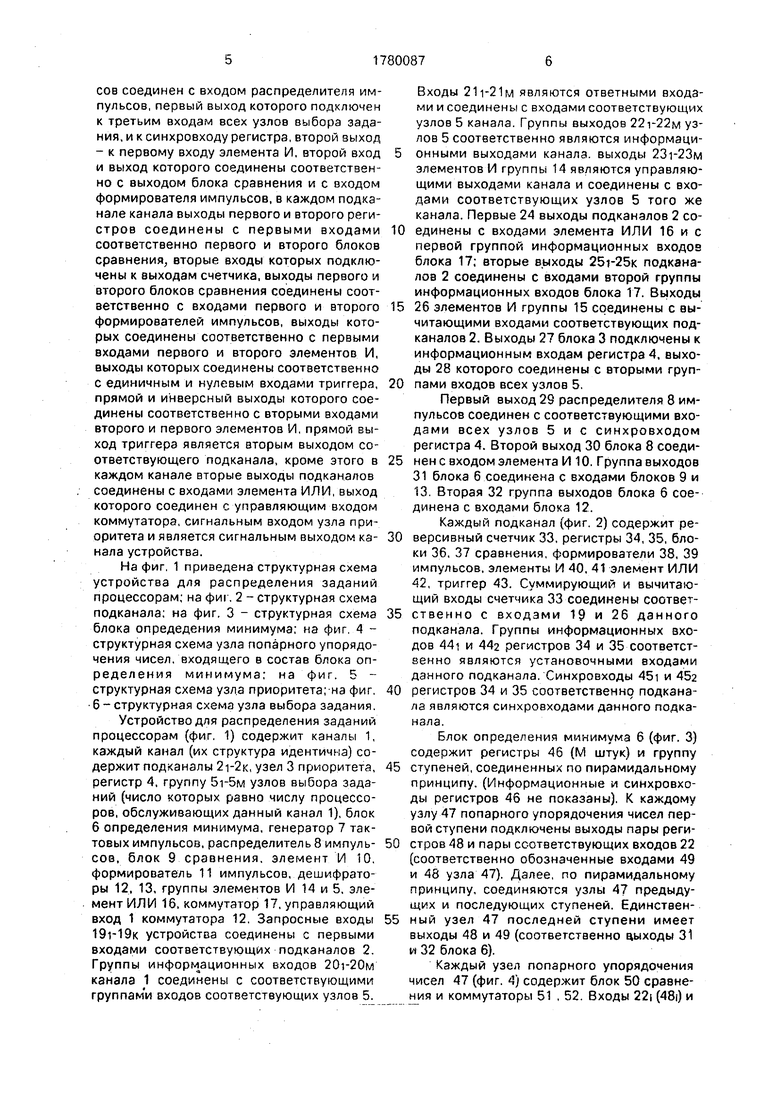

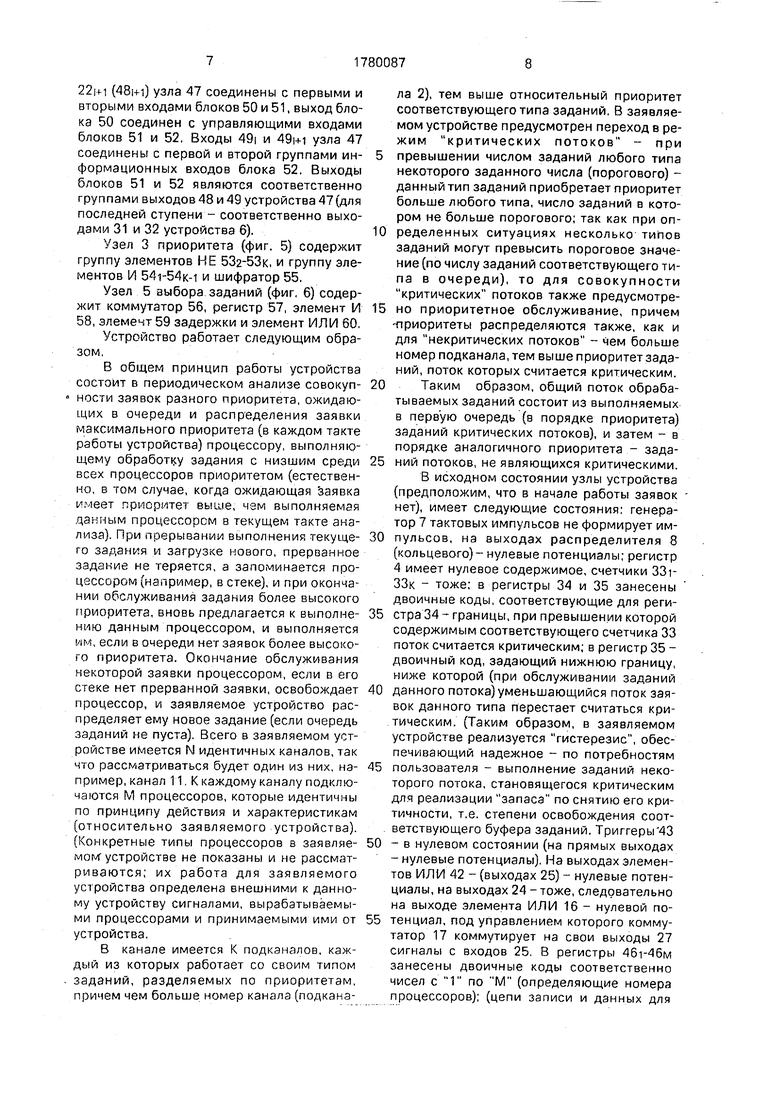

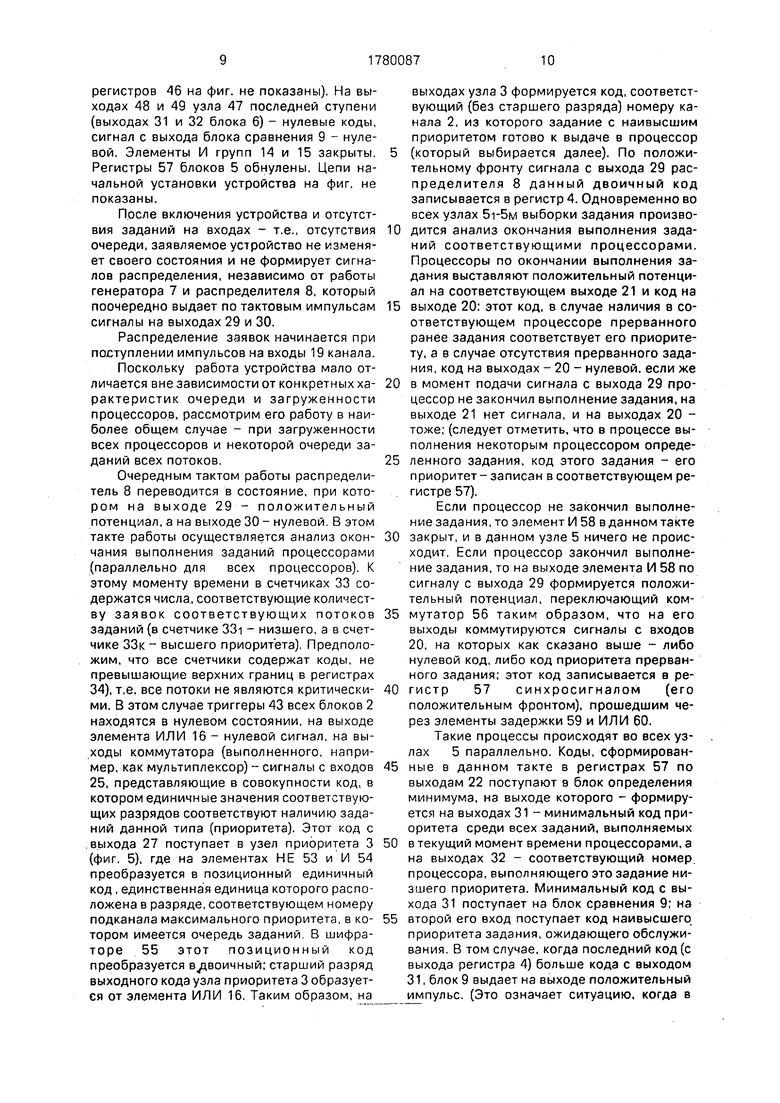

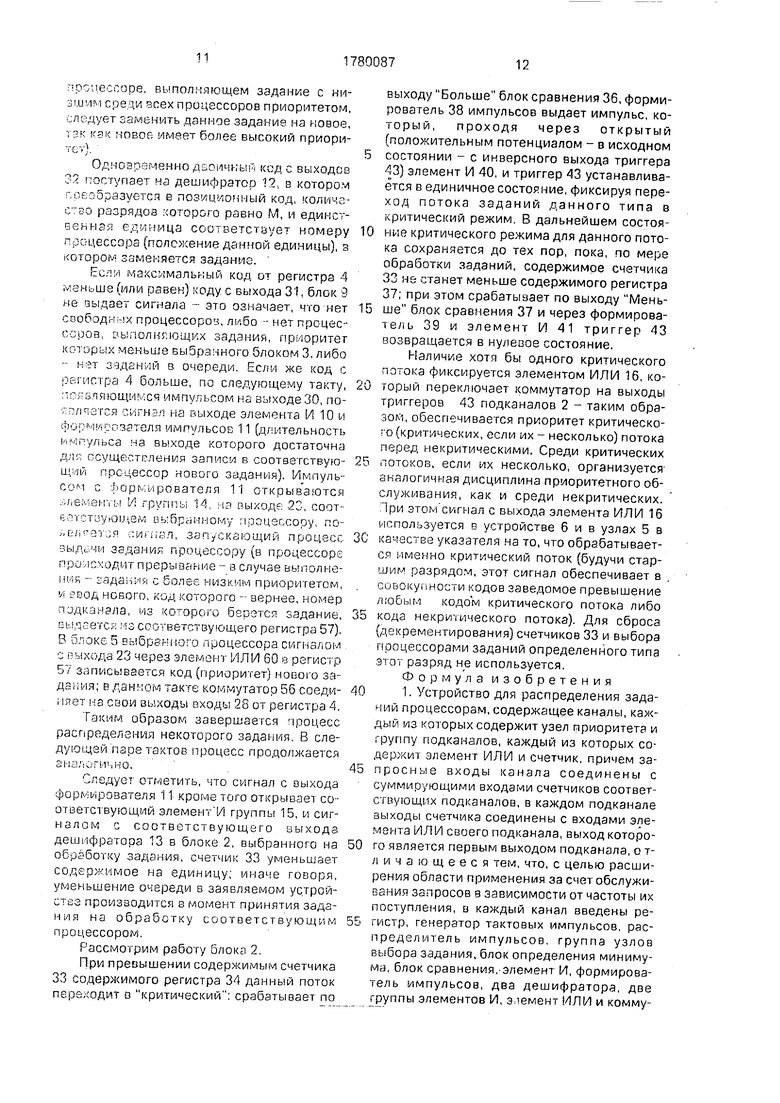

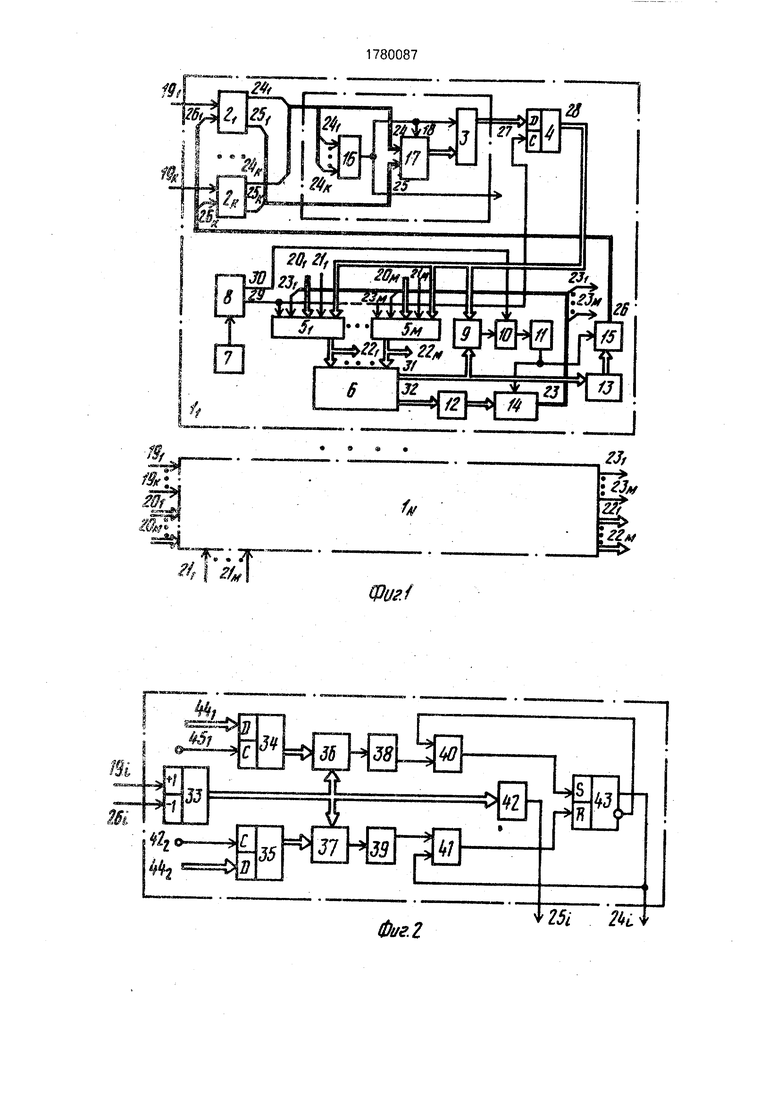

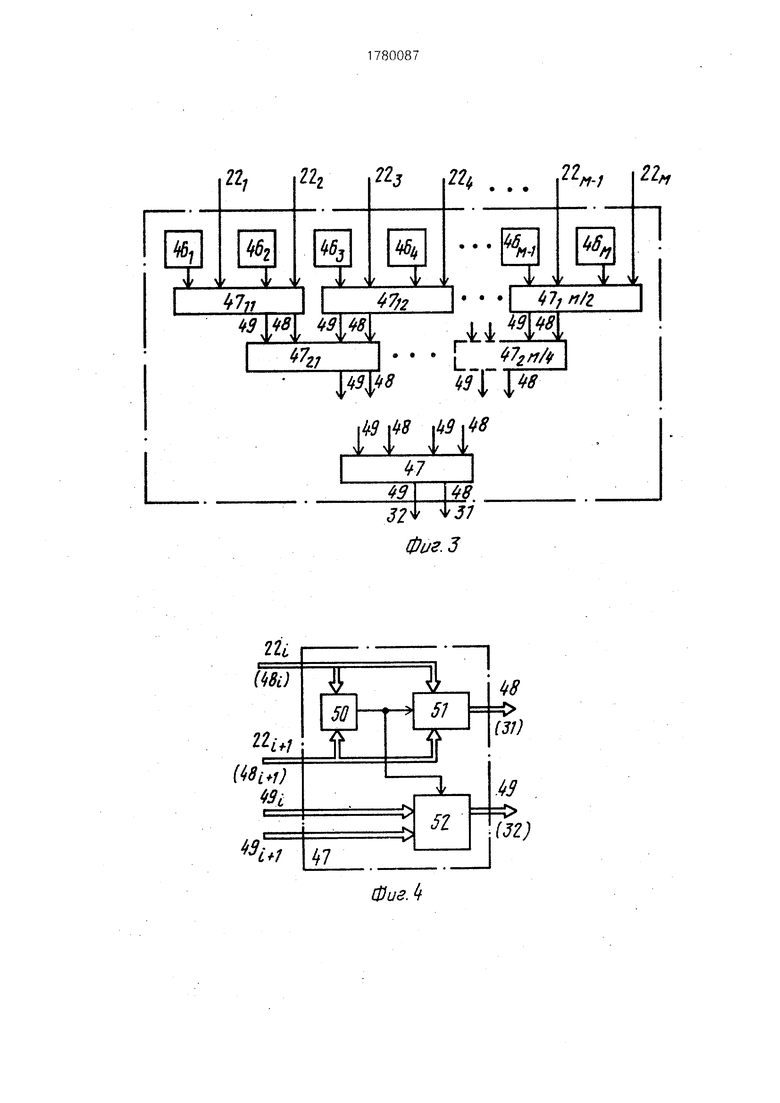

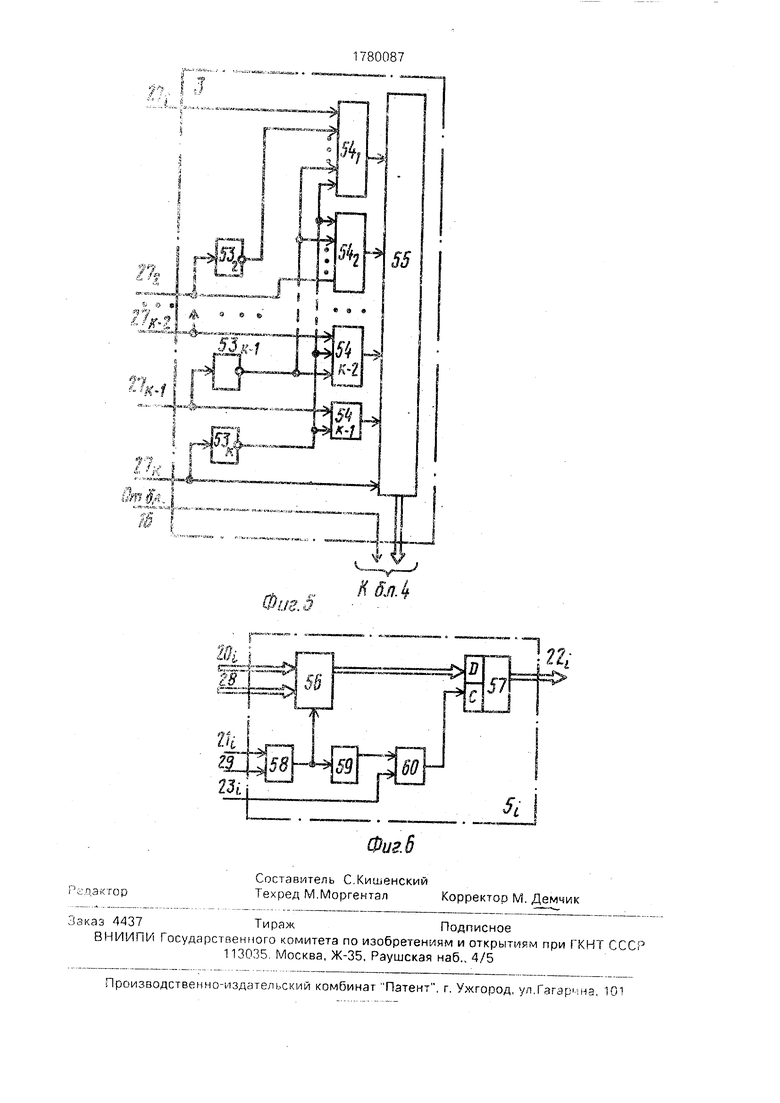

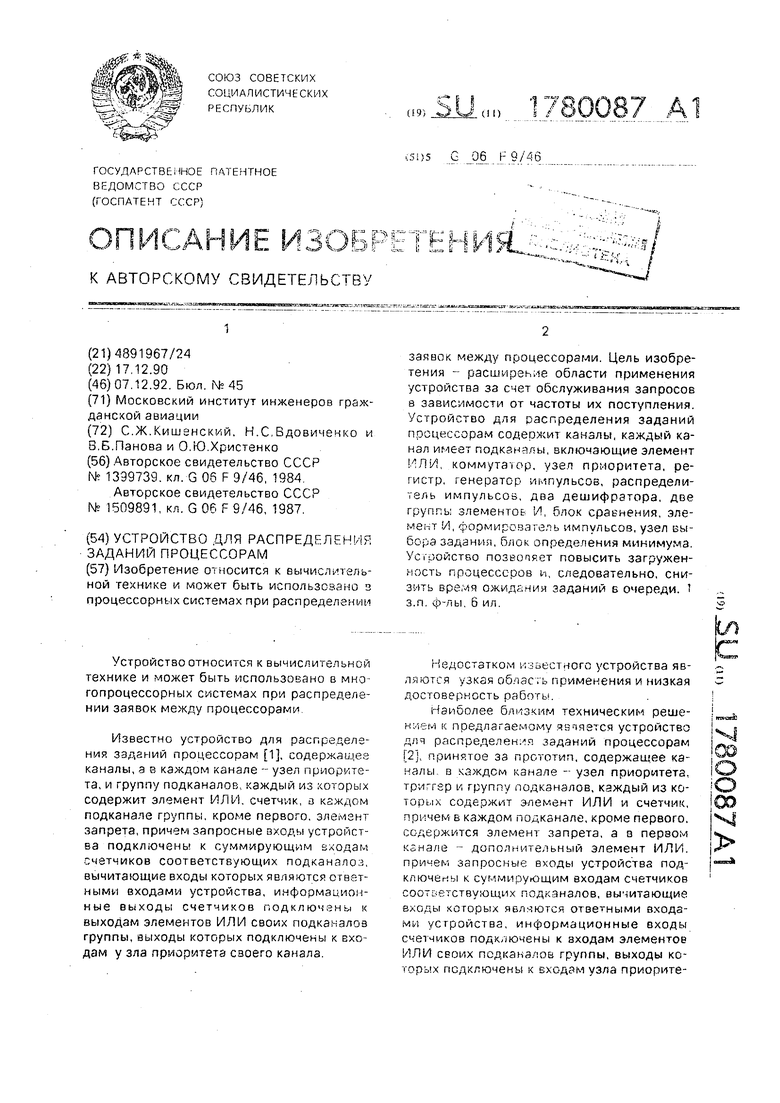

На фиг, 1 приведена структурная схема устройства для распределения заданий процессорам; на фиг, 2 - структурная схема подканала; на фиг. 3 - структурная схема блока опредедения минимума; на фиг. 4 структурная схема узла попарного упорядочения чисел, входящего в состав блока определения минимума; на фиг. 5 структурная схема узда приоритета;-на фиг, 6 - структурная схема узла выбора задания.

Устройство для распределения заданий процессорам (фиг. 1) содержит каналы 1, каждый канал (их структура идентична) содержит подканалы 21-2к, узел 3 приоритета, регистр 4, группу Бгбм узлов выбора заданий (число которых равно числу процессоров, обслуживающих данный канал 1), блок 6 определения минимума, генератор 7 тактовых импульсов, распределитель 8 импульсов, блок 9 сравнения, элемент И 10, формирователь 11 импульсов, дешифраторы 12, 13, группы элементов И 14 и 5, элемент ИЛИ 16. коммутатор 17, управляющий вход 1 коммутатора 12, Запросные входы 191-19к устройства соединены с первыми входами соответствующих подканалов 2. Группы информационных входов 201-20м канала 1 соединены с соответствующими группами входов соответствующих узлов 5.

Входы 21i-2lM являются ответными входами и соединены с входами соответствующих узлов 5 канала. Группы выходов 22i-22M узлов 5 соответственно являются информационными выходами канала, выходы 231-23м элементов И группы 14 являются управляющими выходами канала и соединены с входами соответствующих узлов 5 того же канала. Первые 24 выходы подканалов 2 соединены с входами элемента ИЛИ 16 и с первой группой информационных входов блока 17; вторые выходы 251-25к подканалов 2 соединены с входами второй группы информационных входов блока 17. Вь|ходы

5 26 элементов И группы 15 соединены с вычитающими входами соответствующих подканалов 2. Выходы 27 блока 3 подключены к информационным входам регистра 4. выходы 28 которого соединены с вторыми груп0 пами входов всех узлов 5,

Первый выход 29 распределителя 8 импульсов соединен с соответствующими входами всех узлов 5 и с синхровходом регистра 4. Второй выход 30 блока 8 соединен с входом элемента И 10. Группа выходов 31 блока 6 соединена с входами блоков 9 и 13. Вторая 32 группа выходов блока 6 соединена с входами блока 12.

Каждый подканал (фиг. 2) содержит реверсивный счетчик 33, регистры 34, 35, блоки 36, 37 сравнения, формирователи 38, 39 импульсов, элементы И 40, 41 элемент ИЛИ 42, триггер 43. Суммирующий и вычитающий входы счетчика 33 соединены соответственно с входами 19 и 26 данного подканала. Группы информационных входов 44i и 442 регистров 34 и 35 соответственно являются установочными входами данного подканала. Синхровходы 45i и 452

0 регистров 34 и 35 соответственно подканала являются синхроаходами данного подканала.

Блок определения минимума 6 (фиг. 3) содержит регистры 46 (М штук) и группу

5 ступеней, соединенных по пирамидальному принципу. (Информационные и синхровходы регистров 46 не показаны), К каждому узлу 47 попарного упорядочения чисел первой ступени подключены выходы пары регистров 48 и пары соответствующих входов 22 (соответственно обозначенные входами 49 и 48 узла 47). Далее, по пирамидальному принципу, соединяются узлы 47 предыдущих и последующих ступеней. Единственный узел 47 последней ступени имеет выходы 48 и 49 (соответственно выходы 31 и 32 блока 6).

Каждый узел попарного упорядочения чисел 47 (фиг. 4) содержит блок 50 сравнения и коммутаторы 51 , 52. Входы 22i (48i) и

22i+i (48n-i) узла 47 соединены с первыми и вторыми входами блоков 50 и 51, выход блока 50 соединен с управляющими входами блоков 51 и 52, Входы 49i и 49i+i узла 47 соединены с первой и второй группами информационных входов блока 52, Выходы блоков 51 и 52 являются соответственно группами выходов 48 и 49 устройства 47(для последней ступени - соответственно выходами 31 и 32 устройства 6).

Узел 3 приоритета (фиг, 5) содержит группу элементов НЕ 532-53к, и группу элементов И 541-54к-1 и шифратор 55,

Узел 5 выбора заданий (фиг, 6) содержит коммутатор 56, регистр 57, элемент И 58, элемент 59 задержки и элемент ИЛИ 60,

Устройство работает следующим образом,

В общем принцип работы устройства состоит в периодическом анализе совокупности заявок разного приоритета, ожидающих в очереди и распределения заявки максимального приоритета (в каждом такте работы устройства) процессору, выполняющему обработ1 :у задания с низшим среди всех процессоров приоритетом (естественно, в том случае, когда ожидающая заявка и.меет ,пр1.10ритет выше, чем выполняемая данным процессором в текущем такте анализа). При прерывании выполнения текущего задания и загрузке нового, прерванное задание не теряется, а запоминается процессором (например, в стеке), и при окончании обслуживания задания более высокого приоритета, вновь предлагается к выполнени,ю данным процессором, и выполняется им, если в очереди нет заявок более высокого приоритета. Окончание обслуживания некоторой заявки процессорам, если в его стеке нет прерванной заявки, освобождает процессор, и заявляемое устройство распределяет ему новое задание (если очередь заданий не пуста). Всего в заявляемом устройстве имеется N идентичных каналов, так что рассматриваться будет один из них, например, канал 11. К каждому каналу подключаются М процессоров,которые идентичны по принципу действия и характеристикам (относительно заявляемого устройства). (Конкретные типы процессоров в заявляемом устройстве не показаны и не рассматриваются; их работа для заявляемого устройства определена внешними к данному устройству сигналами, вырабатываемыми процессорами и принимаемыми ими от устройства,

В канале имеется К подканалов, каждый из которых работает со своим типом . заданий, разделяемых по приоритетам, причем чем больше номер канала (подканала 2), тем выше относительный приоритет соответствующего типа заданий, В заявляемом устройстве предусмотрен переход в режим критических потоков - при

превышении числом заданий любого типа некоторого заданного числа (порогового) данный тип заданий приобретает приоритет больше любого типа, число заданий в котором не больше порогового; так как при определенных ситуациях несколько типов заданий могут превысить пороговое значение (по числу заданий соответствующего типа в очереди), то для совокупности критических потоков также предусмотрено приоритетное обслуживание, причем -приоритеты распределяются также, как и для некритических потоков - чем больше номер подканала, тем выше приоритет заданий, поток которых считается критическим,

0 Таким образом, общий поток обрабатываемых заданий состоит из выполняемых в первую очередь (в порядке приоритета) заданий критических потоков), и затем - в порядке аналогичного приоритета - зада5 НИИ потоков, не являющихся критическими, В исходном состоянии узлы устройства (предположим, что в начале работы заявок нет). Имеет следующие состояния: генератор 7 тактовых импульсов не формирует импульсов, на выходах распределителя 8 (кольцевого)-нулевые потенциалы; регистр 4 имеет нулевое содержимое, счетчики 33iЗЗк - тоже; в регистры 34 и 35 занесены двоичные коды, соответствующие для регистра 34 - границы, при превышении которой содержимым соответствующего счетчика 33 поток считается критическим; в регистр 35 двоичный код, задающий нижнюю границу, ниже которой (при обслуживании заданий

0 данного потока) уменьшающийся поток заявок данного типа перестает считаться критическим, (Таким образом, в заявляемом устройстве реализуется гистерезис, обеспечивающий надежное - по потребностям

5 пользователя - выполнение заданий некоторого потока, становящегося критическим для реализации запаса по снятию его критичности, т,е, степени освобождения соответствующего буфера заданий. Триггеры43

0 - в нулевом состоянии (на прямых выходах - нулевые потенциалы). На выходах элементов ИЛИ 42 - (выходах 25) - нулевые потенциалы, на выходах 24 - тоже, следовательно на выходе элемента ИЛИ 16 - нулевой потенциал, под управлением которого коммутатор 17 коммутирует на свои выходы 27 сигналы с входов 25, В регистры 4б1-46м занесены двоичные коды соответственно чисел с 1 по М (определяющие номера процессоров); (цепи записи и данных для

регистров 46 на фиг. не показаны). На выходах 48 и 49 узла 47 последней ступени (выходах 31 и 32 блока 6) - нулевые коды, сигнал с выхода блока сравнения 9 - нулевой. Элементы И групп 14 и 15 закрыты. Регистры 57 блоков 5 обнулены. Цепи начальной установки устройства на фиг. не показаны.

После включения устройства и отсутствия заданий на входах - т.е., отсутствия очереди, заявляемое устройство не изменяет своего состояния и не формирует сигналов распределения, независимо от работы генератора 7 и распределителя 8, который поочередно выдает по тактовым импульсам сигналы на выходах 29 и 30.

Распределение заявок начинается при поступлении импульсов на входы 19 канала.

Поскольку работа устройства мало отличается вне зависимости от конкретных характеристик очереди и загруженности процессоров, рассмотрим его работу в наиболее общем случае - при загруженности всех процессоров и некоторой очереди заданий всех потоков.

Очередным тактом работы распределитель 8 переводится в состояние, при котором на выходе 29 - положительный потенциал, а на выходе 30 - нулевой. В этом такте работы осуществляется анализ окончания выполнения заданий процессорами (параллельно для всех процессоров). К этому моменту времени в счетчиках 33 содержатся числа, соответствующие количеству заявок соответствующих потоков заданий (в счетчике 33i - низшего, а в счетчике ЗЗк - высшего приоритета). Предположим, что все счетчики содержат коды, не превышающие верхних границ в регистрах 34), т.е. все потоки не являются критическими. В этом случае триггеры 43 всех блоков 2 находятся в нулевом состоянии, на выходе элемента ИЛИ 16 - нулевой сигнал, на вы,ходы коммутатора (выполненного, например, как мультиплексор) - сигналы с входов 25, представляющие в совокупности код, в котором единичные значения соответствующих разрядов соответствуют наличию заданий данной типа (приоритета). Этот код с .в.ыхода 27 поступает в узел приоритета 3 (фиг. 5), где на элементах НЕ 53 и И 54 преобразуется в позиционный единичный код, единственная единица которого расположена в разряде, соответствующем номеру подканала максимального приоритета, в котором имеется очередь заданий. В шифраторе 55 этот позиционный код преобразуется в воичный: старший разряд выходного кода узла приоритета 3 образуется от элемента ИЛИ 16. Таким образом, на

выходах узла 3 формируется код, соответствующий (без старшего разряда) номеру канала 2, из которого задание с наивысшим приоритетом готово к выдаче в процессор 5 (который выбирается далее). По положительному фронту сигнала с выхода 29 распределителя 8 данный двоичный код записывается в регистр 4. Одновременно во всех узлах 51-5м выборки задания производится анализ окончания выполнения заданий соответствующими процессорами. Процессоры по окончании выполнения задания выставляют положительный потенциал на соответствующем выходе 21 и код на

5 выходе 20: этот код, в случае наличия в соответствующем процессоре прерванного ранее задания соответствует его приоритету, а в случае отсутствия прерванного задания, код на выходах - 20 - нулевой, если же

0 в момент подачи сигнала с выхода 29 процессор не закончил выполнение задания, на выходе 21 нет сигнала, и на выходах 20 тоже; (следует отметить, что в процессе выполнения некоторым процессором определенного задания, код этого задания - его приоритет- записан в соответствующем регистре 57).

Если процессор не закончил выполнение задания, то элемент И 58 в данном такте

0 закрыт, и в данном узле 5 ничего не происходит. Если процессор закончил выполнение задания, то на выходе элемента И 58 по сигналу с выхода 29 формируется положительный потенциал, переключающий коммутатор 56 таким образом, что на его выходы коммутируются сигналы с входов 20, на которых как сказано выше - либо нулевой код, либо код приоритета прерванного задания; этот код записывается в регистр 57 синхросигналом (его положительным фронтом), прошедшим через элементы задержки 59 и ИЛИ 60.

Такие процессы происходят во всех узлах 5 параллельно. Коды, сформированные в данном такте в регистрах 57 по выходам 22 поступают в блок определения минимума, на выходе которого - формируется на выходах 31 - минимальный код приоритета среди всех заданий, выполняемых

0 в текущий момент времени процессорами, а на выходах 32 - соответствующий номер. процессора, выполняющего это задание низшего приоритета. Минимальный код с выхода 31 поступает на блок сравнения 9; на

5 второй его вход поступает код наивысшего приоритета задания, ожидающего обслуживания. В том случае, когда последний код (с выхода регистра 4) больше кода с выходом 31, блок 9 выдает на выходе положительный импульс. (Это означает ситуацию, когда в

r-poiteccope, выполняющем задание с низшмм среди всех процессоров приоритетом, следует заменить данное задание на новое, ТЭК КЗ к новое имеет более высокий приориОдноэременнодвоичный коде выходов 32 поступает на дешифратор 12, в котором поеооразуется в позиционный код, количасгзо разрядоа .чоторого равно М, и единственная ед/1М1-1ца соответстаует номеру процессора (положение данной единицы), з котором заменяется задание.

Если ма; сммальный код от регмстра 4 меньше (или равен) коду с выхода 31, блок Э не выдает сигнала - это означает, что нет свободных процессороз, либо - нет процесСеров, выполняющих задания, приоритет которых меньше выбранного блоком 3, либо - нет заданий в очереди. Если же код с регистра 4 больше, по следующему такту, появляющимся импульсом на выходе 30, порголчатся сигнал на выходе элемента И 10 и срорм /1розателя импульсов 11 (длительность |лмпульса на выходе которого достаточна ,цлй ссуществлен ля записи в соответствуюш.ий процессор нового задания). Импульсом с формирователя 11 открываются /элементы И группы 14, на выходе 23, соотр-отстуующем выбранному процессору, по;,оу етоя сигггал, запускающий процесс зыдичи задания процессору (в процессоре пролс.ходит прерывание - в случае выполнения - зада1тия с более низки приоритетом, I/ г вод нового, код которого - вернее, номер подканала, из которого берется задание. вьлдсетсй соответствующего регистра 57). В блоке 5 выбр8Н -10го процессора сигналом с выхода 23 через злемонт ИЛИ 60 в регистр 57 записывается код (приоритет) нового задания; в данном такте коммутатор 56 соединяет на свои выходы ахо,ць 28 от регистра 4.

Таким образом завершается процесс распределения некоторого задания, В следующей паре тактов процесс продолжается аналогично.

Следует отметить, что сигнал с выхода формирователя 11 кроме того открывает соответствующий элементИ группы 15, и сигналом с соответствующего выхода дешифратора 13 в блоке 2, выбранного на обработ у задания, счетчик 33 уменьшает со,цержммое на единицу; иначе говоря, уменьшение очереди в заявляемом ус.тройстаз производится в момент принятия задания на обработку соответствующим процессором.

Рассмотрим работу блока 2.

При превышении содержимым счетчика 33 содержимого регистра 34 данный поток переходит в критический : срабатывает rip

выходу Больше блок сравнения 36, формирователь 38 импульсов выдает импульс, который, проходя через открытый (положительным потенциалом - в исходном

состоянии - с инверсного выхода триггера 43) элемент И 40, и триггер 43 устанавливается в единичное состояние, фиксируя переход потока заданий данного типа в критический режим. В дальнейшем состояние критического режима для данного потока сохраняется до тех пор, пока, по мере обработки заданий, содержимре счетчика 33 н& станет меньше содержимого регистра 37; при этом срабатывает по выходу Мень5 ше блок сравнения 37 и через формирователь 39 и элемент И 41 триггер 43 возвращается в нулевое состояние.

Наличие хотя бы одного критического потока фиксируется элементом ИЛИ 16, который переключает коммутатор на выходы триггеров 43 подканалов 2 - таким образом, обеспечивается приоритет критического (критических,если их - несколько) потока перед некритическими. Среди критических

5 потоков, если их несколько, организуетсяаналогичная дисциплина приоритетного обслуживания, как и среди некритических. При зтомсигнал с выхода элемента ИЛИ 16 используется в устройстве бив узлах 5 в

С качестве указателя на то, что обрабатываетс.я именно критический поток (будучи старшим разрядо.м, этот сигнал обеспечивает в совокупности кодов заведомое превышение любым кодом критического потока либо

5 кода некритического потока). Для сброса (декрементирования) счетчиков 33 и выбора процессорами заданий рпределенного типа этот разряд не используется.

Формула изобретения

0 1. Устройство для распределения заданий процессорам, содержащее каналы, каждый из которых содержит узел приоритета и группу подканалов, каждый из которых содержит элемент ИЛИ и счетчик, причем запросные входы канала соединены с суммирующими входами счетчиков соответствующих подканалов, в каждом подканале выходы счетчика соединены с входами элемента ИЛИ своего подканала, выход которого является первым выходом подканала, о тличающееся тем, что, с целью расширения области применения за счет обслуживания запросов в зависимости от частоты их поступления, в каждый канал введены регистр, генератор тактовых импульсов, распределитель импульсов, группа узлов выбора задания, блок определения минимума, блок сравнения,-элемент И, формирователь импульсов, два дешифратора, две группы элементов И, элемент ИЛИ и коммутатор. а в каждый канал введены два регистра, два блока сравнения, два формирователя импульсов, два элемента И и триггер, причем в каждом канале устройства первые и вторые выходы подканалов соединены соответственно с первой и второй группой информационных входов коммутатора, выходы узла приоритета подключены к информационной группе входов регистра, выходы которого соединены с входами первой группы блока сравнения и с первыми группами входов узлов выбора задания группы, вторые группы входов которых являются информационными входами канала, первые входы - ответными входами канала, а выходы являются информационными выходами канала и соединены с входами блока опреде ения минимума, первая группа выходов которого соединена с второй группой входов блока сравнения и с входами первого дешифратора, а вторая группа выходов блока определения минимума соединена с входами второго дешифратора, выходы первого и второго дешифраторов соединены соответственно с первыми входами элементов И второй и первой групп, вторые входы которых соединены с выходом формирователя импульсов, выходы элементов И первой группы соединены с вторыми входами соответствующих узлов выбора задания и являются управляющими выходами канала, выходыэлементов И второй группы соединены с вычитающими входами счетчиков соответствующих подканалов, выход генератора тактовых импульсов соединен с входом распределителя импульсов, первый выход которого подключена третьим входам всех узлов выбора задания и к синхровходу регистра, а второй выход - к первому входу элемента И, второй вход и выход которого соединены соответственно с выходом блока сравнения и с входом

формирователя импульсов, в каждом подканале канала выходы первого и второго регистров соединены с первыми входами соответственно первого и второго блоков

сравнения, вторые входы которых подключены к выходам счетчика, выходы первого и второго блоков сравнения соединены соответственно с входами первого и второго формирователей импульсов, выходы которых соединены соответственно с первыми входами первого и второго элементов И, выходы которых соединены соответственно с единичным и нулевым входами триггера, прямой и инверсный выходы которого соединены соответственно с вторыми входами второго и первого элементов И, прямой выход триггера является вторым выходом соответствующего подканала, кроме этого, в каждом канале вторые выходы подканалов

соединены с входами элемента ИЛИ, выход которого соединен с управляющим входом коммутатора, сигнальным входом узла приоритета и является сигнальным выходом канала устройства.

2. Устройство по п. 1, о т л и ч а ю щ е ес я тем, что узел выбора задания содержит регистр, коммутатор, элементы И, ИЛИ и

задержки, причем первая и вторая группы входов узла выбора задания соединены соответственно с первой и второй группой информационных входов коммутатора, выход которого является выходом узла выбора заДания, первый и третий входы которого соединены с входами элемента И, выход которого соединен с управляющим входом коммутатора И, через элемент задержки - с первым входом элемента ИЛИ, второй вход

и выход которого соединены соответственно с вторым входом узла выбора задания и синхровходом регистра.

JSf

акям

;tj:

т

и г/

/// Й

Ж

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения | 1978 |

|

SU813400A2 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для сопряжения | 1984 |

|

SU1166126A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для сопряжения | 1978 |

|

SU813401A2 |

| Устройство для обмена информацией | 1979 |

|

SU826330A1 |

| Устройство для сопряжения | 1980 |

|

SU926645A2 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1509891A1 |

Изобретение относится к вычислительной технике и может быть использовано з процессорных системах при распределениизаявок между процессорами. Цель изобретения - расширекие области применения устройства за счет обслуживания запросов а зависимости от частоты их поступления. Устройство для распределения заданий процессорам содержит каналы, каждыу"^ канал имеет подкзна.г-ы, включающие элемент ИЛИ, коммутатор, узел приоритета, регистр, генератор импульсов, распределитель импульсов, два дешифратора, две группы злемеитоь И, блок сравнения, эле- .мент И, формирователь импульсов, узел выбора задания, блок определения минимума. УсгройстБо позвопяет повысить загруженность процессоров и, следовательно, снизить вре.мя ожидания заданий Б очереди. 1 з.п. ф-лы. 6 ил.Устройство относится к вычислительной технике и может быть использовано в многопроцессорных системах при распределении заявок между процессорами.Известно устройство для распределения заданий процессорам [1], содержащее каналы, а в каждом канале - узел приоритета, и группу подканалов, каждый из которых содержит элемент ИЛИ, счетчик, в каждом подканале группы, кроме первого, элемент запрета, причем запросные входы устройства подключены к суммирующим входам счетчиков соответствующих подканалоз, вычитающие входы которых являются ответными входами устройства, информационные выходы счетчиков подключены к выходам элементов ИЛИ своих подканалоз группы, выходы которых подключены к входам у зла приоритета своего канала.Недостатком и.звестного устройства являются узкая область применения и низкая достоверность работы.Наиболее близким техническим решением к предлагаемому янтяется устройство для распределени.я заданий процессорам [2], принятое за прототип, содержащее каналы, в каждом канале - узел приоритета, триггер и группу подканалов, каждый из которых содержит элемент ИЛИ и счетчик, причем Б каждом подканале, кроме первого, содержится элемент запрета, а в первом кзнале - дополнительный элемент ИЛИ. причем запросные входы устройства подключены к суммирующим входам счетчиков соответствующих подканалов, вычитающие входы которых являются ответными входами устройства, информационные входы счетчиков подк/-;Ючены к входам элементов ИЛИ своих подканалов группы, выходы которых подключены к входам узла приорите-Г"'"литV,( >&

J

ЗЕ I

иЬ

ЬО

J5

2

г/

22,

22,

-M

I

62

«5,

2jiI

ад

9

fN

47;

11

v

Ъ2

k9

8

ДА

L.v

/i I

ffJY

51 1

j; //г J

(5

o

rj/;

.

№;

Фие.

| Многоканальное устройство для обслуживания запросов | 1986 |

|

SU1399739A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-12-07—Публикация

1990-12-17—Подача