Изобретение относится к вычислительной технике и может быть использовано при построении устройств управления микропрограммной ЭВМ.

Цель изобретения - повышение быстродействия.

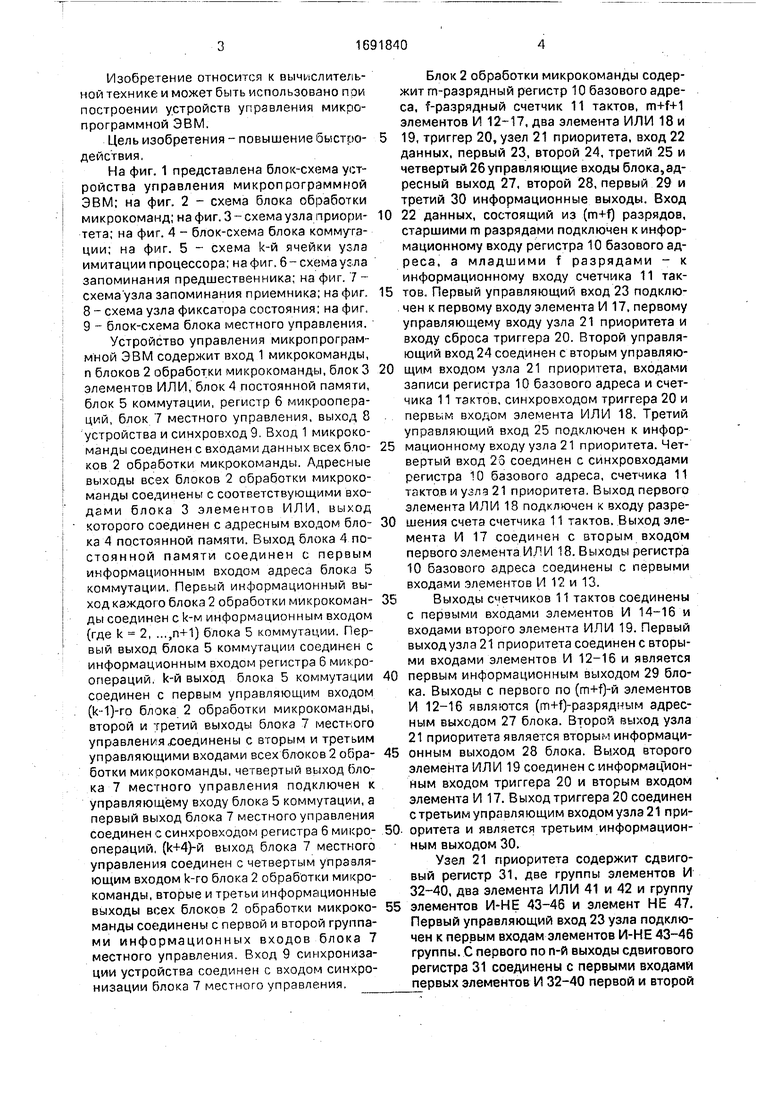

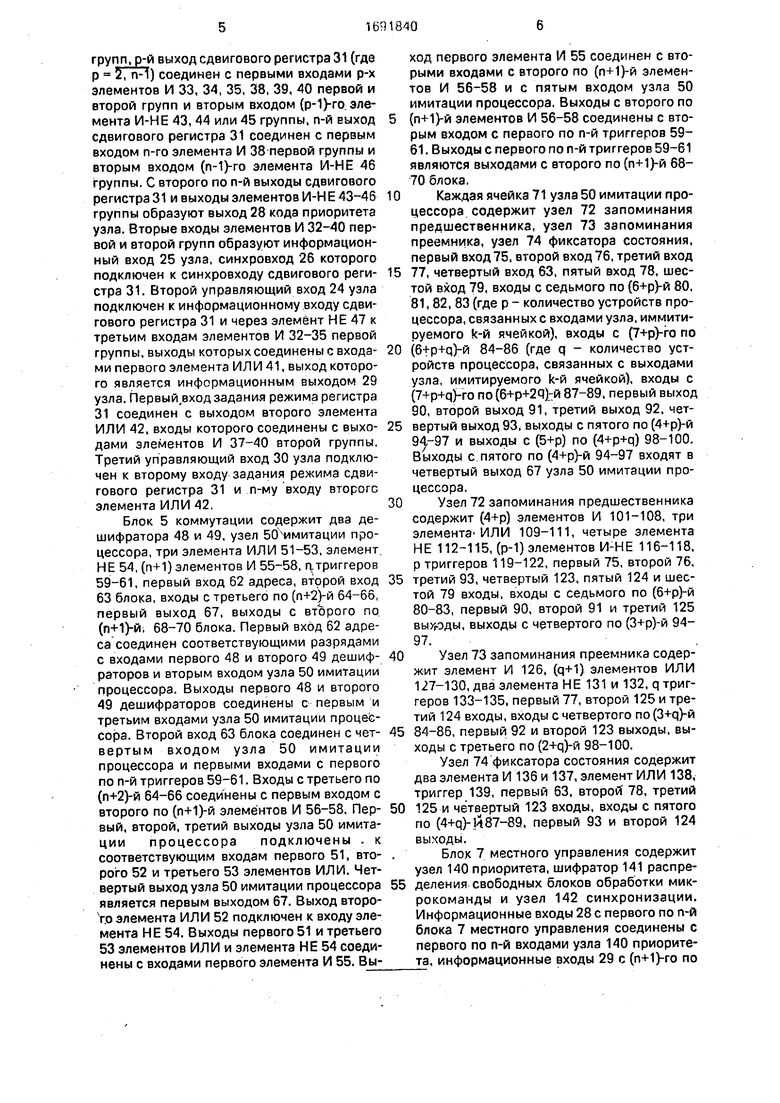

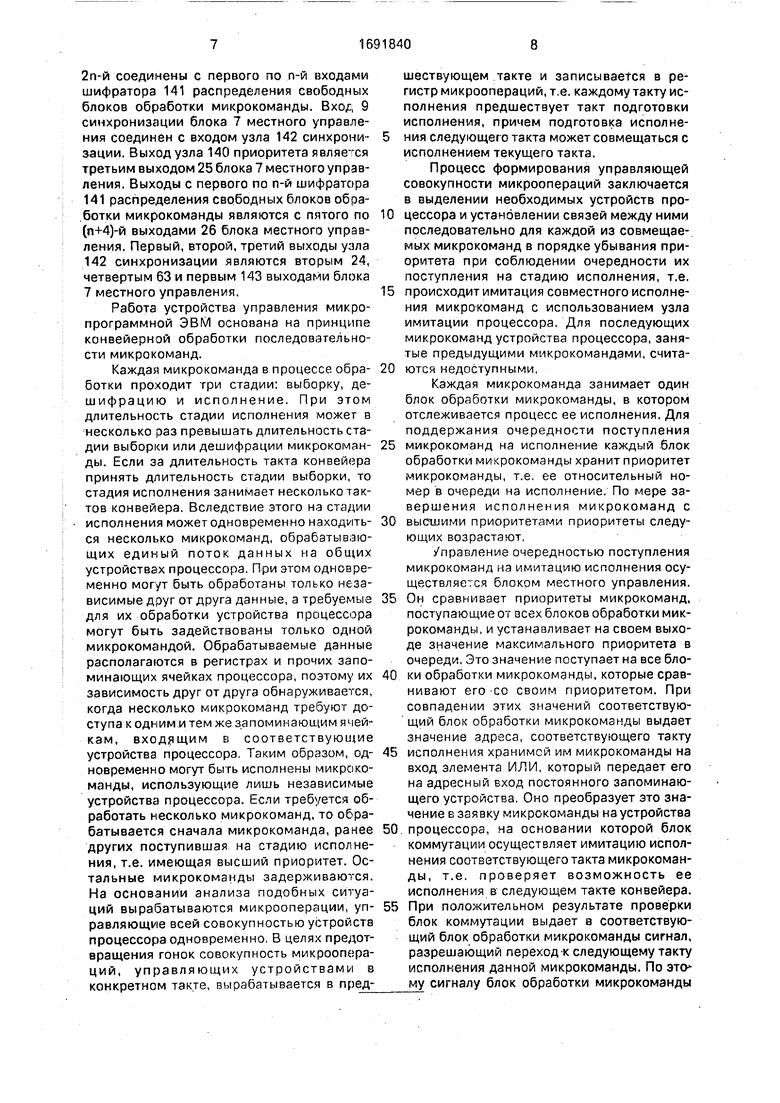

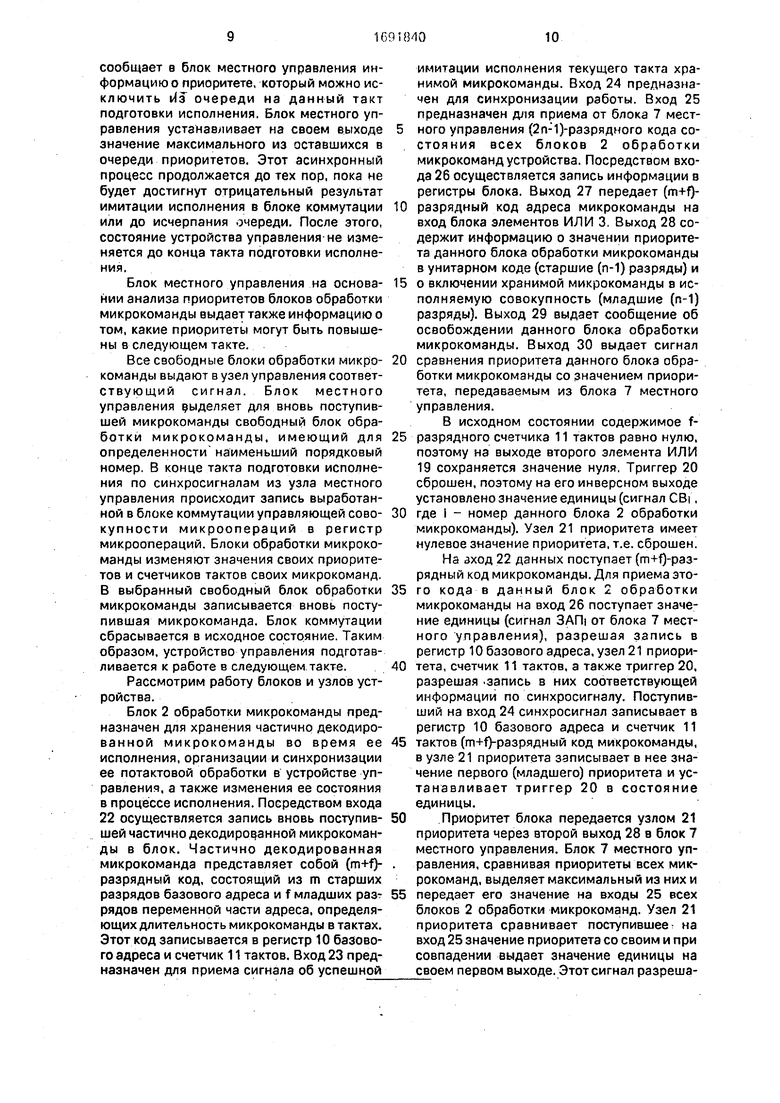

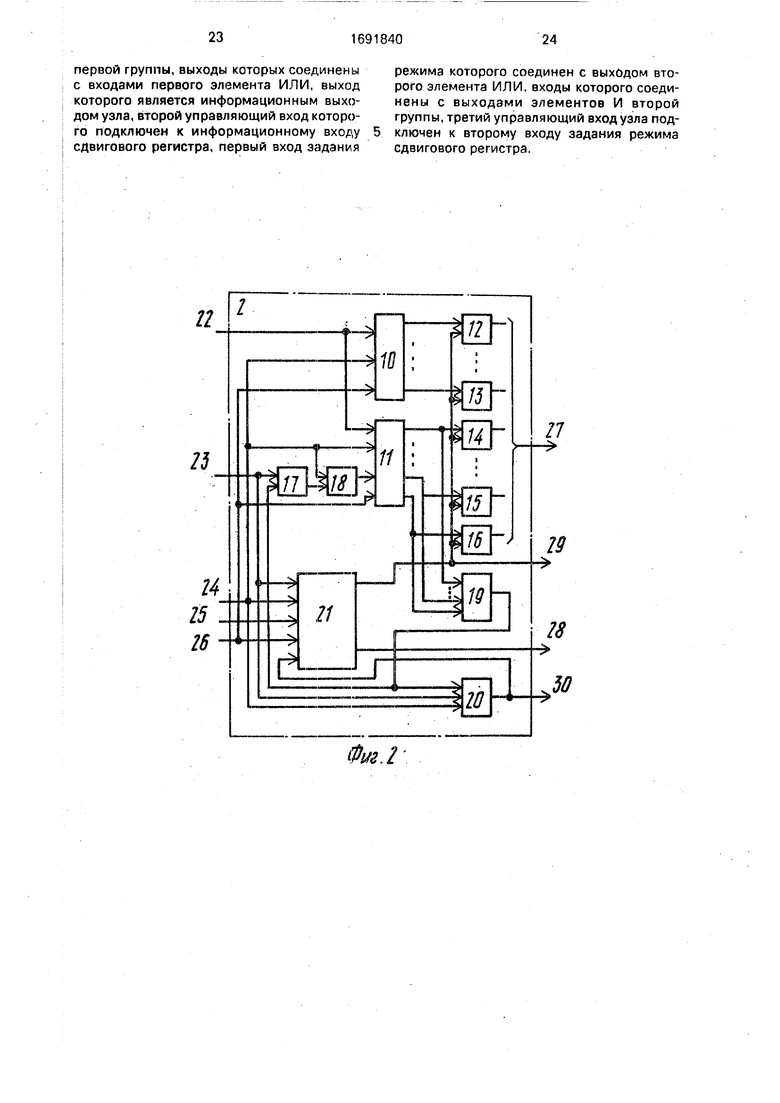

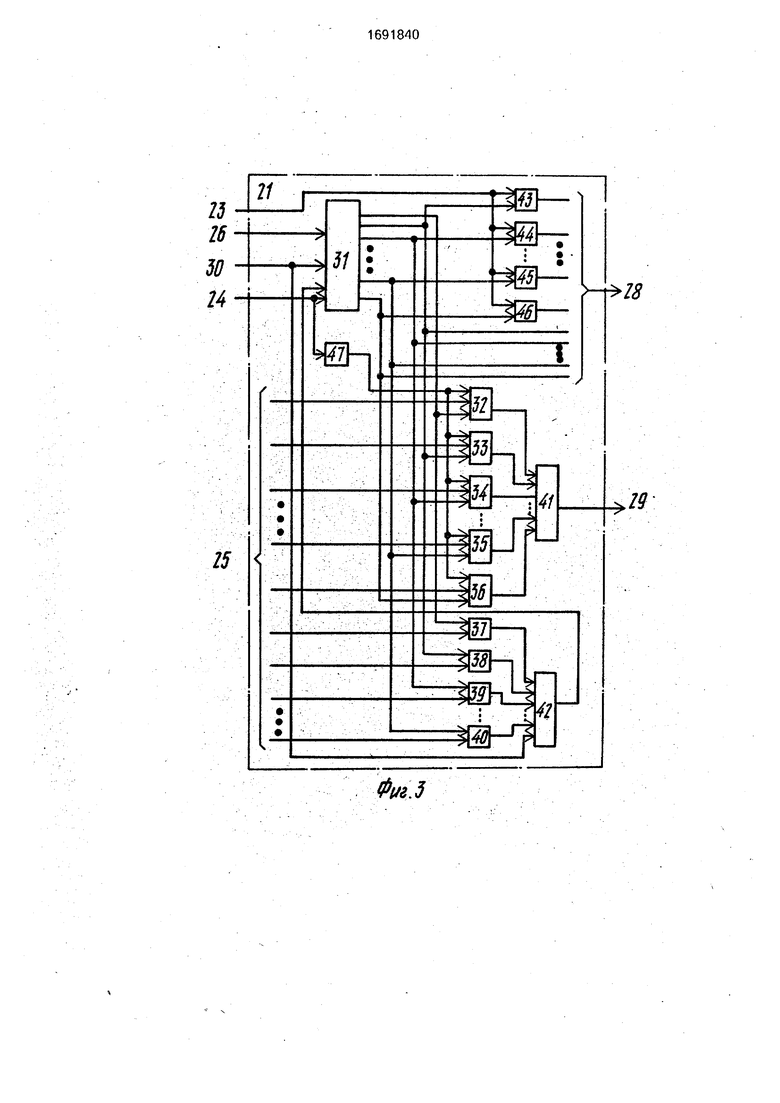

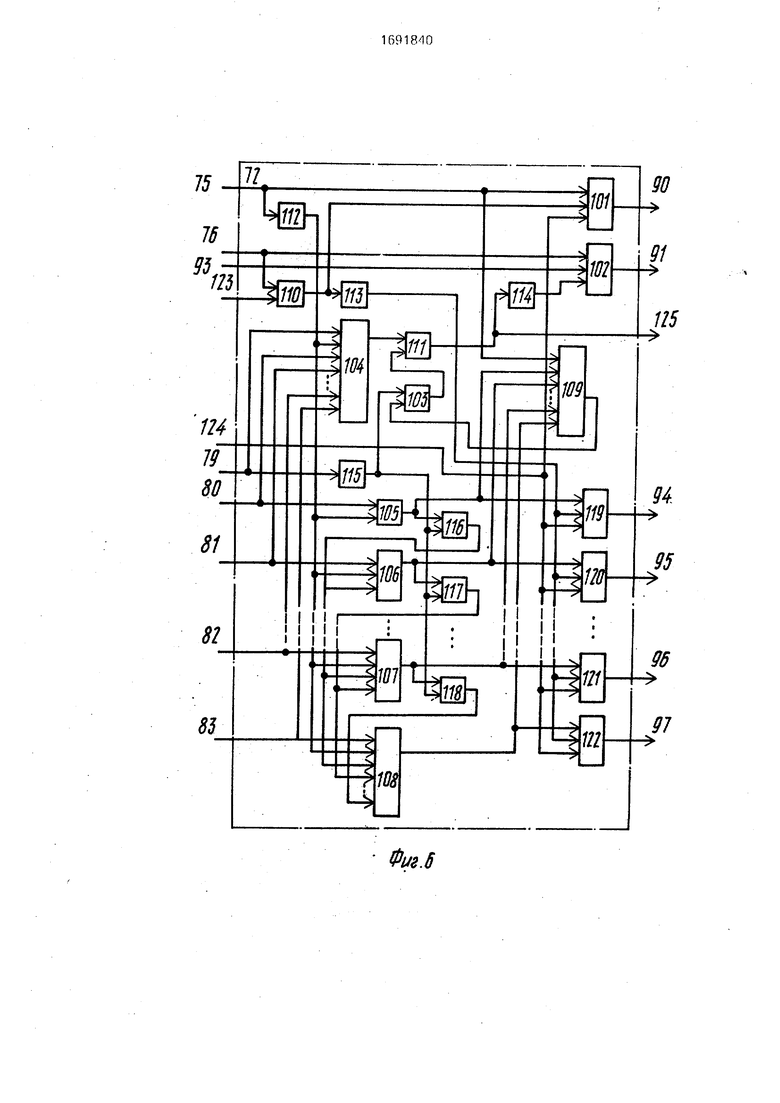

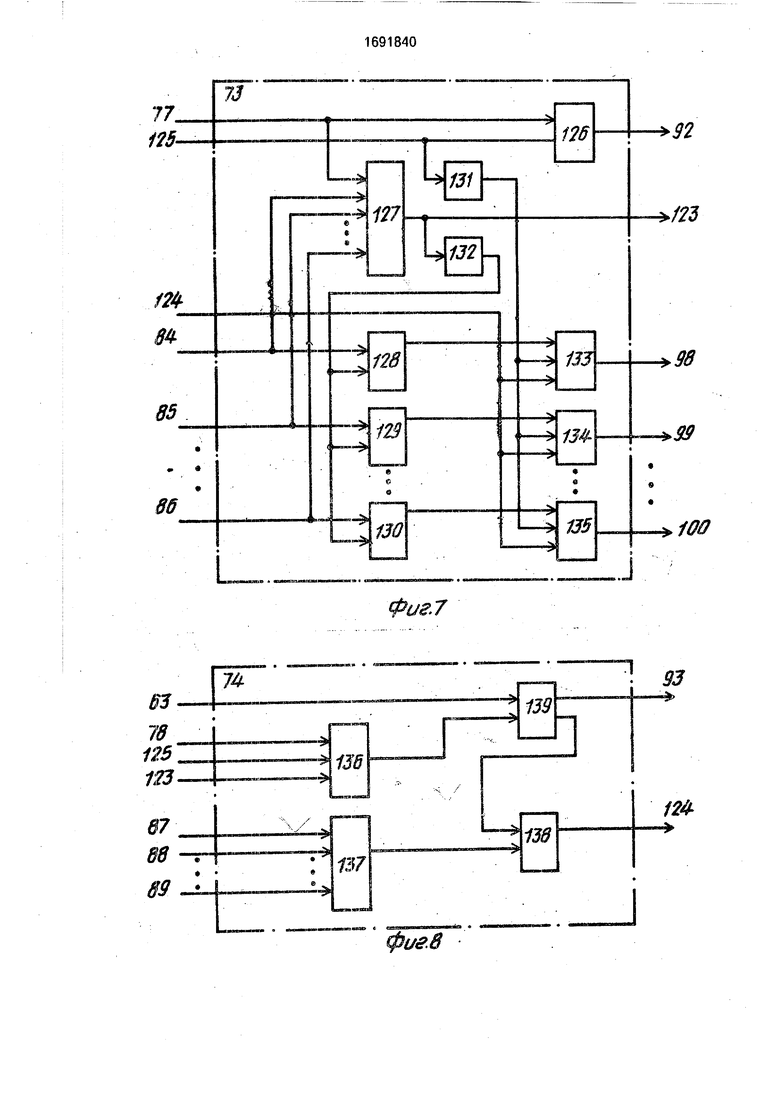

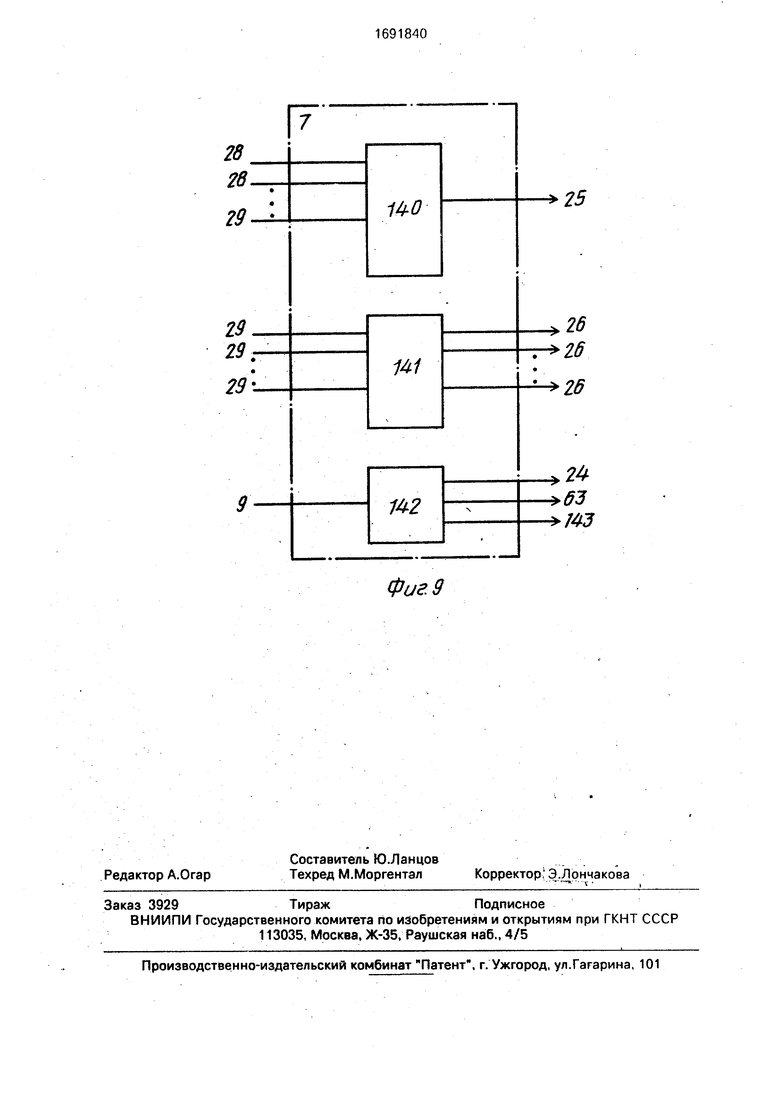

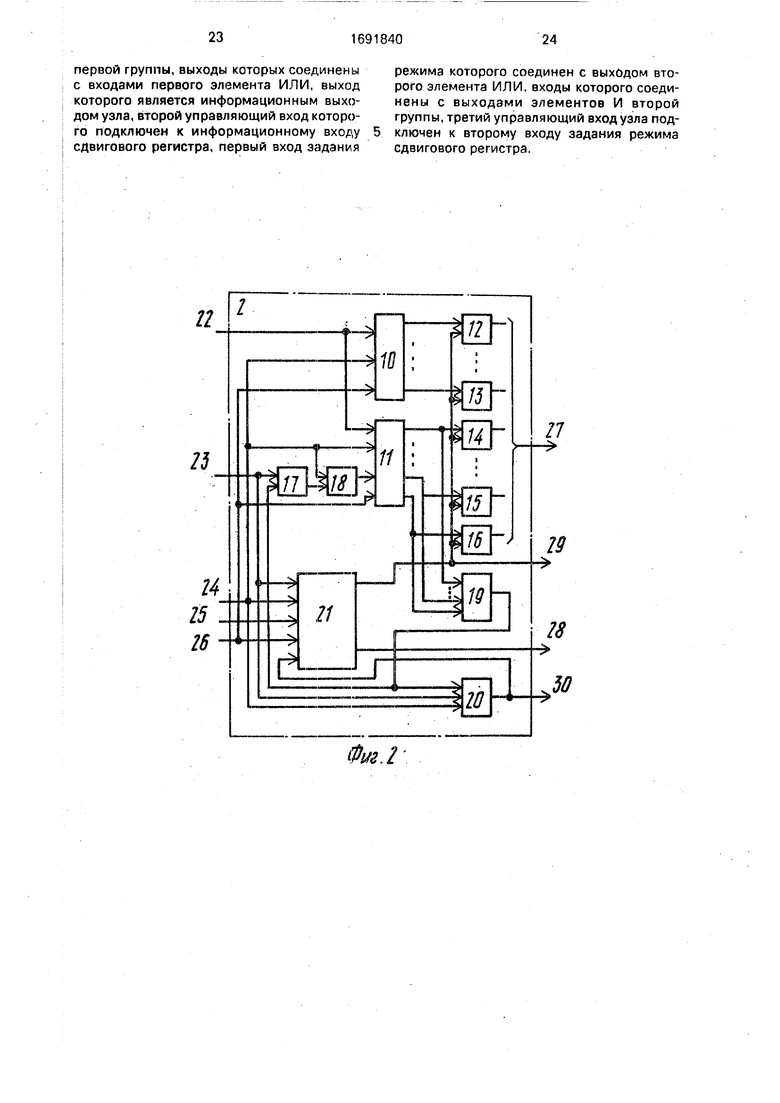

На фиг. 1 представлена блок-схема устройства управления микропрограммной ЭВМ; на фиг. 2 - схема блока обработки микрокоманд; на фиг. 3 - схема узла приоритета; на фиг. 4 - блок-схема блока коммутации; на фиг. 5 - схема k-й ячейки узла имитации процессора; на фиг. 6-схема узла запоминания предшественника; на фиг. 7 - схема узла запоминания приемника; на фиг.

8- схема узла фиксатора состояния; на фиг.

9- блок-схема блока местного управления.

Устройство управления микропрограммной ЭВМ содержит вход 1 микрокоманды, п блоков 2 обработки микрокоманды, блок 3 элементов ИЛИ, блок 4 постоянной памяти, блок 5 коммутации, регистр 6 микроопераций, блок 7 местного управления, выход 8 устройства и синхровход 9. Вход 1 микрокоманды соединен с входами данных всехбпо- ков 2 обработки микрокоманды. Адресные выходы всех блоков 2 обработки микрокоманды соединены с соответствующими входами блока 3 элементов ИЛИ, выход которого соединен с адресным входом блока 4 постоянной памяти. Выход блока 4 по- стоянной памяти соединен с первым информационным входом адреса блока 5 коммутации. Первый информационный выход каждого блока 2 обработки микрокоманды соединен с k-м информационным входом (где k 2, ...,п+1) блока 5 коммутации. Первый выход блока 5 коммутации соединен с информационным входом регистра 6 микроопераций. k-й выход блока 5 коммутации соединен с первым управляющим входом (k-1)-ro блока 2 обработки микрокоманды, второй и третий выходы блока 7 местного управления .соединены с вторым и третьим управляющими входами всех блоков 2 обработки микрокоманды, четвертый выход блока 7 местного управления подключен к управляющему входу блока 5 коммутации, а первый выход блока 7 местного управления соединен с синхровходом регистра 6 микроопераций. ( выход блока 7 местного управления соединен с четвертым управляющим входом k-ro блока 2 обработки микрокоманды, вторые и третьи информационные выходы всех блоков 2 обработки микрокоманды соединены с первой и второй группами информационных входов блока 7 местного управления. Вход 9 синхронизации устройства соединен с входом синхронизации блока 7 местного управления.

Блок 2 обработки микрокоманды содержит m-разрядный регистр 10 базового адреса, f-разрядный счетчик 11 тактов, m+f+1 элементов И 12-17, два элемента ИЛИ 18 и

19, триггер 20, узел 21 приоритета, вход 22 данных, первый 23, второй 24, третий 25 и четвертый 26 управляющие входы блока,адресный выход 27, второй 28, первый 29 и третий 30 информационные выходы. Вход

22 данных, состоящий из (m+f) разрядов, старшими m разрядами подключен к информационному входу регистра 10 базового адреса, а младшими f разрядами - к информационному входу счетчика 11 тактов. Первый управляющий вход 23 подключен к первому входу элемента И 17, первому управляющему входу узла 21 приоритета и входу сброса триггера 20. Второй управляющий вход 24 соединен с вторым управляющим входом узла 21 приоритета, входами записи регистра 10 базового адреса и счетчика 11 тактов, синхровходом триггера 20 и первым входом элемента ИЛИ 18. Третий управляющий вход 25 подключен к информационному входу узла 21 приоритета. Четвертый вход 23 соединен с синхровходами регистра 10 базового адреса, счетчика 11 тактов и узла 21 приоритета. Выход первого элемента ИЛИ 18 подключен к входу разрешения счета счетчика 11 тактов. Выход элемента И 17 соединен с вторым входом первого элемента ИЛИ 18. Выходы регистра 10 базового адреса соединены с первыми входами элементов И 12 и 13.

Выходы счетчиков 11 тактов соединены с первыми входами элементов И 14-16 и входами второго элемента ИЛИ 19. Первый выход узла 21 приоритета соединен с вторыми входами элементов И 12-16 и является

первым информационным выходом 29 блока. Выходы с первого по (т+т)-й элементов И 12-16 являются (т+т)-разрядным адресным выходом 27 блока. Второй выход узла 21 приоритета является вторым информационным выходом 28 блока. Выход второго элемента ИЛИ 19 соединен с информационным входом триггера 20 и вторым входом элемента И 17. Выход триггера 20 соединен с третьим у правля ющим входом узла 21 приоритета и является третьим информационным выходом 30.

Узел 21 приоритета содержит сдвиговый регистр 31, две группы элементов И 32-40, два элемента ИЛИ 41 и 42 и группу

элементов И-НЕ 43-46 и элемент НЕ 47. Первый управляющий вход 23 узла подключен к первым входам элементов И-НЕ 43-46 группы. С первого по n-й выходы сдвигового регистра 31 соединены с первыми входами

первых элементов И 32-40 первой и второй

групп, р-й выход сдвигового регистра 31 (где р 57n-i) соединен с первыми входами р-х элементов И 33, 34, 35, 38, 39, 40 первой и второй групп и вторым входом (р-1)-го элемента И-НЕ 43, 44 или 45 группы, n-й выход сдвигового регистра 31 соединен с первым входом n-го элемента И 38 первой группы и вторым входом (п-1)-го элемента И-НЕ 46 группы. С второго по n-й выходы сдвигового регистра 31 и выходы элементов И-НЕ 43-46 группы образуют выход 28 кода приоритета узла. Вторые входы элементов И 32-40 первой и второй групп образуют информационный вход 25 узла, синхровход 26 которого подключен к синхровходу сдвигового регистра 31. Второй управляющий вход 24 узла подключен к информационному входу сдвигового регистра 31 и через элемент НЕ 47 к третьим входам элементов И 32-35 первой группы, выходы которых соединены с входами первого элемента ИЛ И 41, выход которого является информационным выходом 29 узла. Первый,вход задания режима регистра 31 соединен с выходом второго элемента ИЛИ 42, входы которого соединены с выходами элементов И 37-40 второй группы. Третий управляющий вход 30 узла подключен к второму входу задания режима сдвигового регистра 31 и n-му входу второго элемента ИЛИ 42.

Блок 5 коммутации содержит два дешифратора 48 и 49, узел 50ч1митации процессора, три элемента ИЛИ 51-53, элемент НЕ 54, (п+1) элементов И 55-58, п.триггеров 59-61, первый вход 62 адреса, второй вход 63 блока, входы с третьего по (п+2)-й 64-66, первый выход 67, выходы с второго по (п+1)-й, 68-70 блока. Первый вход 62 адреса соединен соответствующими разрядами с входами первого 48 и второго 49 дешифраторов и вторым входом узла 50 имитации процессора. Выходы первого 48 и второго 49 дешифраторов соединены с первым и третьим входами узла 50 имитации процессора. Второй вход 63 блока соединен с чет- вертым входом узла 50 имитации процессора и первыми входами с первого по n-й триггеров 59-61. Входы с третьего по (п+2)-й 64-66 соединены с первым входом с второго по ( элементов И 56-58. Первый, второй, третий выходы узла 50 имитации процессора подключены . к соответствующим входам первого 51, второго 52 и третьего 53 элементов ИЛИ. Четвертый выход узла 50 имитации процессора является первым выходом 67. Выход второго элемента ИЛИ 52 подключен к входу элемента НЕ 54. Выходы первого 51 и третьего 53 элементов ИЛИ и элемента НЕ 54 соединены с входами первого элемента И 55. Выход первого элемента И 55 соединен с вторыми входами с второго по (п+1}-й элементов И 56-58 и с пятым входом узла 50 имитации процессора. Выходы с второго по

(п+1)-й элементов И 56-58 соединены с вторым входом с первого по n-й триггеров 59- 61. Выходы с первого по n-й триггеров 59-61 являются выходами с второго по (п-И)-й 68- 70 блока.

0 Каждая ячейка 71 узла 50 имитации процессора содержит узел 72 запоминания предшественника, узел 73 запоминания преемника, узел 74 фиксатора состояния, первый вход 75, второй вход 76, третий вход

5 77, четвертый вход 63, пятый вход 78, шестой вход 79, входы с седьмого по (6+р)-й 80, 81,82, 83 (где р - количество устройств процессора, связанных с входами узла, иммити- руемого k-й ячейкой), входы с (7+р)-го по

0 (6+р+р)-й 84-86 (где q - количество устройств процессора, связанных с выходами узла, имитируемого k-й ячейкой), входы с (7+p+q}-ro по (6+р+2Р1-й 87-89, первый выход 90, второй выход 91, третий выход 92, чет5 вертый выход 93, выходы с пятого по (4+р)-й 94/-Э7 и выходы с (5+р) по (4+p+q) 98-100. Выходы с пятого по ( 94-97 входят в четвертый выход 67 узла 50 имитации процессора.

0 Узел 72 запоминания предшественника содержит (4+р) элементов И 101-108, три элемента ИЛИ 109-111, четыре элемента НЕ 112-115, (р-1) элементов И-НЕ 116-118, р триггеров 119-122, первый 75, второй 76,

5 третий 93, четвертый 123, пятый 124 и шестой 79 входы, входы с седьмого по (6+р}-й 80-83, первый 90, второй 91 и третий 125 выводы, выходы с четвертого по (3+р)-й 94- 97.

0 Узел 73 запоминания преемника содержит элемент И 126, (q+1) элементов ИЛИ 127-130, два элемента НЕ 131 и 132, q триггеров 133-135, первый 77, второй 125 и третий 124 входы, входы с четвертого no(3+q)-u

5 84-86, первый 92 и второй 123 выходы, выходы с третьего по (2+q)-u 98-100.

Узел 74 фиксатора состояния содержит два элемента И 136 и 137, элемент ИЛИ 138, триггер 139, первый 63, второй 78, третий

0 125 и четвертый 123 входы, входы с пятого по (4+д Й87-89, первый 93 и второй 124 выходы.

Блок 7 местного управления содержит узел 140 приоритета, шифратор 141 распре5 деления свободных блоков обработки микрокоманды и узел 142 синхронизации. Информационные входы 28 с первого по п-й блока 7 местного управления соединены с первого по n-й входами узла 140 приоритета, информационные входы 29 с (п+1)-го по

2п-й соединены с первого по n-й входами шифратора 141 распределения свободных блоков обработки микрокоманды. Вход 9 синхронизации блока 7 местного управления соединен с входом узла 142 синхронизации. Выход узла 140 приоритета является третьим выходом 25 блока 7 местного управления. Выходы с первого по n-й шифратора

141распределения свободных блоков обработки микрокоманды являются с пятого по (п+4)-й выходами 26 блока местного управления. Первый, второй, третий выходы узла

142синхронизации являются вторым 24, четвертым 63 и первым 143 выходами блока 7 местного управления.

Работа устройства управления микропрограммной ЭВМ основана на принципе конвейерной обработки последовательности микрокоманд.

Каждая микрокоманда в процессе обработки проходит три стадии: выборку, дешифрацию и исполнение. При этом длительность стадии исполнения может в несколько раз превышать длительность стадии выборки или дешифрации микрокоманды. Если за длительность такта конвейера принять длительность стадии выборки, то стадия исполнения занимает несколько тактов конвейера. Вследствие этого на стадии исполнения может одновременно находиться несколько микрокоманд, обрабатывающих единый поток данных на общих устройствах процессора. При этом одновременно могут быть обработаны только независимые друг от друга данные, а требуемые для их обработки устройства процессора могут быть задействованы только одной микрокомандой. Обрабатываемые данные располагаются в регистрах и прочих запоминающих ячейках процессора, поэтому их зависимость друг от друга обнаруживается, когда несколько микрокоманд требуют доступа к одним и тем же запоминающим ячейкам, входящим в соответствующие устройства процессора. Таким образом, одновременно могут быть исполнены микрокоманды, использующие лишь независимые устройства процессора. Если требуется обработать несколько микрокоманд, то обрабатывается сначала микрокоманда, ранее других поступившая на стадию исполнения, т.е. имеющая высший приоритет. Остальные микрокоманды задерживаются. На основании анализа подобных ситуаций вырабатываются микрооперации, управляющие всей совокупностью устройств процессора одновременно. В целях предотвращения гонок совокупность микроопераций, управляющих устройствами в конкретном такте, вырабатывается в предшествующем такте и записывается в регистр микроопераций, т.е. каждому такту исполнения предшествует такт подготовки исполнения, причем подготовка исполнения следующего такта может совмещаться с исполнением текущего такта.

Процесс формирования управляющей совокупности микроопераций заключается в выделении необходимых устройств про0 цессора и установлении связей между ними последовательно для каждой из совмещаемых микрокоманд в порядке убывания приоритета при соблюдении очередности их поступления на стадию исполнения, т.е.

5 происходит имитация совместного исполнения микрокоманд с использованием узла имитации процессора. Для последующих микрокоманд устройства процессора, занятые предыдущими микрокомандами, счита0 ются недоступными.

Каждая микрокоманда занимает один блок обработки микрокоманды, в котором отслеживается процесс ее исполнения. Для поддержания очередности поступления

5 микрокоманд на исполнение каждый блок обработки микрокоманды хранит приоритет микрокоманды, т.е. ее относительный номер в очереди на исполнение. По мере завершения исполнения микрокоманд с

0 высшими приоритетами приоритеты следующих возрастают.

Управление очередностью поступления микрокоманд на имитацию исполнения осуществляется блоком местного управления.

5 Он сравнивает приоритеты микрокоманд, поступающие от всех блоков обработки микрокоманды, и устанавливает на своем выходе значение максимального приоритета в очереди. Это значение поступает на все бло0 ки обработки микрокоманды, которые сравнивают его со своим приоритетом. При совпадении этих значений соответствующий блок обработки микрокоманды выдает значение адреса, соответствующего такту

5 исполнения хранимой им микрокоманды на вход элемента ИЛИ, который передает его на адресный вход постоянного запоминающего устройства. Оно преобразует это значение в заявку микрокоманды на устройства

0 процессора, на основании которой блок коммутации осуществляет имитацию исполнения соответствующего такта микрокоманды, т.е. проверяет возможность ее исполнения в следующем такте конвейера.

5 При положительном результате проверки блок коммутации выдает в соответствующий блок обработки микрокоманды сигнал, разрешающий переход к следующему такту исполнения данной микрокоманды. По этому сигналу блок обработки микрокоманды

сообщает в блок местного управления информацию о приоритете, который можно исключить Аз очереди на данный такт подготовки исполнения. Блок местного управления устанавливает на своем выходе значение максимального из оставшихся в очереди приоритетов. Этот асинхронный процесс продолжается до тех пор, пока не будет достигнут отрицательный результат имитации исполнения в блоке коммутации или до исчерпания очереди. После этого, состояние устройства управления не изменяется до конца такта подготовки исполнения.

Блок местного управления на основании анализа приоритетов блоков обработки микрокоманды выдает также информацию о том, какие приоритеты могут быть повышены в следующем такте.

Все свободные блоки обработки микрокоманды выдают в узел управления соответ- ствующий сигнал. Блок местного управления выделяет для вновь поступившей микрокоманды свободный блок обработки микрокоманды, имеющий для определенности наименьший порядковый номер. В конце такта подготовки исполнения по синхросигналам из узла местного управления происходит запись выработанной в блоке коммутации управляющей сово- купности микроопераций в регистр микроопераций. Блоки обработки микрокоманды изменяют значения своих приоритетов и счетчиков тактов своих микрокоманд. В выбранный свободный блок обработки микрокоманды записывается вновь поступившая микрокоманда. Блок коммутации сбрасывается в исходное состояние. Таким образом, устройство управления подготавливается к работе в следующем такте.

Рассмотрим работу блоков и узлов устройства.

Блок 2 обработки микрокоманды предназначен для хранения частично декодированной микрокоманды во время ее исполнения,организации и синхронизации ее потактовой обработки в устройстве управления, а также изменения ее состояния в процессе исполнения. Посредством входа 22 осуществляется запись вновь поступившей частично декодированной микрокоманды в блок. Частично декодированная микрокоманда представляет собой (m+f)- разрядный код, состоящий из m старших разрядов базового адреса и f младших раз рядов переменной части адреса, определяющих длительность микрокоманды в тактах. Этот код записывается в регистр 10 базового адреса и счетчик 11 тактов. Вход 23 предназначен для приема сигнала об успешной

имитации исполнения текущего такта хранимой микрокоманды. Вход 24 предназначен для синхронизации работы. Вход 25 предназначен для приема от блока 7 местного управления {2п:1)-разрядного кода со- стояния всех блоков 2 обработки микрокоманд устройства. Посредством входа 26 осуществляется запись информации в регистры блока. Выход 27 передает (m+f)0 разрядный код адреса микрокоманды на вход блока элементов ИЛИ 3, Выход 28 содержит информацию о значении приоритета данного блока обработки микрокоманды в унитарном коде (старшие (п-1) разряды) и

5 о включении хранимой микрокоманды в исполняемую совокупность (младшие (п-1) разряды). Выход 29 выдает сообщение об освобождении данного блока обработки микрокоманды. Выход 30 выдает сигнал

0 сравнения приоритета данного блока обработки микрокоманды со значением приоритета, передаваемым из блока 7 местного управления.

В исходном состоянии содержимое f5 разрядного счетчика 11 тактов равно нулю, поэтому на выходе второго элемента ИЛИ 19 сохраняется значение нуля. Триггер 20 сброшен, поэтому на его инверсном выходе установлено значение единицы (сигнал CBi,

0 где I - номер данного блока 2 обработки

микрокоманды). Узел 21 приоритета имеет

нулевое значение приоритета, т.е. сброшен.

На аход 22 данных поступает (m+f)-pa3рядный код микрокоманды. Для приема это5 го кода в данный блок 2 обработки микрокоманды на вход 26 поступает значение единицы (сигнал ЗАП| от блока 7 местного управления), разрешая запись в регистр 10 базового адреса, узел 21 приори0 тета, счетчик 11 тактов, а также триггер 20, разрешая .запись в них соответствующей информации по синхросигналу. Поступивший на вход 24 синхросигнал записывает в регистр 10 базового адреса и счетчик 11

5 тактов (т+т)-разрядный код микрокоманды, в узле 21 приоритета записывает в нее значение первого (младшего) приоритета и устанавливает триггер 20 в состояние единицы.

0 Приоритет блока передается узлом 21 приоритета через второй выход 28 в блок 7 местного управления. Блок 7 местного управления, сравнивая приоритеты всех микрокоманд, выделяет максимальный из них и

5 передает его значение на входы 25 всех блоков 2 обработки микрокоманд. Узел 21 приоритета сравнивает поступившее- на вход 25 значение приоритета со своим и при совпадении выдает значение единицы на своем первом выходе. Этот сигнал разрешает прохождение кода микрокоманды через элементы И 12-16 на первый адресный выход 27. Этот же сигнал поступает на выход 29. указывая блоку 5 коммутации на источник заявки на имитацию исполнения. При выявлении возможности успешного исполнения данного такта микрокоманды на вход 13 поступает значение единицы (сигнал ИСП|). Этот сигнал через первый вход узла 21 приоритета изменяет его состояние, в результате чего он запрещает прохождение кода микрокоманды на выход 27. Кроме того, сигнал ИСП| через элементы И 17 и ИЛИ 18 поступает в счетчик 11 тактов, разрешая вычитание единицы из его содержимого с приходом очередного синхросигнала в конце такта. Этим же синхросигналом повышается приоритет блока, если освободился один из высших приоритетов. При реализации последнего такта хранимой микрокоманды содержимое счетчика 11 тактов равно нулю, поэтому на выходе элемента ИЛИ 19 также появляется значение нуля, которое запрещает вычитание единицы из содержимого счетчика 11 тактов. С приходом на вход 23 очередного сигнала ИСП) триггер 20 сбрасывается в ноль. На его инверсном выходе появляется единица (сигнал СВ|). которая поступает на выход 30 и пятый вход узла приоритетов, приводя его в исходное состояние. В следующем такте данный блок 2 готов к приему новой микрокоманды.

Рассмотрим работу узла 21 приоритетов.

Узел 21 приоритета выполняет две функции: хранение и изменение в процессе работы приоритета блока и сравнение своего приоритета со значением, поступающим от узла 7 местного управления. Информация от блока 7 местного управления поступает через (2п-1)-разрядный вход 25 и содержит в старших п разрядах значение приоритета микрокоманды, выбранного для имитации исполнения, в унитарном коде. В младших (п-1) разрядах передается маска сдвига приоритета, которая содержит единицы в разрядах, соответствующих младшим приоритетам по отношению к свободному. Для хранения и изменения соответственного приоритета предназначен п-разрядный сдвиговый регистр 31. Он синхронизируется синхросигналами с входа 24 узла. При подаче на второй и третий входы регистра 31 комбинации 11 осуществляется запись значения по его первому входу, при комбинации 01 происходит сдвиг содержимого регистра в сторону старших разрядов, при комбинации 00 регистр хранит информацию. Если данный блок свободен, то на вхо

де 30 узла 21 приоритета установлено значение единицы, поэтому в младший разряд регистра в конце каждого такта записывается значение сигнала ЗАП| с входа 26. В старшие разряды регистра записываются нули. Когда данный блок занят микрокомандой, на входе 30 устанавливается ноль. При этом регистр 31 хранит значение приоритета. Если этот приоритет попадает в диапаз9н увеличиваемых, то регистр по очередному синхросигналу сдвигает хранимую единицу в сторону старших разрядов. Разрешение на сдвиг поступает с выхода второго элемента ИЛ И 42, который совместно с элементами И 37-40 реализует функцию

П-1 ().

Старший разряд не анализируется, поскольку далее невозможно увеличивать приоритет.

Если значение в регистре совпадает со значением в старших п разрядах входа 25,

то на выходе 29 узла появляется значение единицы. Функция сравнения реализуется элементами И 32-36 и элементом ИЛИ 41. На время действия синхросигнала элементы И 32-36 запираются нулем на выходе

элемента НЕ 47.

На старшие (п-1) разрядов второго выхода 23 поступает значение хранимого приоритета (младший разряд приоритета передавать нет смысла, поскольку в устройстве обязательно присутствует блок 2 обработки микрокоманды с младшим приоритетом). С приходом на вход 23 сигнала ИСП это же значение поступает на (п-1) младших разрядов выхода 28 э инверсном

виде. Для этих целей служат элементы И-Н Е 43-46. Значение на их выходах (ВКЛг1) подтверждает включение хранимой микрокоманды в исполняемую совокупность на данный такт.

Блок 5 коммутации предназначен для определения возможности совмещения нескольких микрокоманд и выработки набора управляющих сигналов для совокупности совмещаемых микрокоманд. На первый

вход 62 адреса от блока 4 постоянной памяти поступает информация о наборе узлов и устройств процессора, участвующих в исполнении данного такта конкретной микрокоманды. Она содержит код узла-источника

информации, обрабатываемой данной микрокомандой, код назначения (устройства или узла, куда записан результат исполнения). Остальные необходимые устройства имеют значения единицы в соответствуют щем разряде первого входа 52 адреса. На

второй вход 63 поступают синхросигналы. Входы с третьего по (п+2)-й 64-66 предназначены для приема информации о блоке 2 обработки микрокоманды, анализируемой в данный момент.

Первый выход 67 содержит полный набор управляющих сигналов для совокупности совмещаемых микрокоманд. Выходы с второго по (п+1)-й 68-70 предназначены для передачи в соответствующий блок 2 обработки микрокоманды подтверждения о включении данной микрокоманды в исполняемую совокупность микрокоманд (сигналы ИСП|).

Блок работает следующим образом.

На первый вход 62 адреса поступает заявка микрокоманды на устройства процессора из 1-го блока 2 обработки микрокоманды. Одновременно на одном из входов с третьего по (п+2)-й 64-66, подключенном к 1-му блоку 2 обработки микрокоманды, появляется значение единицы. Код источника с первого 62 поступает на первый дешифратор 48 и выбирает в качестве источника один из узлов процессора. Код назначения с первого входа 62 поступает на второй дешифратор 49 и выбирает один из узлов процессора. Эта информация в совокупности с остальной частью информации входа 62 адреса поступает на первый, второй и третий входы узла 50 имитации процессора.

Узел 50 имитации процессора состоит из набора ячеек 71, каждая из которых соответствует определенному узлу или функции процессора. Ячейки 71 объединены между собой связями, соответствующими связями между узлами процессора. На основании информации, поступившей на первый, второй и третий входы узла 50 имитации процессора проверяется готовность к работе требуемых устройств и возможность их соединения между собой в данном такте исполнения набора микрокоманд. При успешном исходе проверки на четвертом выходе узла 50 имитации процессора и, соответственно, на первом выходе 67 появляются сигналы, управляющие коммутацией и функционированием узла процессора. На первом выходе узла 50 имитации процессора в разряде, соответствующем выбранному источнику, появляется значение единицы, которое .через первый элемент ИЛИ 51 поступает на вход первого элемента И 55. На третьем выходе узла 50 имитации процессора в разряде, соответствующем выбранному преемнику, появляется значение единицы, которое через третий элемент ИЛИ 53 также поступает на вход первого элемента И 55. Во всех разрядах второго выхода узла 50

имитации процессора сохраняются значения нуля, вследствие чего на пыходе элемента НЕ 54 сохраняется значение единицы, полученное на выходе элемента И 55, посту- пающее на пятый вход узла 50 имитации процессора и фиксирующее связи, установленные для исполнения данной микрокоманды в данном такте. Это же значение при совпадении с единицей на i-м входе с треть0 его по (п+2)-й 64-66 на входах i-ro элемента И 56-58 вырабатывает на его выходе единицу (сигнал 1/1 СП|), которая фиксируется 1-м триггером (59-61).

С приходом на первый вход 62 адреса

5 информации и микрокоманды, хранящейся в (1+1)-м блоке 2 обработки микрокоманды. все разряды первого, второго и третьего выходов узлов 50 имитации процессора обнуляются, а значение на его четвертом выходе

0 сохраняется. Процесс проверки возможности исполнения анализируемой микрокоманды повторяется. При успешном исходе проверки набор управляющих сигналов на первом выходе 67 дополняется. Один из

5 триггеров с первого по п-й 59-61, соответствующий (1+1)-му блоку 2 обработки микрокоманды, устанавливается в единичное состояние. Этот процесс в данном такте повторяется для всех остальных блоков обра0 ботки микрокоманд до исчерпания очереди микрокоманд или до достижения отрицательного результата проверки.

Отрицательный результат проверки характеризуется значением нуля на всех раз5 рядах первого выхода узла 50 имитации процессора (отсутствует подтверждение готовности источника) или на всех разрядах третьего выхода узла 50 (отсутствует подтверждение готовности приемника), или на0 личием значения единицы хотя бы на одном разряде второго выхода узла 50 (невозможно подключить одно из требуемых устройств процессора). При этом состояние всего устройства управления не изменяется до конца

5 данного такта.

По окончании данного такта синхросигналом с второго входа 63 все триггеры с первого по п-й 59-61 и узел 50 имитации процессора устанавливаются в исходное со0 стояние. При этом все разряды первого выхода 67 обнуляются. В следующем такте повторяется описанный процесс.

Каждая ячейка 71 узла 50 имитации процессора предназначена для имитации одно5 го из функциональных узлов процессора (регистра, сумматора, мультиплексора и т.д.). Она связана с другими ячейками узла 50 имитации процессора и позволяет моделировать процесс занятия и освобождения связей имитируемого функционального уза. Сигналы, полученные в результате модеирования, управляют реальными входами- выходами имитируемого функционального зла. Совокупность ячеек 71 и связей между ними имитирует структуру процессора.

Первый вход 75 ячейки является одним из разрядов первого входа узла 50 имитации процессора и предназначен для указания данной ячейки в качестве источника. Второй вход 76 является одним из разрядов второго входа узла 50 имитации процессора и предназначен для указания данной ячейки в качестве требуемой для выполнения данной микрокоманды и не являющейся источником или приемником. Третий вход 77 является одним из разрядов третьего входа узла 50 имитации процессора и предназначен для указания данной ячейки в качестве приемника. Четвертый вход 63 предназначен для синхронизации ячейки 71, пятый вход 78 - для фиксации состояния входов и выходов ячейки, шестой вход 79 - для указания логической операции над входами ячейки с седьмого по ()-й (при значении нуля - выбор одного из единичных входов, при значении единицы - конъюнкция над входами). Входы с седьмого по (р+6)-й 80-83 предназначены для приема сигналов-заявок от ячеек, имитирующих узлы, подключенные к входам узла, соответствующего данной ячейке. Входы с ( no (p+q+6)-u 84-86 предназначены для приема сигналов-ответов от ячеек, имитирующих узлы, подключенные к выходам узла, соответствующего данной ячейке. Входы с (р+ q+7)-ro по +Јq+6)-u 87-89 предназначены для приема сигналов - подтверждений срабатывания ячеек, имитирующих узлы, подключенные к выходам узла, соответствующего данной ячейке.

Первый выход 90 является одним из разрядов первого выхода узла 50 имитации процессора и передает подтверждение о готовности к использованию данной ячейки в качестве источника. Второй выход 91 является одним из разрядов второго выхода узла 50 имитации процессора и предназначен для передачи сообщения о том, что данная ячейка необходима для реализации данной микрокоманды, но не может быть задействована в текущем такте. Третий выход 92 являет одним из разрядов третьего выхода узла 50 и передает подтверждение о готовности использовать данную ячейку в качестве приемника. Четвертый выход 93 предназначен для передачи подтверждения срабатывания данной ячейки. Выходы с пятого по (р+4)-й 94-97 предназначены для выдачи ответных сигналов ячейкам, от которых поступили сигналы-заявки, Они же образуют первый выход 67 блока 5 коммутации. Выходы с ( по (р+р+4)-й 98-100 предназначены для передачи сигналов-заявок ячейкам, имитирующим узлы, подклюценные к выходам узла, соответствующего данной ячейке.

Ячейка может имитировать функциональные узлы процессора. При значении нуля на шестом входе 79 ячейка имитирует

0 многовходовый функциональный узел, у которого может быть задействован только один из входов. В целях упрощения механизма выбора входа все входы располагаются г порядке убывания приоритетов связей.

5 При установлении связи через более предпочтительный вход все менее предпочтительные входы подавляются. Вопрос о приоритете (предпочтительности) связей решается исходя из конкретной структуры

0 процессора. К узлам такого типа можно отнести, например, мультиплексоры, регист-, ры с мультиплексированием входов и ряд других узлов. При значении единицы на шестом входе 79 ячейка имитирует многовхо5 довый функциональный .узел, для работы которого необходимо обязательно подключение всех связей на входе. К таким узлам могут быть отнесены сумматоры, память, регистры со сложным управлением и т.д. Тип

0 каждой конкретной ячейки определяется при проектировании устройства управления и значение на ее шестом входе 79 задается в виде константы.

Ячейки подключаются друг к другу сле5 дующим образом.

Допустим, что к входам k-й ячейки требуется подключить две ячейки i и j. а к выходу - ячейки I и т. Выходы ячеек I и j могут быть подключены и к другим ячейкам кроме

0 рассматриваемой k. К входам ячеек t и m также могут быть подключены и другие ячейки. Следовательно, для k-й ячейки pk и qk равно 2,

По одному из выходов с (р+5)-го по5 (p+q+4)-ft 98-100 i-я и j-я ячейки (например, шестой 98 и для 1-й ячейки и седьмой 99 для j-й ячейки) подключены, соответственно, к седьмому входу 80 и восьмому входу 81 k-й ячейки. Соответственно, пятый выход 94 k-й

0 ячейки подключен к входу (pi+7) 84 1-й ячейки, а шестой выход 95 k-й ячейки - к входу 85 (pj+8) j-й ячейки, Четвертый выход 93 k-й ячейки соединен с входами (pi+ql+7) 87 1-й ячейки и (pj+qj+8) J-й ячейки. Седьмой (рк+5)

5 выход 98 k-й ячейки соединен с одним из входов с седьмого по (рт+6)-й, например, с восьмым, входом 81 1-й ячейки, а восьмой (pk+б) выход k-й ячейки соединен с одним из входов с седьмого по (р+6)-й (например, с восьмым входом 81) т-й ячейки. Тогда шеетой выход 95 1-й ячейки соединен с девятым входом (pk+7) 84 k-й ячейки, а шестой выход 95 m-й ячейки соединен с десятым входом (pk+7) 85 k-й ячейки. Четвертые выходы 93 1-й и m-й ячеек подключены к одиннадцатому (pk+qk+7) 87 и к двенадцатому (pk+qk+8) 88 входам k-й ячейки, Кроме того, эти же выходы подключены к соответствующим входам ячеек, связанных с входами 1-й и m-й ячеек.

Рассмотрим функционирование узла 50 имитации процессора на примере описанной цепочки.

Допустим, что 1-я ячейка выбрана в качестве источника (на ее первый вход 75 подан сигнал единицы), а m-я ячейка выбрана в качестве приемника (на ее третий вход 77 подан сигнал единицы). Допустим, что к-я ячейка имитирует мультиплексор и связь между 1-й и m-й ячейками возможна лишь через нее. Тогда на третьем выходе 125 узла 72 запоминания предшественника 1-й ячейки появляется сигнал единицы, который, поступая на второй вход 125 -узла 73 запоминания преемника,вызывает появление значений единицы на всех выходах с (pi+5) no (pi+ql+4) 98-100. Сигналы с этих выходов подаются на соответствующие входы всех ячеек, связанных с i-й ячейкой, в том числе, на седьмой вход 80 k-й ячейки. На третьем выходе 125 узла 72 запоминания предшественника k-й ячейки появляется сигнал единицы, который через второй вход 125 узла 73 запоминания преемника k-й ячейки вызывает появление значения единицы на восьмом выходе 99. Эти значения поступают на восьмые входы 81, m-й и 1-й ячеек. 1-я ячейка работает аналогично k-й ячейке.

В m-й ячейке значение единицы с третьего выхода 125 узла 72 запоминания предшественника поступает на второй вход 125 узла 73 запоминания преемника и вызывает появление значения единицы на третьем выходе 92, что подверждает готовность преемника. На втором выходе 123 узла 73 запоминания преемника устанавливается сигнал единицы, который поступает на узел 72 запоминания предшественника и вызывает-повторение состояния входов с седьмого по (рт+б)-й 80-83, на выходах с пятого по (рт+4)-й 94-97. Это состояние характеризуется наличием единицы на шестом выходе 95 и нулями на остальных. Значение единицы на третьем 125 и четвертом 123 входах фиксатора состояния 74 вызывает появление значения единицы на четвертом выходе 93, что означает подтверждение срабатывания m-й ячейки. На выходах с (pm+5)-ro no (pm+qm+4)-u 98-100 установлено значение

нуля, поэтому ячейки, являющиеся преемниками m-й ячейки,не затрагиваются. Сигналы с выходов с пятого по (p-f 4}-й 94-97 m-й ячейки поступают на соответствующие входы с (р+7)-го по (р+р+6)-й 84-86 всех ячеек, являющихся преемниками m-й, в том числе значение единицы поступает на десятый вход 85 k-й ячейки, а остальные ячейки получают значение нуля. В k-й ячейке поступле0 ние единицы на десятый вход 85 вызывает повторение состояния девятого входа 84 (нуля) и десятого входа 85 (единицы) на седьмом 98 и восьмом 99 выходах, а также появление единицы на втором выходе 123 узла

5 73 запоминания преемника, в результате чего так же, как в m-й ячейке, на четвертом выходе 93 появляется значение единицы, а на пятом 94 и шестом 95 выходах повторяются значения седьмого 80 (единица) и вось0 мого 81 (ноль) входов. Так как состояние седьмого выхода 98 k-й ячейки изменилось с единицы на ноль, то 1-я ячейка возвращается в исходное состояние. Поскольку на вход (pi+7) 84 1-й ячейки поступает единица

5 с пятого выхода 94 k-й ячейки, на втором выходе 123 узла 73 запоминания преемника 1-й ячейки появляется значение единицы, которое, поступая на узел 72 запоминания предшественника, вызывает появление

0 единицы на первом выходе 90 (что означает готовность источника), а поступая на фиксатор 74 состояния, вызывает появление единицы но четвертом выходе 93. На выходах с (pi+5)-ro no (pi+qi+4)-u 98-100 повторяется

5 состояние входов с (pi+7)-ro no (pit-qi+6)-u 84-86.

Значения единицы на первом и третьем выходах узла 50 имитации процессора вызывают появление единицы на пятом входе

0 78, которое передается на пятые входы 78 всех ячеек. Состояние ячеек, имеющих значение единицы на четвертом выходе 93, фиксируется, вследствие чего на вторых выходах 124 их фиксаторов состояния 74 появ5 ляется значение единицы, которое фиксирует состояние выходов с пятого по ( 94-97 и с ( no (p+q+4)-u 98-100 в узле 72 запоминания предшественников и узле 73 запоминания преемников.

0 Допустим, что в данном тексте неообхо- димо также передать информацию из j-й ячейки источника в -ю ячейку приемника, j-я ячейка начинает функционировать так же, как и 1-я ячейка, однако вследствие того, что

5 все выходы k-й ячейки зафиксированы, в 1-ю ячейку через k-ю ячейку информация не поступает. Если между J-й ячейкой и 1-й ячейкой нет связи, кроме как через k-ю ячейку, то ни на один из выходов с седьмого по (р+6)-й 80-83 1-й ячейки не поступает значение единицы, следовательно, на третьем вы- ходе 921-й ячейки не может быть выработан сигнал подтверждения приемника. Вследствие этого (поскольку другие ячейки в качестве преемников не отмечены) ни на один из входов с (pj+7)-ro no (pj+qj+6)-ft 84-86 J-й ячейки не поступают ответные сигналы и не вырабатывается сигнал подтверждения готовности приемника на первом выходе 90 j-й ячейки. Из-за отсутствия подтверждения готовности источника и приемника на первом и третьем выходах узла 50 имитации процессора состояние устройства управления не изменяется до конца данного такта.

На первом выходе 67 блока коммутации присутствуют сигналы, управляющие входами узлов, соответствующих зафиксированным ячейкам. По окончании такта сигналом на четвертом входе 63 всех ячеек сбрасываются в исходное состояние все фиксаторы состояний 74, вследствие чего выходы всех ячеек освобождены и блок 5 коммутации приходит в исходное состояние.

Блок 7 (фиг, 9) местного управления предназначен для синхронизации работы устройства в целом, а также для управления приемом микрокоманд в блоки 2 обработки микрокоманд и выдачей информации из них в блок 5 коммутации.

Первый, второй и четвертый выходы блока 7 местного управления предназначены для выдачи синхросигналов в блоки 2 обработки микрокоманд, блок 5 коммутации и регистр 6 микроопераций. Посредством второго выхода 25 в блоки 2 обработки микрокоманды поступает информация о приоритете блока 2 обработки микрокоманд, подключаемого к блоку 5 коммутации (сигналы ППР , где J 1п), благодаря чему

блоки 2 обработки микрокоманд подключаются к блоку 5 коммутации последовательно в порядке убывания приоритетов. Посредством этого же выхода (младшие (п-1) разрядов - сигналы СД, где j 2, .,,, п) осуществляется управление изменением приоритетов блоков 2 обработки микрокоманд.

Выходы 26 с пятого по (п+4)-й предназначены для выбора свободного блока 2 обработки микрокоманд для загрузки очередной микрокоманды из декодера (сигналы ЗАПь где 1 1п).

Входы 28 с первого по n-й предназначены для приема информации о приоритетах блоков 2 обработки микрокоманд (в старших разрядах - сигналы ПРг1 а в младших разрядах - сигналы ВК/М, где f - номер блока, J 2п).

Через входы 29 с (п+1)-го по 2п-й осуществляется прием информации о занятости

соответствующего блока 2 обработки микрокоманд (сигналы CBOBi, где I 1п).

2п+1-й вход 9 является входом синхронизации, на который подаются синхросигналы

(СИ) от внешнего по отношению к устройству синхрогенератора.

Блок 7 местного управления состоит из узла 140 приоритета, узла 141 шифратора распределения свободных блоков обработки микрокоманд 141 и узла 142 синхронизации.

Узел 140 приоритета может быть реализован в виде комбинационной схемы, выходы которой описываются логическими

уравнениями;

0

5

0

5

0

5

0

5

ппр(иГпр|лвкл|))и(А (())) Cflj U (5пр|)

Узел 141 шифратора распределения свободных блоков обработки микрокоманд также может быть реализован в виде комбинационной схемы, выходы которой описываются логическим уравнением:

1 - 4

ЗАП| СВОБ| А ( П CBk)

При этом предполагается, что СДп, СВ0, ПР|П+Г - 0.

Узел 142 синхронизации может быть реализован в виде формирователя синхроимпульсов.

Формула изобретения

1. Устройство управления микропрограммной ЭВМ, содержащее блок местного управления, блок постоянной памяти и регистр микроопераций,синхровход которого соединен с первым выходом блока местного управления,.выход регистра микрооперацией является выходом устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены п блоков обработки микрокоманд (где п 2), блок элементов ИЛИ и блок коммутации, причем вход микрокоманды устройства соединен с входами данных всех блоков обработки микрокоманды, адресные выходы всех блоков обработки микрокоманды соединены с соответствующими входами блока элементов ИЛИ, выход которого соединен с адресным входом постоянной памяти, выход которого соединен с первым информационным входом блока коммутации, первый информационный выход каждого блока обработки микрокоманды соединен с k-м информационным входом (где k - 2jvn) блока коммутации (где п - максимальное количество одновременно выполняемых микропрограмм 21) первый выход блока коммутации соединен с информационным входом регистра микроопераций, k-й выход блока коммутации соединен с первым управляющим входом (k-iy-ro блока обработки микрокоманды, второй и третий выходы блока местногоуправлениясоединенысоответственно с вторым и третьим управляющими входами всех блоков обработки микрокоманды, четвертый выход блока местного управления подключен к управляющему входу блока коммутации, (к+4}-й выход блока местного управления соединен с четвертым управляющим входом k-го блока обработки микрокоманды, вторые и третьи информационные выходы всех блоков обработки микрокоманды соединены соответственно с первой и второй группами информационных входов блока местного управления, вход синхронизации устройства соединен с входом синхронизации блока местного управления, причем блок местного управления содержит узел приоритета, шифратор распределения свободных блоков обработки микрокоманды и узел синхронизации, причем информационные входы с первого по л-й блока местного управления соединены соответственно с первого по входами узла приоритета, информационные входы с первого по n-й соединены соответственно с первого по n-й входами шифратора распределения свободных блоков обработки микрокоманды, вход синхронизации блока местного управления соединен с входом синхронизации, выход узла приоритета является третьим выходом блока местного управления, выходы с первого по n-й шифратора распределения свободных блоков обработки микрокоманды являются соответственно с пятого по (п+4)-й выходами блока местного управления, первый, второй и третий выходы узла синхронизации являются соответственно вторым, четвертым, первым выходами блока местного управления, причем каждый блок обработки микрокоманды содержит регистр базового адреса, счетчик тактов, две группы элементов И, элемент И, два элемента ИЛИ, триггер и узел приоритета, старшие разряды входа данных блока обработки микрокоманды подключены к информационному входу регистра базового адреса, младшие разряды входа данных блока обработки микрокоманды подключены к информационному входу счетчика тактов, первый управляющий вход блока обработки микрокоманды подключен к первому входу элемента И, первому управляющему входу узла приоритета и входу сброса триггера, второй управляющий вход блока обработки микрокоманды соединен с вторым упрапляющим входом узла приоритета, входлми записи регистра базового адреса и счетчика тактов, первым входом первого элемента ИЛИ, а 5 также с синхровходом триггера, третий управляющий вход блока обработки микрокоманды соединен с информационным входом узла приоритета, четвертый управляющий вход блока обработки микрокоман0 ды соединен с синхровходами узла приоритета и регистра базового адреса, а также со счетным входом счетчика тактов, вход разрешений счета которого соединен с выходом первого элемента ИЛИ, второй

5 вход которого соединен с выходом элемента И, второй вход которого соединен с информационным входом триггера и выходом второго элемента ИЛИ, выходы регистра базового адреса и счетчика тактов соедине0 ны с первыми входами элементов И соответственно первой и второй групп, вторые входы которых соединены с информационным выходом узла приоритета и явлются первым информационным выходом блока

5 обработки микрокоманды, второй информационный выход которого явля-ется выходом кода приоритета узла приоритета, третий управляющий вход которого соединен с выходом триггера и подключен к третьему ин0 формационному входу блока обработки микрокоманды, входы второго элемента ИЛИ соединены с выходами счетчика тактов, выходы элементов И первой и второй групп образуют адресный выход блока об5 работки микрокоманды.

2. Устройство по п. 1,отличающее- с я тем, что узел приоритета содержит сдвиговый регистр, элемент НЕ, две группы эле0 ментов И, два элемента ИЛИ и группу элементов И-НЕ, причем первый управляющий вход узла подключен к первым входам элементов И-НЕ группы, первый выход сдвигового регистра соединен с первыми

5 входами первых элементов И первой и второй группы, р-выход сдвигового регистра (где р 2, п-1) соединен с первыми входами р-х элементов И первой и второй групп и вторым входом (р+1)-го элемента И-НЕ груп0 пы, n-й выход сдвигового регистра соединен с первым входом п-го элемента И первой группы и вторым входом (п-1 )-го элемента И-НЕ группы, с второго по n-й выходы сдвигового регистра и выходы элементов И-НЕ

5 группы образуют выход кода приоритета, вторые входы элементов И первой и второй групп образуют информационный вход узла, синхровход которого подключен к синх- ровходу сдвигового регистра и через элемент НЕ к третьим входам элементов И

первой группы, выходы которых соединены с входами первого элемента ИЛИ, выход которого является информационным выходом узла, второй управляющий вход которого подключен к информационному входу сдвигового регистра, первый вход задания

режима которого соединен с выходом второго элемента ИЛИ, входы которого соединены с выходами элементов И второй группы, третий управляющий вход узла подключен к второму входу задания режима сдвигового регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

| Микропрограммный процессор | 1981 |

|

SU1037262A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

Изобретение относится к вычислительной технике и предназначено для управления устройствами процессора микропрограммной ЭВМ. Цель изобретения - повышение быстродействия. Предложенное устройство содержит блок 2 постоянной памяти, регистр 6 микроопераций, п блоков 2 обработки микрокоманд, где n S2, блок 4 элементов ИЛИ, блок 5 коммутации и блок 7 местного управления. Работа устройства управления основана на принципе конвейерной обработки последовательности микрокоманд. Процесс формирования управляющей совокупности микросигналов заключается в выделении необходимых устройств процессора и установлении связей между ними последовательно для каждой из исполняемых одновременно микрокоманд в порядке убывания приоритета. Информация о приоритете микрокоманды постоянно сообщается блоком обработки микрокоманд в блок местного управления, который подключает к блоку коммутации блок обработки микрокоманд с максимальным приоритетом. Таким образом осуществляется асинхронное управление очередностью подключения блоков обработки микрокоманд. 1 з.п. ф-лы, 9 ил. ON Ч 00 fe в фиг.1

Фм.1

о со

О5 (Ј

а J5 «5a «Ч| h

62

6465 §6

TJMgiffl

1

Г 49 }

5В

а ш ш

Л {

Ню

лЬ

г

Ш

ф

«в f

59

W

63

67

Фиг.6

о

т со

Ч™ ОЗ (О

к

I

5 S

fe§

Фиг 9

| Прибор для схватывания жезла на ходу поезда | 1919 |

|

SU1720A1 |

| Способ приготовления ртутной мази | 1924 |

|

SU1870A1 |

Авторы

Даты

1991-11-15—Публикация

1989-03-24—Подача