Изобретение относится к вычислительной технике и может быть использовано в процессоре электронной вычислительной машины (ЭВМ).

Цель изобретения - повышение надежности за счет изоляции сбойной информации.

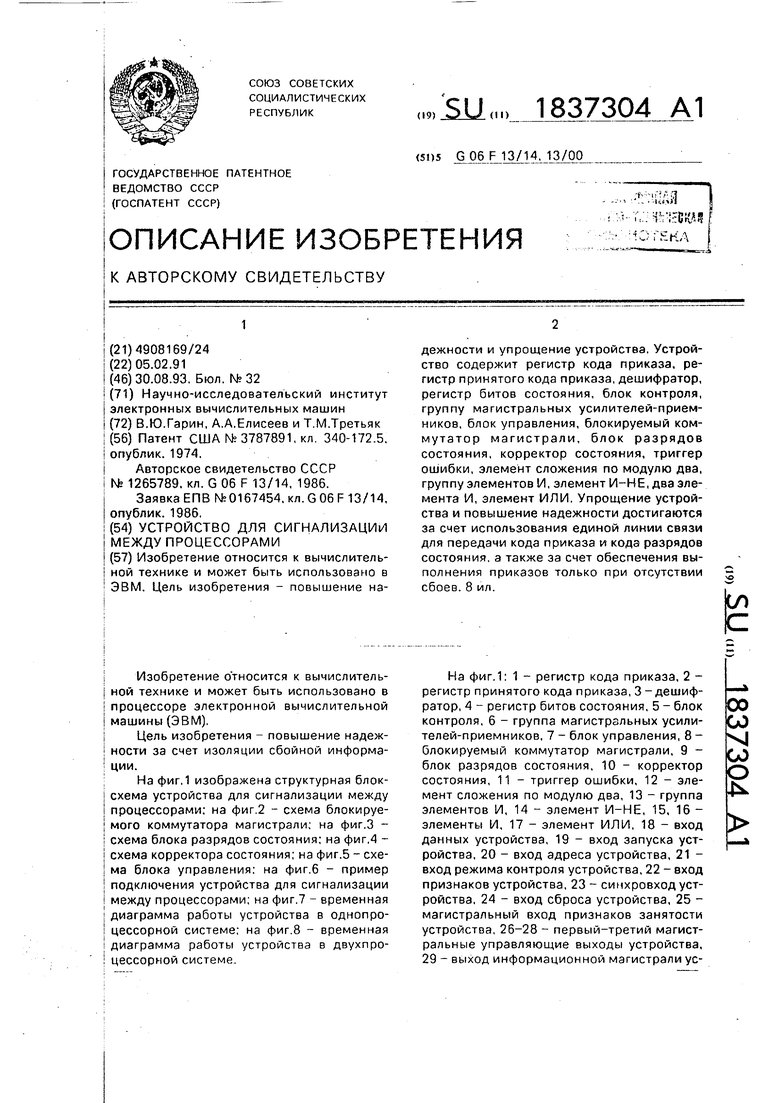

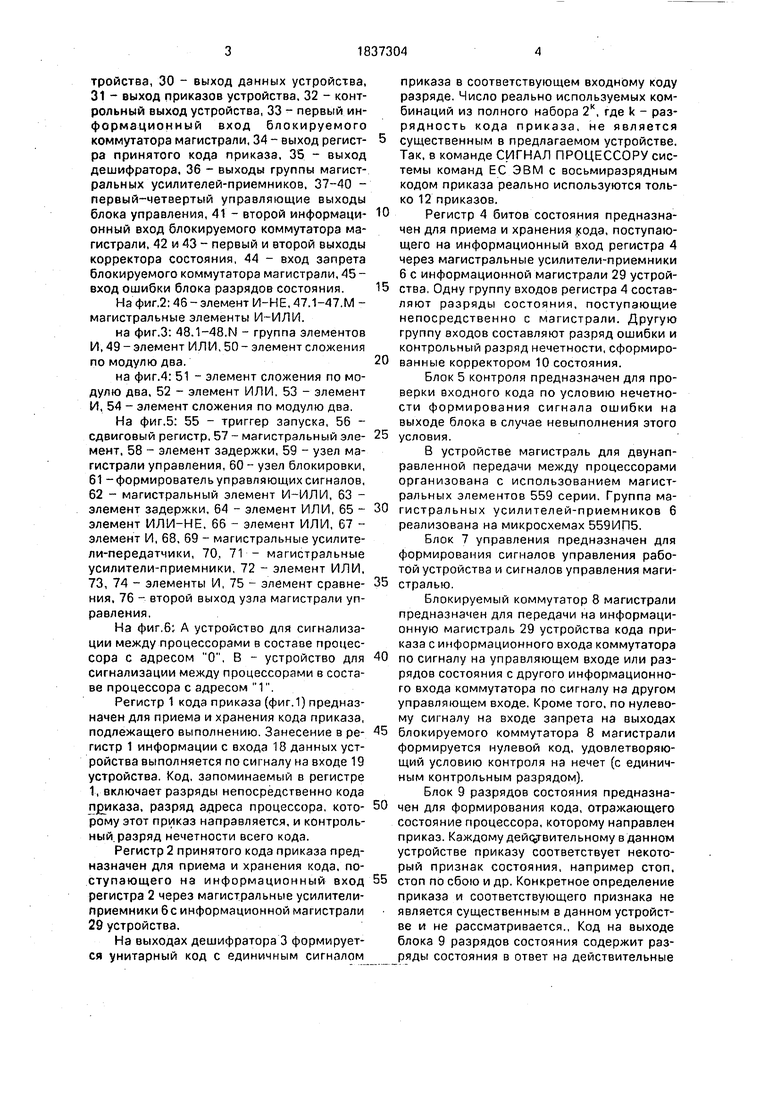

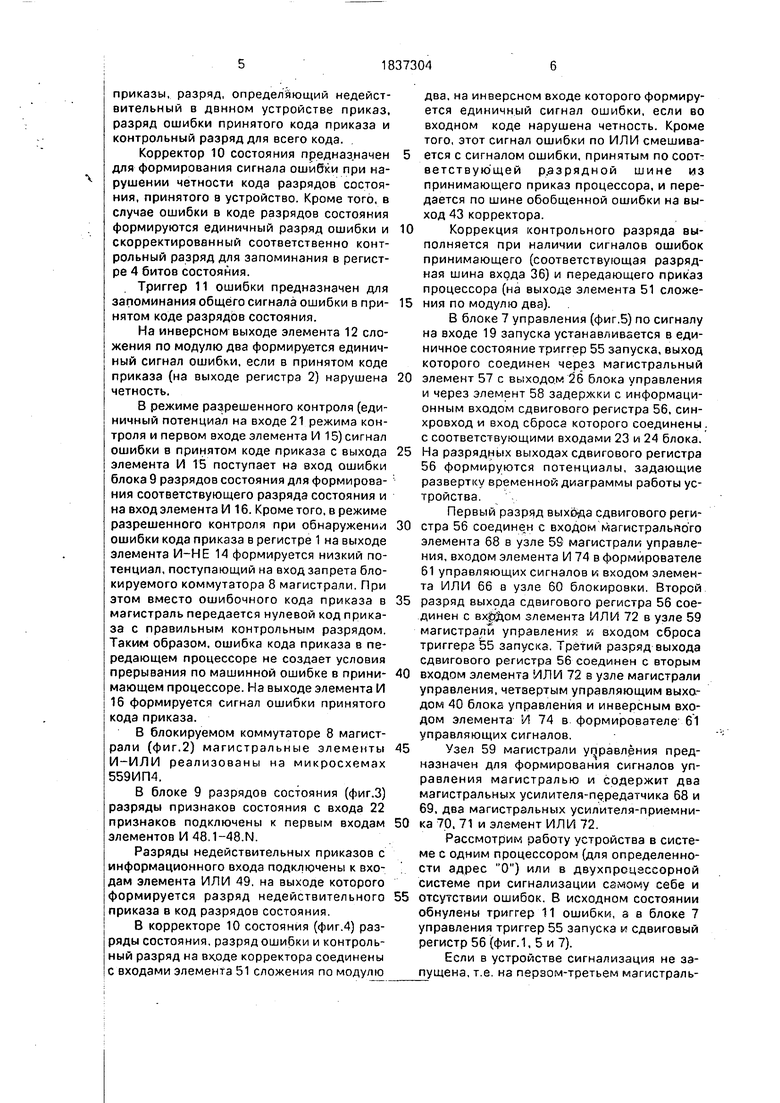

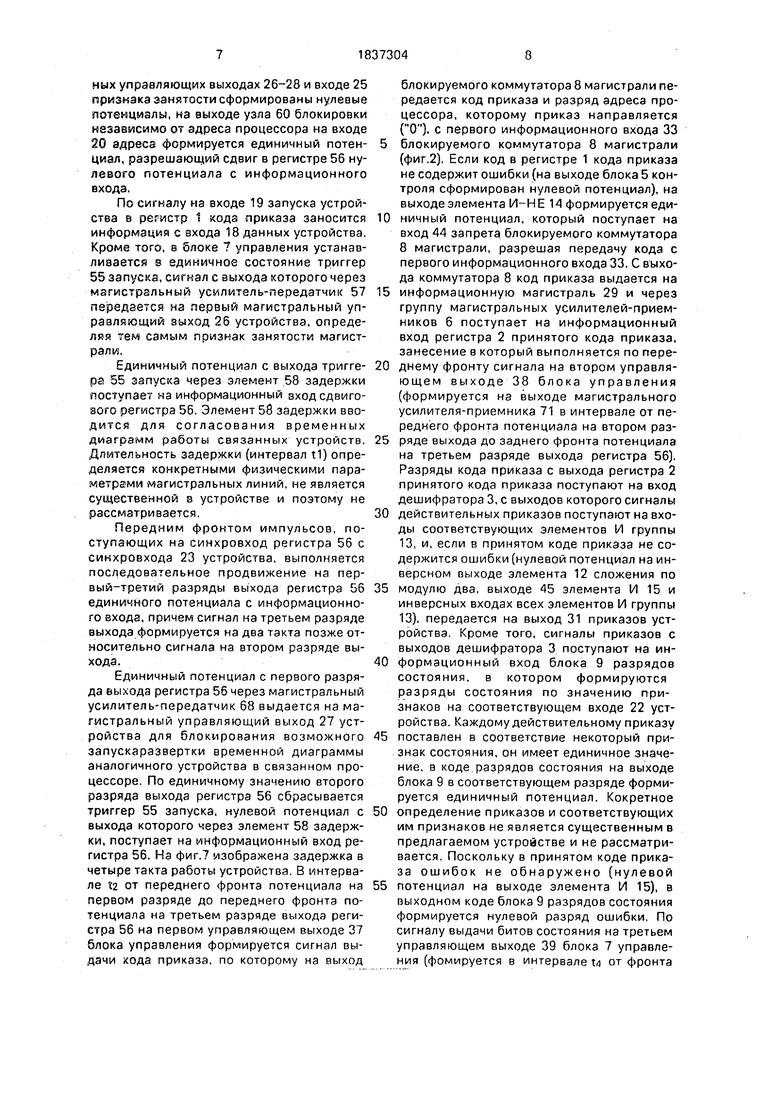

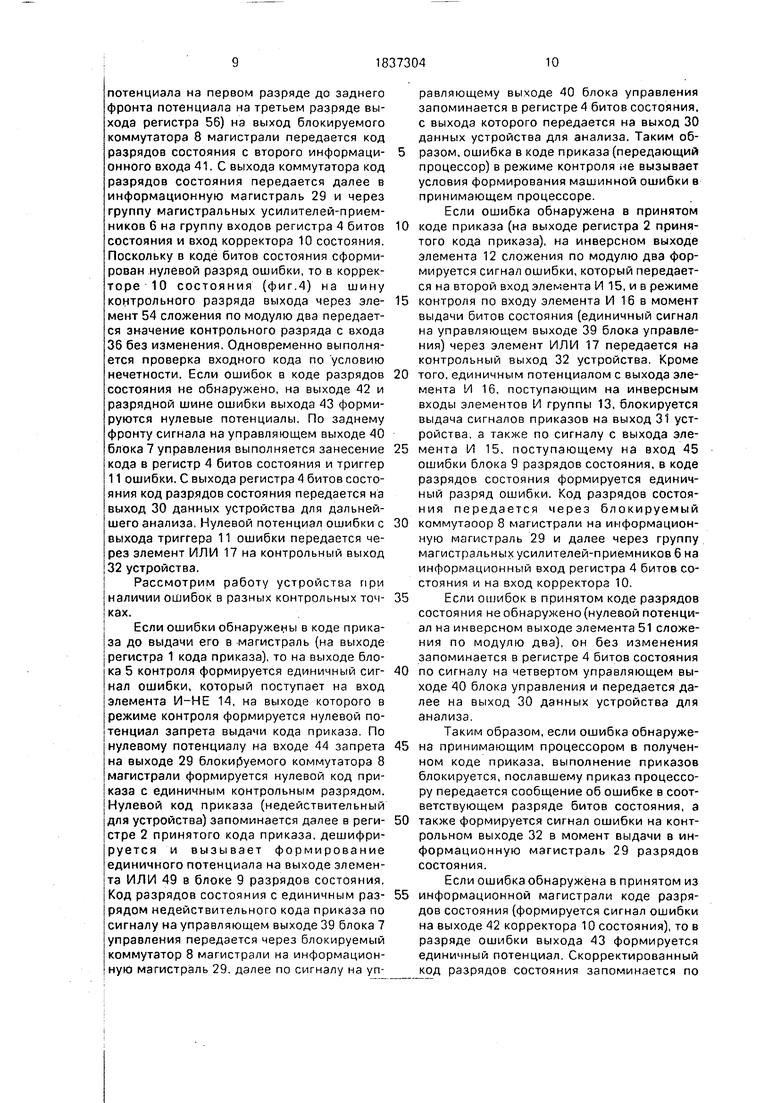

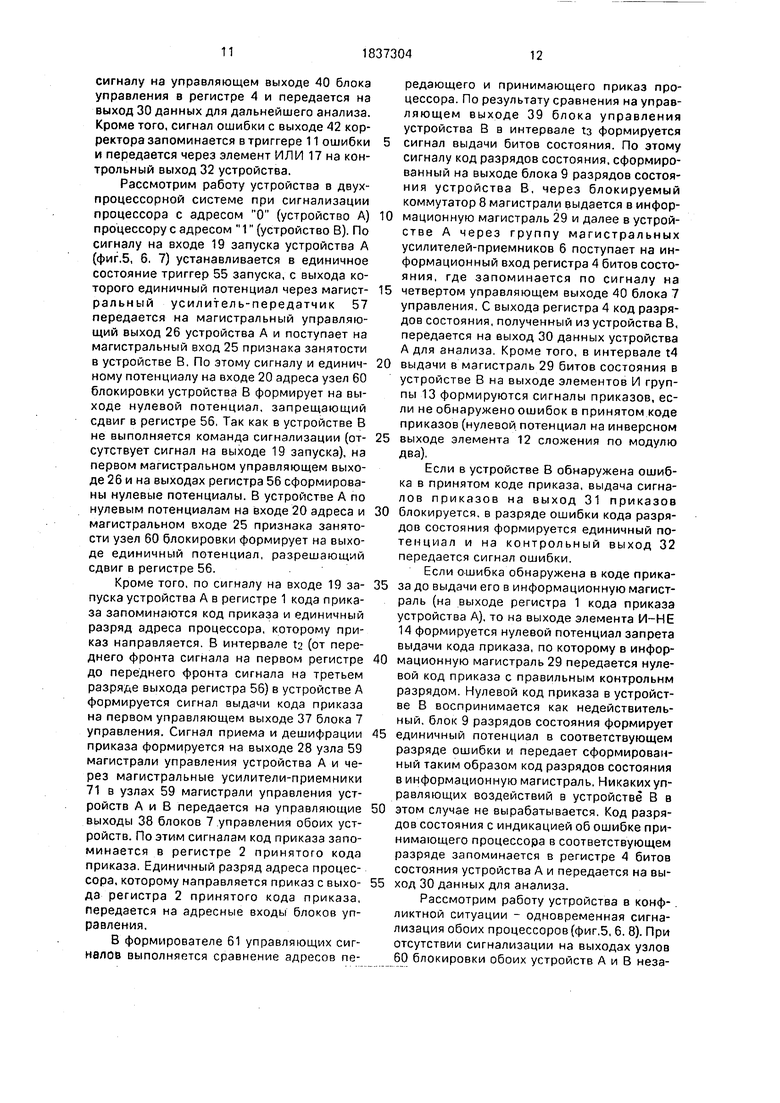

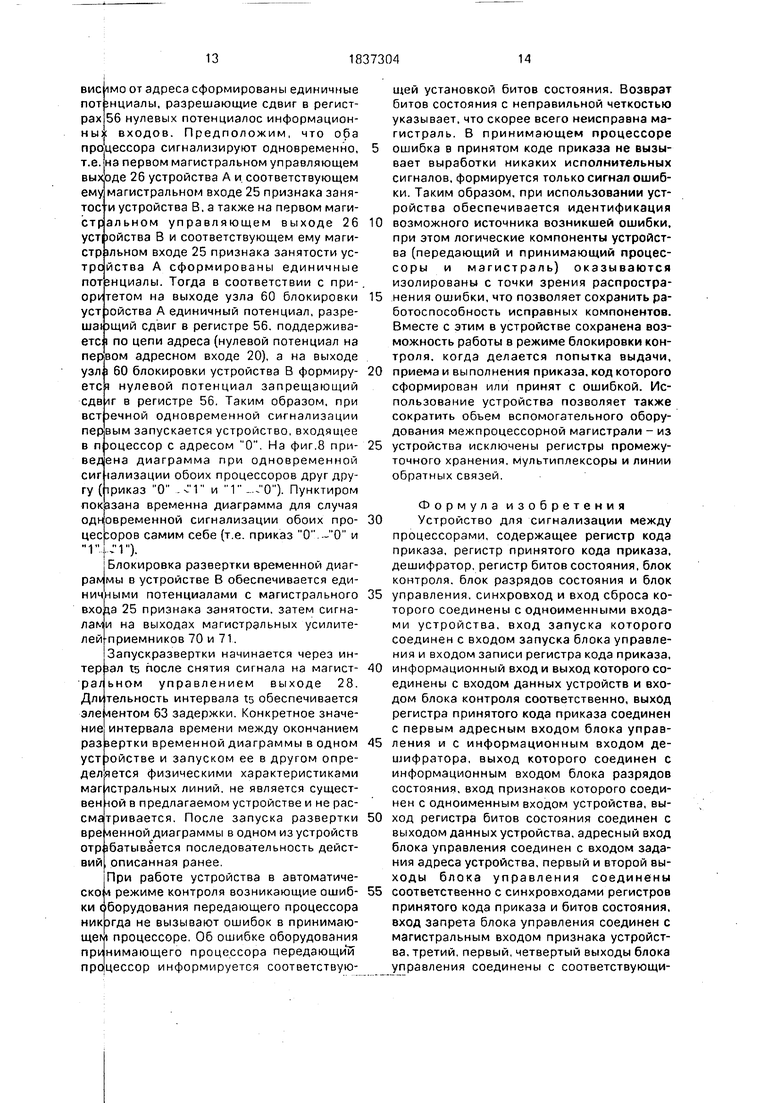

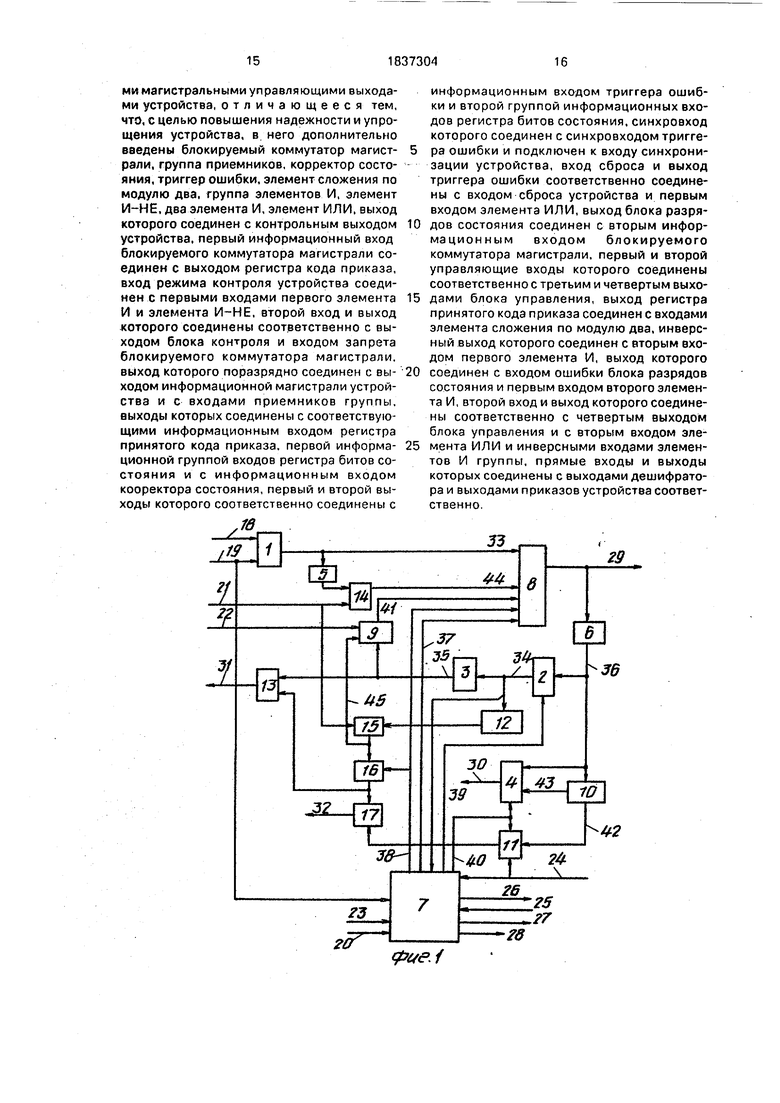

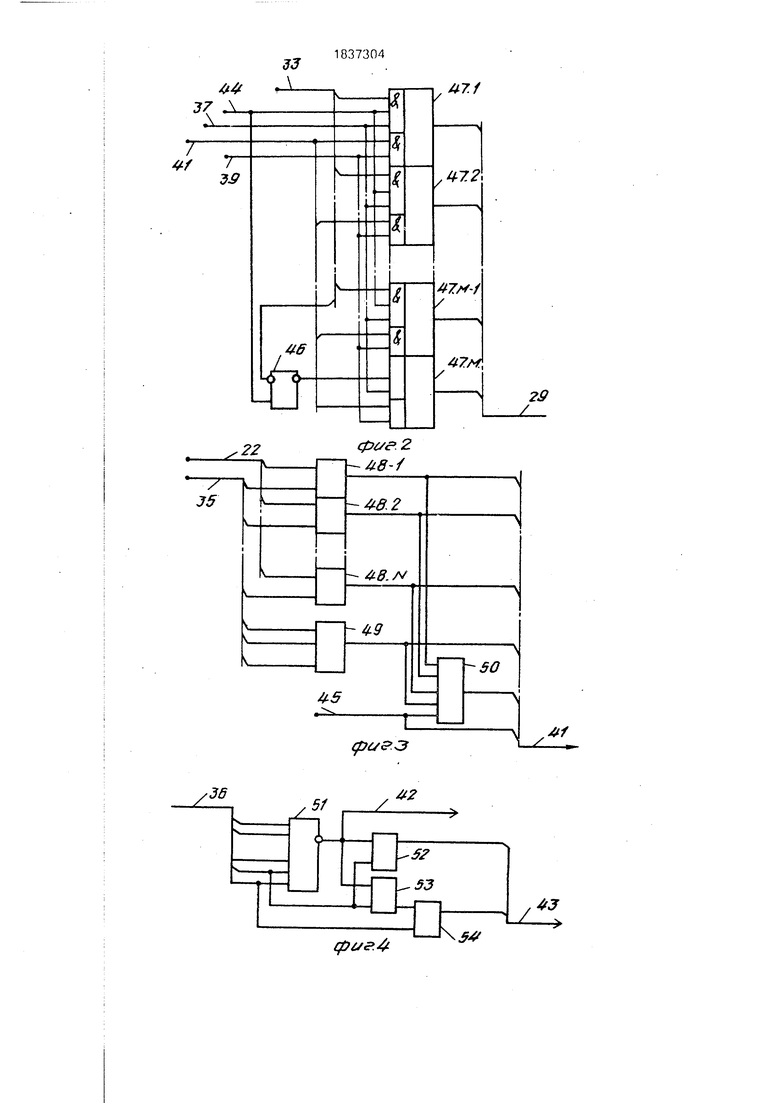

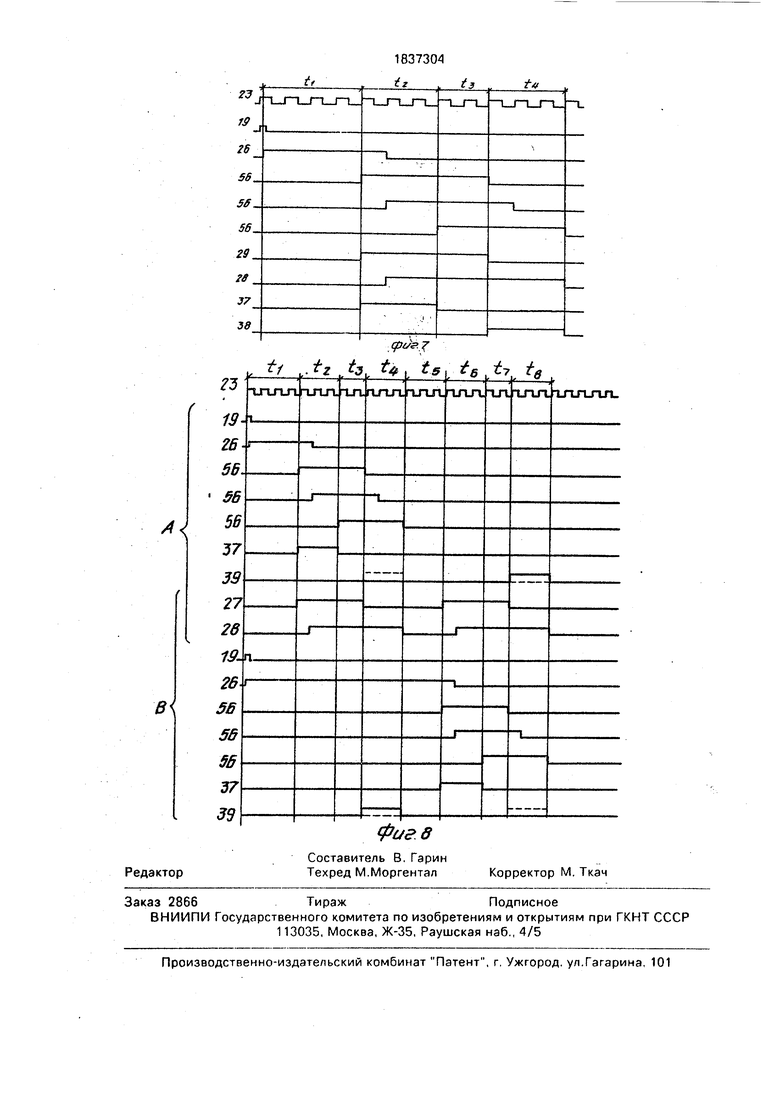

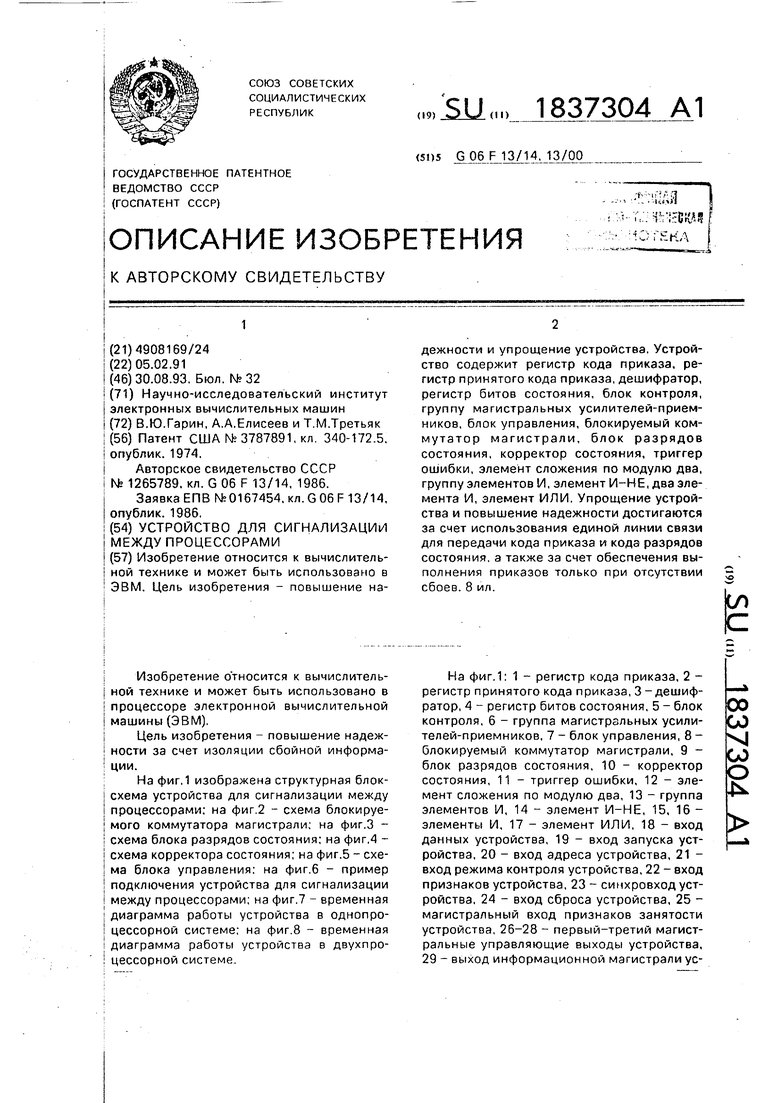

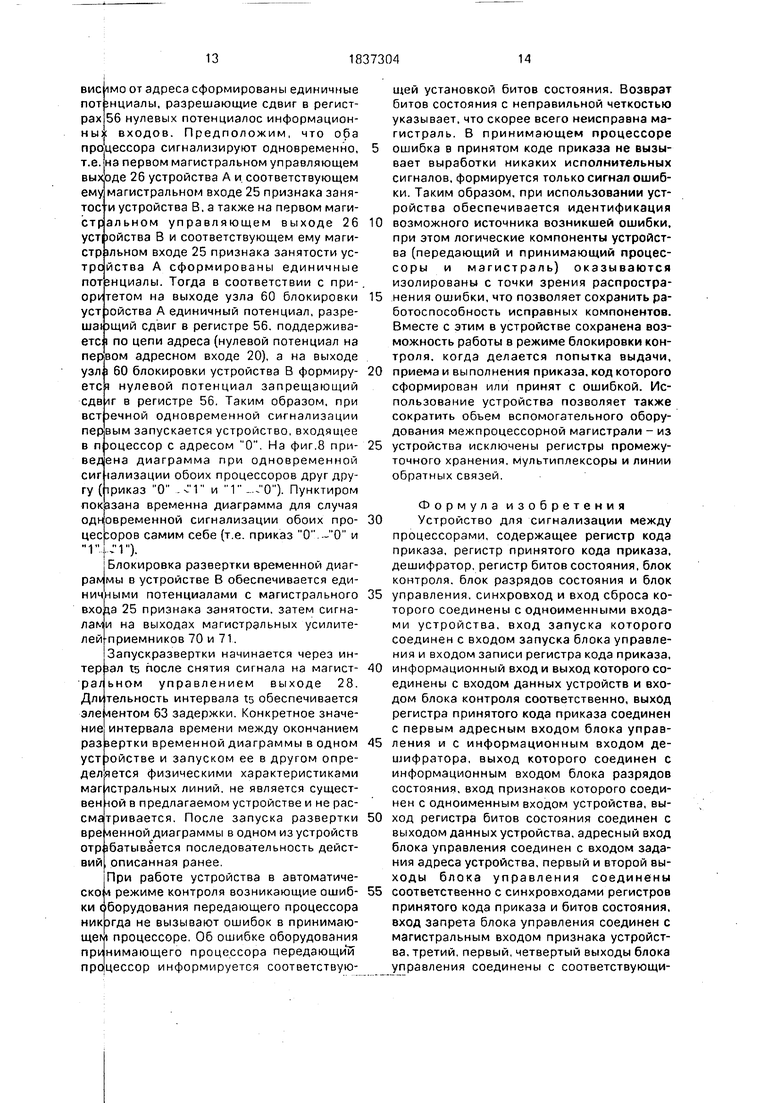

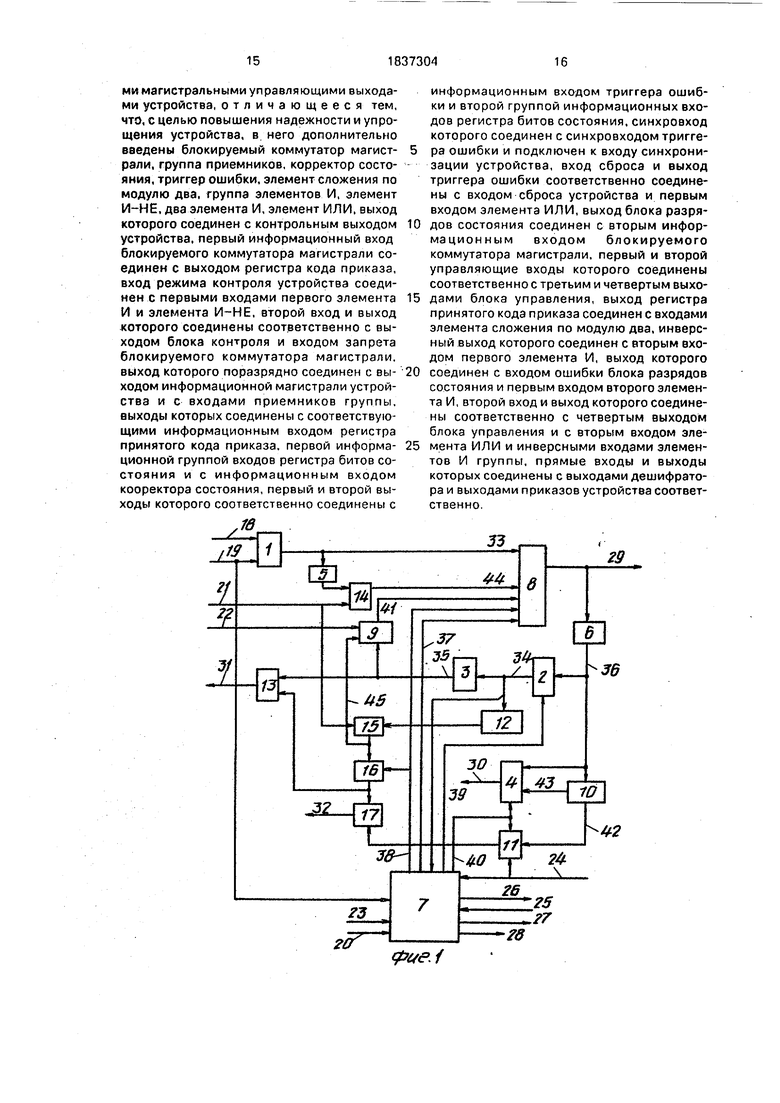

На фиг.1 изображена структурная блок- схема устройства для сигнализации между процессорами: на фиг.2 - схема блокируемого коммутатора магистрали; на фиг.З - схема блока разрядов состояния; на фиг.4 - схема корректора состояния; на фиг.5 - схема блока управления: на фиг.6 - пример подключения устройства для сигнализации между процессорами; на фиг.7 - временная диаграмма работы устройства в однопроцессорной системе; на фиг.8 - временная диаграмма работы устройства в двухпроцессорной системе.

На фиг.1: 1 - регистр кода приказа, 2 - регистр принятого кода приказа, 3-дешифратор, 4 - регистр битов состояния, 5 - блок контроля, 6 - группа магистральных усилителей-приемников, 7 - блок управления, 8 - блокируемый коммутатор магистрали, 9 - блок разрядов состояния, 10 - корректор состояния, 11 - триггер ошибки, 12 - элемент сложения по модулю два, 13 - группа элементов И, 14 - элемент И-НЕ, 15, 16 - элементы И, 17 - элемент ИЛИ, 18 - вход данных устройства, 19 - вход запуска устройства, 20 - вход адреса устройства, 21 - вход режима контроля устройства, 22 - вход признаков устройства, 23 - синхровход устройства, 24 - вход сброса устройства, 25 - магистральный вход признаков занятости устройства, 26-28 - первый-третий магистральные управляющие выходы устройства, 29 - выход информационной магистрали ус00

со

XI

со о J

тройства, 30 - выход данных устройства, 31 - выход приказов устройства, 32 - контрольный выход устройства, 33 - первый информационный вход блокируемого коммутатора магистрали, 34 - выход регист- ра принятого кода приказа. 35 - выход дешифратора, 36 - выходы группы магистральных усилителей-приемников, 37-40 - первый-четвертый управляющие выходы блока управления, 41 - второй информаци- онный вход блокируемого коммутатора магистрали, 42 и 43 - первый и второй выходы корректора состояния, 44 - вход запрета блокируемого коммутатора магистрали, 45 - вход ошибки блока разрядов состояния.

На фиг.2:46 - элемент И-НЕ, 47.1-47.М- магистральные элементы И-ИЛИ.

на фиг.З: 48.1-48,N - группа элементов И, 49 - элемент ИЛИ, 50 - элемент сложения по модулю два.

на фиг.4: 51 - элемент сложения по модулю два, 52 - элемент ИЛИ. 53 - элемент И, 54 - элемент сложения по модулю два.

На фиг.5: 55 - триггер запуска, 56 - сдвиговый регистр, 57 - магистральный эле- мент, 58 - элемент задержки, 59 - узел магистрали управления, 60 - узел блокировки,

61-формирователь управляющих сигналов,

62- магистральный элемент И-ИЛИ, 63 - элемент задержки, 64 - элемент ИЛИ, 65 - элемент ИЛИ-НЕ. 66 - элемент ИЛИ, 67 - элемент И, 68, 69 - магистральные усилители-передатчики, 70, 71 - магистральные усилители-приемники, 72 - элемент ИЛИ, 73, 74 - элементы И, 75 - элемент сравне- ния, 76 - второй выход узла магистрали управления.

На фиг.6; А устройство для сигнализации между процессорами в составе процессора с адресом О, В - устройство для сигнализации между процессорами в составе процессора с адресом 1.

Регистр 1 кода приказа (фиг.1) предназначен для приема и хранения кода приказа, подлежащего выполнению. Занесение в ре- гистр 1 информации с входа 18 данных устройства выполняется по сигналу на входе 19 устройства. Код, запоминаемый в регистре 1, включает разряды непосредственно кода приказа, разряд адреса процессора, кото- рому этот приказ направляется, и контрольный, разряд нечетности всего кода.

Регистр 2 принятого кода приказа предназначен для приема и хранения кода, поступающего на информационный вход регистра 2 через магистральные усилители- приемники 6с информационной магистрали 29 устройства.

На выходах дешифратора 3 формируется унитарный код с единичным сигналом

приказа в соответствующем входному коду разряде. Число реально используемых комбинаций из полного набора 2К, где k - разрядность кода приказа, не является существенным в предлагаемом устройстве. Так. в команде СИГНАЛ ПРОЦЕССОРУ системы команд ЕС ЭВМ с восьмиразрядным кодом приказа реально используются только 12 приказов.

Регистр 4 битов состояния предназначен для приема и хранения кода, поступающего на информационный вход регистра 4 через магистральные усилители-приемники 6 с информационной магистрали 29 устройства, Одну группу входов регистра 4 составляют разряды состояния, поступающие непосредственно с магистрали. Другую группу входов составляют разряд ошибки и контрольный разряд нечетности, сформированные корректором 10 состояния.

Блок 5 контроля предназначен для проверки входного кода по условию нечетности формирования сигнала ошибки на выходе блока в случае невыполнения этого условия.

В устройстве магистраль для двунаправленной передачи между процессорами организована с использованием магистральных элементов 559 серии. Группа магистральных усилителей-приемников 6 реализована на микросхемах 559ИП5.

Блок 7 управления предназначен для формирования сигналов управления работой устройства и сигналов управления магистралью.

Блокируемый коммутатор 8 магистрали предназначен для передачи на информационную магистраль 29 устройства кода приказа с информационного входа коммутатора по сигналу на управляющем входе или разрядов состояния с другого информационного входа коммутатора по сигналу на другом управляющем входе. Кроме того, по нулевому сигналу на входе запрета на выходах блокируемого коммутатора 8 магистрали формируется нулевой код, удовлетворяющий условию контроля на нечет (с единичным контрольным разрядом).

Блок 9 разрядов состояния предназначен для формирования кода, отражающего состояние процессора, которому направлен приказ. Каждому действительному в данном устройстве приказу соответствует некоторый признак состояния, например стоп, стоп по сбою и др. Конкретное определение приказа и соответствующего признака не является существенным в данном устройстве и не рассматривается., Код на выходе блока 9 разрядов состояния содержит разряды состояния в ответ на действительные

приказы, разряд, определяющий недействительный в двнном устройстве приказ, разряд ошибки принятого кода приказа и контрольный разряд для всего кода.

Корректор 10 состояния предназначен для формирования сигнала ошибки при нарушении четности кода разрядов состояния, принятого в устройство. Кроме того, в случае ошибки в коде разрядов состояния формируются единичный разряд ошибки и скорректированный соответственно контрольный разряд для запоминания в регистре 4 битов состояния.

Триггер 11 ошибки предназначен для запоминания общего сигнала ошибки в принятом коде разрядов состояния.

На инверсном выходе элемента 12 сложения по модулю два формируется единичный сигнал ошибки, если в принятом коде приказа (на выходе регистра 2) нарушена четность.

В режиме разрешенного контроля (единичный потенциал на входе 21 режима контроля и первом входе элемента И 15) сигнал ошибки в принятом коде приказа с выхода элемента И 15 поступает на вход ошибки блока 9 разрядов состояния для формирования соответствующего разряда состояния и на вход элемента И 16. Кроме того, в режиме разрешенного контроля при обнаружении ошибки кода приказа в регистре 1 на выходе элемента И-НЕ 14 формируется низкий потенциал, поступающий на вход запрета блокируемого коммутатора 8 магистрали. При этом вместо ошибочного кода приказа в магистраль передается нулевой код приказа с правильным контрольным разрядом. Таким образом, ошибка кода приказа в передающем процессоре не создает условия прерывания по машинной ошибке в принимающем процессоре. На выходе элемента И 16 формируется сигнал ошибки принятого кода приказа.

В блокируемом коммутаторе 8 магистрали (фиг.2) магистральные элементы И-ИЛИ реализованы на микросхемах 559ИП4.

В блоке 9 разрядов состояния (фиг.З) разряды признаков состояния с входа 22 признаков подключены к первым входам элементов И 48.1-48.N.

Разряды недействительных приказов с информационного входа подключены к входам элемента ИЛИ 49. на выходе которого формируется разряд недействительного приказа в код разрядов состояния.

В корректоре 10 состояния (фиг.4) разряды состояния, разряд ошибки и контрольный разряд на вхдце корректора соединены с входами элемента 51 сложения по модулю

два, на инверсном входе которого формируется единичный сигнал ошибки, если во входном коде нарушена четность. Кроме того, этот сигнал ошибки по ИЛИ смешива- 5 ется с сигналом ошибки, принятым по соответствующей разрядной шине из принимающего приказ процессора, и передается по шине обобщенной ошибки на выход 43 корректора.

0Коррекция контрольного разряда выполняется при наличии сигналов ошибок принимающего (соответствующая разрядная шина входа 36) и передающего приказ процессора (на выходе элемента 51 сложе5 ния по модулю два).

В блоке 7 управления (фиг.5) по сигналу на входе 19 запуска устанавливается в единичное состояние триггер 55 запуска, выход которого соединен через магистральный

0 элемент 57 с выходом 26 блока управления и через элемент 58 задержки с информационным входом сдвигового регистра 56, син- хровход и вход сброса которого соединены . с соответствующими входами 23 и 24 блока.

5 На разрядных выходах сдвигового регистра 56 формируются потенциалы, задающие

развертку временной диаграммы работы устройства.

Первый разряд выхода сдвигового реги0 стра 56 соединен с входом магистрального элемента 68 в узле 5В магистрали управления, входом элемента И 74 в формирователе 61 управляющих сигналов и входом элемента ИЛИ 66 в узле 60 блокировки. Второй

5 разряд выхода сдвигового регистра 56 соединен с входом элемента ИЛИ 72 в узле 59 магистрали управления v, входом сброса триггера 55 запуска. Третий разряд выхода сдвигового регистра 56 соединен с вторым

0 входом элемента ИЛИ 72 в узле магистрали управления, четвертым управляющим выходом 40 блока управления и инверсным входом элемента И 74 в формирователе 61 управляющих сигналов.

5 Узел 59 магистрали управления предназначен для формирования сигналов управления магистралью и содержит два магистральных усилителя-передатчика 68 и 69, два магистральных усилителя-приемни0 ка70. 71 и элемент ИЛИ 72.

Рассмотрим работу устройства в системе с одним процессором (для определенно- .. сти адрес О) или в двухпроцессорной системе при сигнализации самому себе и

5 отсутствии ошибок. В исходном состоянии обнулены триггер 11 ошибки, а в блоке 7 управления триггер 55 запуска и сдвиговый регистр 56 (фиг.1. 5 и 7).

Если в устройстве сигнализация не запущена, т.е. на перзом-третьем магистральных управляющих выходах 26-28 и входе 25 признака занятости сформированы нулевые потенциалы, на выходе узла 60 блокировки независимо от адреса процессора на входе 20 адреса формируется единичный потен- циал, разрешающий сдвиг в регистре 56 нулевого потенциала с информационного входа.

По сигналу на входе 19 запуска устройства в регистр 1 кода приказа заносится информация с входа 18 данных устройства. Кроме того, в блоке 7 управления устанавливается в единичное состояние триггер 55 запуска, сигнал с выхода которого через магистральный усилитель-передатчик 57 передается на первый магистральный управляющий зыход 26 устройства, определяя тем самым признак занятости магистрали.

Единичный потенциал с выхода тригге- ра 55 запуска через элемент 58 задержки поступает на информационный вход сдвигового регистра 56. Элемент 58 задержки вводится для согласования временных диаграмм работы связанных устройств. Длительность задержки (интервал t1) определяется конкретными физическими параметрами магистральных линий, не является существенной в устройстве и поэтому не рассматривается.

Передним фронтом импульсов, поступающих на синхровход регистра 56 с сикхровхода 23 устройства, выполняется последовательное продвижение на пер- вый-третий разряды выхода регистра 56 единичного потенциала с информационного входа, причем сигнал на третьем разряде выхода формируется на два такта позже относительно сигнала на втором разряде выхода.

Единичный потенциал с первого разряда выхода регистра 56 через магистральный усилитель-передатчик 68 выдается на магистральный управляющий выход 27 устройства для блокирования возможного запускаразвертки временной диаграммы аналогичного устройства в связанном процессоре. По единичному значению второго разряда выхода регистра 56 сбрасывается триггер 55 запуска, нулевой потенциал с выхода которого через элемент 58 задержки, поступает на информационный вход регистра 56. На фиг.7 изображена задержка в четыре такта работы устройства. В интервале t2 от переднего фронта потенциала на первом разряде до переднего фронта потенциала на третьем разряде выхода регистра 56 на первом управляющем выходе 37 блока управления формируется сигнал выдачи хода приказа, по которому на выход

блокируемого коммутатора 8 магистрали передается код приказа и разряд адреса процессора, которому приказ направляется (О), с первого информационного входа 33 блокируемого коммутатора 8 магистрали (фиг.2). Если код в регистре 1 кода приказа не содержит ошибки (на выходе блока 5 контроля сформирован нулевой потенциал), на выходе элемента И-НЕ 14 формируется единичный потенциал, который поступает на вход 44 запрета блокируемого коммутатора 8 магистрали, разрешая передачу кода с первого информационного входа 33. С выхода коммутатора 8 код приказа выдается на информационную магистраль 29 и через группу магистральных усилителей-приемников 6 поступает на информационный вход регистра 2 принятого кода приказа, занесение в который выполняется по переднему фронту сигнала на втором управляющем выходе 38 блока управления (формируется на выходе магистрального усилителя-приемника 71 в интервале от переднего фронта потенциала на втором разряде выхода до заднего фронта потенциала на третьем разряде выхода регистра 56). Разряды кода приказа с выхода регистра 2 принятого кода приказа поступают на вход дешифратора 3, с выходов которого сигналы действительных приказов поступают на входы соответствующих элементов И группы 13, и, если в принятом коде приказа не содержится ошибки (нулевой потенциал на инверсном выходе элемента 12 сложения по модулю два, выходе 45 элемента И 15 и инверсных входах всех элементов И группы 13), передается на выход 31 приказов устройства. Кроме того, сигналы приказов с выходов дешифратора 3 поступают на информационный вход блока 9 разрядов состояния, в котором формируются разряды состояния по значению признаков на соответствующем входе 22 устройства. Каждому действительному приказу поставлен в соответствие некоторый признак состояния, он имеет единичное значение, в коде разрядов состояния на выходе блока 9 в соответствующем разряде формируется единичный потенциал. Кокретное определение приказов и соответствующих им признаков не является существенным в предлагаемом устройстве и не рассматривается. Поскольку в принятом коде приказа ошибок не обнаружено (нулевой потенциал на выходе элемента И 15), в выходном коде блока 9 разрядов состояния формируется нулевой разряд ошибки. По сигналу выдачи битов состояния на третьем управляющем выходе 39 блока 7 управления (фомируется в интервале t4 от фронта

потенциала на первом разряде до заднего фронта потенциала на третьем разряде выхода регистра 56) на выход блокируемого коммутатора 8 магистрали передается код разрядов состояния с второго информационного входа 41. С выхода коммутатора код разрядов состояния передается далее в информационную магистраль 29 и через группу магистральных усилителей-приемников 6 на группу входов регистра 4 битов состояния и вход корректора 10 состояния. Поскольку в коде битов состояния сформирован нулевой разряд ошибки, то в корректоре 10 состояния (фиг.4) на шину контрольного разряда выхода через элемент 54 сложения по модулю два передается значение контрольного разряда с входа 36 без изменения. Одновременно выполняется проверка входного кода по условию нечетности. Если ошибок в коде разрядов состояния не обнаружено, на выходе 42 и разрядной шине ошибки выхода 43 формируются нулевые потенциалы. По заднему фронту сигнала на управляющем выходе 40 блока 7 управления выполняется занесение кода в регистр 4 битов состояния и триггер 11 ошибки. С выхода регистра 4 битов состояния код разрядов состояния передается на выход 30 данных устройства для дальней- шего анализа. Нулевой потенциал ошибки с {выхода триггера 11 ошибки передается че- |рез элемент ИЛИ 17 на контрольный выход J32 устройства.

| Рассмотрим работу устройства при (наличии ошибок в разных контрольных точ- ках.

| Если ошибки обнаружены в коде прика- за до выдачи его в магистраль (на выходе регистра 1 кода приказа), то на выходе бло- |ка 5 контроля формируется единичный сиг- |нал ошибки, который поступает на вход элемента И-НЕ 14, на выходе которого в режиме контроля формируется нулевой потенциал запрета выдачи кода приказа. По нулевому потенциалу на входе 44 запрета на выходе 29 блокируемого коммутатора 8 магистрали формируется нулевой код при- каза с единичным контрольным разрядом. Нулевой код приказа (недействительный для устройства) запоминается далее в регистре 2 принятого кода приказа, дешифрируется и вызывает формирование единичного потенциала на выходе элемента ИЛИ 49 в блоке 9 разрядов состояния. |Код разрядов состояния с единичным разрядом недействительного кода приказа по сигналу на управляющем выходе 39 блока 7 управления передается через блокируемый коммутатор 8 магистрали на информационную магистраль 29. далее по сигналу на управляющему выходе 40 блока управления запоминается в регистре 4 битов состояния, с выхода которого передается на выход 30 данных устройства для анализа. Таким образом, ошибка в коде приказа (передающий процессор) в режиме контроля не вызывает условия формирования машинной ошибки в принимающем процессоре.

Если ошибка обнаружена в принятом

0 коде приказа (на выходе регистра 2 принятого кода приказа), на инверсном выходе элемента 12 сложения по модулю два формируется сигнал ошибки, который передается на второй вход элемента И 15, и в режиме

5 контроля по входу элемента И 16 в момент выдачи битов состояния (единичный сигнал на управляющем выходе 39 блока управления) через элемент ИЛИ 17 передается на контрольный выход 32 устройства. Кроме

0 того, единичным потенциалом с выхода элемента И 16, поступающим на инверсным входы элементов И группы 13, блокируется выдача сигналов приказов на выход 31 устройства, а также по сигналу с выхода эле5 мента И 15, поступающему на вход 45 ошибки блока 9 разрядов состояния, в коде разрядов состояния формируется единичный разряд ошибки. Код разрядов состояния передается через блокируемый

0 коммутаоор 8 магистрали на информационную магистраль 29 и далее через группу магистральных усилителей-приемников 6 на информационный вход регистра 4 битов состояния и на вход корректора 10.

5Если ошибок в принятом коде разрядов

состояния не обнаружено (нулевой потенциал на инверсном выходе элемента 51 сложения по модулю два), он без изменения запоминается в регистре 4 битов состояния

0 по сигналу на четвертом управляющем выходе 40 блока управления и передается далее на выход 30 данных устройства для анализа.

Таким образом, если ошибка обнаруже5 на принимающим процессором в полученном коде приказа, выполнение приказов блокируется, пославшему приказ процессору передается сообщение об ошибке в соответствующем разряде битов состояния, а

0 также формируется сигнал ошибки на контрольном выходе 32 в момент выдачи в информационную магистраль 29 разрядов состояния.

Если ошибка обнаружена в принятом из

5 информационной магистрали коде разрядов состояния (формируется сигнал ошибки на выходе 42 корректора 10 состояния), то в разряде ошибки выхода 43 формируется единичный потенциал. Скорректированный код разрядов состояния запоминается по

сигналу на управляющем выходе 40 блока управления в регистре 4 и передается на выход 30 данных для дальнейшего анализа. Кроме того, сигнал ошибки с выходе 42 корректора запоминается в триггере 11 ошибки и передается через элемент ИЛИ 17 на контрольный выход 32 устройства.

Рассмотрим работу устройства в двухпроцессорной системе при сигнализации процессора с адресом О (устройство А) процессору с адресом 1 (устройство В). По сигналу на входе 19 запуска устройства А (фиг.5, 6. 7) устанавливается в единичное состояние триггер 55 запуска, с выхода которого единичный потенциал через магист- ральный усилитель-передатчик 57 передается на магистральный управляющий выход 26 устройства А и поступает на магистральный вход 25 признака занятости в устройстве В. По этому сигналу и единич- ному потенциалу на входе 20 адреса узел 60 блокировки устройства В формирует на выходе нулевой потенциал, запрещающий сдвиг в регистре 56, Так как в устройстве В не выполняется команда сигнализации (от- сутствует сигнал на выходе 19 запуска), на первом магистральном управляющем выходе 26 и на выходах регистра 56 сформированы нулевые потенциалы. В устройстве А по нулевым потенциалам на входе 20 адреса и магистральном входе 25 признака занятости узел 60 блокировки формирует на выходе единичный потенциал, разрешающий сдвиг в регистре 56.

Кроме того, по сигналу на входе 19 за- пуска устройства А в регистре 1 кода приказа запоминаются код приказа и единичный разряд адреса процессора, которому приказ направляется. В интервале t2 (от переднего фронта сигнала на первом регистре до переднего фронта сигнала на третьем разряде выхода регистра 56) в устройстве А формируется сигнал выдачи кода приказа на первом управляющем выходе 37 блока 7 управления. Сигнал приема и дешифрации приказа формируется на выходе 28 узла 59 магистрали управления устройства А и через магистральные усилители-приемники 71 в узлах 59 магистрали управления устройств А и В передается на управляющие выходы 38 блоков 7.управления обоих устройств. По этим сигналам код приказа запоминается в регистре 2 принятого кода приказа. Единичный разряд адреса процессора, которому направляется приказ с выхо- да регистра 2 принятого кода приказа, передается на адресные входы блоков управления.

В формирователе 61 управляющих сигналов выполняется сравнение адресов передающего и принимающего приказ процессора. По результату сравнения на управляющем выходе 39 блока управления устройства В в интервале ta формируется сигнал выдачи битов состояния. По этому сигналу код разрядов состояния, сформированный на выходе блока 9 разрядов состояния устройства В, через блокируемый коммутатор 8 магистрали выдается в информационную магистраль 29 и далее в устройстве А через группу магистральных усилителей-приемников 6 поступает на информационный вход регистра 4 битов состояния, где запоминается по сигналу на четвертом управляющем выходе 40 блока 7 управления. С выхода регистра 4 код разрядов состояния,полученный из устройства В, передается на выход 30 данных устройства А для анализа, Кроме того, в интервале т.4 выдачи в магистраль 29 битов состояния в устройстве В на выходе элементов И группы 13 формируются сигналы приказов, если не обнаружено ошибок в принятом коде приказов (нулевой потенциал на инверсном выходе элемента 12 сложения по модулю два).

Если в устройстве В обнаружена ошибка в принятом коде приказа, выдача сигналов приказов на выход 31 приказов блокируется, в разряде ошибки кода разрядов состояния формируется единичный потенциал и на контрольный выход 32 передается сигнал ошибки.

Если ошибка обнаружена в коде приказа до выдачи его в информационную магистраль (на выходе регистра 1 кода приказа устройства А), то на выходе элемента И-НЕ 14 формируется нулевой потенциал запрета выдачи кода приказа, по которому в информационную магистраль 29 передается нулевой код приказа с правильным контрольнм разрядом. Нулевой код приказа в устройстве В воспринимается как недействительный, блок 9 разрядов состояния формирует единичный потенциал в соответствующем разряде ошибки и передает сформированный таким образом код разрядов состояния в информационную магистраль, Никаких управляющих воздействий в устройстве В в этом случае не вырабатывается. Код разрядов состояния с индикацией об ошибке принимающего процессора в соответствующем разряде запоминается в регистре 4 битов состояния устройства А и передается на выход 30 данных для анализа.

Рассмотрим работу устройства в конф-. ликтной ситуации - одновременная сигнализация обоих процессоров(фиг.5, 6. 8). При отсутствии сигнализации на выходах узлов 60 блокировки обоих устройств А и В независИмо от адреса сформированы единичные потенциалы, разрешающие сдвиг в регистpax

56 нулевых потенциалос информационных

входов. Предположим, что оба процессора сигнализируют одновременно, т.е. на первом магистральном управляющем выходе 26 устройства А и. соответствующем

ему

магистральном входе 25 признака занятос и устройства В. а также на первом маги- стральном управляющем выходе 26 устройства В и соответствующем ему магистр

альном входе 25 признака занятости устройства А сформированы единичные потэнциалы. Тогда в соответствии с приоритетом на выходе узла 60 блокировки устройства А единичный потенциал, разрешающий сдвиг в регистре 56. поддержива- етсн по цепи адреса (нулевой потенциал на первом адресном входе 20), а на выходе узла 60 блокировки устройства В формируется нулевой потенциал запрещающий в регистре 56. Таким образом, при вст ечной одновременной сигнализации первым запускается устройство, входящее в процессор с адресом О. На фиг.8 приведена диаграмма при одновременной сиг (ализации обоих процессоров друг другу (триказ О . и 1 ..). Пунктиром показана временна диаграмма для случая одновременной сигнализации обоих процессоров самим себе (т.е. приказ и ).

i Блокировка развертки временной диаграммы в устройстве В обеспечивается единичными потенциалами с магистрального вхо ;а 25 признака занятости, затем сигналами на выходах магистральных усилите- лей приемников 70 и 71.

Запускразвертки начинается через ин- терёал ts после снятия сигнала на магист- ра/ ьном управлением выходе 28. Дл1 тельность интервала t5 обеспечивается эле лентом 63 задержки. Конкретное значение интервала времени между окончанием раз зертки временной диаграммы в одном уст юйстве и запуском ее в другом определяется физическими характеристиками магистральных линий, не является сущест-юй в предлагаемом устройстве и не растривается. После запуска развертки

вен

сма

временной диаграммы в одном из устройств отрабатывается последовательность действий описанная ранее.

При работе устройства в автоматическом режиме контроля возникающие ошибки С борудования передающего процессора никэгда не вызывают ошибок в принимающем процессоре. Об ошибке оборудования принимающего процессора передающий процессор информируется соответствующей установкой битов состояния. Возврат битов состояния с неправильной четкостью указывает, что скорее всего неисправна магистраль. В принимающем процессоре

ошибка в принятом коде приказа не вызывает выработки никаких исполнительных сигналов, формируется только сигнал ошибки. Таким образом, при использовании устройства обеспечивается идентификация

возможного источника возникшей ошибки, при этом логические компоненты устройства (передающий и принимающий процессоры и магистраль) оказываются изолированы с точки зрения распространения ошибки, что позволяет сохранить работоспособность исправных компонентов. Вместе с этим в устройстве сохранена возможность работы в режиме блокировки контроля, когда делается попытка выдачи,

приема и выполнения приказа, код которого сформирован или принят с ошибкой. Использование устройства позволяет также сократить обьем вспомогательного оборудования межпроцессорной магистрали - из

устройства исключены регистры промежуточного хранения, мультиплексоры и линии обратных связей.

Формула изобретения

Устройство для сигнализации между

процессорами, содержащее регистр кода приказа, регистр принятого кода приказа, дешифратор, регистр битов состояния, блок контроля, блок разрядов состояния и блок

управления, синхровход и вход сброса которого соединены с одноименными входами устройства, вход запуска которого соединен с входом запуска блока управления и входом записи регистра кода приказа,

информационный вход и выход которого соединены с входом данных устройств и входом блока контроля соответственно, выход регистра принятого кода приказа соединен с первым адресным входом блока управления и с информационным входом дешифратора, выход которого соединен с информационным входом блока разрядов состояния, вход признаков которого соединен с одноименным входом устройства, выход регистра битов состояния соединен с выходом данных устройства, адресный вход блока управления соединен с входом задания адреса устройства, первый и второй выходы блока управления соединены

соответственно с синхровходами регистров принятого кода приказа и битов состояния, вход запрета блока управления соединен с магистральным входом признака устройства, третий, первый, четвертый выходы блока управления соединены с соответствующими магистральными управляющими выходами устройства, отличающееся тем, что, с целью повышения надежности и упрощения устройства, в него дополнительно введены блокируемый коммутатор магист- рали, группа приемников, корректор состояния, триггер ошибки, элемент сложения по модулю два, группа элементов И, элемент И-НЕ, два элемента И, элемент ИЛИ. выход которого соединен с контрольным выходом устройства, первый информационный вход блокируемого коммутатора магистрали соединен с выходом регистра кода приказа, вход режима контроля устройства соединен с первыми входами первого элемента И и элемента И-НЕ, второй вход и выход которого соединены соответственно с выходом блока контроля и входом запрета блокируемого коммутатора магистрали. выход которого поразрядно соединен с вы- ходом информационной магистрали устройства и с входами приемников группы, выходы которых соединены с соответствующими информационным входом регистра принятого кода приказа, первой информа- ционной группой входов регистра битов состояния и с информационным входом кооректора состояния, первый и второй выходы которого соответственно соединены с

.16

информационным входом триггера ошибки и второй группой информационных входов регистра битов состояния, синхровход которого соединен с синхровходом триггера ошибки и подключен к входу синхронизации устройства, вход сброса и выход триггера ошибки соответственно соединены с входом сброса устройства и первым входом элемента ИЛИ, выход блока разрядов состояния соединен с вторым информационным входом блокируемого коммутатора магистрали, первый и второй управляющие входы которого соединены соответственно с третьим и четвертым выходами блока управления, выход регистра принятого кода приказа соединен с входами элемента сложения по модулю два, инверсный выход которого соединен с вторым входом первого элемента И, выход которого соединен с входом ошибки блока разрядов состояния и первым входом второго элемента И, второй вход и выход которого соединены соответственно с четвертым выходом блока управления и с вторым входом элемента ИЛИ и инверсными входами элементов И группы, прямые входы и выходы которых соединены с выходами дешифратора и выходами приказов устройства соответственно.

гТ7

ЈS &

Lffi

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля магистралей электронных вычислительных машин | 1981 |

|

SU964648A1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

| Устройство для сопряжения ЭВМ с внешним абонентом | 1988 |

|

SU1594553A1 |

| МИКРОЭВМ | 1994 |

|

RU2108619C1 |

| Устройство для обмена информацией | 1988 |

|

SU1536395A2 |

| Устройство для сопряжения процессора с памятью | 1983 |

|

SU1149272A1 |

| Система для обмена данными между информационными процессорами | 1980 |

|

SU1001070A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Устройство для управления и обмена данными | 1986 |

|

SU1319042A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ. Цель изобретения - повышение надежности и упрощение устройства. Устройство содержит регистр кода приказа, регистр принятого кода приказа, дешифратор, регистр битов состояния, блок контроля, группу магистральных усилителей-приемников, блок управления, блокируемый коммутатор магистрали, блок разрядов состояния, корректор состояния, триггер ошибки, элемент сложения по модулю два, группу элементов И, элемент И-НЕ, два элемента И, элемент ИЛИ. Упрощение устройства и повышение надежности достигаются за счет использования единой линии связи для передачи кода приказа и кода разрядов состояния, а также за счет обеспечения выполнения приказов только при отсутствии сбоев. 8 ил.

W

/

/

/ff

/

9Ј

/

M 9V

Z9#SC/

/-ffV

ZZ

t OEACBL

V ЈЈ

f

c

Авторы

Даты

1993-08-30—Публикация

1991-02-05—Подача